June 1999

## **LM78**

# **Microprocessor System Hardware Monitor**

# **General Description**

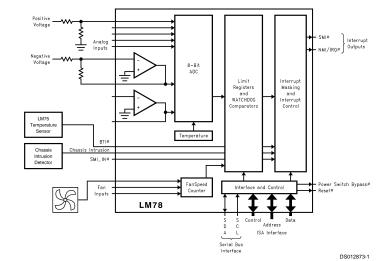

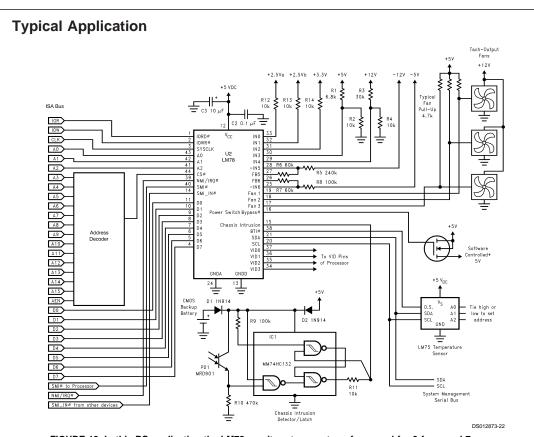

The LM78 is a highly integrated Data Acquisition system for hardware monitoring of servers, Personal Computers, or virtually any microprocessor based system. In a PC, the LM78 can be used to monitor power supply voltages, temperatures, and fan speeds. Actual values for these inputs can be read at any time, and programmable WATCHDOG™ limits in the LM78 activate a fully programmable and maskable interrupt system with two outputs.

The LM78 has an on-chip temperature sensor, 5 positive analog inputs, two inverting inputs (for monitoring negative voltages), and an 8-bit ADC. An input is provided for the overtemperature outputs of additional temperature sensors and this is linked to the interrupt system. The LM78 provides inputs for three fan tachometer outputs. Additional inputs are provided for Chassis Intrusion detection circuits, VID monitor inputs, and chainable interrupt. The LM78 provides both ISA and Serial Bus interfaces. A 32-byte auto-increment RAM is provided for POST (Power On Self Test) code storage.

## **Applications**

- System Hardware Monitoring for Servers and PCs

- Office Electronics

- Electronic Test Equipment and Instrumentation

## **Features**

- Temperature sensing

- 5 positive voltage inputs

- 2 op amps for negative voltage monitoring

- 3 fan speed monitoring inputs

- Input for additional temperature sensors

- Chassis Intrusion Detector input

- WATCHDOG comparison of all monitored values

- POST code storage RAM

- ISA and I<sup>2</sup>C<sup>TM</sup> Serial Bus interfaces

## **Key Specifications**

■ Voltage monitoring accuracy

±1% (max)

■ Temperature Accuracy -10°C to +100°C

±3°C (max)

Supply VoltageSupply Current

Operating: 1 mA typ Shutdown: 10 µA typ

■ ADC Resolution

8 Bits

# **Typical Application**

# indicates Active Low ("Not")

TRI-STATE® is a registered trademark of National Semiconductor Corporation. WATCHDOG™ is a trademark of National Semiconductor Corporation.  $I^2C^9$  is a registered trademark of the Phillips Corporation.

© 1999 National Semiconductor Corporation

DS012873

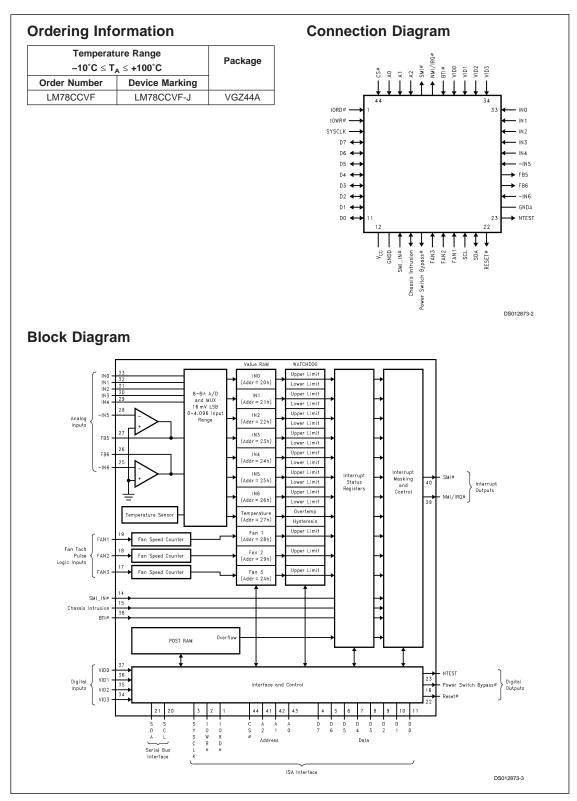

#### . .

| Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Pin   | Number        | Туре                                                                    | Description                                                                                                                                                                                                                                                                                                                             |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |               | Digital Input                                                           | An active low standard ISA bus I/O Read Control.                                                                                                                                                                                                                                                                                        |  |

| Pin Descriptions           Pin Name(s)         Pin Number of Pins           IORD         1           IOWR         2           SYSCLK         3           D7-D0         4-11           8           V <sub>CC</sub> (+5V)         12           1           Number of Pins           1           1           1           2           1           8                                                                                                                                                                                                                                                                                                                                                                                 |       | Digital Input | An active low standard ISA bus I/O Write Control.                       |                                                                                                                                                                                                                                                                                                                                         |  |

| Pin Name(s)         Pin Number of Pins         Ty           IORD         1         1         Digital           IOWR         2         1         Digital           SYSCLK         3         1         Digital           D7-D0         4-11         8         Digital                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       | <u> </u>      | The reference clock for the ISA bus. Typically ranges from 4.167 MHz to |                                                                                                                                                                                                                                                                                                                                         |  |

| Pin Name(s)         Pin Number of Pins           IORD         1           IOWR         2           SYSCLK         3           D7-D0         4-11           8           V <sub>CC</sub> (+5V)         12           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1 |       |               | 8.33 MHz. The minimum clock frequency this input can handle is 1 Hz.    |                                                                                                                                                                                                                                                                                                                                         |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4–11  | 8             | Digital I/O                                                             | Bi-directional ISA bus Data lines. D0 corresponds to the low order bit, with D7 the high order bit.                                                                                                                                                                                                                                     |  |

| V <sub>CC</sub> (+5V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12    | 1             | POWER                                                                   | +5V $V_{CC}$ power. Bypass with the parallel combination of 10 $\mu F$ (electolytic or tantalum) and 0.1 $\mu F$ (ceramic) bypass capacitors.                                                                                                                                                                                           |  |

| GNDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 13    | 1             | GROUND                                                                  | Internally connected to all digital circuitry.                                                                                                                                                                                                                                                                                          |  |

| SMI_IN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 14    | 1             | Digital Input                                                           | Chainable $\overline{SMI}$ (System Management Interrupt) Input. This is an active low input that propagates the $\overline{SMI}$ signal to the $\overline{SMI}$ output of the LM78 via $\overline{SMI}$ Mask Register Bit 6 and $\overline{SMI}$ enable Bit 1 of the Configuration Register.                                            |  |

| Chassis<br>Intrusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 15    | 1             | Digital I/O                                                             | An active high input from an external circuit which latches a Chassis Intrusion event. This line can go high without any clamping action regardless of the powered state of the LM78. The LM78 provides an internal open drain on this line, controlled by Bit 7 of NMI Mask Register 2, to provide a minimum 20 ms reset of this line. |  |

| Power<br>Switch<br>Bypass                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 16    | 1             | Digital Output                                                          |                                                                                                                                                                                                                                                                                                                                         |  |

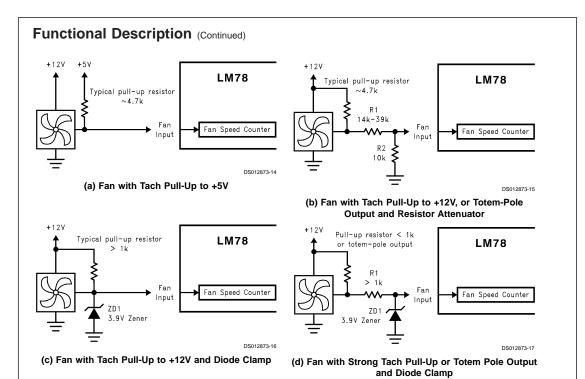

| FAN3-FAN1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 17–19 | 3             | Digital Input                                                           | 0V to +5V amplitude fan tachometer input.                                                                                                                                                                                                                                                                                               |  |

| SCL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20    | 1             | Digital Input                                                           | Serial Bus Clock.                                                                                                                                                                                                                                                                                                                       |  |

| SDA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 21    | 1             | Digital I/O                                                             | Serial Bus bidirectional Data.                                                                                                                                                                                                                                                                                                          |  |

| RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 22    | 1             | Digital Output                                                          | Master Reset, 5 mA driver (open drain), active low output with a 20 ms minimum pulse width. Available when enabeld via Bit 7 in SMI Mask Register 2.                                                                                                                                                                                    |  |

| NTEST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 23    | 1             | Test Output                                                             | NAND Tree totem-pole output that provides board-level connectivity testing. Refer to Section 11.0 on NAND Tree testing.                                                                                                                                                                                                                 |  |

| GNDA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 24    | 1             | GROUND                                                                  | Internally connected to all analog circuitry. The ground reference for all analog inputs.                                                                                                                                                                                                                                               |  |

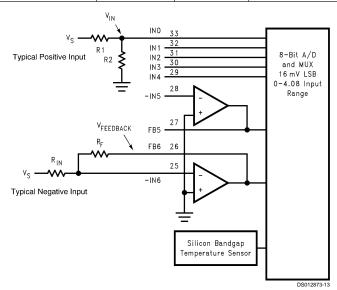

| -IN6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25    | 1             | Analog Input                                                            | Ground-referred inverting op amp input. Refer to Section 4.0, "ANALOG INPUTS".                                                                                                                                                                                                                                                          |  |

| FB6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 26    | 1             | Analog Output                                                           | Output of inverting op amp for Input 6. Refer to section 4.0, "ANALOG INPUTS".                                                                                                                                                                                                                                                          |  |

| FB5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 27    | 1             | Analog Output                                                           | Output of inverting op amp for Input 5. Refer to section 4.0, "ANALOG INPUTS".                                                                                                                                                                                                                                                          |  |

| -IN5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 28    | 1             | Analog Input                                                            | Ground-referred inverting op amp input. Refer to Section 4.0, "ANALOG INPUTS".                                                                                                                                                                                                                                                          |  |

| IN4-IN0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 29–33 | 5             | Analog Input                                                            | 0V to 4.096V FSR Analog Inputs.                                                                                                                                                                                                                                                                                                         |  |

| VID3-VID0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 34–37 | 4             | Digital Input                                                           | Voltage Supply readouts from P6. This value is read in the VID/Fan Divisor Register.                                                                                                                                                                                                                                                    |  |

| BTI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 38    | 1             | Digital Input                                                           | Board Temperature Interrupt driven by O.S. outputs of additional temperature sensors such as LM75. Provides internal pull-up of 10 k $\Omega$ .                                                                                                                                                                                         |  |

| NMI/IRQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 39    | 1             | Digital Output                                                          | Non-Maskable Interrupt (open source)/Interrupt Request (open drain). The mode is selected with Bit 5 of the Configuration Register and the output is enabled when Bit 2 of the Configuration Register is set to 1. The default state is disabled and $\overline{\mbox{IRQ}}$ mode.                                                      |  |

| SMI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 40    | 1             | Digital Output                                                          | System Management Interrupt (open drain). This output is enabled when Bit 1 in the Configuration Register is set to 1. The default state is disabled.                                                                                                                                                                                   |  |

#### . .

| Pin<br>Name(s) | Pin<br>Number | Number of Pins | Туре          | Description                                                                                                                           |

|----------------|---------------|----------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------|

| \2-A0          | 41–43         | 3              | Digital Input | The three lowest order bits of the 16-bit ISA Address Bus. A0 corresponds to the lowest order bit.                                    |

| S              | 44            | 1              | Digital Input | Chip Select input from an external decoder which decodes high order address bits on the ISA Address Bus. This is an active low input. |

| TOTAL PINS     |               | 44             |               |                                                                                                                                       |

|                |               | 1              |               |                                                                                                                                       |

|                |               |                |               |                                                                                                                                       |

|                |               |                |               |                                                                                                                                       |

|                |               |                |               |                                                                                                                                       |

|                |               |                |               |                                                                                                                                       |

|                |               |                |               |                                                                                                                                       |

|                |               |                |               |                                                                                                                                       |

|                |               |                |               |                                                                                                                                       |

|                |               |                |               |                                                                                                                                       |

|                |               |                |               |                                                                                                                                       |

|                |               |                |               |                                                                                                                                       |

|                |               |                |               |                                                                                                                                       |

|                |               |                |               |                                                                                                                                       |

|                |               |                |               |                                                                                                                                       |

|                |               |                |               |                                                                                                                                       |

|                |               |                |               |                                                                                                                                       |

|                |               |                |               |                                                                                                                                       |

|                |               |                |               |                                                                                                                                       |

|                |               |                |               |                                                                                                                                       |

|                |               |                |               |                                                                                                                                       |

|                |               |                |               |                                                                                                                                       |

|                |               |                |               |                                                                                                                                       |

|                |               |                |               |                                                                                                                                       |

|                |               |                |               |                                                                                                                                       |

|                |               |                |               |                                                                                                                                       |

|                |               |                |               |                                                                                                                                       |

|                |               |                |               |                                                                                                                                       |

|                |               |                |               |                                                                                                                                       |

|                |               |                |               |                                                                                                                                       |

|                |               |                |               |                                                                                                                                       |

|                |               |                |               |                                                                                                                                       |

|                |               |                |               |                                                                                                                                       |

|                |               |                |               |                                                                                                                                       |

|                |               |                |               |                                                                                                                                       |

Absolute Maximum Ratings (Notes 1, 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Positive Supply Voltage (V<sub>CC</sub>) 6.5V Voltage on Any Input or Output Pin -0.3V to  $(V_{CC}+0.3V)$ Ground Difference (GNDD-GNDA) ±300 mV Input Current at any Pin (Note 3) ±5 mA Package Input Current (Note 3) ±20 mA Maximum Junction Temperature 150°C  $(T_J max)$ ESD Susceptibility(Note 5)

Machine Model 175V Soldering Information

PQFP Package (Note 6):

Human Body Model 2000V

Vapor Phase (60 seconds) 215°C 220°C Infrared (15 seconds) Storage Temperature -65°C to +150°C

## Operating Ratings(Notes 1, 2)

Operating Temperature Range  $T_{MIN} \le T_A \le T_{MAX}$ LM78  $-55^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$ Specified Temperature Range  $T_{MIN} \le T_A \le T_{MAX}$ LM78  $-10^{\circ}\text{C} \le \text{T}_{\text{A}} \le +100^{\circ}\text{C}$ Junction to Ambient Thermal Resistance ( $\theta_{\text{JA}}(\text{Note 4})$  ) NS Package ID: VGZ44A 62°C/W +4.25V to +5.75V Supply Voltage (V<sub>CC</sub>) Ground Difference (IGNDD-GNDAI) ≤100 mV V<sub>IN</sub> Voltage Range -0.05V to  $V_{CC}$  + 0.05V

## **DC Electrical Characteristics**(Note 7)

The following specifications apply for +4.25  $V_{DC} \le V_{CC} \le +5.75 \ V_{DC}$ ,  $f_{SYSCLK} = 8.33 \ MHz$ ,  $R_S = 25\Omega$ , unless otherwise specified. Boldface limits apply for  $T_A = T_J = T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A = T_J = 25^{\circ}C$ .

| Symbol          | Parameter                                     | Conditions                                                             | Typical  | Limits   | Units     |

|-----------------|-----------------------------------------------|------------------------------------------------------------------------|----------|----------|-----------|

|                 |                                               |                                                                        | (Note 8) | (Note 9) | (Limits)  |

| POWER           | SUPPLY CHARACTERISTICS                        |                                                                        |          | •        |           |

| I <sub>cc</sub> | Supply Current                                | Interface Inactive                                                     | 1.0      | 2        | mA (max)  |

|                 |                                               | Shutdown Mode                                                          | 10       |          | μΑ        |

| TEMPER          | RATURE-TO-DIGITAL CONVERTER CHARACT           | ERISTICS                                                               |          | ,        | •         |

|                 | Accuracy                                      | $-10^{\circ}\text{C} \le \text{T}_{\text{A}} \le +100^{\circ}\text{C}$ |          | ±3       | °C (max)  |

|                 | Resolution                                    |                                                                        |          | 1        | °C (min)  |

| ANALO           | G-TO-DIGITAL CONVERTER CHARACTERISTI          | cs                                                                     |          |          |           |

|                 | Resolution (8 bits with full-scale at 4.096V) |                                                                        | 16       |          | mV        |

| TUE             | Total Unadjusted Error                        | (Note 10)                                                              |          | ±1       | % (max)   |

| DNL             | Differential Non-Linearity                    |                                                                        |          | ±1       | LSB       |

| PSS             | Power Supply Sensitivity                      |                                                                        | ±1       |          | %/V       |

| t <sub>C</sub>  | Total Monitoring Cycle Time                   | (Note 11)                                                              | 1.0      | 1.5      | sec (max) |

| OP AME          | CHARACTERISTICS                               |                                                                        |          | •        |           |

|                 | Output Current (Sourcing)                     |                                                                        | 50       |          | μΑ        |

|                 | Input Offset Voltage                          | I <sub>OUT</sub> = 50 μA                                               | ±1       |          | mV        |

|                 | Input Bias Current                            |                                                                        | ±0.1     |          | nA        |

|                 | PSRR                                          |                                                                        | 60       |          | dB        |

|                 | DC Open Loop Gain                             |                                                                        | 70       |          | dB        |

|                 | Gain Bandwidth Product                        |                                                                        | 500      |          | kHz       |

| MULTIP          | LEXER/ADC INPUT CHARACTERISTICS               |                                                                        |          |          |           |

|                 | On Resistance                                 |                                                                        | 400      | 2000     | Ω (max)   |

|                 | Off Channel Leakage Current                   |                                                                        | ±0.1     |          | nA        |

|                 | Input Current (On Channel Leakage Current)    |                                                                        | ±0.1     |          | nA        |

| FAN RP          | M-TO-DIGITAL CONVERTER                        | •                                                                      | •        |          |           |

|                 | Accuracy                                      | +25°C ≤ T <sub>A</sub> ≤ +75°C                                         |          | ±10      | % (max)   |

|                 |                                               | $-10^{\circ}\text{C} \le \text{T}_{\text{A}} \le +100^{\circ}\text{C}$ |          | ±15      | % (max)   |

|                 | Full-scale Count                              |                                                                        |          | 255      | (max)     |

# DC Electrical Characteristics(Note 7) (Continued)

The following specifications apply for  $+4.25 \text{ V}_{DC} \leq \text{V}_{CC} \leq +5.75 \text{ V}_{DC}$ ,  $f_{\text{SYSCLK}} = 8.33 \text{ MHz}$ ,  $R_{\text{S}} = 25\Omega$ , unless otherwise specified. **Boldface limits apply for T\_{\text{A}} = T\_{\text{L}} = T\_{\text{apply}} to T\_{\text{A}} = T\_{\text{L}} = T\_{\text{**

| Symbol                                     | Parameter                                                                                             | Conditions                                                             | Typical  | Limits                | Units    |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------|-----------------------|----------|

|                                            |                                                                                                       |                                                                        | (Note 8) | (Note 9)              | (Limits) |

| FAN RP                                     | M-TO-DIGITAL CONVERTER                                                                                |                                                                        |          |                       |          |

|                                            | FAN1 and FAN2 Nominal Input                                                                           | Divisor = 1, Fan Count = 153                                           | 8800     |                       | RPM      |

|                                            | RPM (See Section 6.0)                                                                                 | (Note 12)                                                              |          |                       |          |

|                                            |                                                                                                       | Divisor = 2, Fan Count = 153                                           | 4400     |                       | RPM      |

|                                            |                                                                                                       | (Note 12)                                                              |          |                       |          |

|                                            |                                                                                                       | Divisor = 3, Fan Count = 153                                           | 2200     |                       | RPM      |

|                                            |                                                                                                       | (Note 12)                                                              | 4400     |                       | 221      |

|                                            |                                                                                                       | Divisor = 4, Fan Count = 153<br>(Note 12)                              | 1100     |                       | RPM      |

|                                            | EANS Design Naminal Input DDM                                                                         |                                                                        | 4400     |                       | RPM      |

|                                            | FAN3 Design Nominal Input RPM                                                                         | Fan Count = 153 (Note 12)                                              |          | 20.2                  |          |

|                                            | Internal Clock Frequency                                                                              | +25°C ≤ T <sub>A</sub> ≤ +75°C                                         | 22.5     | 20.2                  | kHz (min |

|                                            |                                                                                                       | 10°0 1 T 1 100°0                                                       | 00.5     | 24.8                  | kHz (max |

|                                            |                                                                                                       | $-10^{\circ}\text{C} \le \text{T}_{\text{A}} \le +100^{\circ}\text{C}$ | 22.5     | 19.1                  | kHz (min |

| DICITAL CUITDUTS (Deuter Switch Dynasa NTE |                                                                                                       |                                                                        |          | 25.9                  | kHz (max |

|                                            | OUTPUTS (Power Switch Bypass, NTE                                                                     |                                                                        |          | 1                     |          |

| V <sub>OUT(1)</sub>                        | Logical "1" Output Voltage                                                                            | I <sub>OUT</sub> = ±5.0 mA                                             |          | 2.4                   | V (min)  |

| V <sub>OUT(0)</sub>                        | Logical "0" Output Voltage                                                                            | $I_{OUT} = \pm 5.0 \text{ mA}$                                         |          | 0.4                   | V (max)  |

|                                            | D7 DIGITAL OUTPUTS                                                                                    |                                                                        |          | 1                     |          |

| V <sub>OUT(1)</sub>                        | Logical "1" Output Voltage                                                                            | I <sub>OUT</sub> = ±12.0 mA                                            |          | 2.4                   | V (min)  |

| $V_{OUT(0)}$                               | Logical "0" Output Voltage                                                                            | I <sub>OUT</sub> = ±12.0 mA                                            |          | 0.4                   | V (max)  |

| I <sub>OUT</sub>                           | TRI-STATE® Output Current                                                                             | $V_{OUT} = 0 V_{DC}$                                                   | 0.005    | 1                     | μA (max  |

|                                            |                                                                                                       | $V_{OUT} = V_{CC}$                                                     | -0.005   | -1                    | μA (min) |

| OPEN D                                     | RAIN DIGITAL OUTPUTS (SDA, RESET,                                                                     | SMI, Chassis Intrusion)                                                |          |                       |          |

| $V_{OUT(0)}$                               | Logical "0" Output Voltage                                                                            | $I_{OUT} = -5.0 \text{ mA}$                                            |          | 0.4                   | V (min)  |

| I <sub>OH</sub>                            | High Level Output Current                                                                             | $V_{OUT} = V_{CC}$                                                     | 0.1      | 100                   | μA (max  |

|                                            | RESET and Chassis Intrusion                                                                           |                                                                        | 45       | 20                    | ms (min  |

|                                            | Pulse Width                                                                                           |                                                                        |          |                       |          |

|                                            | . INPUTS: $\overline{\text{SMI\_IN}}$ , VID0-VID3, $\overline{\text{BTI}}$ , $\overline{\text{CS}}$ , |                                                                        |          | ORD, IOWR, S          | SYSCLK), |

|                                            | es (D0–D7), Chassis Intrusion, and Tac                                                                | h Pulse Logic Inputs (FAN1, FAN2, FA                                   | AN3)     |                       |          |

| $V_{IN(1)}$                                | Logical "1" Input Voltage                                                                             |                                                                        |          | 2.0                   | V (min)  |

| $V_{IN(0)}$                                | Logical "0" Input Voltage                                                                             |                                                                        |          | 8.0                   | V (max)  |

| SERIAL                                     | BUS DIGITAL INPUTS (SCL, SDA)                                                                         |                                                                        |          |                       |          |

| $V_{IN(1)}$                                | Logical "1" Input Voltage                                                                             |                                                                        |          | 0.7 x V <sub>CC</sub> | V (min)  |

| $V_{IN(0)}$                                | Logical "0" Input Voltage                                                                             |                                                                        |          | 0.3 x V <sub>CC</sub> | V (max)  |

| ALL DIG                                    | SITAL INPUTS EXCEPT FOR BTI                                                                           |                                                                        |          |                       |          |

| I <sub>IN(1)</sub>                         | Logical "1" Input Current                                                                             | V <sub>IN</sub> = V <sub>CC</sub>                                      | -0.005   | -1                    | μA (min  |

| I <sub>IN(0)</sub>                         | Logical "0" Input Current                                                                             | V <sub>IN</sub> = 0 V <sub>DC</sub>                                    | 0.005    | 1                     | μA (max  |

| C <sub>IN</sub>                            | Digital Input Capacitance                                                                             |                                                                        | 20       |                       | pF       |

| BIT DIGI                                   | ITAL INPUT                                                                                            | ·                                                                      | •        |                       |          |

| I <sub>IN(1)</sub>                         | Logical "1" Input Current                                                                             | $V_{IN} = V_{CC}$                                                      | 1        | 10                    | μA (max  |

| I <sub>IN(0)</sub>                         | Logical "0" Input Current                                                                             | $V_{IN} = 0 V_{DC}$                                                    | -500     | -2000                 | μA (max  |

| 'IN(0)                                     |                                                                                                       |                                                                        |          |                       |          |

AC Electrical Characteristics (Note 13) The following specifications apply for +4.25  $V_{DC} \le V_{CC} \le +5.75$   $V_{DC}$  unless otherwise specified. Boldface limits apply for  $T_A = T_J = T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A = T_J = 25^{\circ}C$ .

| Symbol                     | Parameter                             | Conditions | Typical  | Limits   | Units    |  |

|----------------------------|---------------------------------------|------------|----------|----------|----------|--|

|                            |                                       |            | (Note 8) | (Note 9) | (Limits) |  |

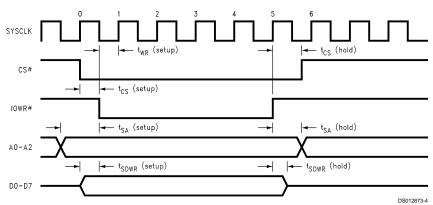

| ISA TIMING CHARACTERISTICS |                                       |            |          |          |          |  |

| f <sub>SYSCLK</sub>        | System Clock (SYSCLK) Input Frequency |            | 8.33     |          | MHz      |  |

| t <sub>CS</sub> (setup)    | CS Active to IORD/IOWR Active         |            |          | 10       | ns (min) |  |

| t <sub>CS</sub> (hold)     | IORD/IOWR Inactive to CS Inactive     |            |          | 10       | ns (min) |  |

| t <sub>SA</sub> (setup)    | Address Valid to IORD/IOWR Active     |            |          | 30       | ns (min) |  |

| t <sub>SA</sub> (hold)     | IORD/IOWR Inactive to Address Invalid |            |          | 10       | ns (min) |  |

| ISA WRITE TIMII            | NG                                    |            |          |          |          |  |

| t <sub>SDWR</sub> (setup)  | Data Valid to IOWR Active             |            |          | 5        | ns (min) |  |

| t <sub>SDWR</sub> (hold)   | IOWR Inactive to Data Invalid         |            |          | 5        | ns (min) |  |

| t <sub>WR</sub> (setup)    | IOWR Active to Rising Edge of SYSCLK  |            |          | 20       | ns (min) |  |

The delay between consecutive  $\overline{\text{IORD}}$  and  $\overline{\text{IOWR}}$  pulses should be greater than 50 ns to ensure that an Power-on reset does not occur unintentionally. (See **Section 3.2** 'Resets' )

FIGURE 1. ISA Bus Write Timing Diagram

. .

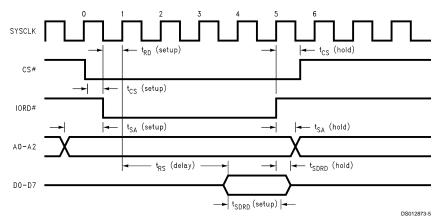

AC Electrical Characteristics (Note 13) The following specifications apply for +4.25  $V_{DC} \le V_{CC} \le$  +5.75  $V_{DC}$  unless otherwise specified. Boldface limits apply for  $T_A = T_J = T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A = T_J = 25$ °C. (Continued)

| Symbol                    | Parameter                                    | Conditions                 | Typical  | Limits   | Units    |  |

|---------------------------|----------------------------------------------|----------------------------|----------|----------|----------|--|

|                           |                                              |                            | (Note 8) | (Note 9) | (Limits) |  |

| ISA READ TIMIN            | ISA READ TIMING                              |                            |          |          |          |  |

| t <sub>SDRD</sub> (setup) | Data Valid to IORD Inactive                  |                            |          | 120      | ns (min) |  |

| t <sub>SDRD</sub> (hold)  | IORD Inactive to Data Invalid                |                            |          | 5        | ns (min) |  |

| t <sub>RD</sub> (setup)   | IORD Active to Rising Edge of SYSCLK         |                            |          | 20       | ns (min) |  |

| t <sub>RS</sub> (delay)   | Rising Edge of SYSCLK number 1 to Data Valid | With 8.33<br>MHz<br>SYSCLK |          | 360      | ns (max) |  |

The delay between consecutive  $\overline{\text{IORD}}$  and  $\overline{\text{IOWR}}$  pulses should be greater than 50 ns to ensure that an Power-on reset does not occur unintentionally. (See**Section 3.2**'Resets')

FIGURE 2. ISA Bus Read Timing Diagram

AC Electrical Characteristics (Note 13) The following specifications apply for +4.25  $V_{DC} \le V_{CC} \le$  +5.75  $V_{DC}$  unless otherwise specified. Boldface limits apply for  $T_A = T_J = T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A = T_J = 25^{\circ}C$ . (Continued)

| Symbol         | Parameter                                | Conditions | Typical  | Limits   | Units    |

|----------------|------------------------------------------|------------|----------|----------|----------|

|                |                                          |            | (Note 8) | (Note 9) | (Limits) |

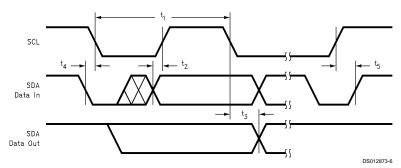

| SERIAL BUS TIM | ING CHARACTERISTICS                      |            |          |          |          |

| t <sub>1</sub> | SCL (Clock) Period                       |            |          | 2.5      | μs (min) |

| t <sub>2</sub> | Data In Setup Time to SCL High           |            |          | 100      | ns (min) |

| t <sub>3</sub> | Data Out Stable After SCL Low            |            |          | 0        | ns (min) |

| t <sub>4</sub> | SDA Low Setup Time to SCL Low (start)    |            |          | 100      | ns (min) |

| t <sub>5</sub> | SDA High Hold Time After SCL High (stop) |            |          | 100      | ns (min) |

FIGURE 3. Serial Bus Timing Diagram

#### . .

#### **Electrical Characteristics (Continued)**

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 2: All voltages are measured with respect to GND, unless otherwise specified

Note 3: When the input voltage  $(V_{IN})$  at any pin exceeds the power supplies  $(V_{IN} < (GNDD \text{ or } GNDA) \text{ or } V_{IN} > V_{CC})$ , the current at that pin should be limited to 5 mA. The 20 mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of 5 mA to four.

Note 4: The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_J$ max,  $\theta_{JA}$  and the ambient temperature,  $T_A$ . The maximum allowable power dissipation at any temperature is  $P_D = (T_J$ max $-T_A)/\theta_{JA}$ .

Note 5: The human body model is a 100 pF capacitor discharged through a 1.5 k $\Omega$  resistor into each pin. The machine model is a 200 pF capacitor discharged directly into each pin.

Note 6: See the section titled "Surface Mount" found in any post 1986 National Semiconductor Linear Data Book for other methods of soldering surface mount de-

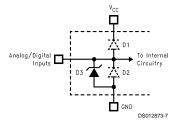

Note 7: Each input and output is protected by a nominal 6.5V breakdown voltage zener diode to GND; as shown below, input voltage magnitude up to 0.3V above  $V_{CC}$  or 0.3V below GND will not damage the LM78. There are parasitic diodes that exist between the inputs and the power supply rails. Errors in the ADC conversion can occur if these diodes are forward biased by more than 50 mV. As an example, if  $V_{CC}$  is 4.50  $V_{DC}$ , input voltage must be  $\leq$  4.55  $V_{DC}$ , to ensure accurate conversions.

An x indicates that the diode exists.

| Pin Name            | D1 | D2 | D3 |

|---------------------|----|----|----|

| ĪŌRD                |    |    | х  |

| ĪOWR                |    |    | х  |

| SYSCLK              |    |    | х  |

| D0-D7               | х  | х  | х  |

| SMI_IN              |    |    | х  |

| Chassis Intrusion   |    | х  | х  |

| Power Switch Bypass | х  | х  | х  |

| Pin Name  | D1 | D2 | D3 |

|-----------|----|----|----|

| FAN1-FAN3 |    |    | х  |

| SCL       |    |    | х  |

| SDA       |    | х  | х  |

| RESET     |    | х  | х  |

| NTEST     | х  | х  | х  |

| Pin Name  | D1 | D2 | D3 |

|-----------|----|----|----|

| -IN6      |    | х  | х  |

| FB6       | х  | х  | х  |

| FB5       | х  | х  | х  |

| -IN5      |    | х  | Х  |

| IN4-IN0   | х  | х  | х  |

| VID3-VID0 | х  | х  | х  |

| Pin Name | D1 | D2 | D3 |

|----------|----|----|----|

| BTI      | х  |    | Х  |

| NMI/IRQ  | х  | х  | х  |

| SMI      |    | х  | х  |

| A0-A2    |    |    | Х  |

| CS       |    |    | Х  |

FIGURE 4. ESD Protection Input Structure

Note 8: Typicals are at  $T_J = T_A = 25$  °C and represent most likely parametric norm.

Note 9: Limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

Note 10: TUE (Total Unadjusted Error) includes Offset, Gain and Linearity errors of the ADC and any error introduced by the amplifiers as shown in the circuit of Figure 13.

Note 11: Total Monitoring Cycle Time includes temperature conversion, 7 analog input voltage conversions and 3 tachometer readings. Each temperature and input voltage conversion takes 100 ms typical and 112 ms maximum. Fan tachometer readings take 20 ms typical, at 4400 rpm, and 200 ms max.

Note 12: The total fan count is based on 2 pulses per revolution of the fan tachometer output.

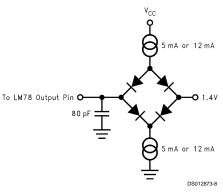

Note 13: Timing specifications are tested at the TTL logic levels,  $V_{IL}$ =0.4V for a falling edge and  $V_{IH}$ =2.4V for a rising edge. TRI-STATE output voltage is forced to 1.4V.

#### **Test Circuit**

FIGURE 5. Digital Output Load Circuitry

# **Functional Description**

#### 1.0 GENERAL DESCRIPTION

The LM78 provides 7 analog inputs, a temperature sensor, a Delta-Sigma ADC (Analog-to-Digital Converter), 3 fan speed counters, WATCHDOG registers, and a variety of inputs and outputs on a single chip. Interfaces are provided for both the ISA parallel bus or Serial Bus. The LM78 performs power supply, temperature, and fan monitoring for personal computers.

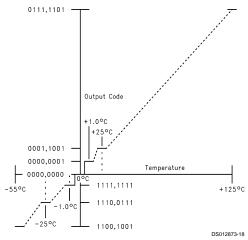

The LM78 continuously converts analog inputs to 8-bit digital words with a 16 mV LSB (Least Significant Bit) weighting, yielding input ranges of from 0V to 4.096V. The two negative analog inputs provide inverting op amps, with their non-inverting input referred to ground. With additional external feedback components, these inputs provide measurements of negative voltages (such as -5V and -12V power supplies). The analog inputs are useful for monitoring several power supplies present in a typical computer. Temperature is converted to an 8-bit two's-complement digital word with a 1°C LSB.

Fan inputs measure the period of tachometer pulses from the fans, providing a higher count for lower fan speeds. The fan inputs are digital inputs with an acceptable range of 0V to 5V and a transition level of approximately 1.4V. Full scale fan counts are 255 (8-bit counter) and this represents a stopped or very slow fan. Nominal speeds, based on a count of 153, are programmable from 1100 to 8800 RPM on FAN1 and FAN2, with FAN3 fixed at 4400 RPM. Signal conditioning circuitry is included to accommodate slow rise and fall times.

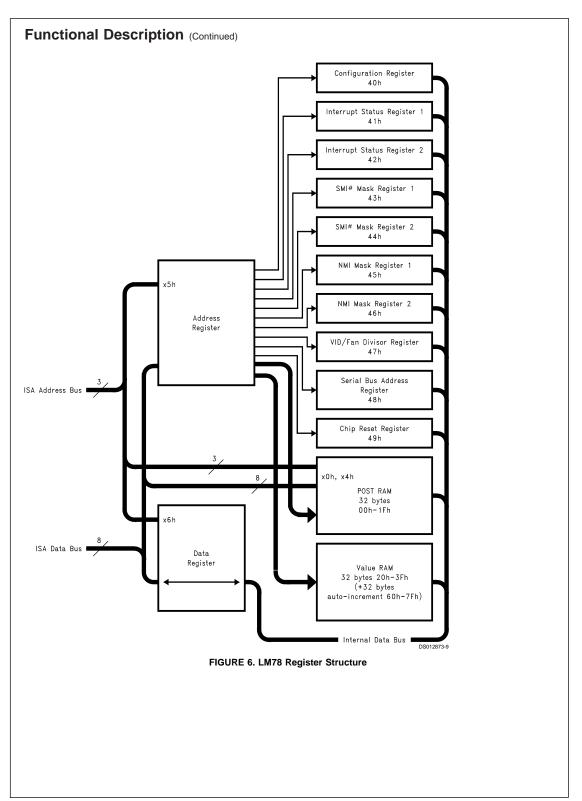

The LM78 provides a number of internal registers, as detailed in Figure 6. These include:

- Configuration Register: Provides control and configuration.

- Interrupt Status Registers: Two registers to provide status of each WATCHDOG limit or Interrupt event.

- Interrupt Mask Registers: Allows masking of individual Interrupt sources, as well as separate masking for each of both hardware Interrupt outputs.

- VID/Fan Divisor Registers: A register to read the status of the VID input lines. The high bits of this register contain the divisor bits for FAN1 and FAN2 inputs.

- Serial Bus Address Register: Contains the Serial Bus address. At power on it assumes the default value of 0101101 binary, and can be altered via the ISA or Serial Bus interface.

- Chip Reset/ID Register: Allows reseting of all the registers to the default power-on reset value. Provides a bit for identification between the current version of this device and an older version which does not have this reset capability.

- POST RAM: FIFO RAM to store up to 32 bytes of 8-bit POST codes. Overflow of the POST RAM will set an Interrupt. The POST RAM, located at base address x0h and x4h, allows for easy decoding to address 80h and 84h, the normal addresses for outputting of POST codes. Interrupt will only be set when writing to port x0h or x4h. The POST RAM can be read via ports 85h and 86h.

- Value RAM: The monitoring results: temperature, voltages, fan counts, and WATCHDOG limits are all contained in the Value RAM. The Value RAM consists of a total of 64 bytes. The first 11 bytes are all of the results, the next 19 bytes are the WATCHDOG limits, and are located at 20h-3Fh, including two unused bytes in the upper locations. The next 32 bytes, located at 60h-7Fh, mirror the first 32 bytes with identical contents. The only difference in the upper bytes are that they auto-increment the LM78 Internal Address Register when read from or written to via the ISA bus (auto-increment is not available for Serial Bus communications).

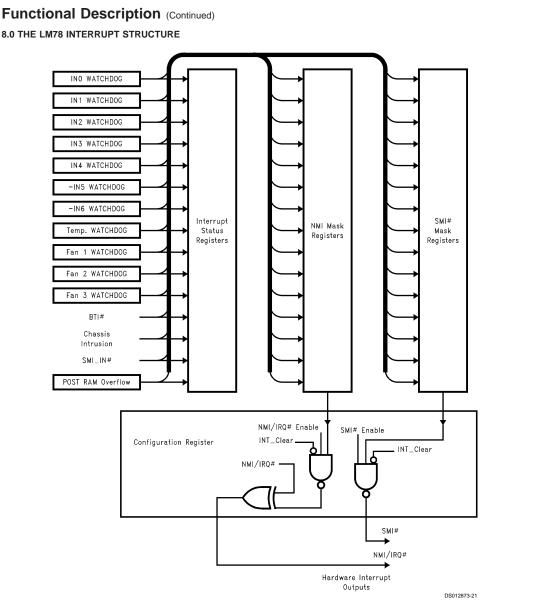

When the LM78 is started, it cycles through each measurement in sequence, and it continuously loops through the sequence approximately once every second. Each measured value is compared to values stored in WATCHDOG, or Limit registers. When the measured value violates the programmed limit the LM78 will set a corresponding Interrupt in the Interrupt Status Registers. Two hardware Interrupt lines,  $\overline{\text{SMI}}$  and  $\overline{\text{NMI/IRQ}}$ , are fully programmable with separate masking of each Interrupt source, and masking of each output. In addition, the Configuration Register has control bits to enable or disable the hardware Interrupts.

Additional digital inputs are provided for chaining of  $\overline{\text{SMI}}$  (System Management Interrupt), outputs of multiple external LM75 temperature sensors via the  $\overline{\text{BTI}}$  (Board Temperature Interrupt) input, and a Chassis Intrusion input. The Chassis Intrusion input is designed to accept an active high signal from an external circuit that latches when the case is removed from the computer.

#### •

## Functional Description (Continued)

#### 2.0 INTERFACE

The LM78 only decodes the three lowest address bits on the ISA bus. Referring to the ISA bus timing diagrams in *Figure 1* and *Figure 2*, the Chip Select Input,  $\overline{\text{CS}}$ , should be taken low by external address decoder circuitry to access the LM78. The LM78 decodes the following base addresses:

- -Port x0h: Power On Self Test codes from ISA bus.

- -Port x4h: Power On Self Test codes from ISA bus.

- -Port x5h: The LM78s Internal Address Register

- -Port x6h: Data Register

$\overline{\text{IORD}}$  is the standard ISA bus signal that indicates to the LM78 that it may drive data on to the ISA data bus.

$\overline{\text{IOWR}}$  is the standard ISA command to the LM78 that it may latch data from the ISA bus.

SYSCLK is the standard ISA SYSCLK, typically 8.33 MHz. This clock is used only for timing of the ISA interface of the LM78. All other clock functions within LM78 such as the ADC and fan counters are done with a separate asynchronous internal clock.

A typical application designed to utilize the POST RAM would decode the LM78 to the address space starting at 80h, which is where POST codes are output to. Otherwise, the LM78 can be decoded into a different desired address space.

To communicate with an LM78 Register, first write the address of that Register to Port x5h. Read or write data from or to that register via Port x6h. A write will take  $\overline{\text{IOWR}}$  low, while a read will take  $\overline{\text{IORD}}$  low.

If the Serial Bus Interface and ISA bus interface are used simultaneously there is the possibility of collision. To prevent this from occurring in applications where both interfaces are used, read port x5h and if the Most Significant Bit, D7, is high, ISA communication is limited to reading port x5h only until this bit is low. A Serial Bus communication occurring while ISA is active will not be a problem, since even a single bit of Serial Bus communication requires 10 microseconds, in comparison to less than a microsecond for an entire ISA communication.

#### 2.1 Internal Registers of the LM78

TABLE 1. The internal registers and their corresponding internal LM78 address is as follows:

| Register                    | LM78 Internal Hex<br>Address                 | Power on<br>Value | Notes                                                                                                                                                                                |

|-----------------------------|----------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                             | (This is the data to be written to Port x5h) |                   |                                                                                                                                                                                      |

| Configuration Register      | 40h                                          | 0000 1000         |                                                                                                                                                                                      |

| Interrupt Status Register 1 | 41h                                          | 0000 0000         | Auto-increment to the address of Interrupt Status Register 2 after a read or write to Port x6h.                                                                                      |

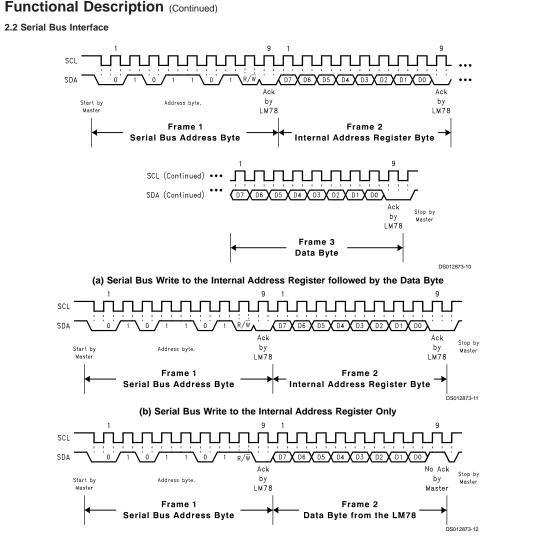

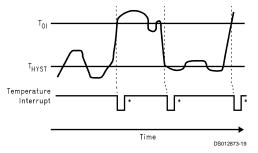

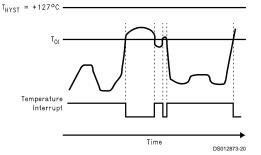

| Interrupt Status Register 2 | 42h                                          | 0000 0000         |                                                                                                                                                                                      |