SBOS231C - JANUARY 2002 - REVISED JULY 2003

# **Digital Temperature Sensor** with I2C Interface

## **FEATURES**

- DIGITAL OUTPUT: I<sup>2</sup>C Serial 2-Wire

- RESOLUTION: 9- to 12-Bits, User-Selectable

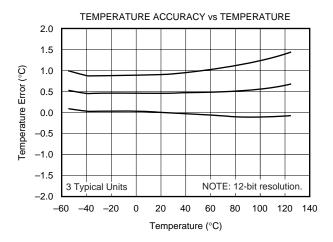

- ACCURACY: ±2.0°C from -25°C to +85°C (max)

- $\pm 3.0^{\circ}$ C from  $-55^{\circ}$ C to  $+125^{\circ}$ C (max)

- LOW QUIESCENT CURRENT: 45µA, 0.1µA Standby

- WIDE SUPPLY RANGE: 2.7V to 5.5V

- TINY SOT23-6 PACKAGE

# **APPLICATIONS**

- POWER-SUPPLY TEMPERATURE MONITORING

- COMPUTER PERIPHERAL THERMAL PROTECTION

- NOTEBOOK COMPUTERS

- CELL PHONES

- BATTERY MANAGEMENT

- OFFICE MACHINES

- THERMOSTAT CONTROLS

- **ENVIRONMENTAL MONITORING and HVAC**

- **ELECTROMECHANICAL DEVICE TEMPERATURE**

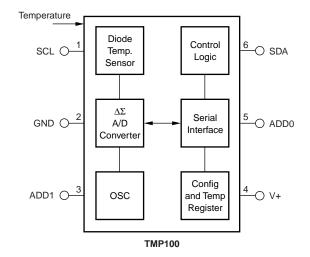

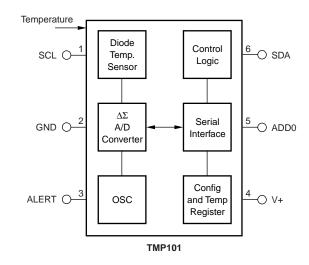

## DESCRIPTION

The TMP100 and TMP101 are 2-wire, serial output temperature sensors available in SOT23-6 packages. Requiring no external components, the TMP100 and TMP101 are capable of reading temperatures with a resolution of 0.0625°C.

The TMP100 and TMP101 feature SMBus and I2C™ interface compatibility, with the TMP100 allowing up to eight devices on one bus. The TMP101 offers SMBus alert function with up to three devices per bus.

The TMP100 and TMP101 are ideal for extended temperature measurement in a variety of communication, computer, consumer, environmental, industrial, and instrumentation applications.

The TMP100 and TMP101 are specified for operation over a temperature range of -55°C to +125°C.

I<sup>2</sup>C is a registered trademark of Philips Incorporated.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

### ABSOLUTE MAXIMUM RATINGS(1)

| Power Supply, V+                          | 7.5V           |

|-------------------------------------------|----------------|

| Input Voltage <sup>(2)</sup>              | 0.5V to 7.5V   |

| Operating Temperature Range               | 55°C to +125°C |

| Storage Temperature Range                 | 60°C to +150°C |

| Junction Temperature (T <sub>J</sub> Max) | +150°C         |

| Lead Temperature (soldering)              | +300°C         |

NOTES: (1) Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability. (2) Input voltage rating applies to all TMP100 and TMP101 input voltages.

# www.sensor-ic.com/ TEL:0755-1837654E AVE 65-BROS-TAA:Is 600163.com DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

## PACKAGE/ORDERING INFORMATION

| PRODUCT               | PACKAGE-LEAD            | PACKAGE<br>DESIGNATOR <sup>(1)</sup> | SPECIFIED<br>TEMPERATURE<br>RANGE       | PACKAGE<br>MARKING     | ORDERING<br>NUMBER                                         | TRANSPORT<br>MEDIA, QUANTITY                                                  |

|-----------------------|-------------------------|--------------------------------------|-----------------------------------------|------------------------|------------------------------------------------------------|-------------------------------------------------------------------------------|

| TMP100<br>"<br>TMP101 | SOT23-6<br>"<br>SOT23-6 | DBV<br>"<br>DBV<br>"                 | -55°C to +125°C<br>"<br>-55°C to +125°C | T100<br>"<br>T101<br>" | TMP100NA/250<br>TMP100NA/3K<br>TMP101NA/250<br>TMP101NA/3K | Tape and Reel, 250 Tape and Reel, 3000 Tape and Reel, 250 Tape and Reel, 3000 |

NOTE: (1) For the most current specifications and package information, refer to our web site at www.ti.com.

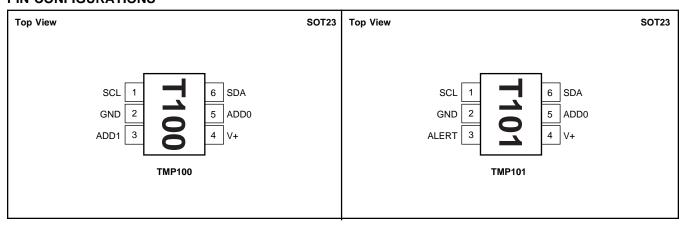

## **PIN CONFIGURATIONS**

# ELEGITATO ALL hCHARACIT. ERISTIGS 6549 FAX:0755-83376182 E-MAIL:szss200163.com

At  $T_A = -55^{\circ}C$  to +125°C, and V+ = 2.7V to 5.5V, unless otherwise noted.

|                                   |                |                                      | ·           | TMP100, TMP1 | 01      |           |

|-----------------------------------|----------------|--------------------------------------|-------------|--------------|---------|-----------|

| PARAMETER                         |                | CONDITION                            | MIN         | TYP          | MAX     | UNITS     |

| TEMPERATURE INPUT                 |                |                                      |             |              |         |           |

| Range                             |                |                                      | -55         |              | +125    | °C        |

| Accuracy (Temperature Error)      |                | −25°C to +85°C                       |             | ±0.5         | ±2.0    | °C        |

|                                   |                | −55°C to +125°C                      |             | ±1.0         | ±3.0    | °C        |

| Resolution                        |                | Selectable                           |             | ±0.0625      |         | °C        |

| DIGITAL INPUT/OUTPUT              |                |                                      |             |              |         |           |

| Input Logic Levels:               |                |                                      |             |              |         |           |

| V <sub>IH</sub>                   |                |                                      | 0.7(V+)     |              | 6.0     | V         |

| V <sub>II</sub>                   |                |                                      | -0.5        |              | 0.3(V+) | v         |

| Input Current, I <sub>IN</sub>    |                | $0V \le V_{IN} \le 6V$               | ""          |              | 1       | μA        |

| Output Logic Levels:              |                | 0 · - · IN - 0 ·                     |             |              |         | "'        |

| V <sub>OL</sub> SDA               |                | I <sub>OL</sub> = 3mA                | 0           | 0.15         | 0.4     | V         |

| V <sub>OL</sub> ALERT             |                | $I_{OL} = 4mA$                       | Ö           | 0.15         | 0.4     | v         |

| Resolution                        |                | Selectable                           | ľ           | 9 to 12      | 0.4     | Bits      |

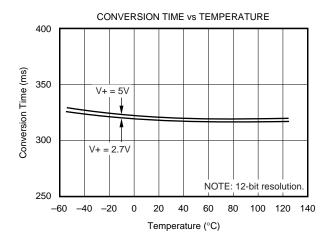

| Conversion Time                   |                | 9-Bit                                |             | 40           | 75      | ms        |

| Conversion Time                   |                | 10-Bit                               |             | 80           | 150     | ms        |

|                                   |                | 11-Bit                               |             | 160          | 300     | ms        |

|                                   |                | 11-Bit                               |             | 320          | 600     |           |

| O                                 |                |                                      |             | <b>I</b>     | 600     | ms<br>-/- |

| Conversion Rate                   |                | 9-Bit                                |             | 25           |         | s/s       |

|                                   |                | 10-Bit                               |             | 12           |         | s/s       |

|                                   |                | 11-Bit                               |             | 6            |         | s/s       |

|                                   |                | 12-Bit                               |             | 3            |         | s/s       |

| POWER SUPPLY                      |                |                                      |             |              |         |           |

| Operating Range                   |                |                                      | 2.7         |              | 5.5     | V         |

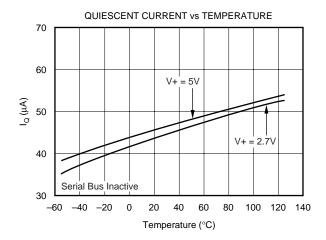

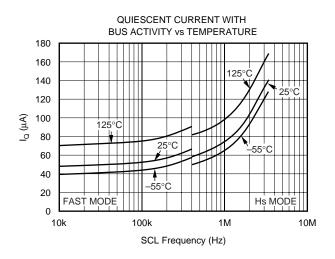

| Quiescent Current                 | l <sub>Q</sub> | Serial Bus Inactive                  |             | 45           | 75      | μΑ        |

|                                   |                | Serial Bus Active, SCL Freq = 400kHz |             | 70           |         | μΑ        |

|                                   |                | Serial Bus Active, SCL Freq = 3.4MHz |             | 150          |         | μΑ        |

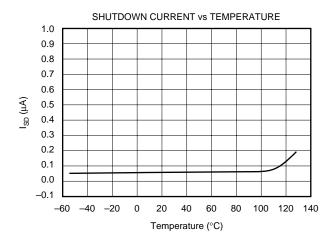

| Shutdown Current                  | $I_{SD}$       | Serial Bus Inactive                  |             | 0.1          | 1       | μΑ        |

|                                   |                | Serial Bus Active, SCL Freq = 400kHz |             | 20           |         | μΑ        |

|                                   |                | Serial Bus Active, SCL Freq = 3.4MHz |             | 100          |         | μΑ        |

| TEMPERATURE RANGE                 |                |                                      |             |              |         |           |

| Specified Range                   |                |                                      | <b>–</b> 55 |              | +125    | °C        |

| Storage Range                     |                |                                      | -60         |              | +150    | °C        |

| Thermal Resistance, $\theta_{JA}$ |                | SOT23-6 Surface-Mount                |             | 150          |         | °C/W      |

At  $T_A = +25$ °C, V+ = 5.0V, unless otherwise noted.

# APPLICATIONS: INFORMATION: 5-83376549 WX: 5785 RESGISTERMAIL: szss200163.com

The TMP100 and TMP101 are digital temperature sensors optimal for thermal management and thermal protection applications. The TMP100 and TMP101 are I2C and SMBus interface compatible and are specified over a temperature range of -55°C to +125°C.

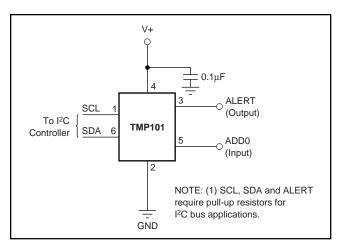

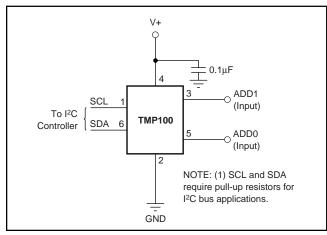

The TMP100 and TMP101 require no external components for operation except for pull-up resistors on SCL, SDA, and ALERT, although a 0.1µF bypass capacitor is recommended, as shown in Figure 1 and Figure 2.

FIGURE 1. Typical Connections of the TMP101.

FIGURE 2. Typical Connections of the TMP100.

The die flag of the lead frame is connected to pin 2. The sensing device of the TMP100 and TMP101 is the chip itself. Thermal paths run through the package leads as well as the plastic package. The lower thermal resistance of metal causes the leads to provide the primary thermal path. The GND pin of the TMP100 or TMP101 is directly connected to the metal lead frame, and is the best choice for thermal input.

To maintain the accuracy in applications requiring air or surface temperature measurement, care should be taken to isolate the package and leads from ambient air temperature. A thermally conductive adhesive will assist in achieving accurate surface temperature measurement.

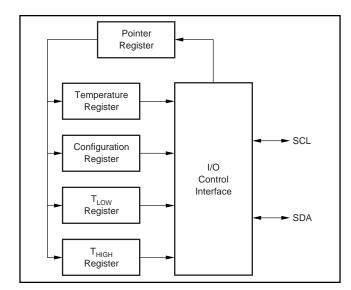

Figure 3 shows the internal register structure of the TMP100 and TMP101. The 8-bit Pointer Register of the TMP100 and TMP101 is used to address a given data register. The Pointer Register uses the two LSBs to identify which of the data registers should respond to a read or write command. Table I identifies the bits of the Pointer Register byte. Table II describes the pointer address of the registers available in the TMP100 and TMP101. Power-up Reset value of P1/P0 is 00.

FIGURE 3. Internal Register Structure of TMP100 and TMP101.

|   | P7 | P6 | P5 | P4 | P3 | P2 | P1     | P0      |

|---|----|----|----|----|----|----|--------|---------|

| Ĺ | 0  | 0  | 0  | 0  | 0  | 0  | Regist | er Bits |

TABLE I. Pointer Register Byte.

| P1 | P0 | REGISTER                                |

|----|----|-----------------------------------------|

| 0  | 0  | Temperature Register (READ Only)        |

| 0  | 1  | Configuration Register (READ/WRITE)     |

| 1  | 0  | T <sub>LOW</sub> Register (READ/WRITE)  |

| 1  | 1  | T <sub>HIGH</sub> Register (READ/WRITE) |

TABLE II. Pointer Addresses of the TMP100 and TMP101 Registers.

## **TEMPERATURE REGISTER**

The Temperature Register of the TMP100 or TMP101 is a 12bit read-only register that stores the output of the most recent conversion. Two bytes must be read to obtain data and are described in Table III and Table IV. The first 12 bits are used to indicate temperature with all remaining bits equal to zero. Data format for temperature is summarized in Table V. Following power-up or reset, the Temperature Register will read 0°C until the first conversion is complete.

| D7  | D6  | D5 | D4 | D3 | D2 | D1 | D0 |

|-----|-----|----|----|----|----|----|----|

| T11 | T10 | T9 | T8 | T7 | T6 | T5 | T4 |

TABLE III. Byte 1 of Temperature Register.

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----|----|----|----|----|----|----|

| Т3 | T2 | T1 | T0 | 0  | 0  | 0  | 0  |

TABLE IV. Byte 2 of Temperature Register.

| TEMPERATUR <mark>S</mark> UNSTA | R传感 <b>坚控制 PUT</b> PYTwww.s<br>(BINARY) | sensor-ic.com/<br>HEX |

|---------------------------------|-----------------------------------------|-----------------------|

| 128                             | 0111 1111 1111                          | 7FF                   |

| 127.9375                        | 0111 1111 1111                          | 7FF                   |

| 100                             | 0110 0100 0000                          | 640                   |

| 80                              | 0101 0000 0000                          | 500                   |

| 75                              | 0100 1011 0000                          | 4B0                   |

| 50                              | 0011 0010 0000                          | 320                   |

| 25                              | 0001 1001 0000                          | 190                   |

| 0.25                            | 0000 0000 0100                          | 004                   |

| 0.0                             | 0000 0000 0000                          | 000                   |

| -0.25                           | 1111 1111 1100                          | FFC                   |

| <b>–</b> 25                     | 1110 0111 0000                          | E70                   |

| <b>–</b> 55                     | 1100 1001 0000                          | C90                   |

| -128                            | 1000 0000 0000                          | 800                   |

TABLE V. Temperature Data Format.

The user can obtain 9, 10, 11, or 12 bits of resolution by addressing the Configuration Register and setting the resolution bits accordingly. For 9, 10, or 11 bit resolution, the most significant bits in the Temperature Register are used with the unused LSBs set to zero.

## **CONFIGURATION REGISTER**

The Configuration Register is an 8-bit read/write register used to store bits that control the operational modes of the temperature sensor. Read/write operations are performed MSB first. The format of the Configuration Register for the TMP100 and TMP101 is shown in Table VI, followed by a breakdown of the register bits. The power-up/reset value of the Configuration Register is all bits equal to 0. The OS/ ALERT bit will read as 1 after power-up/reset.

| В | yte | D7       | D6 | D5 | D4 | D3 | D2  | D1 | D0 |

|---|-----|----------|----|----|----|----|-----|----|----|

|   | 1   | OS/ALERT | R1 | R0 | F1 | F0 | POL | TM | SD |

TABLE VI. Configuration Register Format.

## SHUTDOWN MODE (SD)

The Shutdown Mode of the TMP100 and TMP101 allows the user to save maximum power by shutting down all device circuitry other than the serial interface, which reduces current consumption to less than  $1\mu A$ . For the TMP100 and TMP101, Shutdown Mode is enabled when the SD bit is 1. The device will shutdown once the current conversion is completed. For SD equal to 0, the device will maintain continuous conversion.

## THERMOSTAT MODE (TM)

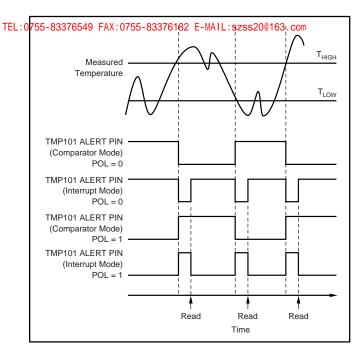

The Thermostat Mode bit of the TMP101 indicates to the device whether to operate in Comparator Mode (TM = 0) or Interrupt Mode (TM = 1). For more information on comparator and interrupt modes, see text "HIGH and LOW Limit Registers."

## **POLARITY (POL)**

The Polarity Bit of the TMP101 allows the user to adjust the polarity of the ALERT pin output. If POL = 0, the ALERT pin will be active LOW, as shown in Figure 4. For POL = 1 the ALERT Pin will be active HIGH, and the state of the ALERT Pin is inverted.

FIGURE 4. Output Transfer Function Diagrams.

## **FAULT QUEUE (F1/F0)**

A fault condition occurs when the measured temperature exceeds the limits set in the  $T_{HIGH}$  and  $T_{LOW}$  Registers. The Fault Queue is provided to prevent a false alert due to environmental noise and requires consecutive fault measurements to trigger the alert function of the TMP101. Table VII defines the number of measured faults that may be programmed to trigger an alert condition.

| F1 | F0 | CONSECUTIVE FAULTS |

|----|----|--------------------|

| 0  | 0  | 1                  |

| 0  | 1  | 2                  |

| 1  | 0  | 4                  |

| 1  | 1  | 6                  |

TABLE VII. Fault Settings of the TMP100 and TMP101.

## **CONVERTER RESOLUTION (R1/R0)**

The Converter Resolution Bits control the resolution of the internal Analog-to-Digital (A/D) converter. This allows the user to maximize efficiency by programming for higher resolution or faster conversion time. Table VIII identifies the Resolution Bits and relationship between resolution and conversion time.

| R1 | R0 | RESOLUTION         | CONVERSION TIME (typical) |

|----|----|--------------------|---------------------------|

| 0  | 0  | 9 Bits (0.5°C)     | 40ms                      |

| 0  | 1  | 10 Bits (0.25°C)   | 80ms                      |

| 1  | 0  | 11 Bits (0.125°C)  | 160ms                     |

| 1  | 1  | 12 Bits (0.0625°C) | 320ms                     |

TABLE VIII. Resolution of the TMP100 and TMP101.

The TMP100 and TMP101 feature a One-Shot Temperature Measurement Mode. When the device is in Shutdown Mode, writing a 1 to the OS/ALERT bit will start a single temperature conversion. The device will return to the shutdown state at the completion of the single conversion. This is useful to reduce power consumption in the TMP100 and TMP101 when continuous monitoring of temperature is not required.

Reading the OS/ALERT bit will provide information about the Comparator Mode status. The state of the POL bit will invert the polarity of data returned from the OS/ALERT bit. For POL = 0, the OS/ALERT will read as 0 until the temperature equals or exceeds  $T_{HIGH}$  for the programmed number of consecutive faults, causing the OS/ALERT bit to read as 1. The OS/ALERT bit will continue to read as 1 until the temperature falls below  $T_{LOW}$  for the programmed number of consecutive faults when it will again read as 0. The status of the TM bit does not affect the status of the OS/ALERT bit.

## HIGH AND LOW LIMIT REGISTERS

In Comparator Mode (TM = 0), the ALERT Pin of the TMP101 becomes active when the temperature equals or exceeds the value in  $T_{HIGH}$  and generates a consecutive number of faults according to fault bits F1 and F0. The ALERT pin will remain active until the temperature falls below the indicated  $T_{LOW}$  value for the same number of faults.

In Interrupt Mode (TM = 1) the ALERT Pin becomes active when the temperature equals or exceeds T<sub>HIGH</sub> for a consecutive number of fault conditions. The ALERT pin remains active until a read operation of any register occurs or the device successfully responds to the SMBus Alert Response Address. The ALERT pin will also be cleared if the device is placed in Shutdown Mode. Once the ALERT pin is cleared, it will only become active again by the temperature falling below T<sub>LOW</sub>. When the temperature falls below T<sub>LOW</sub>, the ALERT pin will become active and remain active until cleared by a read operation of any register or a successful response to the SMBus Alert Response Address. Once the ALERT pin is cleared, the above cycle will repeat with the ALERT pin becoming active when the temperature equals or exceeds T<sub>HIGH</sub>. The ALERT pin can also be cleared by resetting the device with the General Call Reset command. This will also clear the state of the internal registers in the device returning the device to Comparator Mode (TM = 0).

Both operational modes are represented in the Figure 4. Tables IX and X describe the format for the  $T_{HIGH}$  and  $T_{LOW}$  registers. Power-up Reset values for  $T_{HIGH}$  and  $T_{LOW}$  are:  $T_{HIGH} = 80^{\circ} C$  and  $T_{LOW} = 75^{\circ} C$ . The format of the data for  $T_{HIGH}$  and  $T_{LOW}$  is the same as for the Temperature Register.

All 12 bits for the Temperature,  $T_{HIGH}$ , and  $T_{LOW}$  registers are used in the comparisons for the ALERT function for all converter resolutions. The three LSBs in  $T_{HIGH}$  and  $T_{LOW}$  can affect the ALERT output even if the converter is configured for 9-bit resolution.

| 54 <b>19</b> y <b>f9</b> AX | :0 <b>P3</b> 5-8 | 33 <b>76</b> 18 | 2 EPMAI | L: <b>92</b> ss2 | 0 <b>Ф3</b> 3. | corp2 | D1 | D0 |

|-----------------------------|------------------|-----------------|---------|------------------|----------------|-------|----|----|

| 1                           | H11              | H10             | H9      | H8               | H7             | H6    | H5 | H4 |

|                             |                  |                 |         |                  |                |       |    |    |

|                             |                  |                 |         |                  |                |       |    |    |

| Byte                        | D7               | D6              | D5      | D4               | D3             | D2    | D1 | D0 |

TABLE IX. Bytes 1 and 2 of THIGH Register.

| Byte | D7        | D6  | D5 | D4  | D3 | D2 | D1 | D0 |

|------|-----------|-----|----|-----|----|----|----|----|

| 1    | L11       | L10 | L9 | L8  | L7 | L6 | L5 | L4 |

| Byte | D7        | D6  | D5 | D4  | D3 | D2 | D1 | D0 |

| Dyte | <i>D1</i> | 50  | טט | D-7 | 23 | DZ | יט | D0 |

| 2    | L3        | L2  | L1 | L0  | 0  | 0  | 0  | 0  |

TABLE X. Bytes 1 and 2 of T<sub>LOW</sub> Register.

## **SERIAL INTERFACE**

The TMP100 and TMP101 operate only as slave devices on the  $\rm I^2C$  bus and SMBus. Connections to the bus are made via the open-drain I/O lines SDA and SCL. The TMP100 and TMP101 support the transmission protocol for fast (up to 400kHz) and high-speed (up to 3.4MHz) modes. All data bytes are transmitted most significant bit first.

#### SERIAL BUS ADDRESS

To program the TMP100 and TMP101, the master must first address slave devices via a slave address byte. The slave address byte consists of seven address bits, and a direction bit indicating the intent of executing a read or write operation.

The TMP100 features two address pins to allow up to eight devices to be addressed on a single I<sup>2</sup>C interface. Table XI describes the pin logic levels used to properly connect up to eight devices. 'Float' indicates the pin is left unconnected. The state of pins ADD0 and ADD1 is sampled on the first I<sup>2</sup>C bus communication and should be set prior to any activity on the interface.

| ADD1  | ADD0  | SLAVE ADDRESS |

|-------|-------|---------------|

| 0     | 0     | 1001000       |

| 0     | Float | 1001001       |

| 0     | 1     | 1001010       |

| 1     | 0     | 1001100       |

| 1     | Float | 1001101       |

| 1     | 1     | 1001110       |

| Float | 0     | 1001011       |

| Float | 1     | 1001111       |

TABLE XI. Address Pins and Slave Addresses for TMP100.

The TMP101 features one address pin and an ALERT pin, allowing up to three devices to be connected per bus. Pin logic levels are described in Table XII. The address pins of the TMP100 and TMP101 are read after reset or in response to an I<sup>2</sup>C address acquire request. Following reading, the state of the address pins is latched to minimize power dissipation associated with detection.

| ADD0  | SLAVE ADDRESS |  |  |

|-------|---------------|--|--|

| 0     | 1001000       |  |  |

| Float | 1001001       |  |  |

| 1     | 1001010       |  |  |

TABLE XII. Address Pins and Slave Address for TMP101.

# BUS OVERVIEW STAR传感与控制 http://www.sensor-ic.com/ TEL:0byte@sbyttes are written to the register addressed by the Pointer

The device that initiates the transfer is called a "master," and the devices controlled by the master are "slaves." The bus must be controlled by a master device that generates the serial clock (SCL), controls the bus access, and generates the START and STOP conditions.

To address a specific device, a START condition is initiated, indicated by pulling the data-line (SDA) from a HIGH to LOW logic level while SCL is HIGH. All slaves on the bus shift in the slave address byte, with the last bit indicating whether a read or write operation is intended. During the ninth clock pulse, the slave being addressed responds to the master by generating an Acknowledge and pulling SDA LOW.

Data transfer is then initiated and sent over eight clock pulses followed by an Acknowledge Bit. During data transfer SDA must remain stable while SCL is HIGH, as any change in SDA while SCL is HIGH will be interpreted as a control signal.

Once all data has been transferred, the master generates a STOP condition indicated by pulling SDA from LOW to HIGH, while SCL is HIGH.

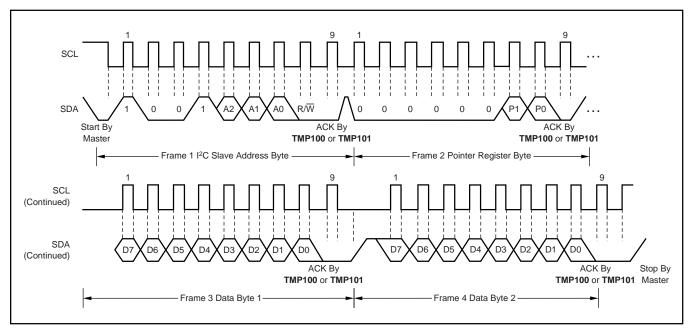

#### WRITING/READING TO THE TMP100 AND TMP101

Accessing a particular register on the TMP100 and TMP101 is accomplished by writing the appropriate value to the Pointer Register. The value for the Pointer Register is the first byte transferred after the  $I^2C$  slave address byte with the  $R/\overline{W}$  bit LOW. Every write operation to the TMP100 and TMP101 requires a value for the Pointer Register. (Refer to Figure 6.)

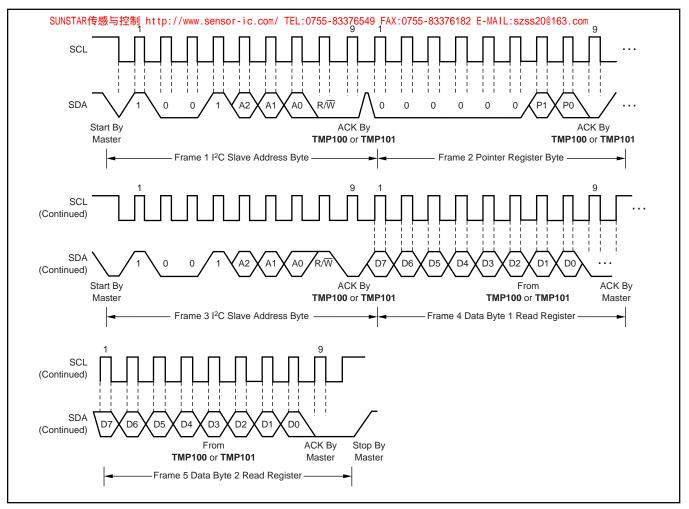

When reading from the TMP100 and TMP101, the last value stored in the Pointer Register by a write operation is used to determine which register is read by a read operation. To change the register pointer for a read operation, a new value must be written to the Pointer Register. This is accomplished by issuing an I²C slave address byte with the  $R/\overline{W}$  bit LOW, followed by the Pointer Register Byte. No additional data is required. The master can then generate a START condition and send the I²C slave address byte with the  $R/\overline{W}$  bit HIGH to initiatnIthe read command. See Figure 7 for details of this sequence. If repeated reads from the same register are desired, it is not necessary to continually send the Pointer Register bytes as the TMP100 and TMP101 will remember the Pointer Register value until it is changed by the next write operation.

## **SLAVE MODE OPERATIONS**

The TMP100 and TMP101 can operate as slave receivers or slave transmitters.

### Slave Receiver Mode:

The first byte transmitted by the master is the slave address, with the  $R/\overline{W}$  bit LOW. The TMP100 or TMP101 then acknowledges reception of a valid address. The next byte transmitted by the master is the Pointer Register. The TMP100 or TMP101 then acknowledges reception of the Pointer Register byte. The next

register. The TMP100 and TMP101 will acknowledge reception of each data byte. The master may terminate data transfer by generating a START or STOP condition.

#### **Slave Transmitter Mode:**

The first byte is transmitted by the master and is the slave address, with the  $R/\overline{W}$  bit HIGH. The slave acknowledges reception of a valid slave address. The next byte is transmitted by the slave and is the most significant byte of the register indicated by the Pointer Register. The master acknowledges reception of the data byte. The next byte transmitted by the slave is the least significant byte. The master acknowledges reception of the data byte. The master may terminate data transfer by generating a Not-Acknowledge on reception of any data byte, or generating a START or STOP condition.

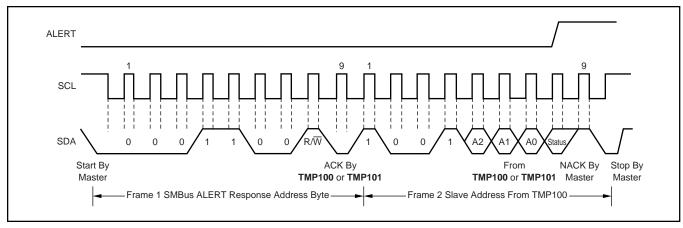

## **SMBus ALERT FUNCTION**

The TMP101 supports the SMBus Alert function. When the TMP101 is operating in Interrupt Mode (TM = 1), the ALERT pin of the TMP101 may be connected as an SMBus Alert signal. When a master senses that an ALERT condition is present on the ALERT line, the master sends an SMBus Alert command (00011001) on the bus. If the ALERT pin of the TMP101 is active, the TMP101 will acknowledge the SMBus Alert command and respond by returning its slave address on the SDA line. The eighth bit (LSB) of the slave address byte will indicate if the temperature exceeding  $T_{HIGH}$  or falling below  $T_{LOW}$  caused the ALERT condition. This bit will be HIGH if the temperature is greater than or equal to  $T_{HIGH}$ . This bit will be LOW if the temperature is less than  $T_{LOW}$ . Refer to Figure 8 for details of this sequence.

If multiple devices on the bus respond to the SMBus Alert command, arbitration during the slave address portion of the SMBus alert command will determine which device will clear its ALERT status. If the TMP101 wins the arbitration, its ALERT pin will become inactive at the completion of the SMBus Alert command. If the TMP101 loses the arbitration, its ALERT pin will remain active.

The TMP100 will also respond to the SMBus ALERT command if its TM bit is set to 1. Since it does not have an ALERT pin, the master needs to periodically poll the device by issuing an SMBus Alert command. If the TMP100 has generated an ALERT, it will acknowledge the SMBus Alert command and return its slave address in the next byte.

### **GENERAL CALL**

The TMP100 and TMP101 respond to the I²C General Call address (0000000) if the eighth bit is 0. The device will acknowledge the General Call address and respond to commands in the second byte. If the second byte is 00000100, the TMP100 and TMP101 will latch the status of their address pins, but will not reset. If the second byte is 00000110, the TMP100 and TMP101 will latch the status of their address pins and reset their internal registers.

In order for the I2C bus to operate at frequencies above 400kHz, the master device must issue an Hs-mode master code (00001XXX) as the first byte after a START condition to switch the bus to high-speed operation. The TMP100 and TMP101 will not acknowledge this byte as required by the I<sup>2</sup>C specification, but will switch their input filters on SDA and SCL and their output filters on SDA to operate in Hs-mode, allowing transfers at up to 3.4MHz. After the Hs-mode master code has been issued, the master will transmit an I2C slave address to initiate a data transfer operation. The bus will continue to operate in Hs-mode until a STOP condition occurs on the bus. Upon receiving the STOP condition, the TMP100 and TMP101 will switch their input and output filters back to fast-mode operation.

#### **TIMING DIAGRAMS**

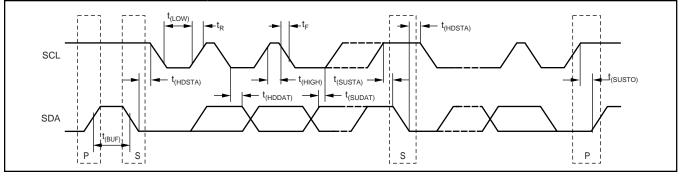

The TMP100 and TMP101 are I<sup>2</sup>C and SMBus compatible. Figures 5 to 8 describe the various operations on the TMP100 and TMP101. Bus definitions are given below. Parameters for Figure 5 are defined in Table XIII.

Bus Idle: Both SDA and SCL lines remain HIGH.

Start Data Transfer: A change in the state of the SDA line, from HIGH to LOW, while the SCL line is HIGH, defines a START condition. Each data transfer is initiated with a START condition.

Stop Data Transfer: A change in the state of the SDA line from LOW to HIGH while the SCL line is HIGH defines a STOP condition. Each data transfer is terminated with a repeated START or STOP condition.

Data Transfer: The number of data bytes transferred between a START and a STOP condition is not limited and is determined by the master device. The receiver acknowledges the transfer of data.

Acknowledge: Each receiving device, when addressed, is obliged to generate an Acknowledge bit. A device that acknowledges must pull down the SDA line during the Acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the Acknowledge clock pulse. Setup and hold times must be taken into account. On a master receive, the termination of the data transfer can be signaled by the master generating a Not-Acknowledge on the last byte that has been transmitted by the slave.

|                                                                                            |                           | FAST MODE |         | HIGH-SPEED MODE |       |     |

|--------------------------------------------------------------------------------------------|---------------------------|-----------|---------|-----------------|-------|-----|

| PARAMETER                                                                                  | MIN                       | MAX       | MIN MAX |                 | UNITS |     |

| SCLK Operating Frequency                                                                   | f <sub>(SCLK)</sub>       |           | 0.4     |                 | 3.4   | MHz |

| Bus Free Time Between STOP and START Cond                                                  | lition t <sub>(BUF)</sub> | 600       |         | 160             |       | ns  |

| Hold Time After Repeated START Condition. After this period, the first clock is generated. | t <sub>(HDSTA)</sub>      | 600       |         | 160             |       | ns  |

| Repeated START Condition Setup Time                                                        | t <sub>(SUSTA)</sub>      | 600       |         | 160             |       | ns  |

| STOP Condition Setup Time                                                                  | t <sub>(SUSTO)</sub>      | 600       |         | 160             |       | ns  |

| Data Hold Time                                                                             | t <sub>(HDDAT)</sub>      | 0         |         | 0               |       | ns  |

| Data Setup Time                                                                            | t <sub>(SUDAT)</sub>      | 100       |         | 10              |       | ns  |

| SCLK Clock LOW Period                                                                      | t <sub>(LOW)</sub>        | 1300      |         | 160             |       | ns  |

| SCLK Clock HIGH Period                                                                     | t <sub>(HIGH)</sub>       | 600       |         | 60              |       | ns  |

| Clock/Data Fall Time                                                                       | t <sub>F</sub>            |           | 300     |                 | 160   | ns  |

| Clock/Data Rise Time                                                                       | t <sub>R</sub>            |           | 300     |                 | 160   | ns  |

TABLE XIII. Timing Diagram Definitions.

FIGURE 5. I<sup>2</sup>C Timing Diagram.

FIGURE 6. I<sup>2</sup>C Timing Diagram for Write Word Format.

FIGURE 7. I2C Timing Diagram for Read Word Format.

FIGURE 8. Timing Diagram for SMBus ALERT.

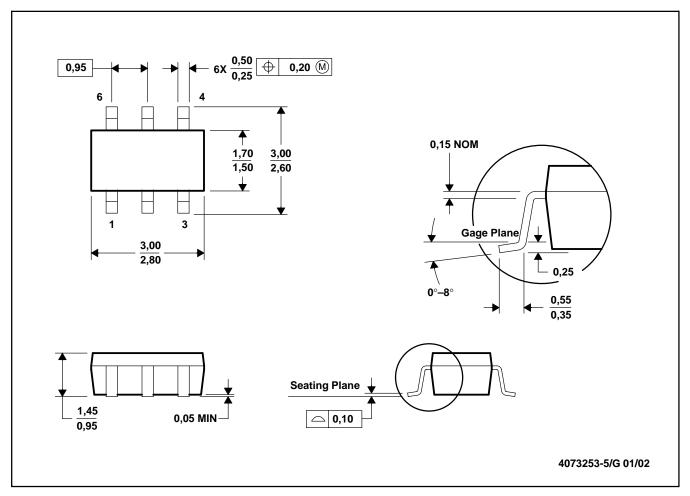

# DBV (R-PDSO-G6)

## **PLASTIC SMALL-OUTLINE**

1

MPDS026D - FEBRUARY 1997 - REVISED FEBRUARY 2002

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion.

- D. Leads 1, 2, 3 may be wider than leads 4, 5, 6 for package orientation.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

|                  |                        |                    |                           |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2003, Texas Instruments Incorporated

SUNSTAR商斯达实业集团是集研发、生产、工程、销售、代理经销 、技术咨询、信息服务等为一体的高 科技企业,是专业高科技电子产品生产厂家,是具有10多年历史的专业电子元器件供应商,是中国最早和 最大的仓储式连锁规模经营大型综合电子零部件代理分销商之一,是一家专业代理和分銷世界各大品牌IC 芯片和電子元器件的连锁经营綜合性国际公司。在香港、北京、深圳、上海、西安、成都等全国主要电子 市场设有直属分公司和产品展示展销窗口门市部专卖店及代理分销商,已在全国范围内建成强大统一的供 货和代理分销网络。 我们专业代理经销、开发生产电子元器件、集成电路、传感器、微波光电元器件、工 控机/DOC/DOM电子盘、专用电路、单片机开发、MCU/DSP/ARM/FPGA软件硬件、二极管、三极管、模 块等,是您可靠的一站式现货配套供应商、方案提供商、部件功能模块开发配套商。专业以现代信息产业 (计算机、通讯及传感器)三大支柱之一的传感器为主营业务,专业经营各类传感器的代理、销售生产、 网络信息、科技图书资料及配套产品设计、工程开发。我们的专业网站——中国传感器科技信息网(全球 传感器数据库)www.SENSOR-IC.COM 服务于全球高科技生产商及贸易商,为企业科技产品开发提供技 术交流平台。欢迎各厂商互通有无、交换信息、交换链接、发布寻求代理信息。欢迎国外高科技传感器、 变送器、执行器、自动控制产品厂商介绍产品到 中国,共同开拓市场。本网站是关于各种传感器-变送器-仪器仪表及工业自动化大型专业网站,深入到工业控制、系统工程计 测计量、自动化、安防报警、消费电 子等众多领域, 把最新的传感器-变送器-仪器仪表买卖信息, 最新技术供求, 最新采购商, 行业动态, 发展方 向,最新的技术应用和市场资讯及时的传递给广大科技开发、科学研究、产品设计人员。本网站已成功为 石油、化工、电力、医药、生物、航空、航天、国防、能源、冶金、电子、工业、农业、交通、汽车、矿 山、煤炭、纺织、信息、通信、IT、安防、环保、印刷、科研、气象、仪器仪表等领域从事科学研究、产 品设计、开发、生产制造的科技人员、管理人员 、和采购人员提供满意服务。 我公司专业开发生产、代 理、经销、销售各种传感器、变送器、敏感元器件、开关、执行器、仪器仪表、自动化控制系统: 专门从 事设计、生产、销售各种传感器、变送器、各种测控仪表、热工仪表、现场控制器、计算机控制系统、数 据采集系统、各类环境监控系统、专用控制系统应用软件以及嵌入式系统开发及应用等工作。如热敏电阻、 压敏电阻、温度传感器、温度变送器、湿度传感器、 湿度变送器、气体传感器、 气体变送器、压力传感 器、 压力变送、称重传感器、物(液)位传感器、物(液)位变送器、流量传感器、 流量变送器、电流 (压) 传感器、溶氧传感器、霍尔传感器 、图像传感器、超声波传感器、位移传感器、速度传感器、加速 度传感器、扭距传感器、红外传感器、紫外传感器、 火焰传感器、激光传感器、振动传感器、轴角传感器、 光电传感器、接近传感器、干簧管传感器、继电器传感器、微型电泵、磁敏(阻)传感器 、压力开关、接 近开关、光电开关、色标传感器、光纤传感器、齿轮测速传感器、 时间继电器、计数器、计米器、温控仪、 固态继电器、调压模块、电磁铁、电压表、电流表等特殊传感器。 同时承接传感器应用电路、产品设计 和自动化工程项目。

## 更多产品请看本公司产品专用销售网站:

商斯达中国传感器科技信息网: http://www.sensor-ic.com/

商斯达工控安防网: http://www.pc-ps.net/

商斯达电子 元器件网: http://www.sunstare.com/

商斯达微波光电产品网:HTTP://www.rfoe.net/

商斯达消费电子产品网://www.icasic.com/

商斯达军工产品网:http://www.junpinic.com/

商斯达实业科技产品网://www.sunstars.cn/传感器销售热线:

地址:深圳市福田区福华路福庆街鸿图大厦 1602 室

电话: 0755-83607652 83376489 83376549 83370250 83370251 82500323

传真: 0755-83376182 (0) 13902971329 MSN: SUNS8888@hotmail.com

邮编: 518033 E-mail:szss20@163.com QQ: 195847376

深圳赛格展销部: 深圳华强北路赛格电子市场 2583 号 电话: 0755-83665529 25059422

技术支持: 0755-83394033 13501568376

欢迎索取免费详细资料、设计指南和光盘 ; 产品凡多,未能尽录,欢迎来电查询。

北京分公司:北京海淀区知春路 132 号中发电子大厦 3097 号

TEL: 010-81159046 82615020 13501189838 FAX: 010-62543996

上海分公司: 上海市北京东路 668 号上海賽格电子市场 D125 号

TEL: 021-28311762 56703037 13701955389 FAX: 021-56703037

西安分公司: 西安高新开发区 20 所(中国电子科技集团导航技术研究所)

西安劳动南路 88 号电子商城二楼 D23 号

TEL: 029-81022619 13072977981 FAX:029-88789382