#### **General Description**

SENS

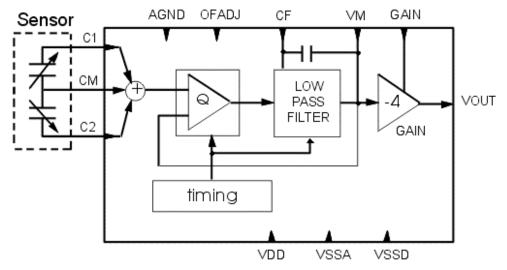

The CS2001 is a CMOS circuit designed to interface with capacitive-type sensors, such as pressure sensors, accelerometers, capacitive microphones and humidity sensors. The interface circuit is compact and easy-to-use since no external components are needed for a default setting of parameters. The low-noise low-drift design enables high precision measurements from DC up to the kHz range.

A high maximum sensitivity of 200 mV/pF can be obtained using a sensor with two nominal capacitances of 25 pF. The circuit is based on a charge compensation feedback loop. This approach guarantees a linear and low-drift transfer between a differential capacitance at the input and the analog output voltage.

For sensors with only one varying capacitance, an additional fixed capacitance with an equal nominal value can be used to form a quasi-differential sensor.

The gain and offset adjustment can be used for adjustment of the sensors sensitivity and offset.

### **Key Product Features**

- Maximum sensitivity of 200 mV/pF

- Linear response to differential capacitances

- Designed for low drift & low noise

- Gain and offset adjustment possibility Dual ±2.5 Volts or single 5 Volts power supply Low power consumption (17 mW max at 5 Volts)

- Frequency bandwidth DC to 17 kHz .

- Output load on analog output: 50 pF and/or  $10k\Omega$

- Available in SO16 or dice

**REV 3.0**

1

## **Typical Applications**

A typical application of the CS2001 circuit is interfacing a sensor which is composed of two active capacitances which vary in a differential way.

### **Electrical Characteristics**

(VSS=VSSA=VSSD, VDD-VSS=5V, Temperature = -40.85  $^{\circ}$ C, Cl = C2 = 50 pF unless otherwise stated)

| Characteristic                           | Min   | Тур  | Max   | Unit     |

|------------------------------------------|-------|------|-------|----------|

| Sensor capacitances total value (Cl±C2)  | 24    |      | 110   | pF       |

| Maximum capacitances relative difference |       |      | ±15   | %        |

| (CC2)/(C1 + C2)                          |       |      |       |          |

| VOUT output dynamic range, measured with |       |      | ±15   | %        |

| respect to AGND                          |       |      |       |          |

| Gain(without trimming)                   | -3.75 | -4   | -4.25 |          |

| Offset voltage in VOUT, measured with    |       |      | ±50   | mV       |

| respect to GND. (without trimming)       |       |      |       |          |

| Offset drift at VOUT output              |       | ±100 | ±150  | uV/℃     |

| White noise spectral density at VOUT,    |       | -133 | -110  | dBV/~/Hz |

| (decoupled supplies)                     |       |      |       |          |

| Flicker noise spectral density at VOUT,  |       |      | -125  | dBV√Hz   |

| measure at 1kHz (decoupled supplies)     |       |      |       |          |

| Slope of flicker noise                   |       |      | -0.69 |          |

| THD measured at VOUT (VOUT=2Vp,          |       |      | -57   | dB       |

| f<10kHz)                                 |       |      |       |          |

| External Cfext capacitance value         | 0     |      | 3     | pF       |

| External resistive load on VOUT          | 10    |      |       | kΩ       |

| External capacitive load on VOUT         |       |      | 50    | Pf       |

| Startup time                             |       | 50   | 70    | ms       |

## **Operating Information**

#### Voltage output

The CS2001 interface circuit is a stand-alone IC, and converts the difference of two capacitances, relative to their sum, into an analog voltage. The ideal DC relationship between the input and output variables is:

| where. |                                                             |

|--------|-------------------------------------------------------------|

| VOUT   | is the output voltage, measured relative to AGND,           |

| C1, C2 | are the associated capacitances of the connected sensor.    |

| Vo     | is half the supply voltage: 0.5(VDD-VSSA), typically 2.5 V. |

|        |                                                             |

REV 3.0

1

#### **Bandwidth control**

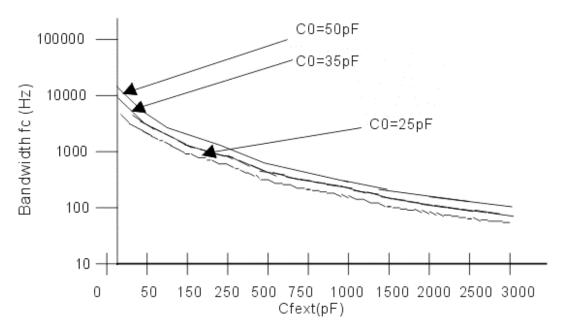

The transfer function of the circuit can be characterised as a first order low pass filter. The bandwidth of the equivalent filter may be programmed by inserting an optional external capacitance Cfext between pin VM and pin CF.

Fig.2: Bandwidth in function of external capacitance

An exact value for the bandwidth fc (Hz) can be calculated from the following equation:

$fc=fs/{3.14*2.77*[(37+Cfext/C0)-1]}$

where:

Cfext is the optional external capacitance between pin CF and VM. The value is to be given in pF.

C0 is the nominal capacitance value of the connected sensor. We suppose that C0=C1=C2. The value is to be given in pF.

**REV 3.0**

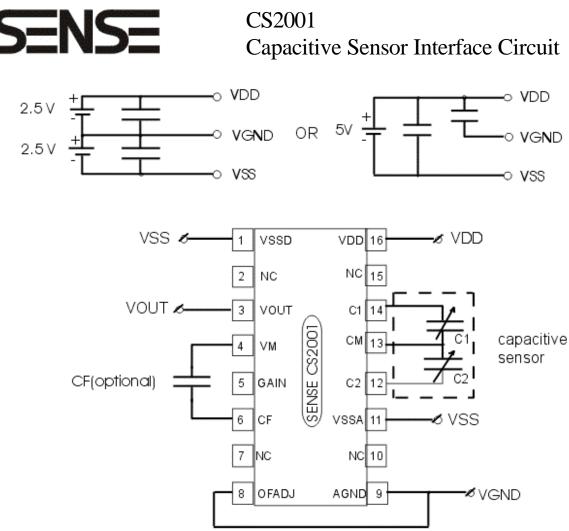

## Pin Description S016 package

| Pin       | Name  | Description                                                                          |

|-----------|-------|--------------------------------------------------------------------------------------|

| 1         | VSSD  | Digital negative supply voltage                                                      |

| 4         | VOUT  | Output of the interface circuit after gain stage                                     |

| 5         | VM    | Unbuffered output of the charge compensation loop                                    |

| 6         | GAIN  | Gain adjustment                                                                      |

| 7         | CF    | A capacitance Cfext for bandwidth adjustment may be connected between pins CF and VM |

| 8         | OFADJ | Offset adjustment or connected to AGND                                               |

| 9         | AGND  | Internally generated GROUND signal (Rint = $3kQ$ ).                                  |

|           |       | Its value is 0.5(VDD±VSSA)                                                           |

| 10        | VSSA  | Analog negative supply voltage                                                       |

| 11        | C2    | To be connected to the lower sensor electrode                                        |

| 12        | СМ    | To be connected to the common sensor electrode                                       |

| 13        | C1    | To be connected to the upper sensor electrode                                        |

| 16        | VDD   | Positive supply voltage                                                              |

| 2,3,14,15 | NC    | Not connected                                                                        |

### **Operating conditions**

#### VSS = VSSA=VSSD

| Parameter                  | Min | Тур | Max | Unit |

|----------------------------|-----|-----|-----|------|

| Supply Voltage (VDD - VSS) | 4.5 | 5.0 | 5.5 | V    |

| Operating temperature      | -40 | 27  | 85  | C    |

| Power supply current       |     | 2.8 | 3.5 | mA   |

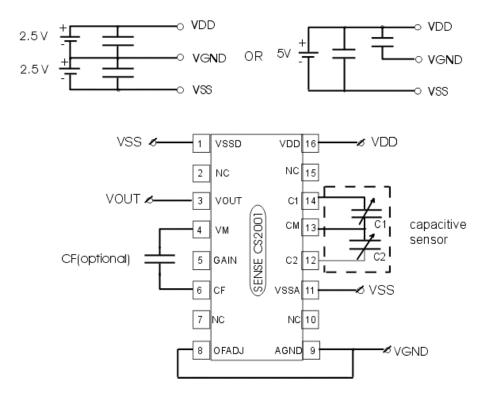

### **Typical Application**

A typical application of the CS2001 circuit is interfacing a sensor which is composed of two active capacitances which vary in a differential way.

The figure shows the simple connection of the circuit, with the optional Cfext. The supply voltages can be taken from a single 5 Volt source or two 2.5 Volt sources. OFADJ must be connected to AGND when the offset adjustment option is not used. VOUT must be measured with respect to AGND.

**REV 3.0**

Fig. 3: Typical Connections of CS2001 circuit without adjustment

#### Gain and Offser Adjustment

#### **Offset adjustment**

The offset of sensor and circuit can be adjusted by applying a voltage to pin "OFADJ'. The voltage can typically take values between 0 and  $\pm 1$  Volt (with respect to VGND). The gain VOFFSET/VOFADJ varies from 1 (C1 and C2 min) to 0.5 (Cl and C2 max). A simple way to generate this voltage is using a variable resistor connected between VDD and VSS. During testing, a programmable voltage source referenced to VGND can be used. if the offset correction is not used, pin 'OFADJ' must be connected to VGND.

#### Gain adjustment

The pin VM gives the **unbuffered** output voltage of the charge compensation loop:  $C_{1}^{1}C_{2}^{2}$

$$VM = 0.5.(VDD-VSS).$$

------

$C1+C2$

5 08/07/99

**REV 3.0**

The default gain factor of -4 (inverting amplifier) between the output VM and VOUT can be modified by connecting resistors R1 and R2 in parallel with integrated resistors 4\*Rint and Rint, respectively (Rint = 14 kQ), see Fig. 4 below. if the nominal gain factor is denoted by GNOM, then the modified gain, GMOD factor can be

if the nominal gain factor is denoted by GNOM, then the modified gain, GMOD factor can be found as:

$$G_{MOD} = G_{NOM} \quad \frac{1+\alpha_2}{1+\alpha_1} \quad \frac{\beta+1+\alpha_1}{\beta+1+\alpha_2}$$

$$G_{NOM} \quad 1+\frac{\beta}{\beta+1}\alpha_2 - \frac{\beta}{\beta+1}\alpha_1$$

where:

$\alpha 1$  is the relative change in R1; R1= 4R(1+ $\alpha_1$ ),

$\alpha 2$  is the relative change in R2; P2 = R(1+ $\alpha_2$ ),

R is the nominal value of the external resistor R2,

$\beta$  is the ratio between the internal resistor value Rint (14 kQ) and the nominal external resistor value R.

The precision obtained depends on the precision of tuning R1 and/or P2. The maximum values for  $\alpha 1$  and  $\alpha 2$ . are  $\pm 10$ %. Typical value could be 5.6 k $\Omega \pm 10$ % for R1 and 1.4 k $\Omega \pm 10$ % for R2 ( $\beta$ = 10). This feature is mainly used for adjustment of the gain of a module containing a sensor and the CS2001 circuit.

Fig. 4: Connection of CS2001 with gain and offset adjustment

6

**REV 3.0**