# XL-1 Series 64, 128, and 256 Channel Variable-Gain CMOS Buffered Multiplexers

#### **Overview**

The XL-1 series buffered multiplexers offer a versatile solution to the increasing demand for low noise amplification and multiplexing. They are designed to interface with linear photosensitive arrays, such as those made of indium gallium arsenide, germanium, amorphous silicon, or any of several special-purpose infrared-sensitive materials. Each

Caution: While the XL-1 Multiplexers have been designed to resist electrostatic discharge (ESD), they can be damaged from such discharges. Always observe proper ESD precautions when handling and storing these devices. channel of the multiplexer channel consists of a charge amplifier in series with two separate buffered sample-andhold paths for correlated double sampling (CDS). A broad range of electrically-selectable integrating capacitors provide accommodation for charge packets from a wide range of sensor materials, pixel sizes, and exposure levels.

#### **Features**

- > 64, 128, or 256 active channels

- 100 µm channel pitch

- Selectable integrating capacitor

- > Dynamic range greater than 90 dB

- > Charge conversion 10 to 160 nV/e-

- Video output frequency 1.0 MHz

- > Low input noise leakage current

- Single clock output operation

- > Built-in correlated double sampling

- > Bi-directional readout capability

#### www.excelitas.com

#### **Buffered Multiplexers**

#### **Functional Description**

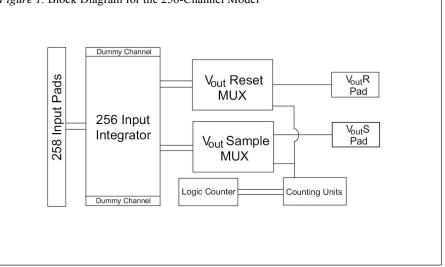

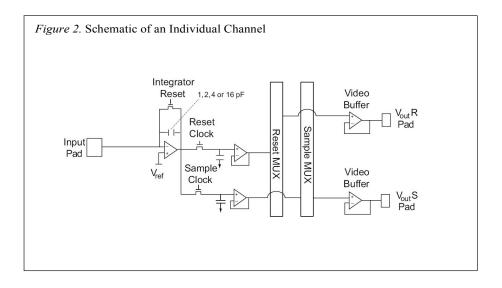

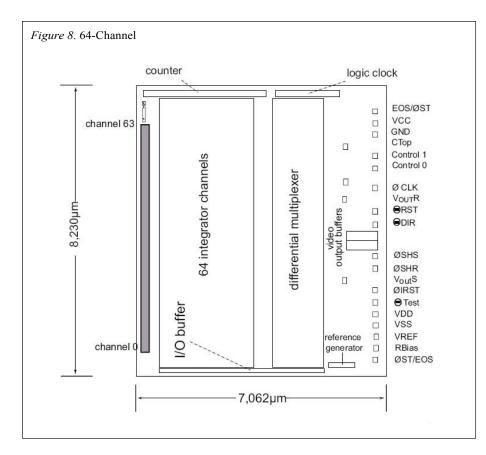

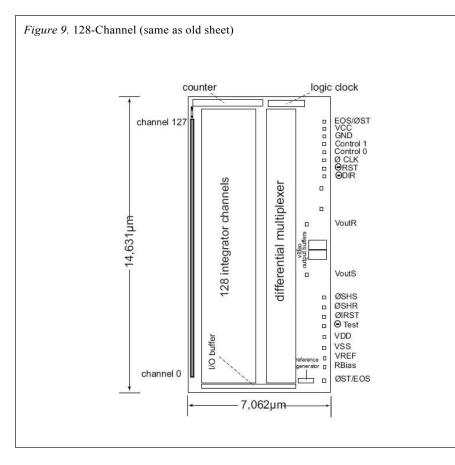

Each XL-1 series multiplexer consists of the 64, 128, or 256 channels. In addition, the 256channel model includes a dummy channel placed on either end of the array to prevent edge non-uniformity effects common in long multiplexers. An on-chip decoder supports readout of the device at any speed up to 1MHz. Data into the decoder and at output pads is buffered for direct readings with low signal degradation. The dual sample-and-hold video outputs support correlated double sampling (CDS). An on-chip counter operates the readout with one master clock signal. Figure 1 shows a block diagram for the 256-channel type. Figure 2 displays a schematic for an individual channel.

Each channel of the multiplexer consists of a charge amplifier in series with two separate buffered paths for CDS. The charge amplifier converts incoming electrons into a voltage that can be stored in either the Reset or Sample path. External clocks,  $Ø_{SHR}$  and  $Ø_{SHS}$  respectively, control access to the reset and sample paths of the CDS. Since these paths are identical, the timing is accurately matched. Inside each path of the CDS is an amplifier set up in a unity gain buffer configuration. This will record the voltage value seen at the output of the charge amplifier an store it until the corresponding decoder path reads it out. The decoders are controlled simultaneously by a start pulse  $(Ø_{ST})$  and a master clock signal  $(\mathcal{O}_{\text{CLK}})$  supplied externally to the multiplexer. Once the decoder is activated, the stored values are read sequentially in one direction until all channels have been accessed.

| Table 1a. Integration Capacitance Selection and Value |           |                     |                     |  |

|-------------------------------------------------------|-----------|---------------------|---------------------|--|

| Control 0                                             | Control 1 | C <sub>i</sub> (pF) | Conversion (nV/e -) |  |

| 0                                                     | 0         | 1                   | 160                 |  |

| 1                                                     | 0         | 2                   | 80                  |  |

| 0                                                     | 1         | 4                   | 40                  |  |

| 1                                                     | 1         | 16                  | 10                  |  |

Upon completion of the readout, the device will generate a digital end-of-scan signal, EOS. This signal can be used as the start pulse for a second multiplexer to facilitate sequential readout of several multiplexer devices placed endto-end on a long imager.

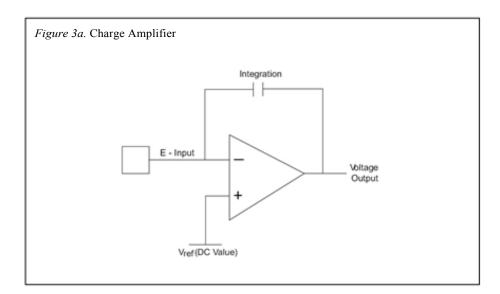

# **Charge Amplifier**

The charge amplifier in each channel converts incoming electrons into a corresponding voltage value based on the sensitivity of the amplifier and its corresponding capacitance value. For this device, the sensitivity is determined by the integration capacitance value (C<sub>i</sub>) selected (1, 2, 4, or 16 pf), as shown in *Table 1A*.

The general equation that governs this effect is:

[charge x sensitivity = voltage]

Therefore, the output will be:

$V_{out} = [V_{ref} - (\# of electrons x sensitivity per electron)]$

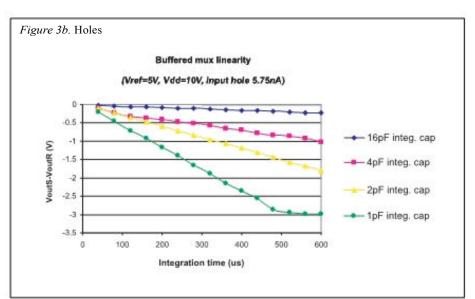

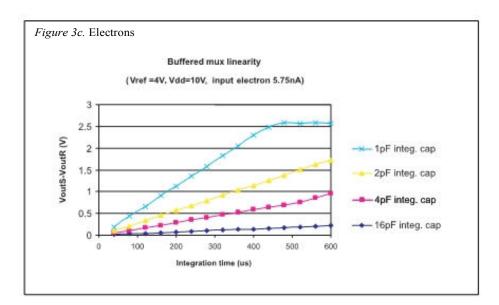

This equation is only valid if  $V_{ref}$  (corresponding reference value) allows the amplifier to operate within its linear region. A generalized schematic for this amplifier configuration is shown in *Figure 3a*. *Figure 3b* and *Figure 3c* show the  $V_{out}$ versus integration time at different gains as the charge amplifier receives incoming holes and electrons, respectively.

The sensitivity of the charge amplifier may be selected from one of four values through two binary control inputs. Integrating capacitors of the 1, 2, 4, and 16 pf provide sensitivities of 0.16, 0.08, 0.04, and 0.01  $\mu$ V/e- respectively.

#### Sample and Hold

After the charge has been integrated into a voltage value, the output can then be stored in one of the two sample-and-hold paths for each channel. There are two sample-andhold paths present to perform offchip CDS operations on the output signal and to improve the dynamic range of the device.

# **Dual Decoders**

To place all of these separate voltage values on two different output pads, two decoders are positioned after all of the sample-and-hold paths. The decoder control is done on the chip. The decoder is controlled by two clocks,  $Ø_{ST}$  and  $Ø_{CLK}$ . Triggering  $Ø_{ST}$  from low to high will signal the control logic to begin monitoring the  $Ø_{CLK}$ . Signal. At each rising edge of the  $Ø_{CLK}$  signal, the control logic will pass the sample-and-hold voltage value to the corresponding output pad.

# Video Buffer

A video buffer follows the decoder and reads out all channels sequentially at a high speed. For this purpose, the video buffer has a high slew rate and low output impedance.

# Timing

There are eight different control clocks that must be synchronized with one another to operate the XL-1 series multiplexers. At power-up and in-between data samples, the multiplexer timing must be reset. To accomplish this, the first signal,  $\mathcal{O}_{RST}$ , is brought from high to low for at least one clock cycle. This transition resets the counter inside the device so the decoders will always begin clocking at the beginning of the multiplexer.

#### **Data Sampling**

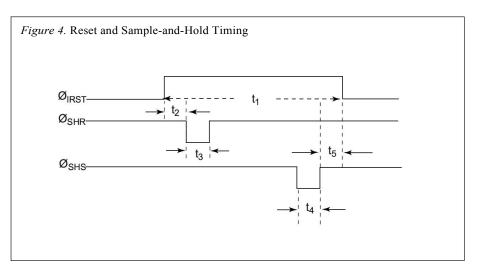

Three signals,  $\emptyset_{SHR}$ ,  $\vartheta_{SHS}$ , and  $\vartheta_{IRST}$  work together to take valid data samples.  $\vartheta_{IRST}$  controls the integration mode. When  $\vartheta_{IRST}$  is high, the amplifier will begin to integrate charge.  $\vartheta_{SHR}$  activates one of the two sample-and-hold paths to pass the output voltage on the charge amplifier. Similarly,  $\vartheta_{SHS}$  activates the second path. *Figure 4* and *Table 1b* show the above clocks on a common time base.

If t1 is too small, there will be insufficient time for integration. If t1 is too large, the integrator will integrate part of the offset as well. Intervals t2 and t5 correspond to the difference in time between  $Ø_{IRST}$  high and  $Ø_{SHR}$  or  $Ø_{SHS}$  low, respectively. Intervals t3 and t4 correspond to the time required for sample-and-hold to settle onto a voltage. For a one-bit output value, one clock cycle is adequate. However, for high-resolution DACs, sufficient time must be allowed for required settling accuracy.

| Table 1b. Data Sample Timing Limits |                        |                 |  |  |

|-------------------------------------|------------------------|-----------------|--|--|

| Time                                | Description            | Minimums        |  |  |

| t1                                  | Total integration time | -               |  |  |

| t2                                  | Reset clock offset     | 1/2 Clock cycle |  |  |

| t3                                  | Reset clock time       | 1 Clock         |  |  |

| t4                                  | Sample clock time      | 1 Clock         |  |  |

| t5                                  | Sample clock offset    | 1/2 Clock cycle |  |  |

# **Output Data Readout**

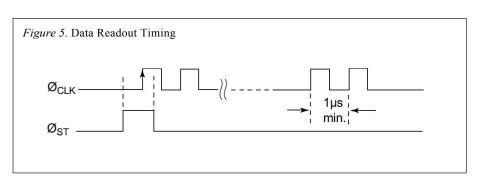

*Figure 5* shows the clock timing for the data readout. A rising edge of the master clock ( $\emptyset_{CLK}$ ) samples the  $\emptyset_{ST}$  signal and begins the readout process. At each rising edge the decoder will send the next sequential channel to the output.  $\emptyset_{CLK}$  increments the counter inside the control logic and allows it to send the next channel value to the output video buffer.

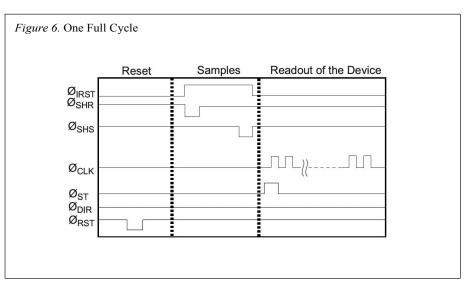

# **Complete Cycle**

*Figure 6* displays one complete process.

#### **Readout Direction Control**

$Ø_{\text{DIR}}$  controls the direction of the device readout. If  $Ø_{\text{DIR}}$  is clocked high, then the multiplexer will clock out data from channel 0 to channel N+1 sequentially, and the start pulse should be sent into the pad marked  $Ø_{\text{ST}}$ /EOS. Conversely, if  $Ø_{\text{DIR}}$  is low, it clocks from channel N+1 to channel 0, and the start pulse must be sent to EOS/ $Ø_{\text{ST}}$ .  $Ø_{\text{DIR}}$  must not be used as a dynamic switch to reverse directions in the middle of a readout cycle.

#### **Electrical Description**

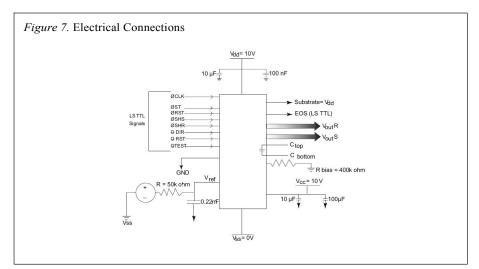

The XL-1 series multiplexers operate with standard power supplies for  $V_{DD} = 10$  VDC,  $V_{SS} = 0$  V, and  $V_{CC} = 10$ VDC. To minimize the noise, the analog and digital grounds are separated. The equivalent input noise is 8 mV rms. It can be calculated by using the following equation:

Input referred Noise = 2 (4/3 x KT x  $C_f/C_iC_L$ )+1/2

System Noise =  $2(8/3 \text{ x KT/q}_{e2}) + 1/2$ Where KT is constant at room temperature, and  $C_{f'}/C_iC_L$  are feedback, input and load capacitance,  $q_e$  is an electron charge. The bias pin is used to bias all analog components in the multiplexer. A 400 K ohm resistor is connected between the  $R_{BIAS}$  pad and  $V_{SS}$  for

reduction of noise current. *Figure 7* shows the electrical connections of the device.

5

## **Physical Description**

XL-1 series multiplexers are provided as sawed, tested die, and are packaged for protection from electrostatic discharge and handling damage. These die should be mounted on ceramic substrates and ball-bonded to the detector and the readout pins. Drawings showing the locations and sizes of bond pads are available in .dxf and .dwg formats from Excelitas.

Recommended bonding procedures are also available from Excelitas. Although these procedures are recommended, due to the high risk of damage attributed to improper handling, the devices are sold without warranty, regardless of bonding procedures.

The bond pad material is aluminum with 1% silicon flush with the top surface of the die suitable for aluminum or gold compression bonding. All die is  $0.675 \pm 0.020$  mm thick.

| Table 2. Specifications                                  |                 |      |                   |              |

|----------------------------------------------------------|-----------------|------|-------------------|--------------|

| Description                                              | Min             | Nom  | Max               | Units        |

| Saturation charge                                        | <b>2</b> .5⁵    |      | 40.5 <sup>6</sup> | рС           |

| Parasitic input capacitance (to Vss)                     |                 | 4.5  |                   | pF           |

| Input leakage current (per channel)                      |                 | ±100 | ±250              | fA           |

| Charge conversion                                        | 10 <sup>6</sup> |      | 160 <sup>5</sup>  | nV/e-        |

| Integration amplifier slew rate                          |                 | 1.0  |                   | V/µsec       |

| Output clocked video level (VREF= 5V)                    |                 |      |                   |              |

| Q: 0 to QSAT                                             | 3.0             | 2.5  | 1.5               | V            |

| Q: 0 to -QSAT                                            | 6.5             | 7.5  | 8.5               | V            |

| Output quiescent video level                             |                 | VREF |                   | V            |

| Output video impedance                                   |                 | 1.5  |                   | K ohm        |

| Output video readout frequency                           |                 |      | 1.0               | MHz          |

| VoutS output variation <sup>1</sup>                      |                 | 15   |                   | mV           |

| VoutR output variation <sup>1</sup>                      |                 | 15   |                   | mV           |

| Video output differential offset <sup>2</sup>            |                 | 40   |                   | mV           |

| Digital outputs (EOL signal) high level                  | 3.5             |      | 5.5               | V            |

| Digital outputs (EOL signal) low level                   | GND             |      | GND+0.3           | V            |

| Quiescent VDD current (IDD)                              |                 | 40   | 45                | mA           |

| Clocked VDD current                                      |                 | 50   | 55                | mA           |

| PSRR (@1kHz & 120 pF Cℕ) To V₅s                          |                 |      | -25               | dB           |

| PSRR (@1kHz & 120 pF Cℕ) To V₀₀                          |                 |      | -25               | dB           |

| Operating potential (V <sub>DD</sub> - V <sub>SS</sub> ) | 9.5             | 10   | 12.5              | V            |

| Reference potential                                      |                 | 5    | 7                 | V            |

| Digital input levels -high level                         | 3.5             | 5    | 5                 | V            |

| Digital Input levels - low level                         | GND             | GND  | 0.4               | V            |

| Bias resistor current                                    |                 | 16   |                   | μA           |

| Operating temperature range                              | 0               |      | 70                | °C           |

| Noise @25 pFC <sub>IN</sub> ³                            |                 |      |                   |              |

| Input referred noise                                     |                 | 5    |                   | μVms         |

|                                                          |                 | 29   | rn                | ns electrons |

| System noise                                             |                 | 70   |                   | µVms         |

|                                                          |                 | 450  | rn                | ns electrons |

| Dynamic range <sup>4</sup>                               | 90              |      |                   | dB           |

Notes:

<sup>1</sup> Output Variation is (max signal-min signal) at zero input charge.

<sup>2</sup> Peak-to-peak signal mismatch (Vout<sub>s</sub> - Vout<sub>r</sub>)at zero input charge.

<sup>3</sup> Noise with 1pF integrating capacitor.

<sup>4</sup> Dynamic range defined as the Max Output/Noise Floor.

<sup>5</sup> Integrating capacitor is 1 pF.

<sup>6</sup> Integrating capacitor is 16 pF.

| Name                | Function                          | Nom. Voltages |  |

|---------------------|-----------------------------------|---------------|--|

| Øtest               | Reserved                          | 0V            |  |

| Ørst                | Integrator reset control          | 0 - 5 V       |  |

| Øshr                | S&H reset control                 | 0 - 5 V       |  |

| Øsнs                | S&H sample control                | 0 - 5 V       |  |

| Vcc                 | Digital positive supply           | 10 V          |  |

| GND                 | Digital ground                    | 0 V           |  |

| VoutS               | Output video sample level         | -             |  |

| VoutR               | Output video reset level          | -             |  |

| Vss                 | Analog ground                     | 0 V           |  |

| Vdd                 | Analog positive supply, substrate | 10 V          |  |

| Ødir                | Bidirectionality control          | 0 - 5 V       |  |

| Ørst                | Counter reset control             | 0 - 5 V       |  |

| Øclk                | Master clock signal               | 0 - 5 V       |  |

| Control 0           | Control 0 for the selectable gain | 0 - 5 V       |  |

| Control 1           | Control 1 for the selectable gain | 0 - 5 V       |  |

| EOS/Ø <sub>ST</sub> | EOS signal/start pulse            | 0 - 5 V       |  |

| INPUTn              | Input to mux channel n            | -             |  |

| Øst/EOS             | Start pulse/EOS signal            | 0 - 5 V       |  |

| R <sub>bias</sub>   | Bias resistor to Vss              | Note 1        |  |

| VREF                | Electrons (Q: 0 to -Qsat)         | 4 V           |  |

|                     | Holes (Q: 0 to Qsat)              | 5 V           |  |

Note 1: Connect through 400 K ohm to GND.

| Table 4. Product Numbers |               |               |               |

|--------------------------|---------------|---------------|---------------|

| Channels                 | 64            | 128           | 256           |

| Sawed and Tested Die     | XL1064CAD-711 | XL1128CAD-711 | XL1256CAD-711 |

#### **No Warranty**

Due to the high risk of damage attributed to improper handling, all XL-1 devices are sold without warranty. Potential users should

discuss proper handling procedures with Excelitas before using these devices. For more information, email us at generalinquiries@excelitas.com or visit our website at www. excelitas.com.

Worldwide Headquarters Excelitas Technologies 44370 Christy Street Fremont, CA 94538 USA Telephone: (+1) 510-979-6500 Toll Free (N. America): (800) 775-OPTO (6786) Fax: (+1) 510-687-1140 generalinquiries@excelitas.com European Headquarters Excelitas Technologies Wenzel-Jaksch-Str. 31 D-65199 Wiesbaden, Germany Telephone: (+49) 611-492-430 Fax: (+49) 611-492-165 Asia Headquarters Excelitas Technologies 47 Ayer Rajah Crescent #06-12 Singapore 139947 Telephone: (+65) 6775-2022 Fax: (+65) 6775-1008

For a complete listing of our global offices, visit www.excelitas.com

©2011 Excelitas Technologies Corp. All rights reserved. The Excelitas logo and design are registered trademarks of Excelitas Technologies Corp. XL-1 Series is a trademark of Excelitas Technologies Corp. or its subsidiaries, in the United States and other countries. All other trademarks not owned by Excelitas Technologies Corp. or its subsidiaries that are depicted herein are the property of their respective owners. Excelitas reserves the right to change this document at any time without notice and disclaims liability for editorial, pictorial or typographical errors.