Agilent Technologies Innovating the HP Way

## Designing with the HCPL-4100 and HCPL-4200 Current Loop Optocouplers

## **Application Note 1018**

### Preface

Agilent Technologies produces a comprehensive line of optocouplers which address different speed and current gain requirements for isolation interface circuits. New Agilent optocoupler products build on the established base of optocoupler technology and expand with additional features that make optocouplers easier to use in special applications. The HCPL-4100 (transmitter) and the HCPL-4200 (receiver) optocouplers include specialized circuits for 20 mA digital current loop applications. These optocouplers are designed to easily interface TTL, LSTTL, and CMOS logic systems to current loop systems. An external current source is needed to complete the current loop system.

This application note will assist the circuit design engineer to achieve maximum performance from Agilent Technologies HCPL-4100 and HCPL-4200 current loop optocouplers. Practical applications for interfacing to and from a current loop will be shown. In addition, overall current loop system aspects and current source designs will be discussed. Potential applications of current loops, configurations, types of current sources, and inherent tradeoffs between data rate and length of wire line are covered.

#### Introduction

Data transmission between electronic equipment, which are physically separated by distances of more than a few feet, can be accomplished in many ways. Wire links, microwave links, and fiber optic links are among the most common means. Each technology has inherent trade-offs in data rate, error rate, simplicity of use, reliability and cost. Of the wire techniques, a signal can be transmitted as a voltage signal or a current signal. Many popular industry standards exist for voltage signal transmission, such as RS-232-C, RS-422, RS-423 (serial data transmission), or IEEE-488 (parallel data transmission), etc. When compared to these voltage signal techniques, a current signal or current loop can provide an excellent alternative.

First, some basic definitions are in order. A current loop is a loop which carries a current, generally 20 mA or 60 mA, between electronic equipment via a twisted pair of wires. The loop can be opened and closed by a transmitter within equipment connected to the loop. These interruptions of current are sensed by other equipment connected to the current loop (receiver). The convention used in this application note for a MARK, or logic 1, corresponds to a presence of loop current, e.g., 20 mA. A SPACE, or logic 0, corresponds to an absence of loop current, e.g., 0 mA. A current loop transmitter or receiver can be either of two types: active (source) or passive (sink). An active transmitter supplies current to the loop. Any receivers or other transmitters within that loop must then be passive units which accept the supplied loop current. Alternatively, an active receiver supplies current to passive transmitters or other passive receivers in the current loop.

Current sources used within a current loop vary in complexity. The simplest current source is a resistor and voltage source. More complex current sources will contain active elements or special integrated circuits to provide constant current under various power supply and load conditions. The compliance voltage of a current source is a term which is used to indicate at what level the current decreases to zero.

There are no widely accepted industry standards for current loops, only accepted conventions. Common digital current loops are 0-20 mA and 0-60 mA, while the analog current loop is 4-20 mA. These levels were originally associated with digital teleprinter equipment and analog industrial sensors such as thermocouples, strain gauges, etc. The HCPL-4100 and HCPL-4200 optocouplers address only the 20 mA digital current loop applications.

## Basic Advantages of Current Loops

In voltage based transmission lines, a voltage signal attenuates over distance. A current loop design ensures constant current through the loop resulting in no signal attenuation. Noise immunity is higher with current loop systems. A constant current maintains a high signal-to-coupled noise ratio. The voltage signal attenuation reduces this ratio.

Even with expensive, low capacitance cable, RS-232-C wire communication over distances greater than 60 m (200 ft.) at 20 kBd is impractical. RS-232-C wire distances are severely limited when compared to current loop distances at the same operating data rate. Current loop systems employ inexpensive twisted pair wire cable. Serial data transmission is accomplished by a simple twowire arrangement. Multiple stations can be connected in series provided sufficient compliance voltage is available. Unlike voltage techniques, if a fault should open the loop, permanent loop current disruption could be sensed.

Optocouplers can be used in current loops to provide optical isolation of the logic circuits from the current loop circuit. This optical isolation prevents ground potential differences or common mode influences from affecting the current loop performance. Optocoupler construction and sophisticated integrated circuit processing achieve excellent common mode rejection (10 kV/ µs). Electrical independence between input and output circuits of an optocoupler permit different reference grounds on either side of the interface.

The maximum data rate of a 20 mA current loop system is determined by the characteristics of the transmitter and receiver and the length and characteristics of the transmission line. For short transmission lines, less than 40 m (131 ft.), the maximum data rate is approximately 120 kBd for the HCPL-4100 and approximately 4.5 MBd for the HCPL-4200.

The small eight pin dual-in-line plastic package results in a savings of printed circuit board space. Standard automatic insertion equipment can be used.

The easy design and implementation of a 20 mA current loop using the HCPL-4100 and HCPL-4200 permits rapid design, fabrication, and testing.

## **Current Loop Applications**

Current loops are used because they offer communications link lengths up to 10 km, have high immunity to errors caused by noise, and are low cost. Previous 20 mA current loop designs were often limited to 5 or 10 kBd speeds even for short line lengths. Agilent Technologies 20 mA current loop transmitters and receivers are capable of 20 kBd at 400 metres.

In the industrial control industry, current loops are used when there is a need to communicate digital information. Because of the proliferation of the micro-processor and advances in digital circuitry and software, digital control of industrial processes is becoming widely accepted. Micro, mini, and mainframe computers are distributed throughout the factory and need to exchange information. The same considerations apply where distributed data processing equipment is used in a factory environment for inventory control or workflow monitoring. Agilent Technologies 20 mA current loops are a natural choice for noisy environments.

For these applications, 20 mA current loops are desirable because they are resistant to errors caused by noise, they eliminate ground loops, can be used in communications links up to 10 km long, are low cost, and can be easily installed. No other common communications system can equal these features.

## Agilent Technologies Current Loop Optocouplers General Design Considerations with Optocouplers

When ordinary optocouplers are used as the interface between logic systems and a current loop, and vice versa, careful design must be followed. The light emitting diode (LED) in a current loop receiver must be protected from current overstress. A threshold needs to be established with hysteresis in order to define the MARK and SPACE conditions and to avoid possible noise effects. The threshold circuit should be located prior to the optical isolation to

prevent the current transfer ratio (CTR) changes within an optocoupler over time from influencing established threshold levels. This input protection/ threshold circuit should be powered solely by the current loop to maintain isolation and reduce power supply requirements. The receiver output circuit should be simple to interface to TTL or CMOS systems. The total current loop receiver circuit needs to occupy minimal board space within loop station equipment. Of course, the design must have good speed performance in order to meet ever increasing speed requirements.

Similar considerations exist for current loop transmitter design. The transmitter will operate from either a TTL or CMOS input data signal. The output of the transmitter should be protected and buffered to handle the loop current and compliance voltage level of the current source. Output protection needs to be provided to ensure against miswired connection of the current loop to the transmitter terminals. The output circuit must be powered by the current loop source. If power failure occurs to the transmitter, the transmitter must remain ON in order to prevent obstruction of data on the current loop. Other subtle effects such as the type of current source and termination used will also influence speed performance of the loop.

These design considerations have been incorporated into the HCPL-4100 and HCPL-4200 to simplify the circuit designer's task.

#### Features Common to the HCPL-4100 (Transmitter) and the HCPL-4200 (Receiver)

The Agilent Technologies current loop optocoupler product family consists of two devices: a current loop transmitter (HCPL-4100) and a current loop receiver (HCPL-4200). Their unique characteristics will be explained by first discussing the features which are common to both devices; then particular characteristics of each device will be addressed.

Optical isolation is provided within each device to permit electrical independence of the logic systems from the current loop system. Electrical independence specifically means two concepts: 1. signal isolation capability between the two systems, 2. insulation capability between the two systems. Signal isolation is the ability of the device to reject common mode signal interference. The common mode rejection capability of both the HCPL-4100 and the HCPL-4200 is typically 10 kV/µs with a specified minimum of 1000 V/µs. The device insulation capability is the ability to withstand a transient potential difference stress between the two systems. The Withstand Test Voltage is 3 kV DC for five seconds.

Speed performance of each device has a typical propagation delay of  $0.2 /\mu s - 0.3 \ \mu s$  with a specified maximum of  $1.6 \ \mu s$  over  $0^{\circ}$ C to  $70^{\circ}$ C, excluding transmission line delay. Depending upon the location of the current source within a loop, data rates of 1.5 MBd for 250 metres loop length is achieved with the HCPL-4200 receiver. Up to 75 kBd for 100 metres of loop length with the HCPL-4100 transmitter is also achieved.

The transmitter input and receiver output are compatible with TTL, LSTTL and CMOS logic levels. Passive current loop switching or monitoring is performed by integrated circuits (ICs) within each device which are powered from an external 20 mA current source. No additional design for power supplies or buffer circuitry is needed for either unit. Current protection of up to  $\pm 30$  mA is provided in each optocoupler. Specific, simple current sources which can be used are explained in a subsequent section.

The HCPL-4100 20 mA current loop transmitter and HCPL-4200 20 mA current loop receiver incorporate these features in eight pin dual-in-line plastic packages. The eight pin dual-in-line package allows for automatic insertion capability and conserves printed circuit board space.

#### Features of the HCPL-4100 Transmitter

The output integrated circuit of the HCPL-4100 transmitter directly controls a recommended 20 mA loop current. The minimum breakdown voltage of this IC, which determines the upper compliance voltage limit of the current source, is 27 V DC. At a recommended loop current of 20 mA, the MARK state voltage drop across the output terminals is typically 2.35 V DC. The SPACE state current level is typically 1.1 mA (maximum 2 mA) which powers the output integrated circuit. Should power fail to the input IC of the HCPL-4100 transmitter, the output IC will remain in the MARK state. This important feature is needed in multidrop current loop applications. A minimum capacitive loading of 1000 pF is required for the output IC (loop side) of the transmitter.

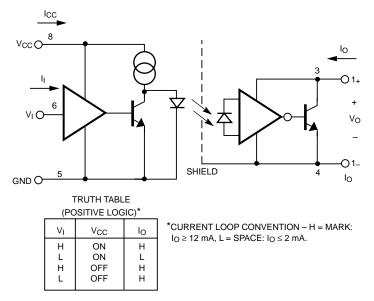

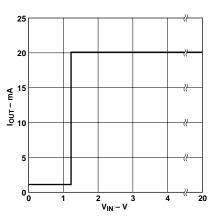

This guarantees stability of the IC under all possible load conditions. In general, an external 1000 pF capacitor can be omitted for twisted wire cable lengths greater than 30 metres (100 ft.). If there is any possibility of using a wire loop length less than 30 metres (100 ft.), the 1000 pF capacitor must be connected. Good engineering practice is to use a bypassing capacitor (0.1  $\mu$ F) from V<sub>CC</sub> to ground for the input IC of the transmitter. Data from directly connected TTL, LSTTL or CMOS units to the input of the HCPL-4100 transmitter will properly operate this device. A block diagram of the HCPL-4100 is given in Figure 1 and transfer characteristic is illustrated in Figure 2.

#### Features of the HCPL-4200 Receiver

The HCPL-4200 receiver input IC directly monitors the 20 mA loop current. Power for this IC is supplied by the current loop from the external current source. Loop current level detection is performed prior to the optical isolation.

Specified current thresholds are a minimum of 12 mA for MARK state and a maximum of 3 mA for SPACE state. The typical threshold for MARK state is 6.8 mA with 0.8 mA hysteresis. A guaranteed switching threshold level for loop current provides additional common mode and differential mode noise immunity, and prevents possible current transfer ratio (CTR) changes from affecting loop current threshold levels. At the recommended loop current of 20 mA, the MARK state voltage drop across the input terminals is typically 2.52 V DC.

Figure 1. Block Diagram and Truth Table for HCPL-4100 Optocoupler

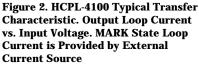

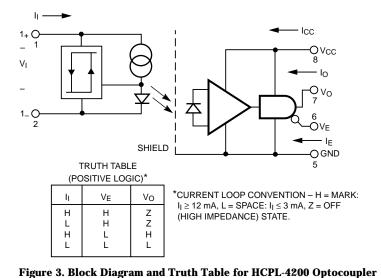

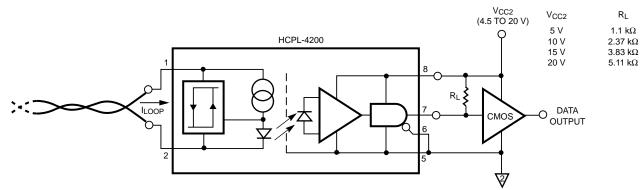

The output integrated circuit of the HCPL-4200 receiver can have a voltage output ( $V_O$ ) greater than the power supply voltage ( $V_{CC}$ ). The absolute maximum voltage level for  $V_O$  and  $V_{CC}$  is 20 V DC. A third state (high impedance) output enable feature is available for use with buss interface applications or special inhibit functions. The output will remain at a high impedance level (third state) if  $V_{CC}$  is zero volts. A block diagram of the HCPL-4200 is given in Figure 3 and the transfer characteristic is illustrated in Figure 4. Conventional TTL and LSTTL logic devices can be directly connected to the output of the HCPL-4200 unit. A standard CMOS interface for the HCPL-4200 receiver is given in Figure 5.

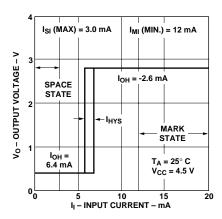

Figure 4. HCPL-4200 Typical Transfer Characteristic. Output Voltage vs. Input Loop Current

Figure 5. Recommended Interface from HCPL-4200 Receiver to CMOS Circuit

## Current Loop Configurations

Current loop configurations can be arranged in three basic ways: simplex, half duplex and full duplex. Two variations within each configuration can exist, i.e., point-to-point or multidrop connections. Definitions for these terms, recommended interface circuits, performance trade-offs and measured performance data will be discussed and illustrated within this section.

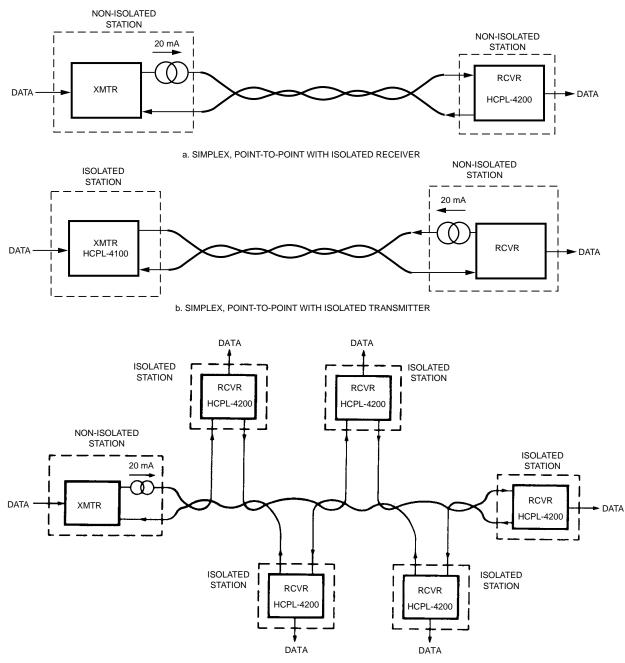

#### Simplex

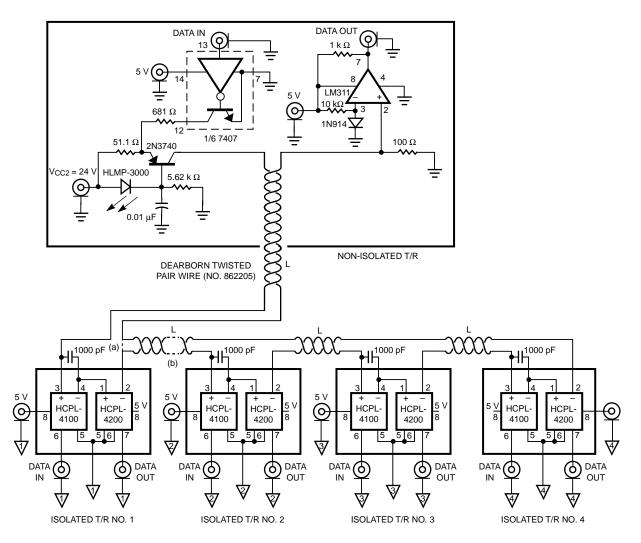

The most fundamental loop configuration is simplex pointto-point. The data flows in only one direction from the transmitter over the current loop to the remote receiver. This configuration is shown in Figures 6a and 6b. Figure 6a illustrates a non-isolated, active current loop transmitter used with an isolated HCPL-4200 receiver. Figure 6b shows an isolated HCPL-4100 current loop transmitter used with a nonisolated, active receiver. A possible point-to-point application is to use a 20 mA current loop for communication between a computer and remote printer. The simplex topology can be expanded from point-to-point to multidrop. In a multidrop system, a number of receivers are in series on the loop which contains only one transmitter as illustrated in Figure

6c. A configuration with multiple transmitters and one receiver is possible as well. However, the priority of the operating transmitter must be established in that case.

Undesired ground loops are eliminated and common mode rejection is increased by providing electrical isolation of the current loop. This isolation can be provided at either the receiver or transmitter end of the loop as illustrated in Figures 6a and 6b respectively. The opposite end need not be isolated. The non-isolated unit will supply the current (active) for this simplex configuration. A circuit diagram of a non-isolated,

c. SIMPLEX, MULTIDROP WITH ISOLATED RECEIVERS

## Figure 6. Simplex Current Loop Configurations: Point-to-Point with Current Source Located at: a. Transmitter, b. Receiver, c. Multidrop

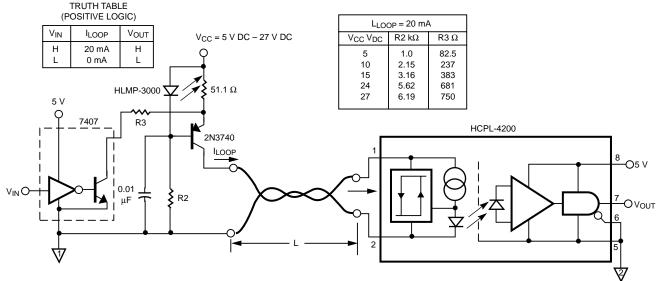

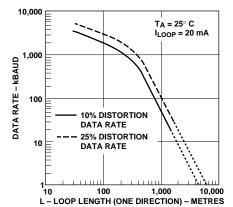

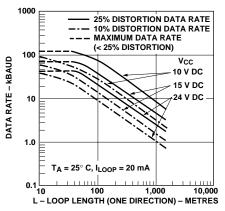

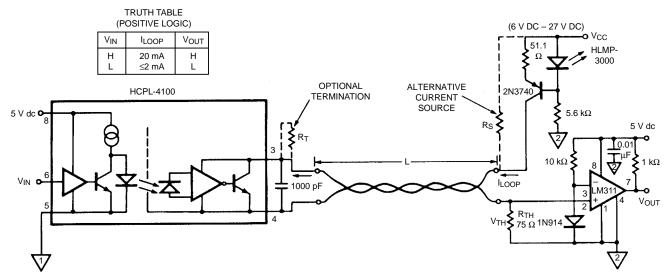

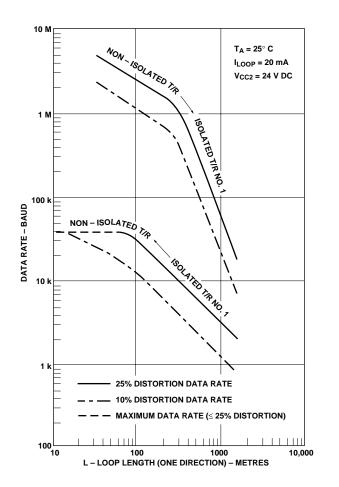

active transmitter connected to the HCPL-4200 receiver (Figure 6a) is given in Figure 7. The data rate performance versus the length of the current loop for this circuit is given in Figure 8.

The circuit for the alternate simplex arrangement of a nonisolated, active receiver connected to the HCPL-4100 transmitter is given in Figure 9. The trade-off of data rate versus loop length and compliance voltage is illustrated in Figure 10.

Comparing the data rate performance for each circuit shows that the active, non-isolated transmitter

Figure 7. Recommended Non-Isolated Active Transmitter with HCPL-4200 Isolated Receiver for Simplex Point-to-Point 20 mA Current Loop

Figure 8. Typical Data Rate vs. Distance for Circuit of Figure 7

Figure 10. Typical Data Rate vs. Distance and Supply Voltage for Circuit of Figure 9

Figure 9. Recommended Non-Isolated Active Receiver with HCPL-4100 Isolated Transmitter for Simplex Point-to-Point 20 mA Current Loop

configuration is faster by a factor of 11 at 1000 metres (3281 ft.) of loop distance.

The design and location of the current source determine loop length and data rate performance. In both simplex configurations, the current source compliance voltage can be much lower than the HCPL-4100 device maximum of 27 V. However, limitation on the length of the loop (DC resistance) and data rate capability would dictate a minimum V<sub>CC</sub> which can be used for the current source. With a 24 V  $\pm$ 10% power supply, multidrop applications for very long loop lengths (>3 km) can be done. Device performance as a function of current source design is covered in a later section.

### **DC Performance**

By summing the MARK state voltage drops around the current loop, a basic equation is derived for DC performance for the loop. This is expressed as the maximum distance over which a current loop can be operated.

(1)

$$L = \frac{V_{COMP} - \Sigma V_{RCVR} - \Sigma V_{XMTR}}{\frac{MARK}{2 I_{LOOP} R_{LINE}}}$$

### Where

L = Length of wire in one direction $V_{COMP} = Compliance voltage of$ current source = (V<sub>CC</sub> - V<sub>SAT</sub>) [1]

(2)

$V_{CC}$  = Supply voltage for current source;  $V_{SAT}$  = Saturation voltage of

current source  $I_{LOOP}$  = Operating loop current  $R_{LINE}$  = DC resistance of wire per length

$\Sigma V_{XMTR}$  = Summation of voltage MARK drops across each nonisolated and isolated transmitter current loop terminals when MARK state current flows.<sup>[2]</sup>  $\Sigma V_{RCVR}$  = Summation of voltage

MARK drops across each nonisolated and isolated receiver current loop terminals when MARK state current flows.<sup>[2]</sup>

### Notes:

1.  $V_{COMP}$  must be less than the breakdown voltage rating of the transmitter unit in SPACE state.

2. The non-isolated unit will supply loop current. If two or more non-isolated units are used, then only one of these units needs to supply loop current.

This equation can be solved for any particular parameter of interest if the other remaining parameters are known. For example, Equations (1) and (2) can be solved for minimum power supply voltage, V<sub>CC</sub>, which can be used for current source of Figure 7 for the following conditions.

(3)

$$V_{COMP} = \Sigma V_{RCVR} + \Sigma V_{XMTR}$$

$$MARK MARK$$

$$+ 2L I_{LOOP} R_{LINE}$$

Where,  $\Sigma V_{RCVR} = 2.76 \text{ V} \text{ (One isolated} \\ \text{MARK} \quad \text{receiver)} \\

\Sigma V_{XMTR} = 0 \text{ V} \text{ (Non-isolated} \\ \text{MARK} \quad \text{transmitter voltage drop} \\

\text{is incorporated in V}_{COMP} \\

I_{LOOP} = 22 \text{ mA (20 mA + 10\%)}, \\

R_{LINE} = 0.053 \Omega/\text{m} \text{ (AWG No. 22)}, \\

L = 305 \text{ m} \\

V_{COMP} = 2.76 \text{ V} + 0 \text{ V} + 2(305 \text{ m}) \\

(0.022 \text{ A}) (0.053 \Omega/\text{m}) \\

\end{array}$

= 3.47 V

and using equation (2)

$V_{CC} = V_{COMP} + V_{SAT};$ where  $V_{SAT} = 1.5 V$  = 3.47 V + 1.5 V V<sub>CC</sub> = 4.97 V

For the listed conditions, these calculations are for the worst case temperature and unit to unit variations.

To address device voltage breakdown concerns, the current source compliance level for the current loop and the SPACE state current need to be known. The SPACE state current is determined by the transmitter when it is in the OFF state. SPACE state current will not be necessarily equal to zero. Hence, when a current loop receiver is designed, the threshold must be set at a proper level to avoid detecting the SPACE state current as well as to provide a noise margin. With the HCPL-4200 receiver, SPACE state current of 3.0 mA or less is allowed. Should a larger noise current margin be desired for SPACE state, the maximum SPACE state current of the HCPL-4200 can be raised effectively by shunting the input with a resistor. Actual device current threshold does not change; only the loop current level required to reach SPACE state threshold increases. Use of a shunting resistor will reduce the noise current margin in the MARK state for the HCPL-4200.

Should the HCPL-4100 transmitter be used, the maximum SPACE state current is 2.0 mA. For half duplex applications, a noise margin of 1.0 mA is specified for SPACE state with the combination of the HCPL-4100/-4200 units.

#### **AC Performance**

AC performance of a current loop is influenced by many factors. Typical data rate capability for the simplex configurations shown in Figures 7 and 9 are shown in

Figures 8 and 10 respectively. The 10% (25%) distortion data rate is defined as the rate at which 10% (25%) distortion occurs to the output bit interval with respect to the reference input bit interval. This is expressed by equation (4).

**Distortion Data Rate**

$$f_{\rm D} = \frac{1}{t_{\rm BIT}} \tag{4}$$

Where D = % distortion and  $t_{BIT}$  is bit time of the input signal when D distortion is present in the output bit interval.

A square wave as well as a 16 bit data stream was used to "exercise" the current loop system. In both simplex point-to-point configurations, the input data rate was adjusted to result in a 10% (25%) distortion to the output signal for either an input square wave or a 16 bit pattern.

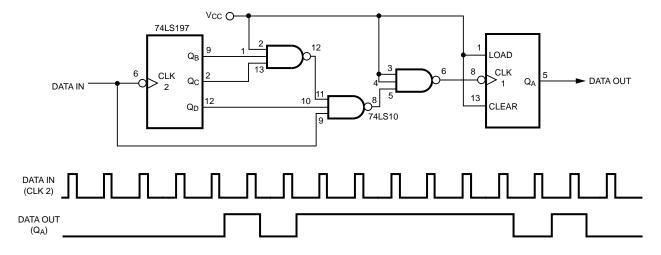

The 16 bit pattern was used to provide two propagation delay test conditions for the current loop. One part of the 16 bit waveform tests for data rate distortion

affected by a long duration in either a MARK or SPACE state prior to state change. The other part of the 16 bit waveform tests for effects on data rate distortion via short durations in either a MARK or SPACE state prior to a state change. In both simplex configurations, Figures 7 or 9, the transition from either a short or a long duration MARK state to a SPACE state affects the data rate distortion the most. The 16 bit exerciser circuit diagram and bit stream waveform are shown in Appendix A.

In the description of the AC performance that follows, an approximation has been made to simplify the analysis. The transmission line is treated as a lumped capacitance. A more complete analysis of AC performance would require rigorous treatment via transmission line theory.

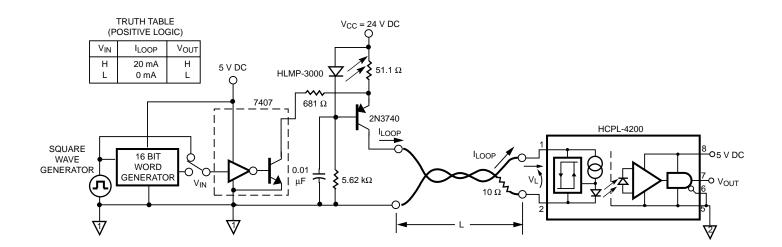

#### Non-isolated Active Transmitter with the HCPL-4200 Receiver

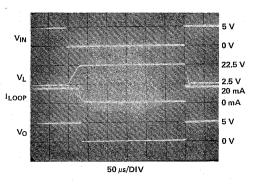

The typical waveforms for the non-isolated active transmitter used with the HCPL-4200 (Figure

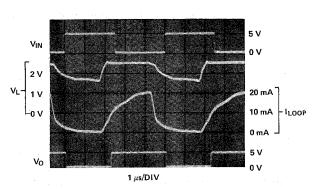

11) are shown in Figures 12 and 13. The loop length is 305 metres (1000 ft.). Figure 12 shows 10% distortion when the input signal is a 16 bit pattern. The total propagation delay shown in Figure 12 for a SPACE to MARK transition is 2.4 µs. The propagation delay of the transmitter and receiver is 0.3 μs. Hence, the propagation delay for the transmission line is 2.1 µs. Current and voltage waveforms for the current loop at the receiver end are shown in Figure 13 for a 10% distortion of data to an input square wave. Notice the loop current waveform delay of  $2.4 \,\mu s$  before V<sub>O</sub> follows V<sub>IN</sub>. The important parameter to observe is loop current. When the loop current level exceeds the HCPL-4200 current threshold, V<sub>O</sub> changes state. Loop voltage at the receiver only follows the current level and changes by approximately one volt. This simplex configuration provides the best speed performance.

Figure 11. Data Rate Test Circuit for Non-Isolated Active Transmitter to Isolated HCPL-4200 Receiver

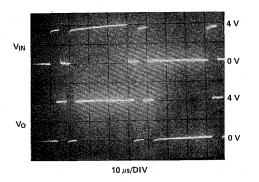

Figure 12. Timing Comparision of Output Signal ( $V_0$ ) to Input Signal ( $V_{IN}$ ) using 16-bit word at 10% Distortion with 305 m (1000 ft.) Loop Distance. Reference Figure 11.

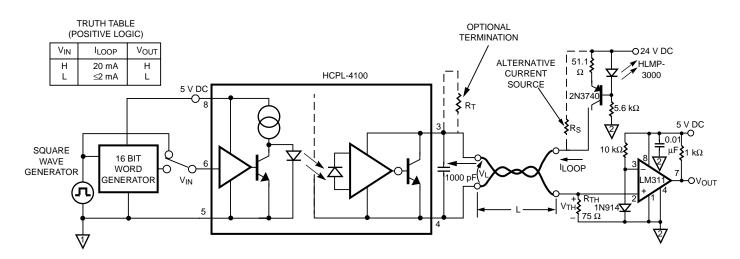

#### Non-Isolated Active Receiver with the HCPL-4100 Transmitter

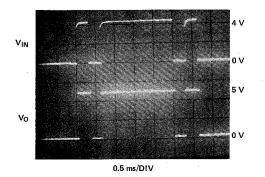

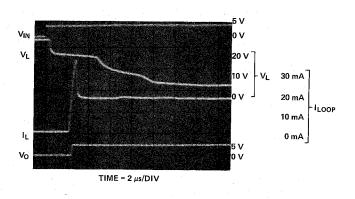

The typical waveforms for the non-isolated active receiver used with the HCPL-4100 (Figure 14) are shown in Figures 15 and 16. The loop length is 305 metres (1000 ft.). Figure 15 shows 10% distortion when the input signal is a 16 bit pattern. Figure 16 illustrates a 10% distortion for an input square wave. Recall that current level determines the switching point, not the voltage level.

At the input low to high state change, the loop current changes momentarily to the MARK state short circuit output current level, I<sub>SC</sub>, (typically 85 mA). A current spike appears at the receiver end after the inherent transmission line propagation delay of approximately 2 µs, as expanded in Figure 17. The spike is caused by sudden discharge of cable capacitance. However, the loop current rapidly decreases from the I<sub>SC</sub> level to a 20 mA level when line discharge is complete. Time duration of ISC can be calculated by referring to the output power dissipation calculations for the

#### HCPL-4100 in Appendix B.

The non-isolated receiver switched states when loop current crossed approximately 10 mA level. Yet, the loop voltage took approximately 10  $\mu$ s to change from a current source voltage compliance level of 22.5 V to a MARK state voltage of 2.4 V at 20 mA. This loop voltage characteristic does not limit the turn on speed performance.

At the input signal high to low transition, the HCPL-4100 transmitter turns off after the device propagation delay. However, the loop current at the receiver does not change from 20 mA until approximately 30 µs later. This is due to the current source charging the line capacitance at a fixed rate of 20 mA from essentially a MARK state voltage level (2.4 V) to the compliance level of the current source. Only after the compliance voltage is reached does the loop current fall below the 10 mA threshold of the receiver. As before, the current level at the receiver determines the switching time. In this example, the compliance voltage of the current source influences the turn off delay of the

Figure 13. Characteristic Waveform Performance of Circuit in Figure 11 with 305 m (1000 ft.) Loop Distance, Square Wave Input and Output Distortion of 10%. a. Input Voltage (V<sub>IN</sub>), b. Receiver Load Voltage (V<sub>L</sub>), c. Loop Current (I<sub>LOOP</sub>), d. Output Voltage (V<sub>0</sub>)

loop. This dependence is graphically illustrated in Figure 10.

#### General Factors Affecting Data Rate

Three factors which limit data rate and their corresponding trade-offs are:

1. Loop length: The length of the line will limit the speed performance of a current loop. This results mainly from the total capacitive loading effect of the cable upon the transmitter and receiver. The data rate versus length of line for the two simplex point-to-point configurations is illustrated in Figures 8 and 10. Shielded cable provides more noise immunity but, in general, the capacitance per unit length will be larger than unshielded cable. The characteristics of the cable used, such as wire size, twist, insulation material, etc. all influence the maximum data rate. (The characteristics of the cable used in the text applications are listed in Appendix C.)

2. Current Source: The location, type and compliance voltage of the current source used within a current loop can affect the system

Figure 14. Data Rate Test Circuit for Isolated HCPL-4100 Transmitter to Non-Isolated Active Receiver

Figure 15. Timing Comparison of Output Signal ( $V_0$ ) to Input Signal ( $V_{IN}$ ) Using 16-bit Word at 10% Distortion with 305 m (1000 ft.) Loop Distance. Reference Figure 14.

Figure 16. Characteristic Waveform Performance of Circuit in Figure 14 with 305 m (1000 ft.) Loop Distance, Square Wave Input and Output Distortion of 10%. a. Input Voltage ( $V_{IN}$ ), b. Transmitter Load Voltage ( $V_L$ ), c. Loop Current ( $I_{LOOP}$ ), d. Output Voltage ( $V_O$ )

Figure 17. Expanded Waveform Response of Figure 16. Displayed are details of  $I_{SC}$  Magnitude and Duration at Receiver as well as Transmitter Output Voltage ( $V_L$ )

data rate. The primary limitation on data rate is the location of the current source within the loop. When the current source is located at the transmitter end of the loop rather than at the receiver end, the maximum data rate is much higher for a given loop length. This effect can be seen when comparing data in Figure 8 to Figure 10. The main reason for the lower data rate capability shown in Figure 10 is that the current source must charge the cable capacitance to the compliance voltage of the current source. The speed achieved in Figure 8 results because cable voltage changes by a small amount between the MARK and SPACE states. Practical applications of the HCPL-4100 and HCPL-4200 optocouplers generally will require the current source to be located at the non-isolated end of the loop. For best speed performance, an active non-isolated transmitter would be used with the HCPL-4200 receiver. However, in full duplex applications (two simplex loops), the non-isolated ends should be at a common location. Hence, overall bidirectional system data rates would be limited by the slowest loop, i.e., the one which contained a non-isolated, active receiver. More discussion of full and half duplex applications is found in subsequent sections.

The type of current source can affect speed performance. A simple resistor, when used with a voltage source at the non-isolated loop end, can set the loop current level. Improper source impedance or termination of the loop causes reflections which distort data resulting in a lower data rate capability. Termination of a current loop with an impedance equivalent to the characteristic impedance of the line can improve the data rate capability by approximately 20%. Termination resistance does reduce part of the voltage available for operating station(s) on the loop.

An active element current source can be controlled by current steering which allows for a higher speed of operation while providing consistently high on and off output impedance. Less variation in current source output impedance can help to reduce multiple signal reflections from occurring. Active element current sources are described in the Current Sources section of this application note.

The compliance voltage can influence the speed performance of the non-isolated, active receiver circuit shown in Figure 9. Data rate dependency upon the compliance voltage is shown in Figure 10. Reducing the current source supply voltage from 24 V DC to 10 V DC for a simplex point-topoint current loop configuration increases the data rate by a factor of 3.5 in a 1000 metre (3281 ft.) loop. The reason for the improvement is that less time is required to charge the transmission line to the lower compliance voltage level at a constant charge rate. However, the opposite simplex arrangement of a non-isolated, active transmitter, Figure 7, has no data rate dependency on compliance voltage as illustrated in Figure 8. This is the result of the HCPL-4200 performing current threshold detection, not voltage level detection.

The maximum usable data rate for a given loop length and configuration is usually determined by the propagation delay differences of the current loop and the amount of skew that is allowed in the user's application. Propagation delay skew is |tPLH - tPHL|. Factors which contribute to the system propagation delay skew are the current source compliance voltage level, the current source location, the inherent propagation delay skew of the current source, as well as the optocoupler propagation delay skew. Detailed information on factors which affect distortion of data are discussed in the subsequent Half Duplex section.

3. Device Performance: The propagation delay of the transmitter and the receiver can influence data rates for short loop lengths (<100 metres) in high speed applications (>1 MBd). Generally, current loops are designed to operate over much greater distances than 100 metres. Consequently, the cable capacitance dominates the data rate limitations.

Another device performance consideration is the power dissipated in the HCPL-4100 transmitter. An example of power dissipation calculation for the HCPL-4100 is given in Appendix B. Derating may be required when operating the unit at large V<sub>CC</sub> voltage.

#### **Optional Device Protection Considerations**

Specific end product applications may require additional device protection. A bridge rectifier can be included in order to remove loop polarity connection concerns. Current buffering can be designed for loop currents greater than 30 mA. Possibility of damage due to electrostatic discharge to the cable or interconnection points can be significantly reduced by the use of energy absorbing devices, such as TransZorbs® or metal oxide varistors (MOV).

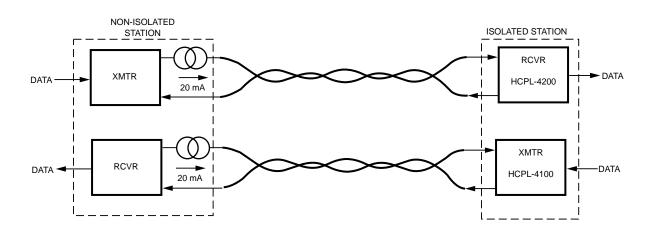

#### **Full Duplex**

A common and useful extension of the simplex configuration is the full duplex configuration. Full duplex communication is defined as the simultaneous, bidirectional transmission of information between local and remote units. The block diagram in Figure 18 shows this point-to-point configuration.

Essentially, a full duplex arrangement is two point-to-point simplex loops (a four wire system) used simultaneously for back and forth data flow. A common current loop application for full duplex configuration is connecting remote terminals to an I/O interface section of a central computer system.

Implementation of optical isolation within a full duplex current loop system should be done at one common end of the loops. Two separate, active, non-isolated units are located at the other end of the loops. Figure 18 illustrates these comments. Providing isolation at one common end will significantly reduce common mode coupling between the two loops. In most

cases, the full duplex data rate is limited by the loop containing the HCPL-4100 and the non-isolated active receiver. This limitation can be circumvented by using an isolated current source at the HCPL-4100 end of the loop and a non-isolated passive receiver. The isolated current source increases the cost of the data link, but this increased cost may be justified by the speed improvement obtained. All information which is described in the Simplex section for the performance of a simplex point-topoint current loop configuration will apply to the full duplex applications as well.

#### **Half Duplex**

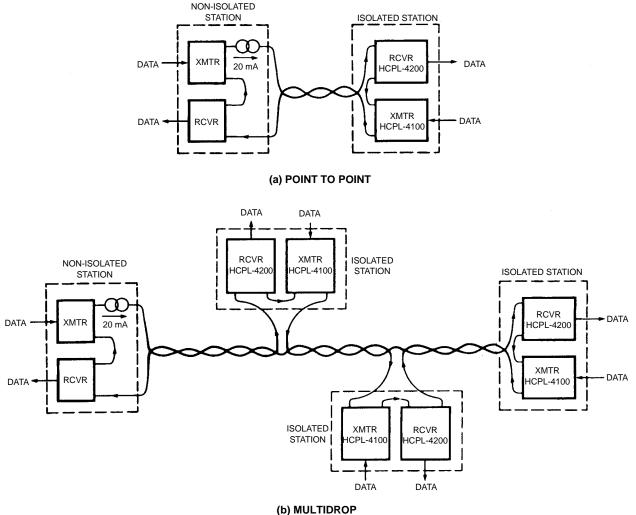

A half duplex current loop provides non-simultaneous, bidirectional data flow between remote and local equipment. This configuration utilizes a simpler two wire interconnection, compared to the four wire arrangement of the full duplex case. The half duplex system can easily be expanded from a point-to-point application to a multi-drop application with multiple transmit and receive stations along the loop. The block diagrams of Figure 19 demonstrate the two cases of point-topoint and multidrop for half duplex.

A characteristic of the half duplex configuration is the need to establish priority of transmitters in the current loop whether the loop is point-to-point or multidrop. Protocol in the information being transferred will ensure that only one transmitter is sending data at any given time. Typical usage of a half duplex current loop parallels similar applications for the full duplex case.

#### **DC Performance**

As Figure 19 illustrates, isolation of the current loop from logic systems is easily implemented at one end of the loop by the use of the combination of the HCPL-4100 transmitter and the HCPL-4200 receiver. Significant reduction of common mode influences on the current loop, elimination of ground potential differences and specified loop current noise immunity are achieved by the use of these complementary optocouplers. For this combination of optocouplers, the loop current noise immunity is a

Figure 18. Full Duplex Point-to-Point Current Loop System Configuration

Figure 19. Half Duplex Current Loop System Configurations for: a. Point-to-Point, b. Multidrop

minimum of 1 mA in the SPACE state and 8 mA in the MARK state. A non-isolated active transceiver (transmitter and receiver) with one current source operates at the opposite end of the current loop.

The maximum compliance voltage of the current source is limited by the breakdown voltage capability of any transmitter in the half duplex loop. The isolated HCPL-4100 transmitter has a maximum operating voltage of 27 V DC. However, in multidrop applications, each isolated HCPL-4200

receiver will share a portion of the compliance voltage during the SPACE state, worst case 0.9 V DC at a minimum SPACE state current of 0.5 mA. Also, each isolated conducting HCPL-4100 transmitter will share a portion of the compliance voltage during SPACE state as well. Worst case, this is 0.95 V DC at 0.5 mA. For example, with four pairs of HCPL-4100 and HCPL-4200 units being used, an additional worst case 6.5 V DC can be added to increase the maximum compliance voltage value from 27 V DC to 33.5 V DC for the

current source. The additional 6.5 V DC is calculated on the basis of one of the HCPL-4100 transmitters interrupting 22 mA loop current at 200 metre station intervals. This increase in the compliance voltage level can allow another isolated station to be used. Minimum V<sub>CC</sub> required for the current source of Figure 20(b) with five isolated stations in the MARK condition with worst case parameters previously used yields 33.2 V DC. A higher compliance voltage can allow longer loop lengths but data rate will be slower. Precautions

must be taken to prevent the removal of any stations from the loop in order to avoid an excessive compliance voltage from overstressing any transmitter remaining in the loop. A design compromise has to be determined for the benefits achieved at different compliance voltages. Equation (1) from the Simplex section can be used to determine any DC parameter in a half duplex application.

A specific active, non-isolated transceiver which can be used in point-to-point and multidrop applications with the HCPL-4100 and HCPL-4200 current loop optocouplers is shown in Figure 20.

## **AC Performance**

#### **Point-to-Point**

The corresponding data rate performance versus loop distance and direction of data is given in Figure 21 for the half duplex point-to-point application. Definitions for 10% and 25% distortion data rate are given under the Simplex Configuration section. Transmission of data from an isolated T/R (transmitter and receiver pair) to an active nonisolated T/R limits the half duplex data rate performance. This limitation is due to slower speed of a current loop when using an isolated transmitter. A lower current source compliance voltage will improve the data rate of an isolated T/R to a non-isolated T/R as discussed in the Simplex section.

Figure 20. Circuit Schematic of Half Duplex Configurations: a. Point-toPoint, b. Multidrop

Figure 21. Half Duplex Point-to-Point (Figure 20a) Data Rate vs. Loop Length and Data Direction

#### Multidrop

The data rate performance for half duplex multidrop applications, as illustrated in Figure 20(b), is summarized in Tables 1 and 2. These tables compare data rate versus the loop distance between stations, total length of loop, direction of data. distortion data rate and data format. Table 1 illustrates at fixed distortion (10% or 25%) how data rate can be different at different stations along the loop. Table 2 shows the pulse width distortion that results when the multidrop loop is operated at several fixed data rates.

Comparision of data rates for point-to-point (half duplex) and multidrop configurations can

appear contradictory. Data presented in Figure 21 and Table 1 illustrate this at a 25% distortion on a 915 m (3000 ft.) loop. A comparison shows the influence of multiple stations upon the data rate for a fixed loop length. In the point-to-point case, the data rate is 62.5 kBd from an active, nonisolated T/R to the isolated T/RNo. 1. In the multidrop case, nonisolated T/R to the isolated T/R No. 3, data rate in the same direction is 25 kBd. As expected, the data rate in point-to-point is faster because the current source only needs to charge the line to a lower sum ( $\cong 1/2$ ) of MARK state voltages than in the multiple station case. However, in the opposite direction of isolated T/R

No. 1 to active, non-isolated T/R, the point-to-point data rate is 3.33 kBd while the multidrop data rate is 6.25 kBd. In this instance, multidrop is 2X faster than the point-to-point case over the same distance, contrary to "expected" results. The reason for this speed improvement results from the fact that when T/R No. 3 interrupts the loop current, the current source will continue to charge the loop until the compliance voltage is reached causing the current source to shut down. Fortunately. the voltage difference between the sum of all MARK state voltage drops and compliance voltage is small due to the total of four stations in the loop. Hence, a small voltage excursion requires considerably less charging time than if this charging occurred over a larger voltage excursion.

In addition, with the usage of multiple stations at a constant data rate, the data distortion can vary from station to station. This distortion varies with respect to the transmitting station. As an illustration from Table 2, the 915 m (3000 ft.) example with three remote stations [i.e., the isolated T/R No. 3 transmitting at 6.25 kBd to successive 305 m (1000 ft.) stations of T/R No. 2. T/R No. 1 and an active non-isolated transceiver] yields distortion levels of 19%, 31%, 25% respectively. Larger distortion at an interim station than at a station located at an end of a loop is due to different thresholds for each station. Identical current threshold levels at each station will provide progressively increasing distortion levels at each station along the loop. Also, reflection of signals between stations can account for inconsistent distortion levels at various stations on a loop system. The designer will be limited to a

| Data In      | Data Out     | Length<br>Data Iı | L<br>between<br>put and<br>put Points<br>ft. | L <sub>T</sub><br>Total<br>Loop<br>Length<br>m (ft.) | Data<br>Rate<br>kBd | %<br>Distortion | Comments                         |

|--------------|--------------|-------------------|----------------------------------------------|------------------------------------------------------|---------------------|-----------------|----------------------------------|

|              |              |                   |                                              |                                                      |                     |                 |                                  |

| Active       | T/R #4       | 122               | 400                                          |                                                      | 250                 | 25%             | Input Signal:                    |

| Non-Isolated | T/R #3       | 92                | 300                                          |                                                      | 370                 |                 | Square Wave                      |

| Transceiver  | T/R #2       | 61                | 200                                          |                                                      | 370                 |                 |                                  |

|              | T/R #1       | 31                | 100                                          |                                                      | 250                 |                 | Current Source:<br>20 mA/24 V DC |

|              | T/R #4       | 122               | 400                                          |                                                      | 125                 | 10%             |                                  |

|              | T/R #3       | 92                | 300                                          |                                                      | 167                 |                 |                                  |

|              | T/R #2       | 61                | 200                                          | 122                                                  | 167                 |                 | Half Duplex                      |

|              | T/R #1       | 31                | 100                                          | (400)                                                | 125                 |                 | Current Loop                     |

| Isolated     | Non-Iso. T/R | 122               | 400                                          |                                                      | 62.5                | 25%             | Curcuit                          |

| T/R #4       | T/R #1       | 92                | 300                                          |                                                      | 62.5                |                 | Schematic:                       |

|              | T/R #2       | 61                | 200                                          |                                                      | 82.5                |                 | Figure 20b                       |

|              | T/R #3       | 31                | 100                                          |                                                      | 100                 |                 | _                                |

|              | Non-Iso. T/R | 122               | 400                                          |                                                      | 25                  | 10%             |                                  |

|              | T/R #1       | 92                | 300                                          |                                                      | 25                  |                 |                                  |

|              | T/R #2       | 61                | 200                                          |                                                      | 33.3                |                 |                                  |

|              | T/R #3       | 31                | 100                                          |                                                      | 40                  |                 |                                  |

| Active       | T/R #3       | 915               | 3000                                         |                                                      | 25                  | 25%             |                                  |

| Non-Isolated | T/R #2       | 610               | 2000                                         |                                                      | 33.3                |                 |                                  |

| Transceiver  | T/R #1       | 305               | 1000                                         |                                                      | 25                  |                 |                                  |

|              | T/R #3       | 915               | 3000                                         |                                                      | 12.5                | 10%             |                                  |

|              | T/R #2       | 610               | 2000                                         | 915                                                  | 16.7                |                 |                                  |

|              | T/R #1       | 305               | 1000                                         | (3000)                                               | 12.5                |                 |                                  |

| Isolated     | Non-Iso. T/R | 915               | 3000                                         |                                                      | 6.25                | 25%             | ]                                |

| T/R #3       | T/R #1       | 610               | 2000                                         |                                                      | 5.0                 |                 |                                  |

|              | T/R #2       | 305               | 1000                                         |                                                      | 8.25                |                 |                                  |

|              | Non-Iso. T/R | 915               | 3000                                         |                                                      | 2.0                 | 10%             |                                  |

|              | T/R #1       | 610               | 2000                                         |                                                      | 2.0                 |                 |                                  |

|              | T/R #2       | 305               | 1000                                         |                                                      | 3.33                |                 |                                  |

# Table 1. Constant % Distortion, Variable Data Rate for Half DuplexMultidrop Configuration

data rate that results in acceptable distortion for each station.

In general, data rate limitations in multidrop applications for data which flows from active nonisolated station to isolated stations will be caused by propagation delay time of the line and the charging or discharging time for the total line capacitance. Charging and discharging the line occurs over a voltage level which is equal to the difference between the sum of all MARK state voltages and the sum of all SPACE state voltages which are presented at the active non-isolated loop connection points. Data rate limitations in the opposite direction (isolated units to an active, non-isolated unit) are limited by propagation delay time of the line and by the time to charge total line capacitance over a voltage equal to the difference between the sum of MARK state voltages and compliance voltage of the current source.

| Data In      | Data Out     | Length<br>Data Ir | L<br>between<br>put and<br>put Points<br>ft. | L <sub>T</sub><br>Total<br>Loop<br>Length<br>m (ft.) | Data<br>Rate<br>kBd | %<br>Distortion | Comments                         |

|--------------|--------------|-------------------|----------------------------------------------|------------------------------------------------------|---------------------|-----------------|----------------------------------|

| Active       | T/R #4       | 122               | 400                                          |                                                      | 250                 | 25%             | Input Signal:                    |

| Non-Isolated | T/R #3       | 92                | 300                                          |                                                      | 250                 | 30%             | Square Wave                      |

| Transceiver  | T/R #2       | 61                | 200                                          |                                                      | 250                 | 15%             | Square mare                      |

| manseerver   | T/R #1       | 31                | 100                                          |                                                      | 250                 | 25%             | Current Source:<br>20 mA/24 V DC |

|              | T/R #4       | 122               | 400                                          |                                                      | 125                 | 10%             |                                  |

|              | T/R #3       | 92                | 300                                          |                                                      | 125                 | 6%              |                                  |

|              | T/R #2       | 61                | 200                                          | 122                                                  | 125                 | 7.5%            | Half Duplex                      |

|              | T/R #1       | 31                | 100                                          | (400)                                                | 125                 | 12%             | Current Loop                     |

| Isolated     | Non-Iso. T/R | 122               | 400                                          |                                                      | 62.5                | 25%             | Curcuit                          |

| T/R #4       | T/R #1       | 92                | 300                                          |                                                      | 62.5                | 25%             | Schematic:<br>Figure 20b         |

|              | T/R #2       | 61                | 200                                          |                                                      | 62.5                | 19%             |                                  |

|              | T/R #3       | 31                | 100                                          |                                                      | 62.5                | 6%              |                                  |

|              | Non-Iso. T/R | 122               | 400                                          |                                                      | 25                  | 10%             |                                  |

|              | T/R #1       | 92                | 300                                          |                                                      | 25                  | 10%             |                                  |

|              | T/R #2       | 61                | 200                                          |                                                      | 25                  | 7.5%            |                                  |

|              | T/R #3       | 31                | 100                                          |                                                      | 25                  | 7.5%            |                                  |

| Active       | T/R #3       | 915               | 3000                                         |                                                      | 25                  | 25%             |                                  |

| Non-Isolated | T/R #2       | 610               | 2000                                         |                                                      | 25                  | 17.5%           |                                  |

| Transceiver  | T/R #1       | 305               | 1000                                         |                                                      | 25                  | 25%             |                                  |

|              | T/R #3       | 915               | 3000                                         |                                                      | 12.5                | 10%             |                                  |

|              | T/R #2       | 610               | 2000                                         | 915                                                  | 12.5                | 7.5%            |                                  |

|              | T/R #1       | 305               | 1000                                         | (3000)                                               | 12.5                | 12%             |                                  |

| Isolated     | Non-Iso. T/R | 915               | 3000                                         |                                                      | 6.25                | 25%             | 1                                |

| T/R #3       | T/R #1       | 610               | 2000                                         |                                                      | 6.25                | 31%             |                                  |

|              | T/R #2       | 305               | 1000                                         |                                                      | 6.25                | 19%             |                                  |

|              | Non-Iso. T/R | 915               | 3000                                         |                                                      | 2.0                 | 10%             |                                  |

|              | T/R #1       | 610               | 2000                                         |                                                      | 2.0                 | 8%              |                                  |

|              | T/R #2       | 305               | 1000                                         |                                                      | 2.0                 | 12%             |                                  |

# Table 2. Constant Data Rate, Variable % Distortion for Half DuplexMultidrop Configuration

#### **Current Sources**

#### Resistor

Current sources used for current loop systems can vary in performance, complexity and cost. The most elementary and inexpensive technique for supplying loop current is to use a series resistor between the non-isolated station power supply and the loop. The resistance value (R<sub>S</sub>) to use is a function of the desired loop current (I<sub>LOOP</sub>), of the type of cable (resistance per length, R<sub>LINE</sub>), the loop length (L), the number of stations on the loop with their respective MARK state terminal voltages ( $\Sigma V_{MARK}$ ) and the power supply voltage (V<sub>CC</sub>) for the non-isolated station. Equation (5) determines the resistor value. The simplicity of a single resistor yielding a 20 mA loop current is achieved at the expense of requiring that the loop configuration cannot be changed without changing the resistor value.

$$R_{S} = \frac{(5)}{\frac{V_{CC} - (I_{LOOP}) (R_{LINE}) 2L - \Sigma V_{MARK}}{I_{LOOP}}}$$

Speed performance of a loop system using a current setting resistor is slower than with an active current source. This difference arises from an exponential current response versus a linear current response associated with an active current source. For a given current threshold level, the linear response will charge a capacitive line quicker than an exponential response. When a current setting resistor is used, termination resistance can be employed at the isolated stations in order to reduce somewhat the signal reflections along a loop. Up to a 20% speed improvement can be obtained with termination resistance equal to characteristic line impedance. However, with the use of termination resistance, allowance must be made for the additional MARK state voltage drop of the terminating resistor with respect to the available compliance range of the current loop.

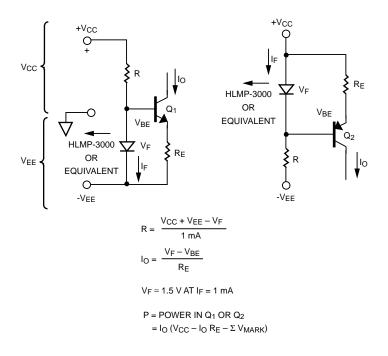

#### **LED/Transistor**

The recommended current source to use is a simple, relatively inexpensive, active constant current source shown in Figure 22. The LED provides a stable voltage reference  $(V_F)$  for the transistor base and also helps to compensate the base-emitter junction voltage (V<sub>BE</sub>) changes with temperature. This current source is fairly independent of the V<sub>CC</sub> level if the LED bias current  $(I_F)$  is set so that the V<sub>F</sub> only changes slightly with large variations in  $I_F (\cong 60 \text{ mV}/$ decade of I<sub>F</sub>). Regulation of 10% in output current can easily be achieved over a V<sub>CC</sub> range of 5 V DC - 27 V DC.

When large  $V_{CC}$  is used with low MARK state voltage conditions, the use of a transistor with good thermal conduction to the ambient environment will minimize the variation in the source current because of the variation of  $V_{BE}$ with temperature. This state is the large power dissipation condition.

This current source can be easily current steered for fast switching. Current steering is illustrated in Figure 7. For applications of this current source at high data rates over short loop distances it is important that the difference in propagation delays from on-to-off and off-to-on be made as small as possible. Status indication is conveniently given by the LED.

#### **Specialized Integrated Circuits**

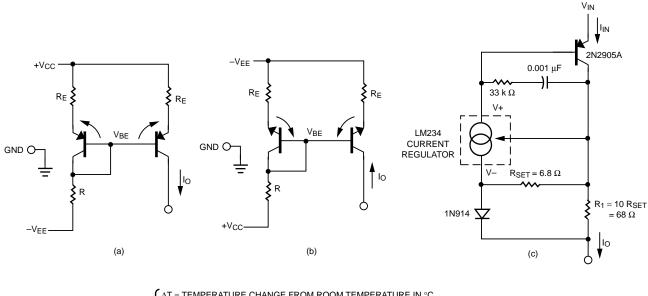

More complicated current sources which are usable in current loops can be current mirrors or specialized integrated circuits. A current mirror displayed in Figure 23

Figure 22. Recommended Constant Current Source

requires the use of a matched pair of transistors in order to perform well.

In general, commercially available matched pairs are not designed for output collector currents greater than 10 mA. Additional components which are needed to obtain 20 mA results in greater complexity and higher cost with less reliability. In order to reduce power supply noise influences and improve thermal stability, significant transistor emitter degeneration resistance must be used. This degeneration sacrifices the available voltage range between the total MARK state voltage and the compliance voltage of the current mirror.

In Figure 23(c), the LM234 integrated circuit current source can be used. More components are required for temperature compensation to provide a proper current level and regulation over a wide temperature range as well as to prevent possible oscillations of this active device. In addition, switching characteristics of the LM234 must be considered with regard to the desired loop speed performance. Over all, the current source provides good regulation  $(\pm 3\%)$  for current loop usage, but the cost of additional components and space in an input-output module may detract from the design convenience of this device.

Figure 23. Specialized Integrated Circuit Current Sources. Current Mirrors: a. PNP, b. NPN. Current Regulator: c. LM234 plus Components

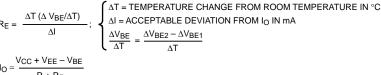

(6)

## **Appendix A.**

#### 16-Bit TTL Data Exerciser Circuit

The purpose of this circuit is to provide long (6 bits) and short (1 bit) durations of the logic one and logic zero states in different time sequences. Figure 24 illustrates the 16-bit TTL output waveform  $(Q_A)$ .

## Appendix B.

# HCPL-4100 Power Dissipation Calculations

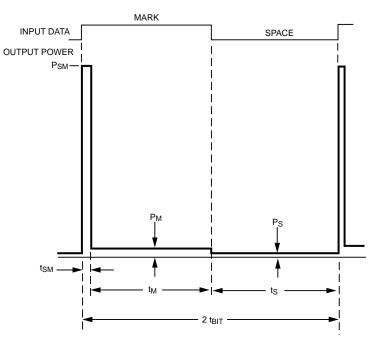

The power dissipation calculation for the HCPL-4100 transmitter is made using the standard method for determining the input power dissipation. Calculation of the output power dissipation must take into account power consumed in three different operating conditions. These conditions are: 1. power dissipated during transition from SPACE to MARK state, 2. power dissipated in MARK state, and 3. power dissipated in SPACE state. The worst case average power dissipated over two bit intervals should be calculated. The average output power dissipation is calculated from the following formula:

$$P_{O} = \frac{P_{SM}t_{SM} + P_{M}t_{M} + P_{S}t_{S}}{2 t_{BIT}}$$

where

$P_0$  = Average output power dissipated during a worst case time interval.

P<sub>SM</sub> = Power dissipated during SPACE to MARK transition

$$=\frac{I_{SC}(V_{COMP}+V_{MO})}{2}$$

(7)

$I_{SC} = MARK \text{ state short circuit}$ output current  $V_{COMP} = Compliance \text{ voltage of}$ current source  $V_{MO} = MARK \text{ state output}$ voltage  $P_M = Power \text{ dissipated during}$ MARK state  $= V_{MO}LOOP \qquad (8)$

$$= V_{MOILOOP}$$

P<sub>S</sub> = Power dissipated during SPACE state

$$= V_{\rm COMP} I_{\rm SO} \tag{9}$$

I<sub>SO</sub> = SPACE state output current

$t_{SM}$  = Duration time of power dissipated during SPACE to MARK transition

$$= \frac{C_{L} (V_{COMP} - V_{MO})}{I_{SC}} \qquad (10)$$

$$\begin{array}{ll} C_L & = Total \mbox{ load capacitance} \\ t_M & = Duration \mbox{ time of MARK} \\ state & \end{array}$$

$t_S$  = Duration time of SPACE state

t<sub>BIT</sub> = Time of bit interval

These formulas are based upon an assumption of a linear discharge of a capacitive load.

Using equations (6) through (10), the worst case output power dissipated in the HCPL-4100

Figure 24. 16-bit TTL Data Exerciser Circuit and Corresponding Waveforms

transmitter can be calculated for the following operating conditions.

L = 200 metres (656 ft.) = 36,000 pF (180 pF/m)CL

$$V_{COMP} = 23.5 \text{ V DC} (V_{CC} = 24 \text{ V})$$

DC)

ILOOP = 22 mA (20 mA + 10%)

= 85 mA ISC

TA = 70°C

CMOS LOGIC (15 V

$$\pm$$

5%)

**HCPL-4100** Power Dissipation Limits at 70°C PIN = 208 mW, $P_{TOTAL} = 283.5 \text{ mW}$

= 2.75 V at 22 mA V<sub>MO</sub>

$I_{SO} = 2 \text{ mA}$

$t_{BIT} = 104.1 \, \mu s$

(9600 Baud, NRZ\* alternating MARK and SPACE states. **Reference Figure 25.)**

\*Non Return to Zero data format.

D = 25% Distortion

Calculation of maximum input power to the HCPL-4100 is based upon linear interpolation of maximum I<sub>CC</sub> and I<sub>IH</sub>.

$$P_{IN} = V_{CC}I_{CC} + V_{IH}I_{IH}$$

(11)

= (15.8 V) (12.6 mA) +

(15.8 V) (0.206 mA)

= 202.3 mW. < 208 mW

max

f

P<sub>SM</sub> = 733.1 mW

Figure 25. Output Power Dissipation over Two Bit Intervals in HCPL-4100 Transmitter

Consequently, maximum derated output power is

Po  $= P_{TOTAL} - P_{IN}$ (12)

= 81.2 mW

Applying given values to equations (7), (8), (9), and (10) results in

| P <sub>SM</sub> | = 1115.6 mW        |

|-----------------|--------------------|

| PM              | = 60.5 mW          |

| Ps              | <sub>=</sub> 47 mW |

| t <sub>SM</sub> | = <b>8.8</b> μs    |

Equation (6) yields average output power per bit interval of = 98.4 mW > 81.2 mW max 20 To circumvent this excess output

power dissipation condition,  $V_{CC}$  of current source can be reduced from 24 V DC to 15V DC. Recalcuation with  $V_{CC} = 15$  V DC yields

= 60.5 mWРм Ps = 29 mW $= 5.0 \, \mu s$ t<sub>SM</sub> Po = 60.9 mW < 81.2 mW max

The major compromises which would be given up are: a. maximum loop length is reduced by one half, and b. less capability for multidrop applications. However, data rate can be doubled to 20 kBd at  $V_{CC}$  = 15 V DC over 200 metres.

### **Appendix C.**

#### Cable Data

The cable which was used throughout this application note contained five pairs of unshielded, twisted. 22 AWG wire (Dearborn No. 862205). Typical measured properties of this cable are listed

below. Other manufacturers provide cable with similar characteristics (Belden No. 9745). Consult cable manufacturer catalogs for detailed information.

$Z_0 = 75 \Omega$ , Characteristic Impedance - line to line

$R_{\text{LINE}} = 52.91 \ \Omega/1000 \text{ m}, \text{ DC}$ Resistance - single conductor

C = 174 pF/m, Capacitance - line to line

$t_{DELAY} = 5.9 \text{ nsec/m}$

## Appendix D.

#### **List of Parameters**

C<sub>L</sub> = Total load capacitance

f<sub>D</sub> = Data rate at which D% output pulse distortion occurs

I<sub>LOOP</sub> = Operating loop current

I<sub>SC</sub> = MARK state short circuit output current

I<sub>SO</sub> = SPACE state output current

L = Length of wire in one direction

P<sub>S</sub> = Power dissipated during SPACE state

P<sub>0</sub> = Average output power dissipated over a time interval

P<sub>SM</sub> = Power dissipated during SPACE to MARK transition

P<sub>M</sub> = Power dissipated during MARK state

$\begin{array}{ll} R_{LINE} &= DC \ resistance \ of \ wire \\ per \ length \end{array}$

$\begin{array}{ll} R_S & = Current \ setting \ resistor \\ from \ non-isolated \ power \ supply \\ t_{BIT} & = Time \ of \ bit \ interval \\ t_S & = Duration \ time \ of \ SPACE \\ state \end{array}$

$t_M$  = Duration time of MARK state

$t_{SM}$  = Duration time of SPACE to MARK transition

V<sub>CC</sub> = Power supply voltage

V<sub>COMP</sub> = Compliance voltage of current source

V<sub>MO</sub> = MARK state output voltage

V<sub>RCVR</sub> = Voltage across current MARK loop receiver terminals when MARK state current flows

$V_{SAT}$  = Saturation voltage of current source

V<sub>XMTR</sub> =Voltage across current MARK loop transmitter terminals when MARK state current flows

## Appendix E.

#### References

1. *Optoelectronics / Fiber Optics Application Manual*, Agilent Technologies, Second Edition, McGraw-Hill, New York, 1981, pp. 3.1-3.77, 10.1-10.8.

2. True, Kenneth M., *The Interface Handbook – Line Drivers and Receivers*, Fairchild Semiconductor Components Group, Mountain View, CA., 1975, pp. 1-1 – 5-12.

3. McNamara, John E., *Technical Aspects of Data Communications,* Second Edition, Digital Equipment Corporation, Bedford, MA., 1982, pp. 13-21, 233-242.

4. Larsen, David G., Ronz, Peter R., Titus, Jonathan A., "INWAS: Interfacing with Asynchronous Serial Mode," *IEEE Transactions on Industrial Electronics and Control Instrumentation*, Vol. IECI-24, No. 1, February 1977, pp. 2-10.

5. *Agilent 13266A Current Loop Converter User's Manual*, Agilent Technologies, Palo Alto, CA 1979 SUNSTAR微波光电 http://www.rfoe.net/ TEL:0755-83396822 FAX:0755-83376182 E-MAIL:szss20@163.com

Agilent Technologies Innovating the HP Way

*www.semiconductor.agilent.com* Data subject to change. Copyright © 1999 Agilent Technologies, Inc. 5953-9359 (11/99) SUNSTAR 商斯达实业集团是集研发、生产、工程、销售、代理经销、技术咨询、信息服务等为一体的高科技企业,是专业高科技电子产品生产厂家,是具有10多年历史的专业电子元器件供应商,是中国最早和最大的仓储式连锁规模经营大型综合电子零部件代理分销商之一,是一家专业代理和分銷世界各大品牌IC芯片和電子元器件的连锁经营综合性国际公司,专业经营进口、国产名厂名牌电子元件,型号、种类齐全。在香港、北京、深圳、上海、西安、成都等全国主要电子市场设有直属分公司和产品展示展销窗口门市部专卖店及代理分销商,已在全国范围内建成强大统一的供货和代理分销网络。我们专业代理经销、开发生产电子元器件、集成电路、传感器、微波光电元器件、工控机/DOC/DOM电子盘、专用电路、单片机开发、MCU/DSP/ARM/FPGA软件硬件、二极管、三极管、模块等,是您可靠的一站式现货配套供应商、方案提供商、部件功能模块开发配套商。商斯达实业公司拥有庞大的资料库,有数位毕业于著名高校——有中国电子工业摇篮之称的西安电子科技大学(西军电)并长期从事国防尖端科技研究的高级工程师为您精挑细选、量身订做各种高科技电子元器件,并解决各种技术问题。

微波光电部专业代理经销高频、微波、光纤、光电元器件、组件、部件、模块、整机;电 磁兼容元器件、材料、设备;微波 CAD、EDA 软件、开发测试仿真工具;微波、光纤仪器仪表。 欢迎国外高科技微波、光纤厂商将优秀产品介绍到中国、共同开拓市场。长期大量现货专业批发 高频、微波、卫星、光纤、电视、CATV 器件: 晶振、VCO、连接器、PIN 开关、变容二极管、开 关二极管、低噪晶体管、功率电阻及电容、放大器、功率管、MMIC、混频器、耦合器、功分器、 振荡器、合成器、衰减器、滤波器、隔离器、环行器、移相器、调制解调器;光电子元器件和组 件:红外发射管、红外接收管、光电开关、光敏管、发光二极管和发光二极管组件、半导体激光 二极管和激光器组件、光电探测器和光接收组件、光发射接收模块、光纤激光器和光放大器、光 调制器、光开关、DWDM 用光发射和接收器件、用户接入系统光光收发器件与模块、光纤连接器、 光纤跳线/尾纤、光衰减器、光纤适 配器、光隔离器、光耦合器、光环行器、光复用器/转换器; 无线收发芯片和模组、蓝牙芯片和模组。

更多产品请看本公司产品专用销售网站:

商斯达微波光电产品网:HTTP://www.rfoe.net/

商斯达中国传感器科技信息网: http://www.sensor-ic.com/

商斯达工控安防网: http://www.pc-ps.net/

商斯达电子元器件网: http://www.sunstare.com/

商斯达消费电子产品网://www.icasic.com/

商斯达实业科技产品网://www.sunstars.cn/ 射频微波光电元器件销售热线:

地址:深圳市福田区福华路福庆街鸿图大厦1602室

电话: 0755-83396822 83397033 83398585 82884100

传真: 0755-83376182 (0) 13823648918 MSN: SUNS8888@hotmail.com

邮编: 518033 E-mail:szss20@163.com QQ: 195847376

深圳赛格展销部: 深圳华强北路赛格电子市场 2583 号 电话: 0755-83665529 25059422 技术支持: 0755-83394033 13501568376

欢迎索取免费详细资料、设计指南和光盘;产品凡多,未能尽录,欢迎来电查询。

北京分公司:北京海淀区知春路 132 号中发电子大厦 3097 号

TEL: 010-81159046 82615020 13501189838 FAX: 010-62543996 上海分公司:上海市北京东路 668 号上海賽格电子市场 D125 号

TEL: 021-28311762 56703037 13701955389 FAX: 021-56703037

西安分公司:西安高新开发区 20 所(中国电子科技集团导航技术研究所)

西安劳动南路 88 号电子商城二楼 D23 号

TEL: 029-81022619 13072977981 FAX:029-88789382