## M6MGB/T64BS4AWG

67,108,864-BIT (4,194,304-WORD BY 16-BIT) CMOS FLASH MEMORY & 4,194,304-BIT (262,144-WORD BY 16-BIT) CMOS SRAM

Stacked-CSP (Chip Scale Package)

### Description

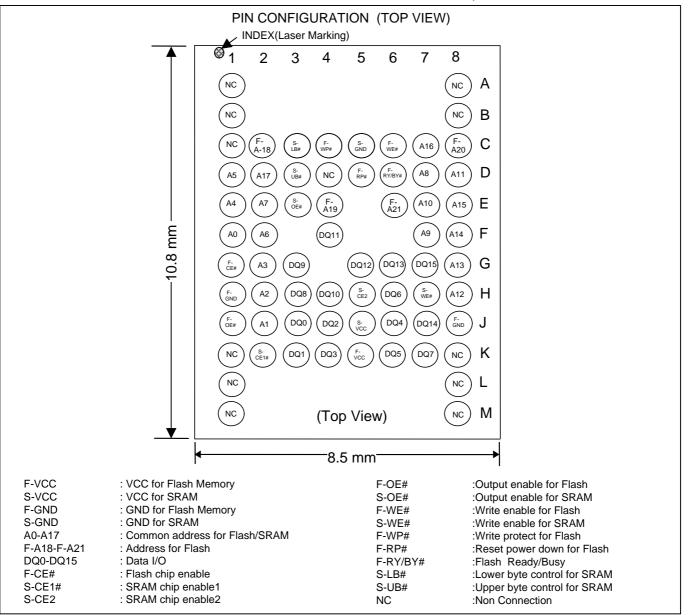

The M6MGB/T64BS4AWG is a Stacked Chip Scale Package (S-CSP) that contents 64M-bit Flash memory and 4M-bit SRAM in a 67-pin Stacked CSP for lead free use.

64M-bit Flash memory is a 4,194,304 words, single power supply and high performance non-volatile memory fabricated by CMOS technology for the peripheral circuit and DINOR IV (Divided bit-line NOR IV) architecture for the memory cell. All memory blocks are locked and can not be programmed or erased, when F-WP# is Low. Using Software Lock Release function, program or erase operation can be executed.

4M-bit SRAM is a 262,144 words asynchronous SRAM fabricated by CMOS technology for the peripheral circuit and TFT type transistor for the memory cell.

The M6MGB/T64BS4AWG is suitable for a high performance cellular phone and a mobile PC that are required to be small mounting area, weight and small power dissipation.

### Features

| Flash         |  |  |  |  |  |

|---------------|--|--|--|--|--|

| SRAM          |  |  |  |  |  |

| upply Voltage |  |  |  |  |  |

| SRAM          |  |  |  |  |  |

|               |  |  |  |  |  |

|               |  |  |  |  |  |

70ns (Max.) 85ns (Max.) F-VCC =S-VCC=2.7 ~ 3.0V Ta= -40 ~ 85 degree 67pin S-CSP, Ball pitch 0.80mm Outer-ball:Su-Ag-Cu

## Application

Mobile communication products

# M6MGB/T64BS4AWG

67,108,864-BIT (4,194,304-WORD BY 16-BIT) CMOS FLASH MEMORY & 4,194,304-BIT (262,144-WORD BY 16-BIT) CMOS SRAM

Stacked-CSP (Chip Scale Package)

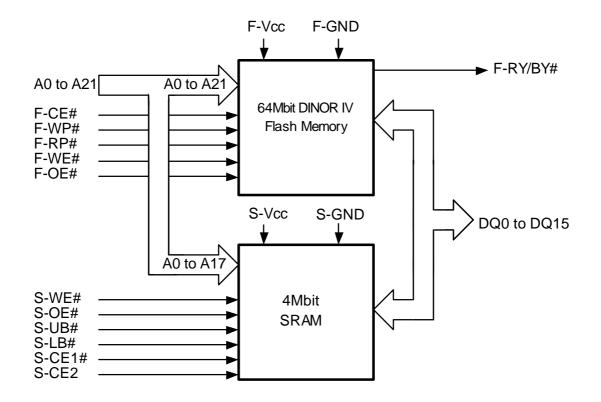

**MCP Block Diagram**

Note: In the Flash memory part there are "Vcc", "GND", "OE#" and "WE#" which mean "F-Vcc", "F-GND", "F-OE#" and "F-WE#", respectively. In the SRAM part there are "GND", "UB#", "LB#", "OE#" and "WE#" which mean "S-GND", "S-UB#", "S-LB#", "S-OE#" and "S-WE#", respectively.

## Capacitance

| Symbol | Parameter             | Conditions                                                                                   | Limits                          |      |      | Unit |    |

|--------|-----------------------|----------------------------------------------------------------------------------------------|---------------------------------|------|------|------|----|

| Cymbol | i didilotoi           |                                                                                              | Min.                            | Тур. | Max. | Onit |    |

| CIN    | Indut                 | A21-A0, F-OE#, F-WE#, F-CE#, F-WP#, F-<br>RP#, S-CE1#, S-CE2, S-OE#, S-WE#, S-<br>LB#, S-UB# | Ta=25°C, f=1MHz,<br>Vin=Vout=0V |      |      | 18   | pF |

| СОИТ   | Output<br>Capacitance | DQ15-DQ0, F-RY/BY#                                                                           |                                 |      |      | 22   | pF |

## M6MGB/T64BS4AWG

#### 67,108,864-BIT (4,194,304-WORD BY 16-BIT) CMOS FLASH MEMORY & 4,194,304-BIT (262,144-WORD BY 16-BIT) CMOS SRAM

Stacked-CSP (Chip Scale Package)

# RenesasTechnologyCorp.

Nippon Bldg.,6-2,Otemachi 2-chome,Chiyoda-ku,Tokyo,100-0004 Japan

### Keep safety first in your circuit designs!

- The products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

- Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

Please contact Renesas Technology Corporation for further details on these materials or the products contained therein.

#### REJ03C0066

© 2003 Renesas Technology Corp New publication, effective April 2003. Specifications subject to change without notice