Notice: This is not final specification. Some parametric limits are subject to change.

#### DESCRIPTION

The M5M5V5636UG is a family of 18M bit synchronous SRAMs organized as 524288-words by 36-bit. It is designed to eliminate dead bus cycles when turning the bus around between reads and writes, or writes and reads. Renesas's SRAMs are fabricated with high performance, low power CMOS technology, providing greater reliability. M5M5V5636UG operates on 3.3V power/ 2.5V I/O supply or a single 3.3V power supply and are 3.3V CMOS compatible.

#### **FEATURES**

- Fully registered inputs and outputs for pipelined operation

- Fast clock speed: 200 MHz

- Fast access time: 3.2ns

- Single 3.3V -5% and +5% power supply VDD

- Separate VDDQ for 3.3V or 2.5V I/O

- Individual byte write (BWa# BWd#) controls may be tied I OW

- Single Read/Write control pin (W#)

- CKE# pin to enable clock and suspend operations

- · Internally self-timed, registers outputs eliminate the need to control G#

- Snooze mode (ZZ) for power down

- Linear or Interleaved Burst Modes

- Three chip enables for simple depth expansion

- JTAG boundary scan support

#### **Package**

165(11x15) bump BGA Body Size (13mm x 15mm) **Bump Pitch 1.0mm**

### **PART NAME TABLE**

| Part Name        | Access | Cycle | Active Current (max.) | Standby Current (max.) |

|------------------|--------|-------|-----------------------|------------------------|

| M5M5V5636UG - 20 | 3.2ns  | 5.0ns | 450mA                 | 30mA                   |

### **APPLICATION**

High-end networking products that require high bandwidth, such as switches and routers.

#### **FUNCTION**

Synchronous circuitry allows for precise cycle control triggered by a positive edge clock transition.

Synchronous signals include: all Addresses, all Data Inputs, all Chip Enables (E1#, E2, E3#), Address Advance/Load (ADV), Clock Enable (CKE#), Byte Write Enables (BWa#, BWb#, BWc#, BWd#) and Read/Write (W#). Write operations are controlled by the four Byte Write Enables (BWa# - BWd#) and Read/Write(W#) inputs. All writes are conducted with on-chip synchronous self-timed write circuitry.

Asynchronous inputs include Output Enable (G#), Clock (CLK) and Snooze Enable (ZZ). The HIGH input of ZZ pin puts the SRAM in the power-down state. The Linear Burst order (LBO#) is DC operated pin. LBO# pin will allow the choice of either an interleaved burst, or a linear burst.

All read, write and deselect cycles are initiated by the ADV LOW input. Subsequent burst address can be internally generated as controlled by the ADV HIGH input.

## **BUMP LAYOUT(TOP VIEW)**

## 165bump-BGA

|   | 1    | 2          | 3          | 4          | 5    | 6          | 7    | 8           | 9           | 10          | 11          |

|---|------|------------|------------|------------|------|------------|------|-------------|-------------|-------------|-------------|

| Α | NC   | <b>A</b> 7 | E1#        | BWc#       | BWb# | E3#        | CKE# | ADV         | <b>A</b> 17 | <b>A</b> 8  | NC          |

| В | NC   | <b>A</b> 6 | E2         | BWd#       | BWa# | CLK        | W#   | G#          | <b>A</b> 18 | <b>A</b> 9  | NC          |

| С | DQPc | NC         | VDDQ       | Vss        | Vss  | Vss        | Vss  | Vss         | VDDQ        | NC          | DQPb        |

| D | DQc  | DQc        | VDDQ       | VDD        | Vss  | Vss        | Vss  | VDD         | VDDQ        | DQb         | DQb         |

| Е | DQc  | DQc        | VDDQ       | VDD        | Vss  | Vss        | Vss  | VDD         | VDDQ        | DQb         | DQb         |

| F | DQc  | DQc        | VDDQ       | VDD        | Vss  | Vss        | Vss  | VDD         | VDDQ        | DQb         | DQb         |

| G | DQc  | DQc        | VDDQ       | VDD        | Vss  | Vss        | Vss  | VDD         | VDDQ        | DQb         | DQb         |

| Н | МСН  | MCH        | NC         | VDD        | Vss  | Vss        | Vss  | VDD         | NC          | NC          | ZZ          |

| J | DQd  | DQd        | VDDQ       | VDD        | Vss  | Vss        | Vss  | VDD         | VDDQ        | DQa         | DQa         |

| K | DQd  | DQd        | VDDQ       | VDD        | Vss  | Vss        | Vss  | VDD         | VDDQ        | DQa         | DQa         |

| L | DQd  | DQd        | VDDQ       | VDD        | Vss  | Vss        | Vss  | VDD         | VDDQ        | DQa         | DQa         |

| М | DQd  | DQd        | VDDQ       | VDD        | Vss  | Vss        | Vss  | VDD         | VDDQ        | DQa         | DQa         |

| N | DQPd | NC         | VDDQ       | Vss        | NC   | NC         | МСН  | Vss         | VDDQ        | NC          | DQPa        |

| Р | NC   | NC         | <b>A</b> 5 | Аз         | TDI  | <b>A</b> 1 | TDO  | <b>A</b> 15 | <b>A</b> 13 | <b>A</b> 11 | NC          |

| R | LBO# | NC         | <b>A</b> 4 | <b>A</b> 2 | TMS  | Α0         | тск  | <b>A</b> 16 | <b>A</b> 14 | <b>A</b> 12 | <b>A</b> 10 |

Note1. MCH means "Must Connect High". MCH should be connected to HIGH.

18874368-BIT(524288-WORD BY 36-BIT) NETWORK SRAM

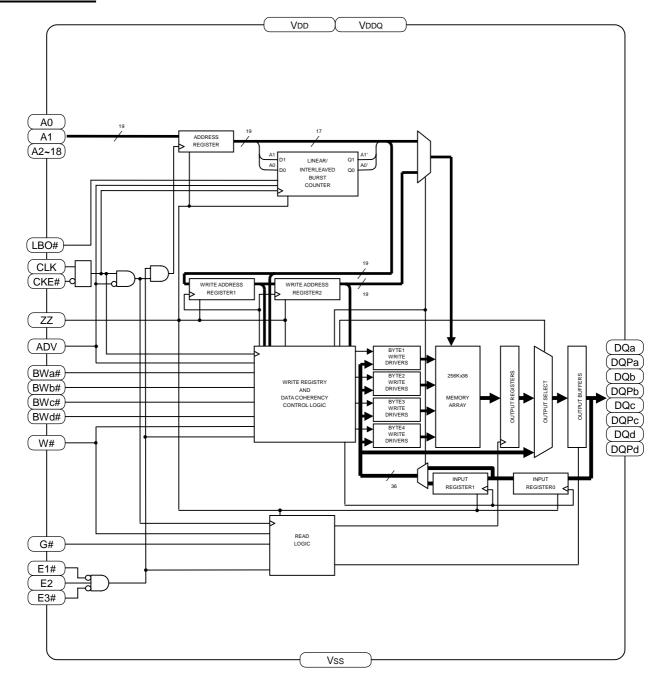

### **BLOCK DIAGRAM**

Note2. The BLOCK DIAGRAM does not include the Boundary Scan logic. See Boundary Scan chapter.

Note3. The BLOCK DIAGRAM illustrates simplified device operation. See TRUTH TABLE, PIN FUNCTION and timing diagrams for detailed information.

18874368-BIT(524288-WORD BY 36-BIT) NETWORK SRAM

## **PIN FUNCTION**

| Pin                                    | Name                                   | Function                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0~A18                                 | Synchronous<br>Address<br>Inputs       | These inputs are registered and must meet the setup and hold times around the rising edge of CLK. A0 and A1 are the two least significant bits (LSB) of the address field and set the internal burst counter if burst is desired.                                                                                                                                                                                         |

| BWa#, BWb#,<br>BWc#, BWd#              | Synchronous<br>Byte Write<br>Enables   | These active LOW inputs allow individual bytes to be written when a WRITE cycle is active and must meet the setup and hold times around the rising edge of CLK. BYTE WRITEs need to be asserted on the same cycle as the address. BWs are associated with addresses and apply to subsequent data. BWa# controls DQa, DQPa pins; BWb# controls DQb, DQPb pins; BWc# controls DQc, DQPc pins; BWd# controls DQd, DQPd pins. |

| CLK                                    | Clock Input                            | This signal registers the address, data, chip enables, byte write enables and burst control inputs on its rising edge. All synchronous inputs must meet setup and hold times around the clock's rising edge.                                                                                                                                                                                                              |

| E1#                                    | Synchronous<br>Chip Enable             | This active LOW input is used to enable the device and is sampled only when a new external address is loaded (ADV is LOW).                                                                                                                                                                                                                                                                                                |

| E2                                     | Synchronous<br>Chip Enable             | This active High input is used to enable the device and is sampled only when a new external address is loaded (ADV is LOW). This input can be used for memory depth expansion.                                                                                                                                                                                                                                            |

| E3#                                    | Synchronous<br>Chip Enable             | This active Low input is used to enable the device and is sampled only when a new external address is loaded (ADV is LOW). This input can be used for memory depth expansion.                                                                                                                                                                                                                                             |

| G#                                     | Output Enable                          | This active LOW asynchronous input enable the data I/O output drivers.                                                                                                                                                                                                                                                                                                                                                    |

| ADV                                    | Synchronous<br>Address<br>Advance/Load | When HIGH, this input is used to advance the internal burst counter, controlling burst access after the external address is loaded. When HIGH, W# is ignored. A LOW on this pin permits a new address to be loaded at CLK rising edge.                                                                                                                                                                                    |

| CKE#                                   | Synchronous<br>Clock Enable            | This active LOW input permits CLK to propagate throughout the device. When HIGH, the device ignores the CLK input and effectively internally extends the previous CLK cycle. This input must meet setup and hold times around the rising edge of CLK.                                                                                                                                                                     |

| ZZ                                     | Snooze<br>Enable                       | This active HIGH asynchronous input causes the device to enter a low-power standby mode in which all data in the memory array is retained. When active, all other inputs are ignored. When this pin is LOW or NC, the SRAM normally operates.                                                                                                                                                                             |

| W#                                     | Synchronous<br>Read/Write              | This active input determines the cycle type when ADV is LOW. This is the only means for determining READs and WRITEs. READ cycles may not be converted into WRITEs (and vice versa) other than by loading a new address. A LOW on the pin permits BYTE WRITE operations and must meet the setup and hold times around the rising edge of CLK. Full bus width WRITEs occur if all byte write enables are LOW.              |

| DQa,DQPa,DQb,DQPb<br>DQc,DQPc,DQd,DQPd | Synchronous<br>Data I/O                | Byte "a" is DQa, DQPa pins; Byte "b" is DQb, DQPb pins; Byte "c" is DQc, DQPc pins; Byte "d" is DQd,DQPd pins. Input data must meet setup and hold times around CLK rising edge.                                                                                                                                                                                                                                          |

| LBO#                                   | Burst Mode<br>Control                  | This DC operated pin allows the choice of either an interleaved burst or a linear burst. If this pin is HIGH or NC, an interleaved burst occurs. When this pin is LOW, a linear burst occurs, and input leak current to this pin.                                                                                                                                                                                         |

| VDD                                    | VDD                                    | Core Power Supply                                                                                                                                                                                                                                                                                                                                                                                                         |

| Vss                                    | Vss                                    | Ground                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VDDQ                                   | VDDQ                                   | I/O buffer Power supply                                                                                                                                                                                                                                                                                                                                                                                                   |

| TDI                                    | Test Data Input                        |                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TDO                                    | Test Data Output                       | These pins are used for Boundary Scan Test.                                                                                                                                                                                                                                                                                                                                                                               |

| TCK                                    | Test Clock                             | and accessed Boundary Court 1000.                                                                                                                                                                                                                                                                                                                                                                                         |

| TMS                                    | Test Mode Select                       |                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MCH                                    | Must Connect High                      | These pins should be connected to HIGH                                                                                                                                                                                                                                                                                                                                                                                    |

| NC                                     | No Connect                             | These pins are not internally connected and may be connected to ground.                                                                                                                                                                                                                                                                                                                                                   |

18874368-BIT(524288-WORD BY 36-BIT) NETWORK SRAM

#### **DC OPERATED TRUTH TABLE**

| Name | Input Status | Operation                  |

|------|--------------|----------------------------|

| LBO# | HIGH or NC   | Interleaved Burst Sequence |

| LBO# | LOW          | Linear Burst Sequence      |

Note4. LBO# is DC operated pin.

Note5. NC means No Connection.

Note6. See BURST SEQUENCE TABLE about interleaved and Linear Burst Sequence.

## **BURST SEQUENCE TABLE**

Interleaved Burst Sequence (when LBO# = HIGH or NC)

| Operation                            | A18~A2         |       | A1,A0 |     |     |  |

|--------------------------------------|----------------|-------|-------|-----|-----|--|

| First access, latch external address | A18~A2         | 0,0   | 0,1   | 1,0 | 1,1 |  |

| Second access(first burst address)   | latched A18~A2 | 0 , 1 | 0,0   | 1,1 | 1,0 |  |

| Third access(second burst address)   | latched A18~A2 | 1,0   | 1,1   | 0,0 | 0,1 |  |

| Fourth access(third burst address)   | latched A18~A2 | 1,1   | 1,0   | 0,1 | 0,0 |  |

#### Linear Burst Sequence (when LBO# = LOW)

| Operation                            | A18~A2         | A1,A0 |       |       |       |

|--------------------------------------|----------------|-------|-------|-------|-------|

| First access, latch external address | A18~A2         | 0,0   | 0 , 1 | 1,0   | 1 , 1 |

| Second access(first burst address)   | latched A18~A2 | 0 , 1 | 1,0   | 1 , 1 | 0,0   |

| Third access(second burst address)   | latched A18~A2 | 1,0   | 1 , 1 | 0,0   | 0 , 1 |

| Fourth access(third burst address)   | latched A18~A2 | 1,1   | 0,0   | 0 , 1 | 1,0   |

Note7. The burst sequence wraps around to its initial state upon completion.

### **TRUTH TABLE**

| E1# | E2 | E3# | ZZ | ADV | W# | BWx# | G# | CKE# | CLK  | DQ     | Address<br>used | Operation                    |

|-----|----|-----|----|-----|----|------|----|------|------|--------|-----------------|------------------------------|

| Н   | Χ  | Χ   | L  | L   | Χ  | Х    | Χ  | L    | L->H | High-Z | None            | Deselect Cycle               |

| Χ   | L  | Х   | L  | L   | X  | X    | Χ  | L    | L->H | High-Z | None            | Deselect Cycle               |

| Х   | Χ  | Н   | L  | L   | Χ  | Χ    | Χ  | L    | L->H | High-Z | None            | Deselect Cycle               |

| Х   | Χ  | Χ   | L  | Н   | Χ  | Х    | Χ  | L    | L->H | High-Z | None            | Continue Deselect Cycle      |

| L   | Н  | L   | L  | L   | Н  | Х    | L  | L    | L->H | Q      | External        | Read Cycle, Begin Burst      |

| Х   | Χ  | Х   | L  | Н   | Χ  | Х    | L  | L    | L->H | Q      | Next            | Read Cycle, Continue Burst   |

| L   | Н  | L   | L  | L   | Н  | Χ    | Н  | L    | L->H | High-Z | External        | NOP/Dummy Read, Begin Burst  |

| Χ   | Χ  | Χ   | L  | Η   | Χ  | Χ    | Н  | L    | L->H | High-Z | Next            | Dummy Read, Continue Burst   |

| L   | Н  | L   | L  | L   | L  | L    | Χ  | L    | L->H | D      | External        | Write Cycle, Begin Burst     |

| Х   | Χ  | Χ   | L  | Н   | Χ  | L    | Χ  | L    | L->H | D      | Next            | Write Cycle, Continue Burst  |

| L   | Ι  | L   | L  | L   | Ш  | Η    | Χ  | L    | L->H | High-Z | None            | NOP/Write Abort, Begin Burst |

| Х   | Χ  | Χ   | L  | Η   | Χ  | Η    | Χ  | L    | L->H | High-Z | Next            | Write Abort, Continue Burst  |

| Х   | Χ  | Χ   | L  | Х   | Χ  | Х    | Χ  | Н    | L->H | -      | Current         | Ignore Clock edge, Stall     |

| Х   | Χ  | Χ   | Н  | Х   | Χ  | Х    | Χ  | Х    | Χ    | High-Z | None            | Snooze Mode                  |

Note8. "H" = input VIH; "L" = input VIL; "X" = input VIH or VIL.

Note9. BWx#=H means all Synchronous Byte Write Enables (BWa#,BWb#,BWc#,BWd#) are HIGH. BWx#=L means one or more Synchronous Byte Write Enables are LOW.

Note10. All inputs except G# and ZZ must meet setup and hold times around the rising edge (LOW to HIGH) of CLK.

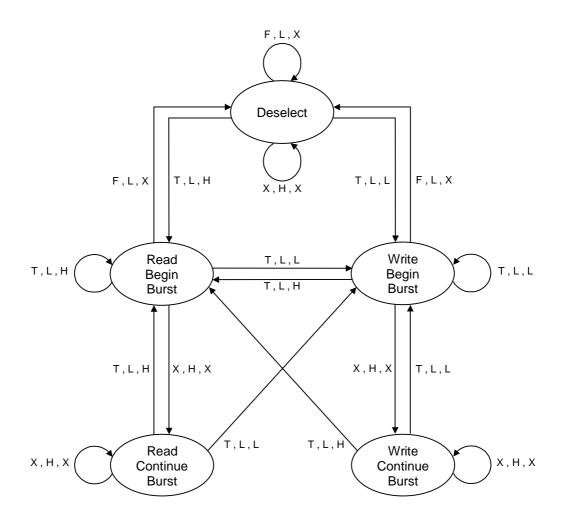

## **STATE DIAGRAM**

Note11. The notation "x , x , x" controlling the state transitions above indicate the state of inputs E, ADV and W# respectively. Note12. If (E1# = L and E2 = H and E3# = L) then E="T" else E="F". Note13. "H" = input VIH; "L" = input VIL; "X" = input VIH or VIL; "T" = input "true"; "F" = input "false".

18874368-BIT(524288-WORD BY 36-BIT) NETWORK SRAM

## **WRITE TRUTH TABLE**

| W# | BWa# | BWb# | BWc# | BWd# | Function        |

|----|------|------|------|------|-----------------|

| Н  | Х    | Х    | Х    | Х    | Read            |

| L  | L    | Н    | Н    | Н    | Write Byte a    |

| L  | Н    | L    | Н    | Н    | Write Byte b    |

| L  | Н    | Н    | L    | Н    | Write Byte c    |

| L  | Н    | Н    | Н    | L    | Write Byte d    |

| L  | L    | Ĺ    | Ĺ    | Ĺ    | Write All Bytes |

| L  | Н    | Н    | Н    | Н    | Write Abort/NOP |

Note14. "H"=input VIH; "L"=input VIL; "X"=input VIH or VIL.

Note15. All inputs except G# and ZZ must meet setup and hold times around the rising edge (LOW to HIGH) of CLK.

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol     | Parameter                       | Conditions          | Ratings         | Unit |

|------------|---------------------------------|---------------------|-----------------|------|

| Vdd        | Power Supply Voltage            |                     | -1.0*~4.6       | V    |

| VDDQ       | I/O Buffer Power Supply Voltage | With rear at to Voc | -1.0*~4.6       | V    |

| VI         | Input Voltage                   | With respect to Vss | -1.0~VDDQ+1.0** | V    |

| Vo         | Output Voltage                  | ]                   | -1.0~VDDQ+1.0** | V    |

| PD         | Maximum Power Dissipation (VDD) |                     | 1180            | mW   |

| Topr       | Operating Temperature           |                     | 0~70            | °C   |

| TSTG(bias) | Storage Temperature(bias)       |                     | -10~85          | °C   |

| TSTG       | Storage Temperature             |                     | -55~125         | °C   |

Note16.\* This is −1.0V when pulse width≤2ns, and −0.5V in case of DC.

\*\* This is −1.0V~VDDQ+1.0V when pulse width≤2ns, and −0.5V~VDDQ+0.5V in case of DC.

18874368-BIT(524288-WORD BY 36-BIT) NETWORK SRAM

## DC ELECTRICAL CHARACTERISTICS (Ta=0~70°C, VDD=3.135~3.465V, unless otherwise noted)

| Cumala al | Davamatas                                       | Condition                                                                                       | Lir      | nits      | I I m i f |

|-----------|-------------------------------------------------|-------------------------------------------------------------------------------------------------|----------|-----------|-----------|

| Symbol    | Parameter                                       | Condition                                                                                       | Min      | Max       | Unit      |

| Vdd       | Power Supply Voltage                            |                                                                                                 | 3.135    | 3.465     | V         |

| \/ppc     | L/O De ff and Daniel and Outside Notice         | VDDQ = 3.3V                                                                                     | 3.135    | 3.465     | V         |

| VDDQ      | I/O Buffer Power Supply Voltage                 | VDDQ = 2.5V                                                                                     | 2.375    | 2.625     | V         |

| VIH       | Lligh level leavet Valtage                      | VDDQ = 3.135~3.465V                                                                             | 2.0      | VDDQ+0.3* | V         |

| VIH       | High-level Input Voltage                        | VDDQ = 2.375~2.625V                                                                             |          | VDDQ+0.3  | V         |

| \ /!!     | Lave lavel land Valtage                         | VDDQ = 3.135~3.465V                                                                             | 0.0*     | 0.8       | V         |

| VIL       | Low-level Input Voltage                         | VDDQ = 2.375~2.625V                                                                             | -0.3*    | 0.7       | V         |

| Voн       | High-level Output Voltage                       | IOH = -2.0mA                                                                                    | VDDQ-0.4 |           | V         |

| Vol       | Low-level Output Voltage                        | IOL = 2.0mA                                                                                     |          | 0.4       | V         |

| _         | Input Leakage Current except ZZ and LBO#        | VI = 0V ~ VDDQ                                                                                  |          | 10        | μA        |

| ILI       | Input Leakage Current of LBO#                   | VI = 0V ~ VDDQ                                                                                  |          | 100       |           |

|           | Input Leakage Current of ZZ                     | VI = 0V ~ VDDQ                                                                                  |          | 100       |           |

| ILO       | Off-state Output Current                        | VI (G#) ≥ VIH, VO = 0V ~ VDDQ                                                                   |          | 10        | μΑ        |

| ICC1      | Power Supply Current : Operating                | Device selected;<br>Output Open, Vı≤Vı∟ or Vı≥Vıн, ZZ≤Vı∟                                       |          | 450       | mA        |

| ICC2      | Power Supply Current : Deselected               | Device deselected<br>VI≤VIL or VI≥VIH, ZZ≤VIL                                                   |          | 180       | mA        |

| ICC3      | CMOS Standby Current (CLK stopped standby mode) | Device deselected; Output Open VI≤Vss+0.2V or VI≥VDDQ-0.2V CLK frequency=0Hz, All inputs static |          | 30        | mA        |

| ICC4      | Snooze Mode Standby Current                     | Snooze mode<br>ZZ≥VDDQ-0.2V, LBO#≥VDD-0.2V                                                      |          | 30        | mA        |

| ICC5      | Stall Current                                   | Device selected;<br>Output Open, CKE#≥VIH<br>VI≤VSS+0.2V or VI≥VDDQ-0.2V                        |          | 140       | mA        |

Note17.\*VILmin is −1.0V and VIH max is VDDQ+1.0V in case of AC(Pulse width≤2ns).

Note18. "Device Deselected" means device is in power-down mode as defined in the truth table.

## **CAPACITANCE**

| Symbol | Parameter                      | Conditions                 |     | Unit |     |      |

|--------|--------------------------------|----------------------------|-----|------|-----|------|

|        | Farameter                      | Conditions                 | Min | Тур  | Max | Unit |

| Cı     | Input Capacitance              | Vi=GND, Vi=25mVrms, f=1MHz |     |      | 6   | pF   |

| Со     | Input / Output(DQ) Capacitance | Vo=GND, Vo=25mVrms, f=1MHz |     |      | 8   | pF   |

Note19. This parameter is sampled.

#### THERMAL RESISTANCE

#### 4-Layer PC board mounted (70x70x1.6mmT)

| Symbol      | Parameter                           | Conditions            |     | Unit |     |       |

|-------------|-------------------------------------|-----------------------|-----|------|-----|-------|

| Syllibol    | Faranietei                          | Conditions            | Min | Тур  | Max | Oilit |

| $\theta$ JA | Thermal Resistance Junction Ambient | Air velocity=0m/sec   |     | 28   |     | °C/W  |

|             |                                     | Air velocity=0.5m/sec |     | 24   |     |       |

|             |                                     | Air velocity=1m/sec   |     | 22   |     |       |

|             |                                     | Air velocity=2m/sec   |     | 20   |     |       |

|             |                                     | Air velocity=5m/sec   |     | 17   |     | °C/W  |

| θις         | Thermal Resistance Junction to Case |                       |     | 4    |     | °C/W  |

Note20. This parameter is sampled.

Systems must be designed to keep Tj below 105 degree C.

Tj: SRAM Junction temperature  $Tj(^{\circ}C)=Ta(^{\circ}C) + \theta JA(^{\circ}C/W) \times Pd(W)$

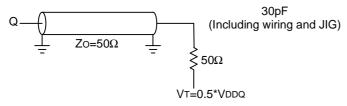

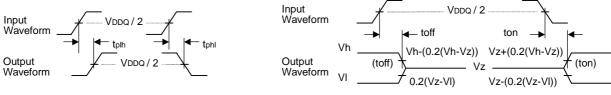

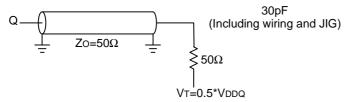

## <u>AC ELECTRICAL CHARACTERISTICS</u> (Ta=0~70°C, VDD=3.135~3.465V, unless otherwise noted) (1)MEASUREMENT CONDITION

Input pulse levels ......VIH=VDDQ, VIL=0V

Input rise and fall times ...... faster than or equal to 1V/ns

Input timing reference levels ....................VIH=VIL=0.5\*VDDQ

Output reference levels ......VIH=VIL=0.5\*VDDQ

Output load -----Fig.1

Fig.1 Output load

Fig.2 Tdly measurement

Fig.3 Tri-State measurement

- Note21. Valid Delay Measurement is made from the VDDQ/2 on the input waveform to the VDDQ/2 on the output waveform. Input waveform should have a slew rate of faster than or equal to 1V/ns.

- Note22.Tri-state toff measurement is made from the VDDQ/2 on the input waveform to the output waveform moving 20% from its initial to final Value VDDQ/2.

Note:the initial value is not VoL or Voн as specified in DC ELECTRICAL CHARACTERISTICS table.

Note23. Tri-state ton measurement is made from the VDDQ/2 on the input waveform to the output waveform moving 20% from its initial Value VDDQ/2 to its final Value.

Note: the final value is not Vol or Voh as specified in DC ELECTRICAL CHARACTERISTICS table.

Note24.Clocks,Data,Address and control signals will be tested with a minimum input slew rate of faster than or equal to 1V/ns.

18874368-BIT(524288-WORD BY 36-BIT) NETWORK SRAM

## (2)TIMING CHARACTERISTICS

|              |                                              | Lir | nits    |       |

|--------------|----------------------------------------------|-----|---------|-------|

| Symbol       | Parameter                                    | 200 | MHz     | Unit  |

| Symbol       | Farameter                                    | -   | 20      | Ullit |

|              |                                              | Min | Max     |       |

| Clock        |                                              |     |         |       |

| tkhkh        | Clock cycle time                             | 5.0 |         | ns    |

| tKHKL        | Clock HIGH time                              | 2.0 |         | ns    |

| tklkh        | Clock LOW time                               | 2.0 |         | ns    |

| Output times | 3                                            |     |         |       |

| tkhqv        | Clock HIGH to output valid                   |     | 3.2     | ns    |

| tkhqx        | Clock HIGH to output invalid                 | 1.5 |         | ns    |

| tKHQX1       | Clock HIGH to output in LOW-Z                | 1.5 |         | ns    |

| tKHQZ        | Clock HIGH to output in High-Z               | 1.5 | 3.2     | ns    |

| tGLQV        | G# to output valid                           |     | 3.2     | ns    |

| tGLQX1       | G# to output in Low-Z                        | 0.0 |         | ns    |

| tGHQZ        | G# to output in High-Z                       |     | 3.2     | ns    |

| Setup times  |                                              |     |         |       |

| tavkh        | Address valid to clock HIGH                  | 1.0 |         | ns    |

| tckeVKH      | CKE# valid to clock HIGH                     | 1.0 |         | ns    |

| tadvVKH      | ADV valid to clock HIGH                      | 1.0 |         | ns    |

| tw∨kH        | Write valid to clock HIGH                    | 1.0 |         | ns    |

| tв∨кн        | Byte write valid to clock HIGH (BWa#~BWd#)   | 1.0 |         | ns    |

| tevkh        | Enable valid to clock HIGH (E1#,E2,E3#)      | 1.0 |         | ns    |

| tDVKH        | Data In valid clock HIGH                     | 1.0 |         | ns    |

| Hold times   |                                              |     |         |       |

| tKHAX        | Clock HIGH to Address don't care             | 0.8 |         | ns    |

| tKHckeX      | Clock HIGH to CKE# don't care                | 0.8 |         | ns    |

| tKHadvX      | Clock HIGH to ADV don't care                 | 0.8 |         | ns    |

| tkhwx        | Clock HIGH to Write don't care               | 0.8 |         | ns    |

| tkhbx        | Clock HIGH to Byte Write don't care          | 0.8 |         | ne    |

| INIDA        | (BWa#~BWb#)                                  |     |         | ns    |

| tKHEX        | Clock HIGH to Enable don't care (E1#,E2,E3#) | 0.8 |         | ns    |

| tkhdx        | Clock HIGH to Data In don't care             | 0.8 |         | ns    |

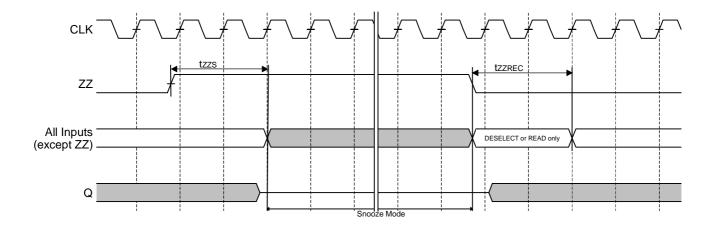

| ZZ           |                                              |     |         |       |

| tzzs         | ZZ standby                                   |     | 2*tкнкн | ns    |

| tzzrec       | ZZ recovery                                  |     | 2*tкнкн | ns    |

Note25.All parameter except tzzs, tzzrec in this table are measured on condition that ZZ=LOW fix.

Note26.Test conditions is specified with the output loading shown in Fig.1 unless otherwise noted.

Note27. tkHQX1, tkHQZ, tGLQX1, tGHQZ are sampled.

Note28.LBO# is static and must not change during normal operation.

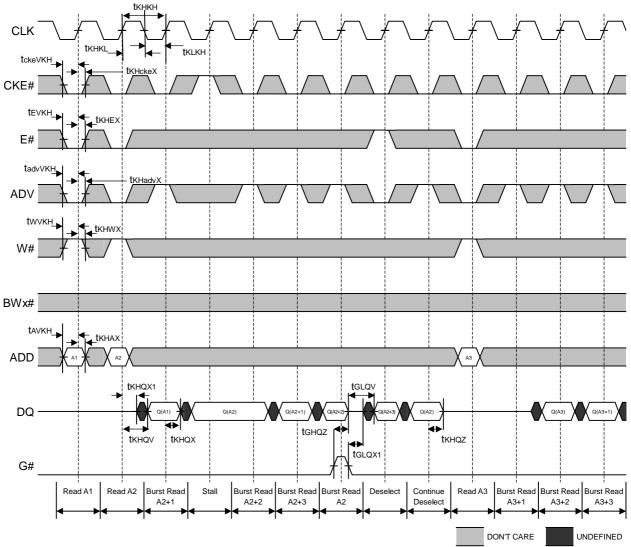

## (3)READ TIMING

Note29.Q(An) refers to output from address An. Q(An+1) refers to output from the next internal burst address following An. Note30. E# represents three signals. When E# is LOW, it represents E1# is LOW, E2 is HIGH and E3# is LOW. Note31.ZZ is fixed LOW.

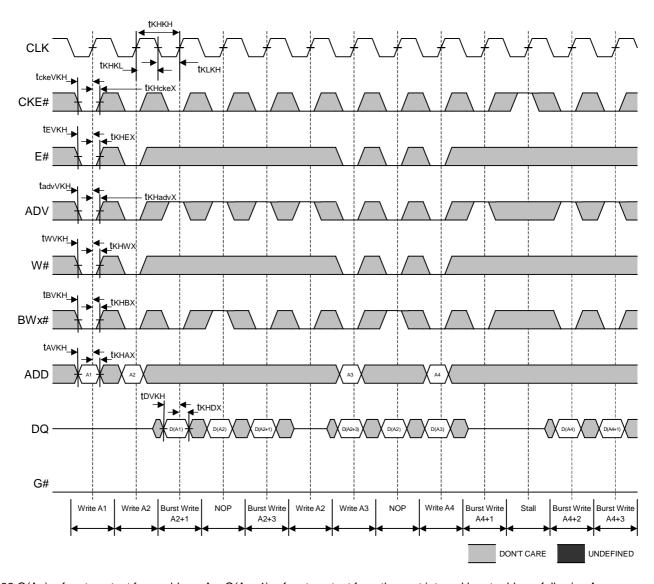

## (4)WRITE TIMING

Note32.Q(An) refers to output from address An. Q(An+1) refers to output from the next internal burst address following An. Note33. E# represents three signals. When E# is LOW, it represents E1# is LOW, E2 is HIGH and E3# is LOW. Note34.ZZ is fixed LOW.

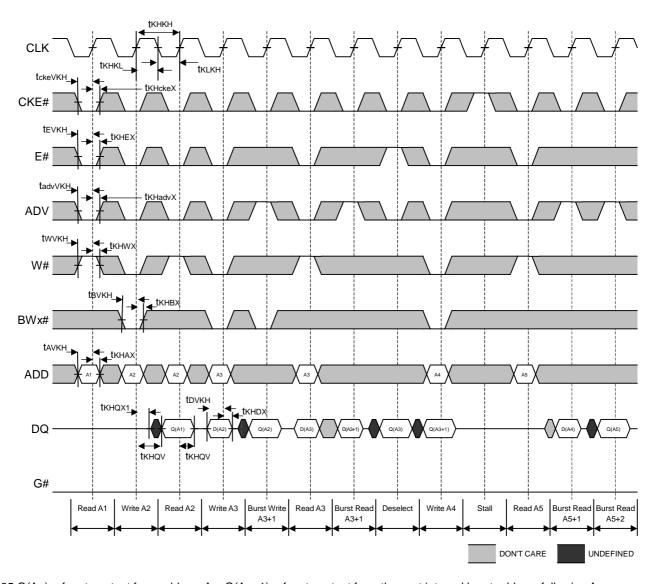

## (5)READ/WRITE TIMING

Note35.Q(An) refers to output from address An. Q(An+1) refers to output from the next internal burst address following An. Note36. E# represents three signals. When E# is LOW, it represents E1# is LOW, E2 is HIGH and E3# is LOW. Note37.ZZ is fixed LOW.

18874368-BIT(524288-WORD BY 36-BIT) NETWORK SRAM

## (6) SNOOZE MODE TIMING

18874368-BIT(524288-WORD BY 36-BIT) NETWORK SRAM

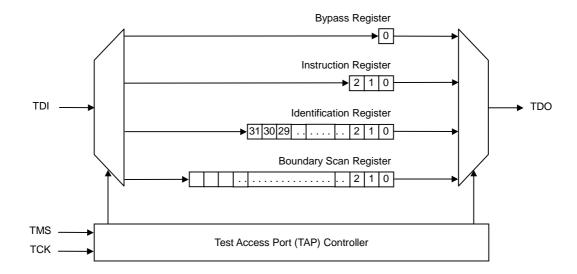

#### JTAG PORT OPERATION

#### Overview

The JTAG Port on this SRAM operates in a manner consistent with IEEE Standard 1149.1-1990, a serial boundary scan interface standard (commonly referred to as JTAG), but dose not implement all of the function required for 1149.1 compliance. The JTAG Port interfaces with conventional CMOS logic level signaling.

#### Disabling the JTAG port

It is possible to use this device without utilizing the JTAG port. The port is reset at power-up and will remain inactive unless clocked. To assure normal operation of the SRAM with the JTAG Port unused, the TCK, TDI and TMS pins may be left floating or tied to High. The TDO pin should be left unconnected.

### **JTAG Pin Description**

#### **Test Clock (TCK)**

The TCK input is clock for all TAP events. All inputs are captured on the rising edge of TCK and the Test Data Out (TDO) propagates from the falling edge of TCK.

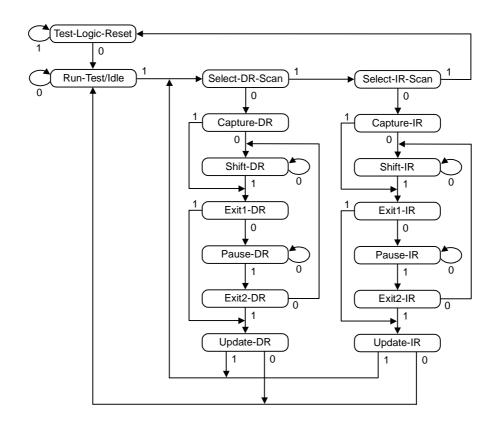

#### **Test Mode Select (TMS)**

The TMS input is sampled on the rising edge of TCK. This is the command input for the TAP Controller state machine. An undriven TMS input will produce the same result as a logic one input level.

#### Test Data In (TDI)

The TDI input is sampled on the rising edge of TCK. This is the input side of the serial registers placed between the TDI and TDO pins. the register placed between the TDI and TDO pins is determined by the state of the TAP Controller state machine and the instruction that is currently loaded in the TAP Instruction Resister (refer to the TAP Controller State Diagram). An undriven TDI Input will produce the same result as a logic one input level.

### Test Data Out (TDO)

The TDO output is active depending on the state of the TAP Controller state machine. Output changes in response to the falling edge of TCK. This is the output side of the serial registers placed between the TDI and TDO pins.

### Note:

This device dose not have a TRST (TAP Reset) pin. TRST is optional in IEEE 1149.1. The Test-Logic-Reset state is entered while TMS is held high for five rising edges of TCK. The TAP Controller is also reset automatically at power-up.

### **JTAG Port Registers**

#### Overview

The various JTAG registers, referred to as Test Access Port or TAP Registers, are selected (one at a time) via the sequence of 1s and 0s applied to TMS as TCK is strobed. Each of TAP Registers are serial shift registers that capture serial input data on the rising edge of TCK and push serial data out on the next falling edge of TCK. When a register is selected, it is placed between the TDI and TDO pins.

#### Instruction Register

The Instruction Register holds the instructions that are executed by the TAP Controller when it is moved into the Run-Test/Idle, or the various data register states. Instructions are 3 bits long. The Instruction Resister can be loaded when it is placed between the TDI and TDO pins. The Instruction Resister is automatically preloaded with the IDCODE instruction at power-up or whenever the controller is placed in Test-Logic-Reset state.

### Renesas LSIs

## M5M5V5636UG - 20

18874368-BIT(524288-WORD BY 36-BIT) NETWORK SRAM

#### **Bypass Register**

The Bypass resister is a single-bit register that can be placed between the TDI and TDO pins. It allows serial test data to be passed through the SRAM's JTAG Port to another device in the scan chain with as little delay as possible.

#### **Boundary Scan Register**

The Boundary Scan Register is a collection of flip flops that can be preset by the logic level found on the SRAM's input or I/O pins. The flip flops are then daisy chained together so the levels found can be shifted serially out of the JTAG Port's TDO pins. The relationship between the device pins and the bits in the Boundary Scan Register is described in the Scan Order Table following. The Boundary Scan Register, under the control of the TAP Controller, is loaded with the contents of the SRAM's I/O ring when the controller is in the Capture-RD state and then is placed between the TDI and TDO pins when the controller is moved to the Shift-DR state. SAMPLE-Z, SAMPLE/PRELOAD and EXTEST instruction can be used to activate the Boundary Scan Register.

#### Identification (ID) Register

The ID register is a 32-bit register that is loaded with a device and vender specific 32-bit code when the controllers put in the Capture-DR state with the IDCODE Instruction loaded in the Instruction Register. The code is loaded from 32-bit on-chip ROM. It describes various attributes of the SRAM (see page 20). The register is then placed between the TDI and TDO pins when the controller is moved into Shift-DR state. Bit 0 in the register is the LSB and the first to reach the TDO pin when shifting begins.

#### **TAP Controller Instruction Set**

#### Overview

There are two classes of instructions defined in the Standard 1149.1-1990; standard (Public) instructions, and device specific (Private) instructions. Some public instructions are mandatory for 1149.1 compliance. Optional Public instructions must be implemented in prescribed ways. The TAP Controller in this device is not fully 1194.1-compliant because some of the mandatory 1149.1 instructions are not fully implemented. The TAP on this device may be used to monitor all input and I/O pads. This device will not perform INTEST or PRELOAD portion of the SAMPLE/PRELOAD command.

When the TAP controller is placed in the Shift-IR state, the Instruction Register is placed between the TDI and TDO pins. In this state the desired instruction is serially loaded through the TDI input (while the previous contents are shifted out at the TDO output). For all instructions, the TAP executes newly loaded instructions only when the controller is moved to the Update-IR state. The TAP Instruction Set for this device is listed in the following table.

### **Instruction Descriptions**

#### **BYPASS**

When the BYPASS instruction is loaded in the Instruction Register, the Bypass Register is placed between the TDI and TDO pins. This occurs when the TAP Controller is moved to the Shift-DR state. This allows the board level scan path to be shortened to facilitate testing of other devices in the scan path.

#### SAMPLE/PRELOAD

SAMPLE/PRELOAD is a Standard1149.1 mandatory public instruction. When the SAMPLE/PRELOAD instruction is loaded in the Instruction Register, moving the TAP Controller into the Capture-DR state loads the data in the SRAM's input and I/O buffers into the Boundary Scan Register. Because the SRAM clock is independent from the TAP Clock (TCK) it is possible for the TAP to attempt to capture the I/O ring contents while the input buffers are in transition (i.e. in a metastable state). Although allowing the TAP to sample metastable inputs will not harm the device, repeatable results cannot be expected. SRAM input signals must be stabilized for long enough to meet the TAP's input data capture set-up plus hold time (tTS plus tTH). The SRAM's clock inputs need not be paused for any other TAP operation except capturing the I/O ring contents into the Boundary Scan Register. Moving the controller to the Shift-DR state then places the Boundary Scan Register between the TDI and TDO pins. Because the PRELOAD portion of the command is not implemented in this device, moving the controller to the Update-DR state with the SAMPLE/PRELOAD instruction loaded in the Instruction Register has the same effect as the Pause-DR command. This functionality is not Standard 1149.1 compliant.

#### **EXTEST**

EXTEST is an IEEE 1149.1 mandatory public instruction. It is to be executed whenever the Instruction Register is loaded with all logic 0s. EXTEST is not implemented in the TAP Controller, and therefore this device is not compliant to the 1149.1 Standard. When the EXTEST instruction is loaded into the Instruction Register, the device responds as if the SAMPLE/PRELOAD instruction has been loaded. There is one difference between the two instructions. Unlike the SAMPLE/PRELOAD instruction, EXTEST place the SRAM outputs in a High-Z state.

#### **IDCODE**

The IDCODE instruction cause the ID ROM to be loaded into the ID register when the controller is in the Capture-DR state and places the ID Register between the TDI and TDO pins in the Shift-DR state. The IDCODE instruction is the default instruction loaded in at power-up and any time the controller is placed in the Test-Logic-Reset state.

#### SAMPLE-Z

If the SAMPLE-Z instruction is loaded in the Instruction Register, all SRAM outputs are forced to an inactive drive state (High-Z) and the Boundary Scan Register is placed between the TDI and TDO pins when the TAP Controller is moved to the Shift-DR state.

#### RFU

These instructions are reserved for future use. Do not use these instructions.

### JTAG TAP BLOCK DIAGRAM

18874368-BIT(524288-WORD BY 36-BIT) NETWORK SRAM

## **BOUNDARY SCAN ORDER**

| Bit | Bump | Pin Name | Bit | Bump    | Pin Name | Bit | Bump | Pin Name |  |  |

|-----|------|----------|-----|---------|----------|-----|------|----------|--|--|

| 0   | 8P   | A15      | 27  | 10A     | A8       | 54  | 1H   | MCH      |  |  |

| 1   | 8R   | A16      | 28  | 10B     | A9       | 55  | 2H   | MCH      |  |  |

| 2   | 9P   | A13      | 29  | 9A      | A17      | 56  | 2J   | DQd      |  |  |

| 3   | 9R   | A14      | 30  | 9B      | A18      | 57  | 1J   | DQd      |  |  |

| 4   | 10P  | A11      | 31  | 8A      | ADV      | 58  | 2K   | DQd      |  |  |

| 5   | 10R  | A12      | 32  | 8B      | G#       | 59  | 1K   | DQd      |  |  |

| 6   | 11R  | A10      | 33  | 7A      | CKE#     | 60  | 1L   | DQd      |  |  |

| 7   | 11N  | DQPa     | 34  | 7B      | W#       | 61  | 2L   | DQd      |  |  |

| 8   | 11M  | DQa      | 35  | 6B      | CLK      | 62  | 1M   | DQd      |  |  |

| 9   | 10M  | DQa      | 36  | 6A      | E3#      | 63  | 2M   | DQd      |  |  |

| 10  | 10L  | DQa      | 37  | 5B      | Bwa#     | 64  | 1N   | DQPd     |  |  |

| 11  | 11L  | DQa      | 38  | 5A      | BWb#     | 65  | 1R   | LBO#     |  |  |

| 12  | 10K  | DQa      | 39  | 4A BWc# |          | 66  | 3R   | A4       |  |  |

| 13  | 11K  | DQa      | 40  | 4B BWd# |          | 67  | 3P   | A5       |  |  |

| 14  | 10J  | DQa      | 41  | 3B      | E2       | 68  | 4R   | A2       |  |  |

| 15  | 11J  | DQa      | 42  | 3A      | E1#      | 69  | 4P   | A3       |  |  |

| 16  | 11H  | ZZ       | 43  | 2A      | A7       | 70  | 6P   | A1       |  |  |

| 17  | 7N   | MCH      | 44  | 2B      | A6       | 71  | 6R   | A0       |  |  |

| 18  | 11G  | DQb      | 45  | 1C      | DQPc     |     |      |          |  |  |

| 19  | 10G  | DQb      | 46  | 1D      | DQc      |     |      |          |  |  |

| 20  | 11F  | DQb      | 47  | 2D      | DQc      |     |      |          |  |  |

| 21  | 10F  | DQb      | 48  | 1E      | DQc      |     |      |          |  |  |

| 22  | 11E  | DQb      | 49  | 2E      | DQc      |     |      |          |  |  |

| 23  | 10E  | DQb      | 50  | 1F      | DQc      |     |      |          |  |  |

| 24  | 11D  | DQb      | 51  | 2F      | DQc      |     |      |          |  |  |

| 25  | 10D  | DQb      | 52  | 1G      | DQc      |     |      |          |  |  |

| 26  | 11C  | DQPb     | 53  | 2G      | DQc      |     |      |          |  |  |

### JTAG TAP CONTROLLER STATE DIAGRAM

## TAP CONTROLLER DC ELECTRICAL CHARACTERISTICS (Ta=0~70°C, VDD=3.135~3.465V, unless otherwise noted)

| Symbol | Parameter                              | -0.3 ** VDDQ-0.1             | nits     | Unit        |       |

|--------|----------------------------------------|------------------------------|----------|-------------|-------|

| Symbol | Farameter                              | Condition                    | Min      | Max         | Offic |

| VIHT   | Test Port Input High Voltage           |                              | 2.0      | VDDQ+0.3 ** | V     |

| VILT   | Test Port Input Low Voltage            |                              | -0.3 **  | 0.8         | V     |

| VOHT   | Test Port Output High Voltage          | Іон=-100μΑ                   | VDDQ-0.1 | -           | V     |

| VOLT   | Test Port Output Low Voltage           | IoL=+100μA                   | •        | 0.1         | V     |

| INT    | TMS, TCK and TDI Input Leakage Current |                              | -10      | 10          | μΑ    |

| IOLT   | TDO Output Leakage Current             | Output Disable, Vout=0V~VDDQ | -10      | 10          | μΑ    |

Note38. \*\*Input Undershoot/Overshoot voltage must be -1V<Vi<VDDQ+1V with a pulse width not to exceed 20% tTCK.

18874368-BIT(524288-WORD BY 36-BIT) NETWORK SRAM

# <u>TAP CONTROLLER AC ELECTRICAL CHARACTERISTICS</u> (Ta=0~70°C, VDD=3.135~3.465V, unless otherwise noted) (1)MEASUREMENT CONDITION

Fig.4 Output load

Output load ......Fig.4

## (2)TIMING CHARACTERISTICS

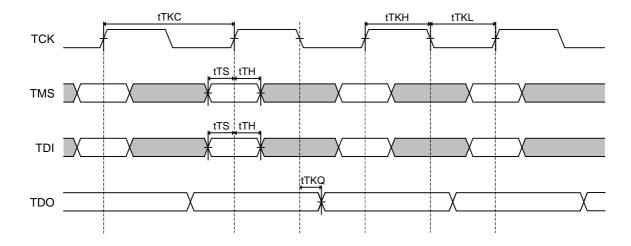

| Symbol | Parameter            | Lim | Unit |       |

|--------|----------------------|-----|------|-------|

| Symbol | Falametei            | Min | Max  | Offic |

| tTF    | TCK Frequency        |     | 20   | MHz   |

| tTKC   | TCK Cycle Time       | 50  |      | ns    |

| tTKH   | TCK High Pulse Width | 20  |      | ns    |

| tTKL   | TCK Low Pulse Width  | 20  |      | ns    |

| tTS    | TDI, TMS setup time  | 10  |      | ns    |

| tTH    | TDI, TMS hold time   | 10  |      | ns    |

| tTKQ   | TCK Low to TDO valid |     | 20   | ns    |

## (3) TIMING

18874368-BIT(524288-WORD BY 36-BIT) NETWORK SRAM

## **JTAG TAP INSTRUCTION SET SUMMARY**

| Instruction    | Code | Description                                                                                                                                                                            |

|----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXTEST         | 000  | Captures I/O ring contents. Places the Boundary Scan Register between TDI and TDO. Forces all SRAM outputs to High-Z state. This instruction is not 1149.1-compliant.                  |

| IDCODE         | 001  | Preloads ID Register and places it between TDI and TDO                                                                                                                                 |

| SAMPLE-Z       | 010  | Captures I/O ring contents. Places the Boundary Scan Register between TDI and TDO. Forces all Data output drivers to High-Z                                                            |

| RFU            | 011  | Do not use this instruction; Reserved for Future Use.                                                                                                                                  |

| SAMPLE/PRELOAD | 100  | Captures I/O ring contents. Places the Boundary Scan Register between TDI and TDO.  This instruction dose not implement 1149.1 preload function and is therefore not 1149.1-compliant. |

| RFU            | 101  | Do not use this instruction; Reserved for Future Use.                                                                                                                                  |

| RFU            | 110  | Do not use this instruction; Reserved for Future Use.                                                                                                                                  |

| BYPASS         | 111  | Places the BYPASS Register between TDI and TDO.                                                                                                                                        |

## STRUCTURE OF IDENTIFICATION REGISTER

|           | Revision Device Information |    |    |    |    |    |    |    |    |    |    |    |    | ,  | IED | EC | Ven | dor | Cod | de o | f RE | NE | SAS | 3 |   |   |   |   |   |   |   |    |

|-----------|-----------------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|-----|----|-----|-----|-----|------|------|----|-----|---|---|---|---|---|---|---|---|----|

| Bit No.   | 31                          | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17  | 16 | 15  | 14  | 13  | 12   | 11   | 10 | 9   | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0  |

| M5M5V5636 | 0                           | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 0   | 0  | 1   | 1   | 0   | 0    | 0    | 1  | 0   | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1  |

|           | 1/10                        | 20 |    |    |    |    |    |    |    |    |    |    |    |    |     |    |     |     |     |      |      |    |     |   |   |   |   |   |   |   |   | CD |

### **PACKAGE OUTLINE**

165(11x15) bump Ball Grid Array(BGA) Pin Pitch 1.00mm

Refer to JEDEC Standard MO-216, Variation CAB-1, which can be seen at:

http://www.jedec.org/download/search/MO-216c.pdf

## **Renesas LSIs**

## M5M5V5636UG - 20

18874368-BIT(524288-WORD BY 36-BIT) NETWORK SRAM

## **REVISION HISTORY**

| Rev. No. | Histor | У                                                   |     |       |      |      |      |       |       |      |        |       |     | Date           |             |

|----------|--------|-----------------------------------------------------|-----|-------|------|------|------|-------|-------|------|--------|-------|-----|----------------|-------------|

| 1.0      | trans  | emiconductor op<br>ferred to RENES<br>n RENESAS and | SAS | Techi | nolo | gy C | orpo | ratio | on or | 1 Ар | ril 1s | st 20 | 03. | August 1, 2003 | Preliminary |

|          |        | Bit No.                                             | 11  | 10    | 9    | 8    | 7    | 6     | 5     | 4    | 3      | 2     | 1   |                | ,           |

|          |        | RENESAS                                             | 0   | 1     | 0    | 0    | 0    | 1     | 0     | 0    | 0      | 1     | 1   |                |             |

|          |        | MITSUBISHI                                          | 0   | 0     | 0    | 0    | 0    | 0     | 1     | 1    | 1      | 0     | 0   |                |             |

18874368-BIT(524288-WORD BY 36-BIT) NETWORK SRAM

# RenesasTechnologyCorp.

Nippon Bldg.,6-2,Oteamchi 2-chome,Chiyoda-ku,Tokyo,100-0004 Japan

Keep safety first in your circuit designs!

Renesas Technology Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corporation product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corporation or a third party.

Renesas Technology Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- Renesas Technology Corporation assumes no responsibility for any damage, or intringement of any third-party's gints, originating in the use of any product data, diagrams, charts, programs, algoritims, or circuit application examples contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor for the latest product information before purchasing a product listed herein.

The information product distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors.

Renesas Technology Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corporation by various means, including the Renesas Technology Corporation before making a final decision on the applicability of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information contained in these materials.

Renesas Technology Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor when considering the use of a product contained herein for any specific purposes, s

© 2003 Renesas Technology Corp. New publication, effective August 2003. Specifications subject to change without notice.