# ML63512A/514A

## **User's Manual**

CMOS 4-bit microcontroller

FIRST EDITION ISSUE DATE: May 2000

FEUL63512A-01

#### NOTICE

- 1. The information contained herein can change without notice owing to product and/or technical improvements. Before using the product, please make sure that the information being referred to is up-to-date.

- 2. The outline of action and examples for application circuits described herein have been chosen as an explanation for the standard action and performance of the product. When planning to use the product, please ensure that the external conditions are reflected in the actual circuit, assembly, and program designs.

- 3. When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating temperature.

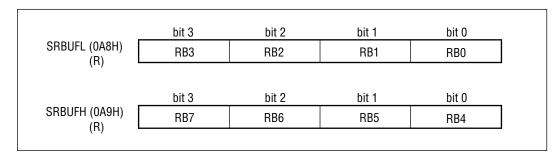

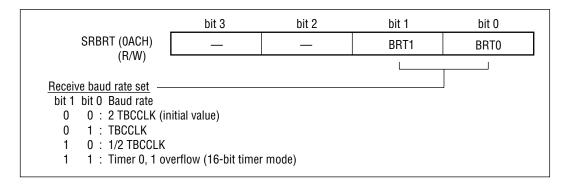

- 4. Oki assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified operating range.

- 5. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of the product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

- 6. The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g., office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not authorized for use in any system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or application may result in the loss or damage of property, or death or injury to humans. Such applications include, but are not limited to, traffic and automotive equipment, safety devices, aerospace equipment, nuclear power control, medical equipment, and life-support systems.

- 7. Certain products in this document may need government approval before they can be exported to particular countries. The purchaser assumes the responsibility of determining the legality of export of these products and will take appropriate and necessary steps at their own expense for these.

- 8. No part of the contents contained herein may be reprinted or reproduced without our prior permission.

- 9. MS-DOS is a registered trademark of Microsoft Corporation.

Copyright 2000 Oki Electric Industry Co., Ltd.

#### Preface

This manual describes the hardware of Oki's original CMOS 4-bit microcontrollers ML63512A and ML63514A.

Refer to the "nX-4/250, 300 Core Instruction Manual" for details of the 4-bit CPU core nX-4/250 which is built into the ML63512A and ML63514A.

The manuals related to the ML63512A and ML63514A are shown below.

- nX-4/250, 300 Core Instruction Manual: Describes the base architecture and instruction set of nX-4/250 core and nX-4/300 core.

- SASM63K User's Manual: Describes the structured assembler operation and assembler language specification.

- Dr.63514 User's Manual: Describes the hardware of the emulator.

- SID63K Debugger User's Manual: Describes the debugger commands.

This document is subject to change without notice.

| Classification  | Notation                                                                                                                                        | Description                                                                                                                                                                                                                                                                      |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ■ Numeric value | xxh, xxH<br>xxb                                                                                                                                 | Represents a hexadecimal number.<br>Represents a binary number.                                                                                                                                                                                                                  |

| ■ Unit          | word, W<br>byte, B<br>nibble, N<br>mega-, M<br>kilo-, K<br>kilo-, k<br>milli-, m<br>micro-, µ<br>nano-, n<br>second, s (lower case)<br>KB<br>MB | 1 word = 16 bits<br>1 byte = 2 nibbles = 8 bits<br>1 nibble = 4 bits<br>10 <sup>6</sup><br>$2^{10} = 1024$<br>$10^3 = 1000$<br>$10^{-3}$<br>$10^{-6}$<br>$10^{-9}$<br>second<br>1 KB = 1 kilobyte = 1024 bytes<br>1 MB = 1 megabyte = 2 <sup>20</sup> bytes<br>= 1,048,576 bytes |

| Symbol          | Note:                                                                                                                                           | Gives more information about mistakable items.                                                                                                                                                                                                                                   |

| ■ Terminology   | "H" level<br>"L" level                                                                                                                          | Indicates high side voltage signal levels $V_{IH}$ and $V_{OH}$ as specified by the electrical characteristics.<br>Indicates low side voltage signal levels $V_{IL}$ and $V_{OL}$ as specified by the electrical characteristics.                                                |

#### Notation

Register description

| Invalid bit   | : | When read, a value of "1" is always obtained. Write operations are invalid. |

|---------------|---|-----------------------------------------------------------------------------|

| R/W attribute | : | "R" indicates data can be read and "W" indicates data can be written.       |

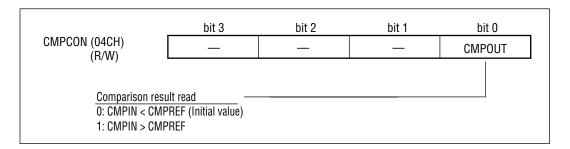

| CMPCON   | (04CH)<br>(R/W) | bit 3 | bit 2 | bit 1 | bit 0<br>CMPOUT |                                       |

|----------|-----------------|-------|-------|-------|-----------------|---------------------------------------|

|          |                 |       |       |       |                 | ······ Bit name<br>······ Invalid bit |

|          | L               |       |       |       |                 | Address                               |

|          |                 |       |       |       |                 | ······ R/W attribute                  |

| <u> </u> |                 |       |       |       |                 | ······ Register name                  |

### Table of Contents

#### Chapter 1 Overview

| 1.1 | Overview                                                  | 1-1  |

|-----|-----------------------------------------------------------|------|

| 1.2 | Features                                                  | 1-1  |

| 1.3 | Block Diagram                                             | 1-4  |

| 1.4 | Pin Configuration                                         | 1-5  |

|     | 1.4.1 ML63512A, ML63514A Pin Configurations               | 1-5  |

| 1.5 | Pin Descriptions                                          | 1-9  |

|     | 1.5.1 Descriptions of the Basic Functions of Each Pin     | 1-9  |

|     | 1.5.2 Descriptions of the Secondary Functions of Each Pin | 1-12 |

|     | 1.5.3 Unused Pin Processing                               | 1-13 |

| 1.6 | Basic Timing                                              | 1-14 |

|     | 1.6.1 Basic Timing of CPU Operation                       |      |

|     | 1.6.2 Port I/O Basic Timing                               | 1-14 |

|     | 1.6.3 Interrupt Basic Timing                              | 1-16 |

|     |                                                           |      |

#### Chapter 2 CPU and Memory Spaces

| 2.1 |        | iew                                                     |     |

|-----|--------|---------------------------------------------------------|-----|

| 2.2 | Regist | ters                                                    | 2-1 |

|     | 2.2.1  | Accumulator (A)                                         | 2-1 |

|     | 2.2.2  | Flag Register                                           | 2-1 |

|     |        | 2.2.2.1 Carry Flag (C)                                  |     |

|     |        | 2.2.2.2 Zero Flag (Z)                                   | 2-2 |

|     |        | 2.2.2.3 G Flag (G)                                      |     |

|     | 2.2.3  | Master Interrupt Enable Flag (MIE)                      |     |

|     |        | Current Bank Register (CBR), Extra Bank Register (EBR), |     |

|     |        | HL Register (HL), XY Register (XY)                      | 2-3 |

|     | 2.2.5  | Program Counter (PC)                                    | 2-4 |

|     |        | RA Registers (RA3, RA2, RA1, RA0)                       |     |

|     | 2.2.7  | Stack Pointer (SP) and Call Stack                       | 2-5 |

|     | 2.2.8  | Register Stack Pointer (RSP) and Register Stack         |     |

| 2.3 |        | ry Spaces                                               |     |

|     |        | Program Memory Space                                    |     |

|     |        | Data Memory Space                                       |     |

|     |        |                                                         |     |

#### Chapter 3 CPU Control Functions

| 3.1 | Overv  | iew                                         | 3-1 |

|-----|--------|---------------------------------------------|-----|

| 3.2 | Syster | m Reset Mode (RST)                          | 3-2 |

|     | 3.2.1  | Transfer to and State of System Reset Mode  | 3-2 |

| 3.3 | Halt N | 1ode                                        | 3-3 |

|     | 3.3.1  | Transfer to and State of Halt Mode          | 3-3 |

|     | 3.3.2  | Halt Mode Release                           | 3-4 |

|     |        | 3.3.2.1 Release of Halt Mode by Interrupt   | 3-4 |

|     |        | 3.3.2.2 Release of Halt Mode by RESETB Pin  | 3-4 |

|     | 3.3.3  | Melody Data Interrupt and Halt Mode Release | 3-5 |

|     | 3.3.4  | Note Concerning HALT Instruction            | 3-5 |

#### Chapter 4 Interrupt (INT)

| 4-1  |

|------|

| 4-3  |

| 4-10 |

| 4-10 |

| 4-11 |

| 4-11 |

|      |

#### Chapter 5 Clock Generator Circuit (OSC)

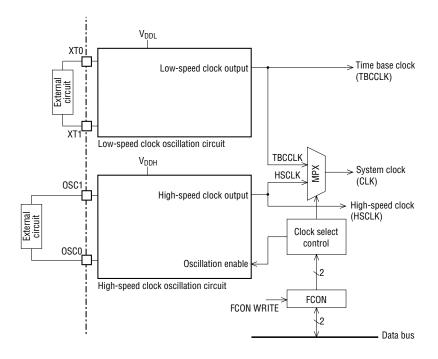

| 5.1 | Overview                              | 5-1 |

|-----|---------------------------------------|-----|

| 5.2 | Clock Generator Circuit Configuration | 5-1 |

| 5.3 | Low-Speed Clock Generator Circuit     | 5-2 |

| 5.4 | High-Speed Clock Generator Circuit    | 5-4 |

|     | System Clock Control                  |     |

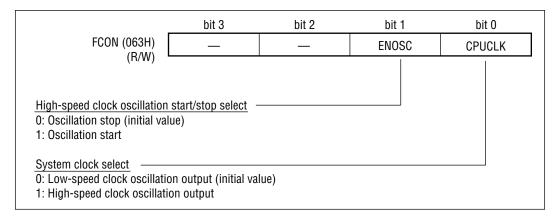

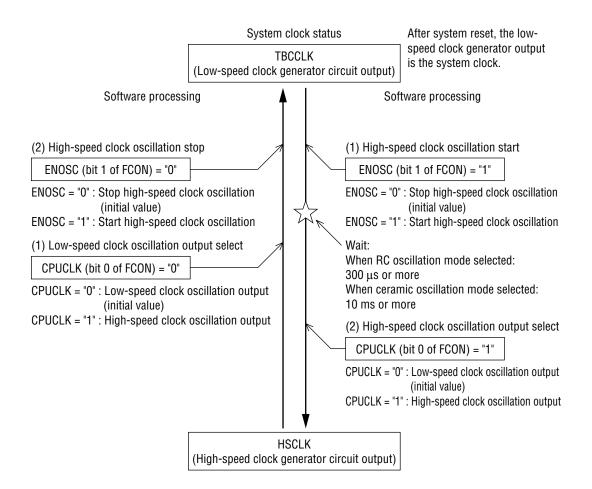

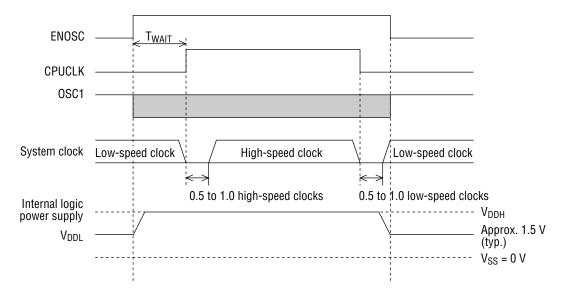

| 5.6 | Frequency Control Register (FCON)     | 5-7 |

|     | System Clock Select Timing            |     |

#### Chapter 6 Time Base Counter (TBC)

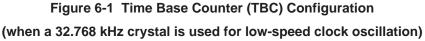

| 6.1 | Overview                        | 6-1 |

|-----|---------------------------------|-----|

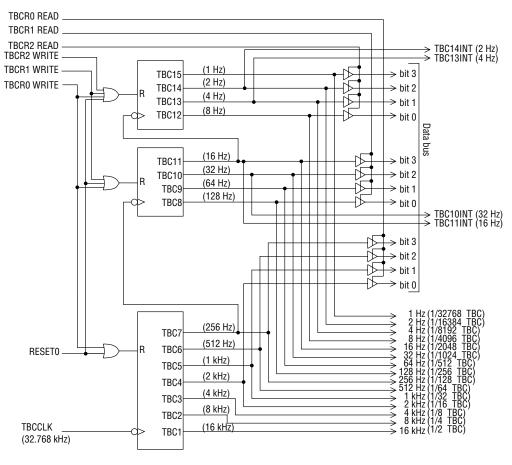

| 6.2 | Time Base Counter Configuration | 6-1 |

| 6.3 | Time Base Counter Registers     | 6-2 |

| 6.4 | Time Base Counter Operation     | 6-3 |

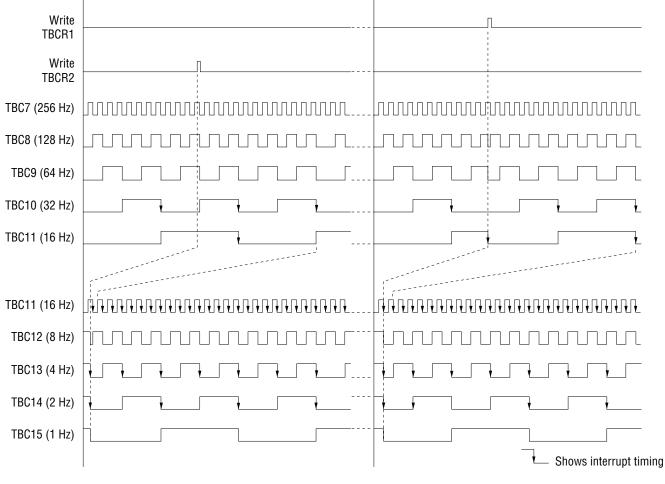

#### Chapter 7 Timers (TIMER)

| 7.1 | Overv | iew                                         | 7-1  |

|-----|-------|---------------------------------------------|------|

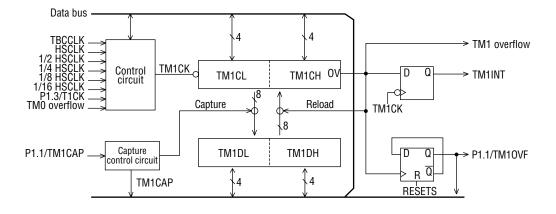

| 7.2 | Timer | Configuration                               | 7-1  |

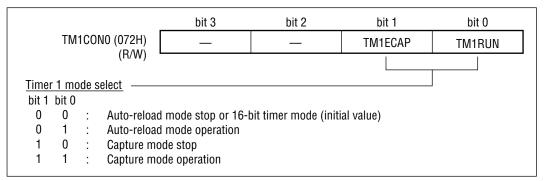

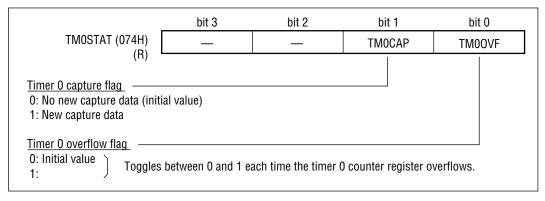

| 7.3 | Timer | Registers                                   | 7-3  |

| 7.4 | Timer | Operation                                   | 7-10 |

|     | 7.4.1 | Timer Clock                                 | 7-10 |

|     | 7.4.2 | Timer Data Registers                        | 7-10 |

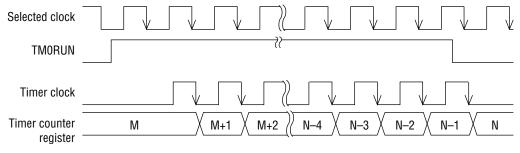

|     | 7.4.3 | Timer Counter Registers                     | 7-10 |

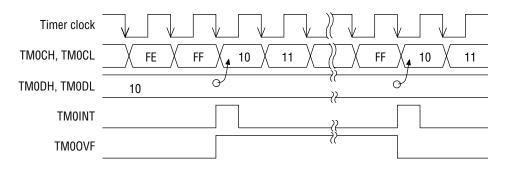

|     | 7.4.4 | Timer Interrupt Requests and Overflow Flags | 7-11 |

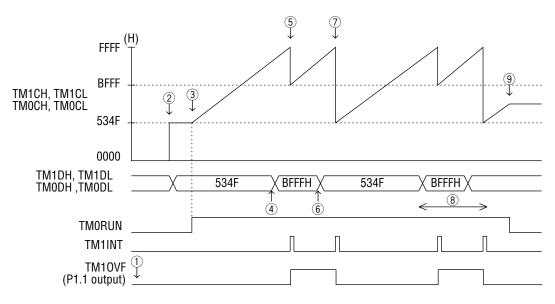

|     | 7.4.5 | Auto-Reload Mode Operation                  | 7-12 |

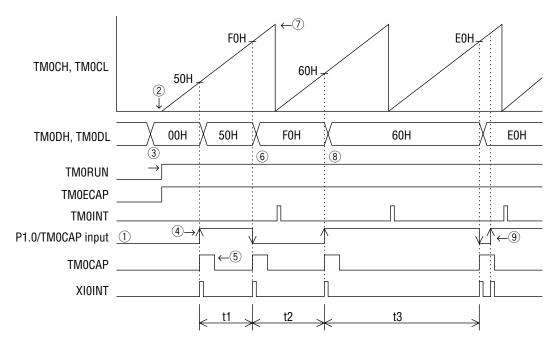

|     | 7.4.6 | Capture Mode Operation                      | 7-14 |

|     | 7.4.7 | Frequency Measurement Mode Operation        | 7-17 |

#### Chapter 8 Ports (INPUT, OUTPUT, I/O PORT)

| Overvi | ew                                                                                                                               | 8-1                                                                    |

|--------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

|        |                                                                                                                                  |                                                                        |

| Port 0 | to Port 6, Port 9 and Port A                                                                                                     | 8-2                                                                    |

| 8.3.1  |                                                                                                                                  |                                                                        |

| 8.3.2  | Port 0 to Port 6, Port 9 and Port A Registers                                                                                    | 8-6                                                                    |

| Port 7 |                                                                                                                                  | 8-19                                                                   |

| 8.4.1  | Port 7 Configuration                                                                                                             | 8-19                                                                   |

| 8.4.2  |                                                                                                                                  |                                                                        |

| 8.4.3  | Port 7 Secondary Functions                                                                                                       | 8-21                                                                   |

| Port 8 |                                                                                                                                  |                                                                        |

| 8.5.1  | Port 8 Configuration                                                                                                             | 8-22                                                                   |

| 8.5.2  | Port 8 Registers                                                                                                                 | 8-23                                                                   |

| Extern | al Interrupt                                                                                                                     | 8-24                                                                   |

| 8.6.1  | External Interrupt Overview                                                                                                      | 8-24                                                                   |

| 8.6.2  | External Interrupt Configuration                                                                                                 | 8-24                                                                   |

| 8.6.3  | External Interrupt Control Registers                                                                                             | 8-25                                                                   |

|        | Ports L<br>Port 0<br>8.3.1<br>8.3.2<br>Port 7<br>8.4.1<br>8.4.2<br>8.4.3<br>Port 8<br>8.5.1<br>8.5.2<br>Extern<br>8.6.1<br>8.6.2 | <ul> <li>8.3.2 Port 0 to Port 6, Port 9 and Port A Registers</li></ul> |

#### Chapter 9 Serial Port (SIO)

| 9.1 | Overvie  | W                                    | 9-1  |

|-----|----------|--------------------------------------|------|

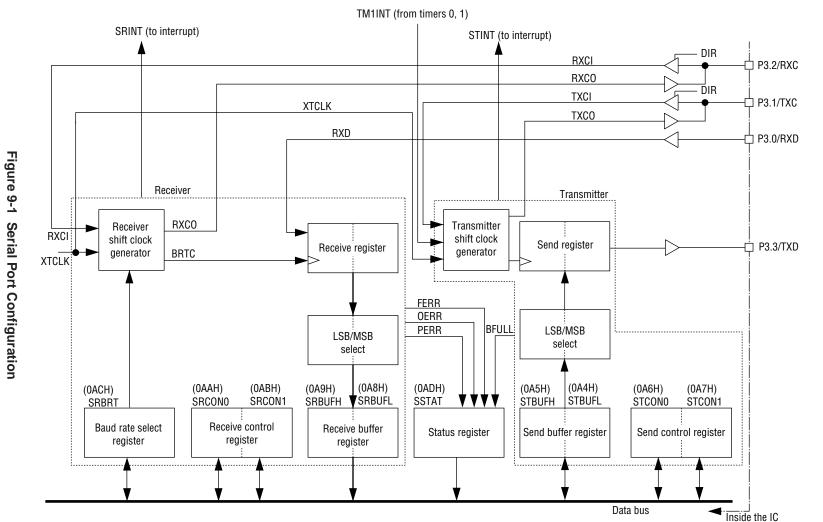

| 9.2 | Serial F | Port Configuration                   | 9-1  |

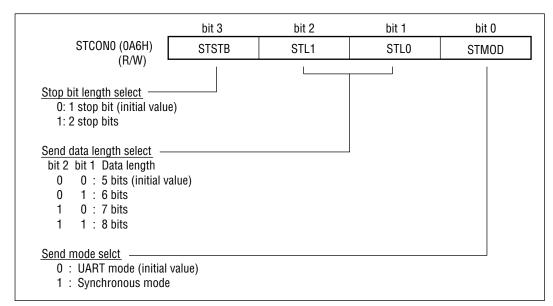

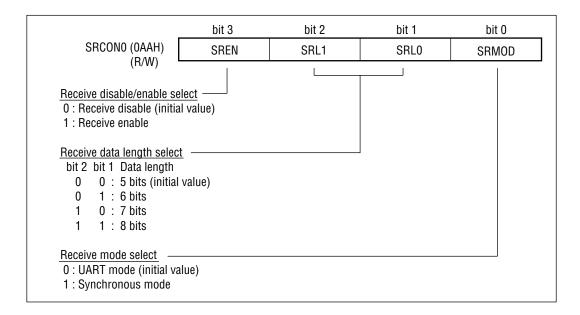

| 9.3 | Serial F | Port Registers                       | 9-3  |

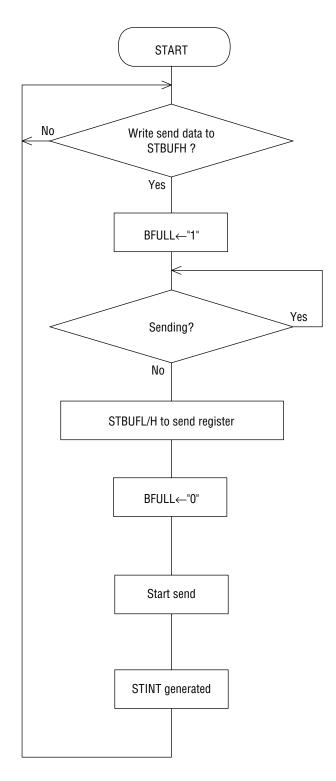

| 9.4 | Serial F | Port Operation Description           | 9-12 |

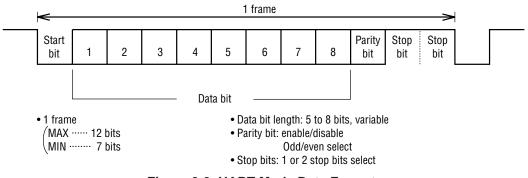

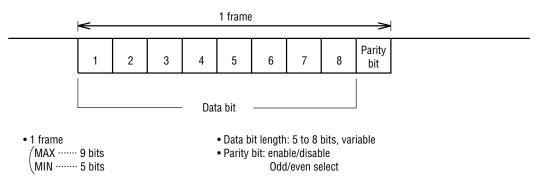

|     | 9.4.1    | Data Format                          | 9-12 |

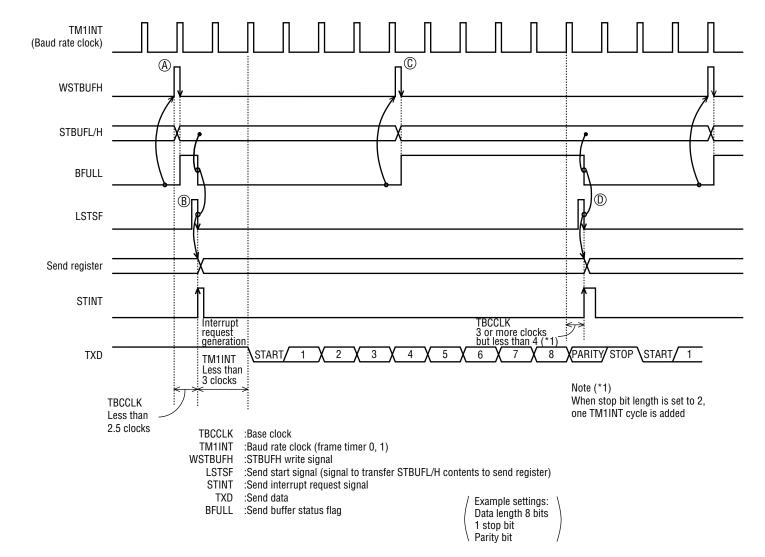

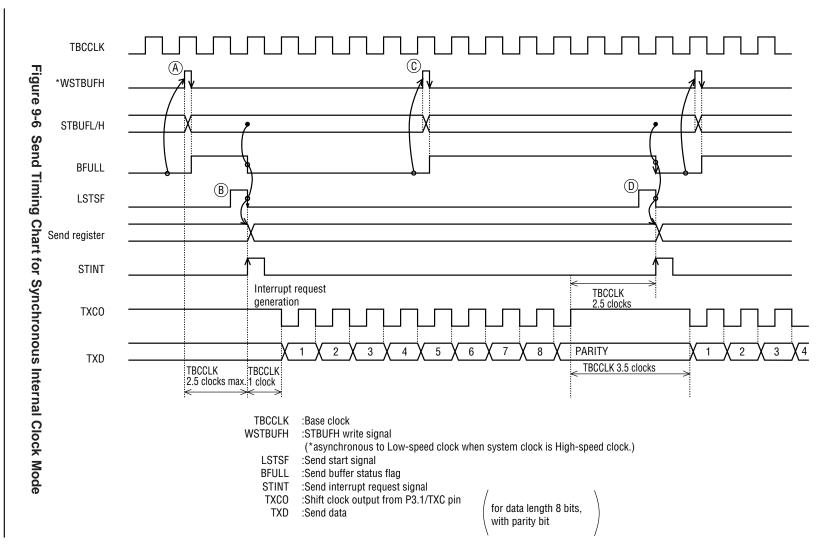

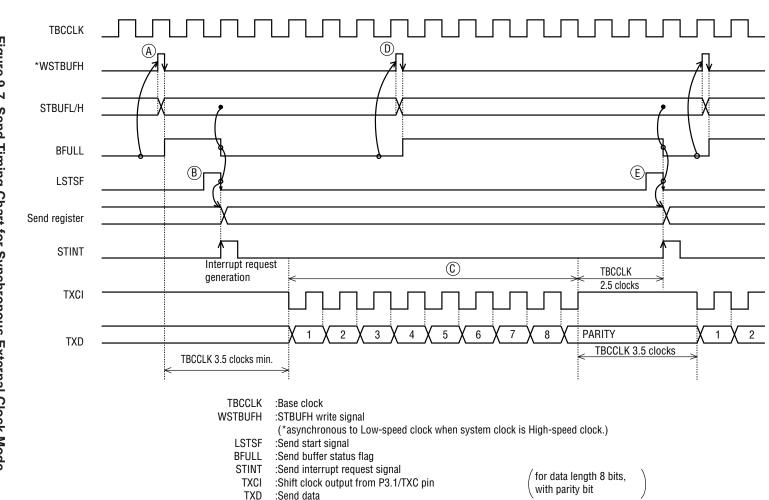

|     | 9.4.2    | Send Operation Description           | 9-13 |

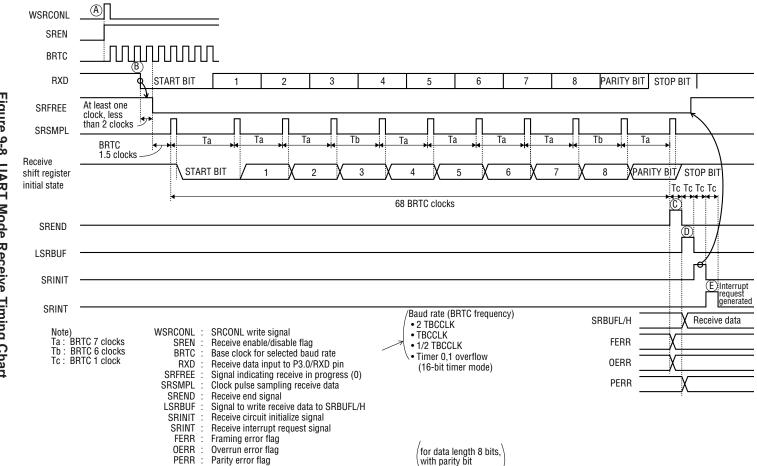

|     | 9.4.3    | Receive Operation Description        | 9-19 |

| 9.5 | Send/R   | eceive Data LSB/MSB First Select     | 9-25 |

|     | 9.5.1    | Selecting Send Data LSB/MSB First    | 9-25 |

|     | 9.5.2    | Selecting Receive Data LSB/MSB First | 9-26 |

|     |          |                                      |      |

#### Chapter 10 Melody Driver (MELODY)

| 10.1 | Overview                                  | 10-1 |

|------|-------------------------------------------|------|

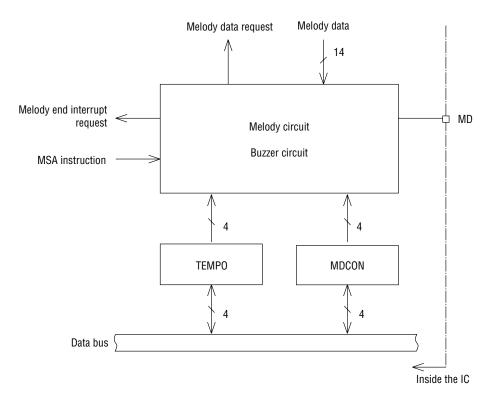

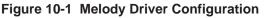

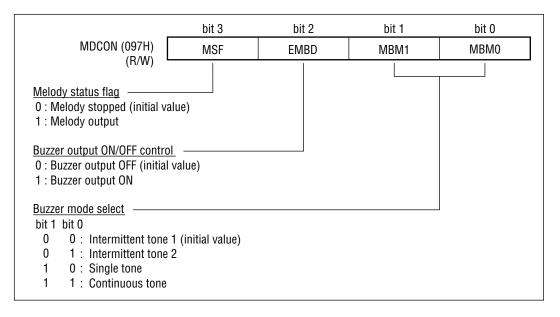

|      | Melody Driver Configuration               |      |

|      | Melody Driver Registers                   |      |

|      | Melody Circuit Operation                  |      |

|      | 10.4.1 Tempo Data                         |      |

|      | 10.4.2 Melody Data                        |      |

|      | 10.4.3 Melody Circuit Application Example |      |

| 10.5 | Buzzer Circuit Operation                  |      |

#### Chapter 11 Level Detector

| 11.1 | Overview                             | 11-1 |

|------|--------------------------------------|------|

|      | Level Detector Configuration         |      |

|      | Level Detector Registers             |      |

|      | 11.3.1 Input Levels and Output Codes |      |

| 11.4 | Level Detector Operation             | 11-7 |

#### Chapter 12 Comparator (CMP)

| 12.1 | Overview                 | 12-1 |

|------|--------------------------|------|

| 12.2 | Comparator Configuration | 12-1 |

| 12.3 | Comparator Register      | 12-2 |

| 12.4 | Comparator Operation     | 12-3 |

#### Chapter 13 Backup Circuit (BACKUP)

| 13.1 | Overview                                                                  | 13-1 |

|------|---------------------------------------------------------------------------|------|

| 13.2 | Power Supply Circuit Configuration                                        | 13-2 |

|      | 13.2.1 Power Supply Circuit Configuration When Backup Circuit is Used     | 13-2 |

|      | 13.2.2 Power Supply Circuit Configuration When Backup Circuit is Not Used | 13-3 |

| 13.3 | Backup Circuit Register                                                   | 13-4 |

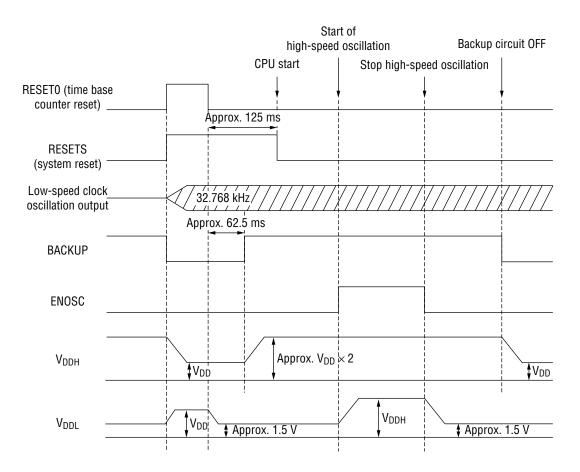

| 13.4 | Power Supply Circuit Operation                                            | 13-5 |

#### Appendixes

| Appendix A | List of Special Function Registers                        | Appendix-1  |

|------------|-----------------------------------------------------------|-------------|

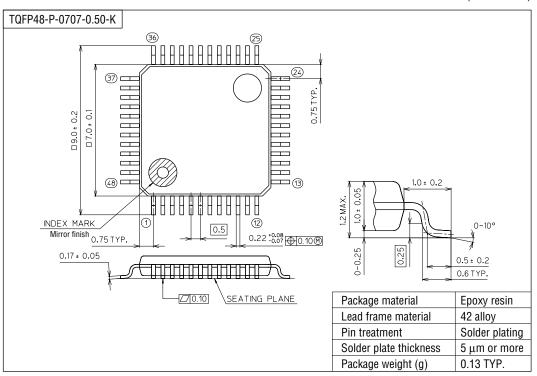

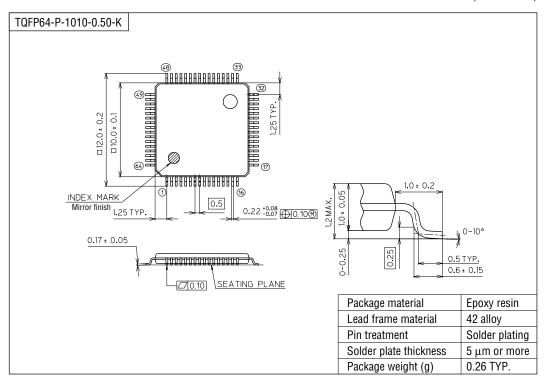

| Appendix B | Package Dimensions                                        | Appendix-4  |

| Appendix C | Electrical Characteristics                                | Appendix-6  |

| Appendix D | Instruction List                                          | Appendix-22 |

| Appendix E | Mask Option                                               | Appendix-44 |

| Appendix F | Differences between the ML63512/514 and the ML63512A/514A | Appendix-46 |

|   | Chapter 1    | Overview                        | 1 |   |

|---|--------------|---------------------------------|---|---|

|   |              |                                 |   |   |

|   | Chapter 2    | CPU and Memory Spaces           | 2 |   |

|   | ·            | · ·                             |   |   |

|   | Chapter 3    | CPU Control Functions           | 3 |   |

|   | ·            |                                 |   | - |

|   | Chapter 4    | Interrupt (INT)                 | 4 |   |

|   | ·            |                                 |   |   |

|   | Chapter 5    | Clock Generator Circuit (OSC)   | 5 | ; |

|   | I            |                                 |   | - |

|   | Chapter 6    | Time Base Counter (TBC)         | 6 | ; |

|   | ·            |                                 |   |   |

|   | Chapter 7    | Timers (TIMER)                  | 7 |   |

|   | 1            |                                 |   | - |

|   | Chapter 8    | Ports (INPUT, OUTPUT, I/O PORT) | 8 | 3 |

|   |              |                                 |   |   |

|   | Chapter 9    | Serial Port (SIO)               | 9 |   |

|   |              |                                 |   |   |

|   | Chapter 10   | Melody Driver (MELODY)          | 1 | 0 |

|   |              |                                 |   |   |

|   | Chapter 11   | Level Detector                  | 1 | 1 |

|   |              |                                 |   |   |

| Γ | Chapter 12   | Comparator (CMP)                | 1 | 2 |

| L |              |                                 |   |   |

|   | Chapter 13   | Backup Circuit (BACKUP)         | 1 | 3 |

| L |              |                                 |   |   |

|   | Appendixes   |                                 |   |   |

|   | , .pponaix00 |                                 |   |   |

# Chapter 1

1

Overview

### Chapter 1 Overview

#### 1.1 Overview

The ML63512A and ML63514A are CMOS 4-bit microcontrollers with built-in level detector and operate at 0.9 V (min.).

The ML63512A and ML63514A are M63512 series mask ROM-version products of OLMS-63K family, which employs Oki's original CPU core nX-4/250.

The program memory capacity and data memory capacity of the ML63512A differ from those of the ML63514A.

48-pin TQFP and 64-pin TQFP packages are available for the ML63512A and ML63514A.

#### 1.2 Features

The ML63512A and ML63514A have the following features.

- a. Extensive instruction set

- 407 instructions

Transfer, rotate, increment/decrement, arithmetic operations, compare, logic operations, mask operations, bit operations, ROM table reference, stack operations, flag operations, jump, conditional branch, call/return, control

- b. Wide variety of addressing modes

- 4 types of data memory indirect addressing modes with current bank register, extra bank register, HL register and XY register

- Data memory bank internal direct addressing mode

- c. Processing speed

- 2 clocks per machine cycle, with most instructions executed in 1 machine cycle

- Minimum instruction execution time: 61 µs (@ 32.768 kHz system clock)

1 µs (@ 2 MHz system clock)

- d. Clock generation circuit

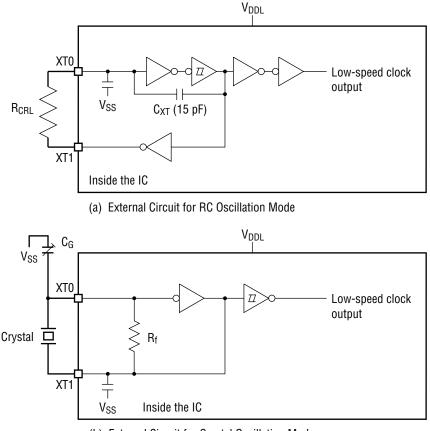

- Low-speed clock: Crystal oscillation or RC oscillation selected with mask option (30 to 80 kHz)

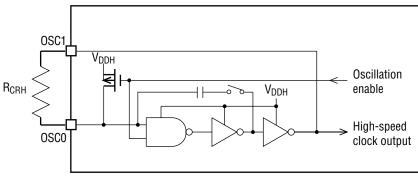

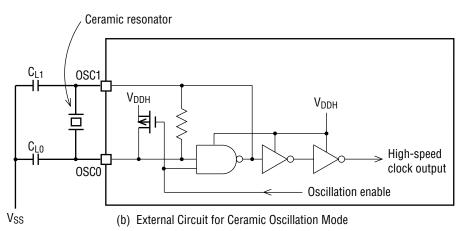

- High-speed clock:

- Ceramic oscillation or RC oscillation selected with software (2 MHz max.)

- e. Program memory space

- ML63512A: 4K words

- ML63514A: 8K words

- The basic instruction length is 16 bits per word.

- f. Data memory space

- ML63512A: 128 nibbles

- ML63514A: 256 nibbles

g. Stack level

|          | Call stack level | Register stack level |

|----------|------------------|----------------------|

| ML63512A | 16               | 16                   |

| ML63514A | 16               | 16                   |

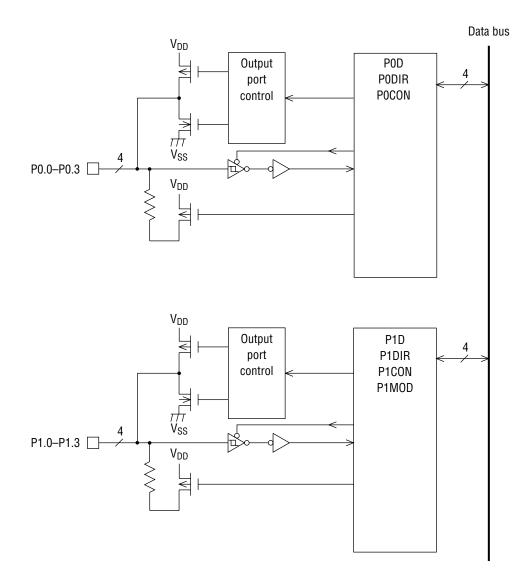

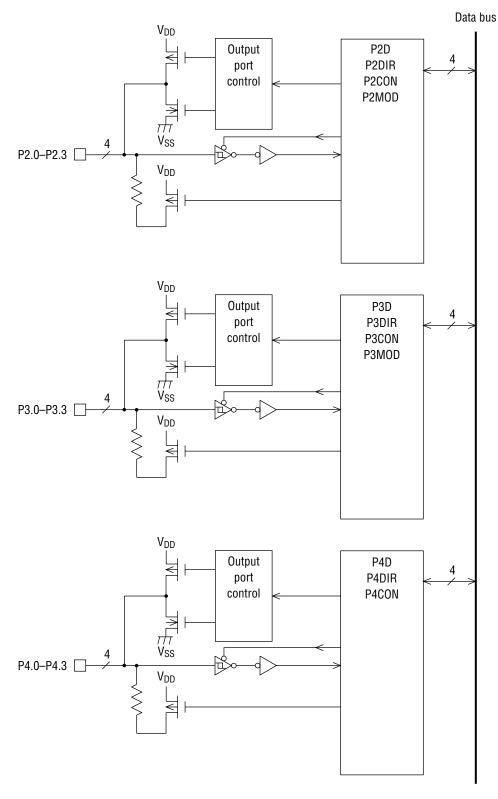

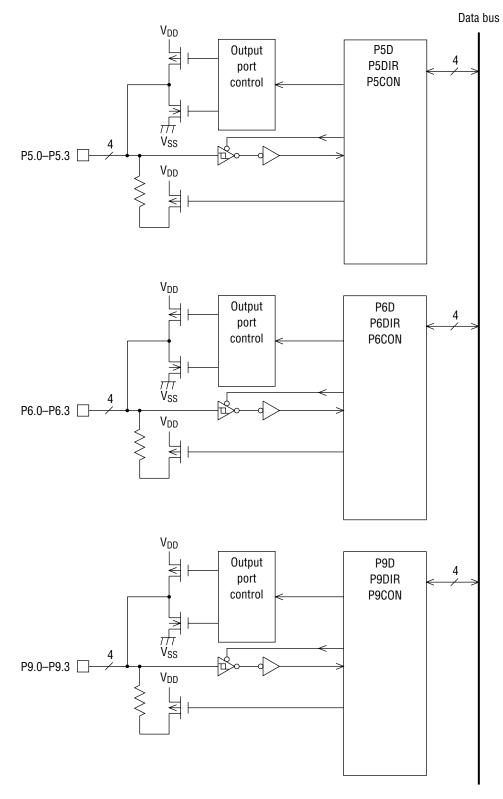

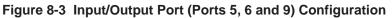

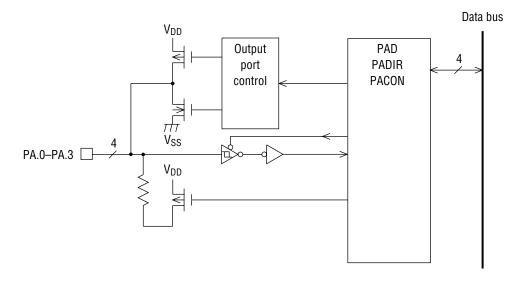

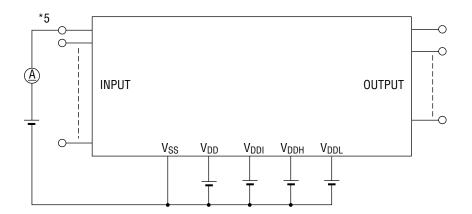

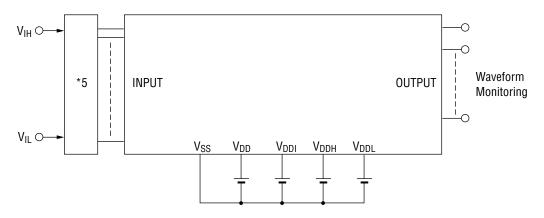

h. Ports

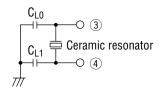

- Input ports: Selectable as input with pull-up resistor or high impedance input.

- Output ports: N-channel open drain output (can directly drive LEDs)

- I/O ports: Selectable as input with pull-up resistor or high impedance input. Selectable as n-channel open drain output or CMOS output.

- Can be interfaced with external peripherals that use a different power supply than this device uses. (Power to the output port is supplied from V<sub>DDI</sub> (separate power supply)).

- Number of ports:

|                | Input ports            | Output ports           | I/O ports               |

|----------------|------------------------|------------------------|-------------------------|

| 48-pin package | 1 port $\times$ 4 bits | 1 port $	imes$ 4 bits  | 6 ports $\times$ 4 bits |

| 64-pin package | 1 port $\times$ 4 bits | 1 port $	imes$ 4 bits  | 9 ports $	imes$ 4 bits  |

| Chip           | 1 port $\times$ 4 bits | 1 port $\times$ 4 bits | 9 ports $	imes$ 4 bits  |

#### i. Melody output function

- Melody sound frequency: 529 to 2979 Hz (@ 32.768 kHz)

- Tone length:

- 63 varieties 15 varieties

- Tempo: 15 varietiesMelody data: Stored in the program memory

- Number of output ports: 1 (dedicated pin)

- Buzzer driver signal output: 4 kHz (@ 32.768 kHz)

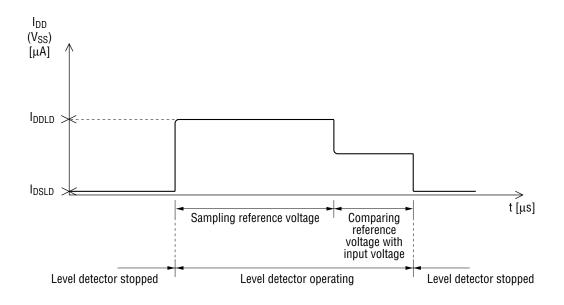

j. Level detector

- Conversion time: Approx. 183 μs (@ 32.768 kHz)

- Dedicated input pins: 2 pins (switched by software; for the secondary functions of the input ports)

Detection level: 12 levels

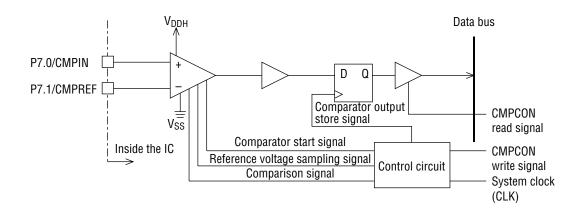

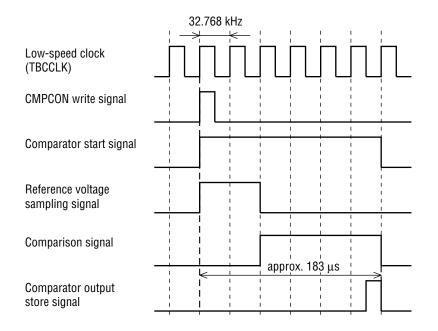

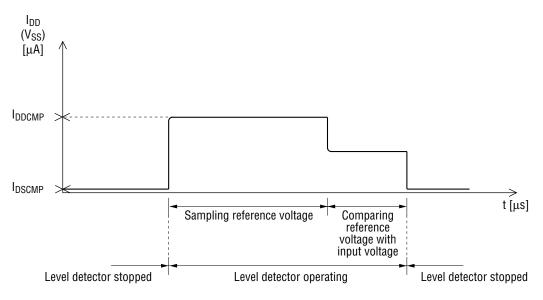

#### k. Comparator

| ٠ | Offset voltage:  | 50 mV max. (V <sub>DD</sub> = 1.5 V) |

|---|------------------|--------------------------------------|

| ٠ | Comparison time: | Approx. 183 μs (@ 32.768 kHz)        |

- Number of channels: 1 (for the secondary functions of the input ports)

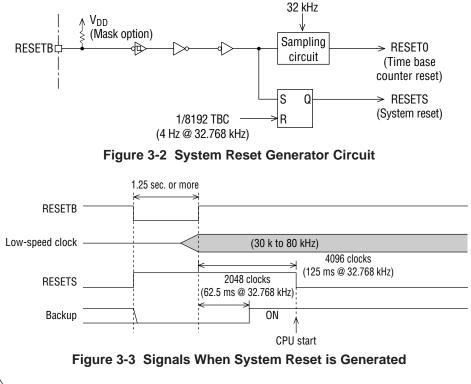

- I. System reset function

- System reset through RESETB pin (connected to the internal 32 kHz sampling circuit) (RESETB pin can be pulled up by mask option)

m. Power supply backup

• Backup circuit (voltage multiplier) enables operation at 0.9 V minimum

| n. Time  | ers, counters         |             |                                                                                  |

|----------|-----------------------|-------------|----------------------------------------------------------------------------------|

| •        | 8-bit timer:          | 2 channels  |                                                                                  |

|          |                       |             | as auto-reload mode, capture mode,<br>ency measurement mode                      |

| •        | 15-bit TBC:           | 1 channel   |                                                                                  |

|          |                       |             | 4 Hz, 8 Hz, 16 Hz, 32 Hz, 64 Hz,128 Hz, 256 Hz,                                  |

|          |                       | 512 Hz, 1 k | Hz, 2 kHz signals can be read (@ 32.768 kHz)                                     |

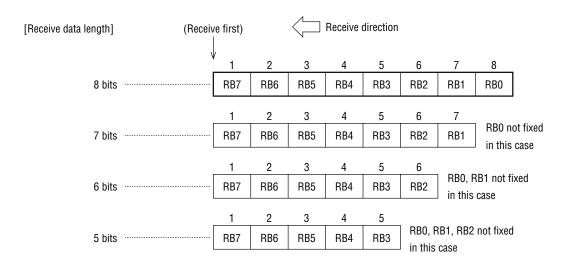

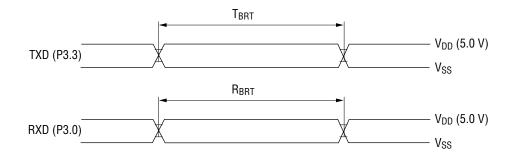

| o. Seria | al port               |             |                                                                                  |

| •        | Mode:                 |             | Selectable as UART mode/synchronous mode                                         |

| •        | UART communicat       | tion speed: | 2TBCCLK, TBCCLK, 1/2TBCCLK, Timers 0 & 1 overflow                                |

|          |                       |             | 24 kbps Max. (when 2TBCCLK @ 80 kHz selected)                                    |

| •        | Clock frequency in    | synchronou  | ,                                                                                |

|          |                       | -           | 30 to 80 kHz (internal clock mode), external clock frequency                     |

| •        | Data length:          |             | 5 to 8 bits                                                                      |

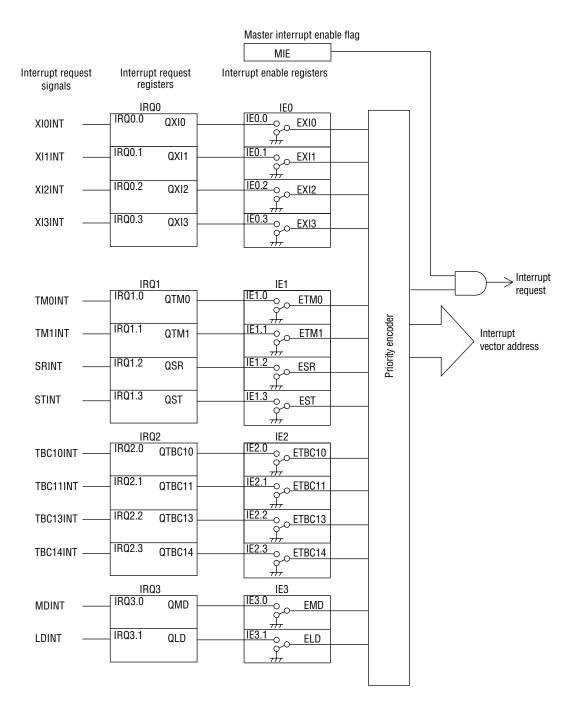

| p. Inter | rupt sources          |             |                                                                                  |

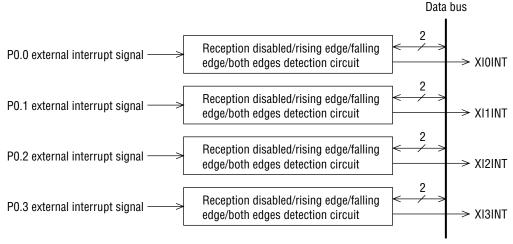

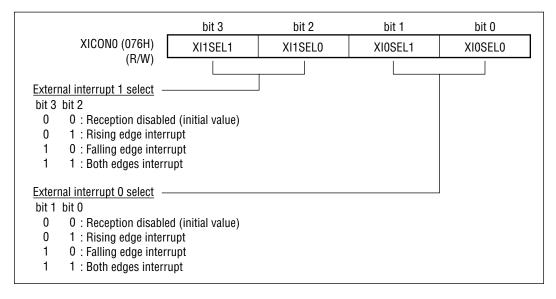

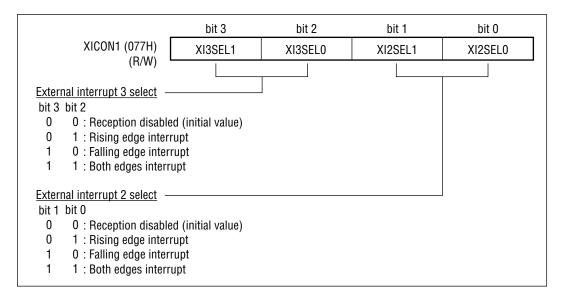

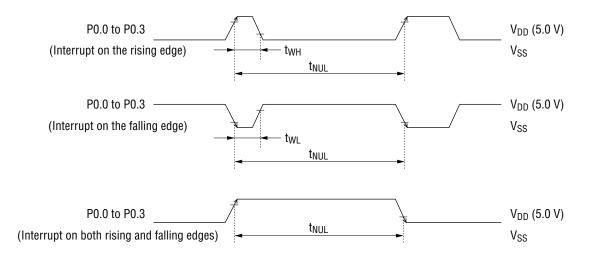

| •        | External interrupt (  | 4 sources): | Selectable as rising edge/falling edge/both rising and falling edges             |

| •        | Internal interrupt (1 | 0 sources): | Time base interrupt $\times$ 4 (2, 4, 16, and 32 Hz @ 32.768 kHz)                |

|          |                       |             | Timer interrupt $\times$ 2                                                       |

|          |                       |             | Level detector interrupt $\times$ 1                                              |

|          |                       |             | Serial port reception interrupt $\times$ 1                                       |

|          |                       |             | Serial port transmission interrupt $\times$ 1<br>Melody end interrupt $\times$ 1 |

|          |                       |             |                                                                                  |

| q. Ship  | ping products         |             |                                                                                  |

|          | Packa                 | ae          | Product                                                                          |

| 11 51                                                                     |                                |

|---------------------------------------------------------------------------|--------------------------------|

| Package                                                                   | Product                        |

| Chip (60 pads)                                                            | ML63512A-xxxWA, ML63514A-xxxWA |

| <ul> <li>48-pin flat package (48TQFP)<br/>TQFP48-P-0707-0.50-K</li> </ul> | ML63512A-xxxTB, ML63514A-xxxTB |

| <ul> <li>64-pin flat package (64TQFP)<br/>TQFP64-P-1010-0.50-K</li> </ul> | ML63512A-xxxTP, ML63514A-xxxTP |

|                                                                           |                                |

xxx indicates the ROM code number.

- r. Operating temperature

- −20 to +70°C

s. Power supply voltage

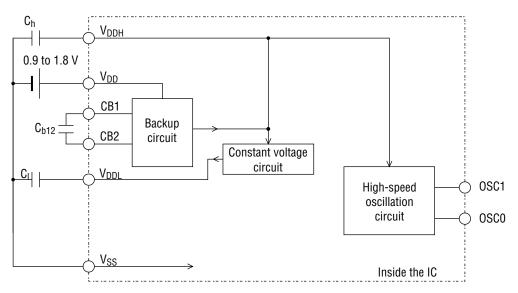

- When using backup: 0.9 to 1.8 V (Maximum operating frequency 1 MHz)

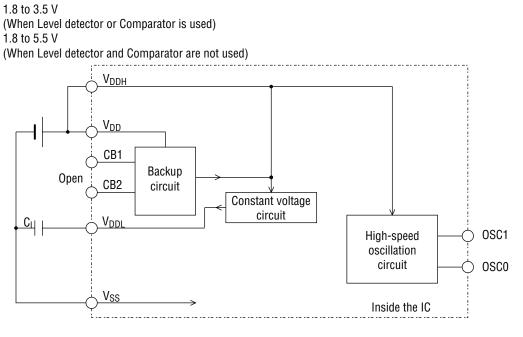

When not using backup: 1.8 to 3.5 V (Maximum operating frequency 2 MHz; when Level detector or Comparator is used) 1.8 to 5.5 V (Maximum operating frequency 2 MHz; when Level detector and Comparator are not used)

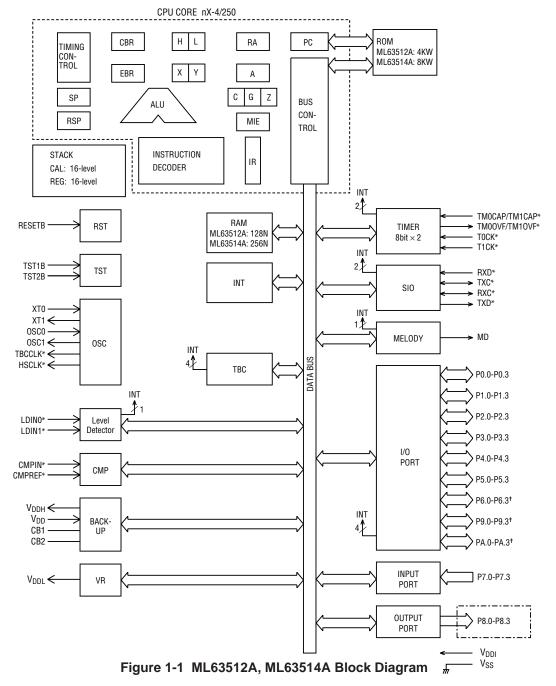

#### 1.3 Block Diagram

Block diagram of the ML63512A and ML63514A is shown in Figure 1-1.

Asterisks (\*) indicate the secondary function of each port. Signal names enclosed by chain lines (  $_{--}$  ) indicate interface signals of the V<sub>DDI</sub> power supply system.

Port 6 (P6.0 to P6.3)<sup>†</sup>, Port 9 (P9.0 to P9.3)<sup>†</sup> and Port A (PA.0 to PA.3)<sup>†</sup> are provided for the 64-pin packages and chips.

#### 1.4 Pin Configuration

#### 1.4.1 ML63512A, ML63514A Pin Configurations

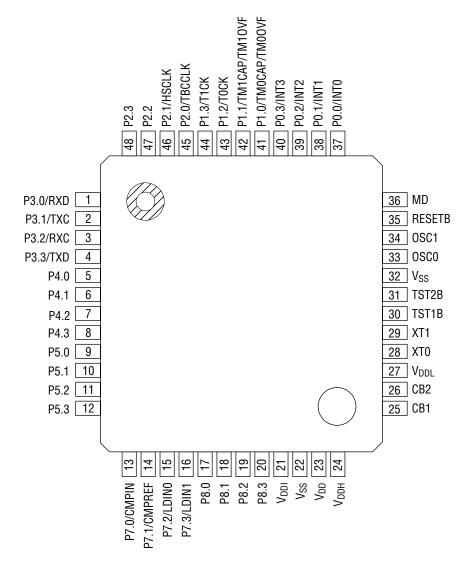

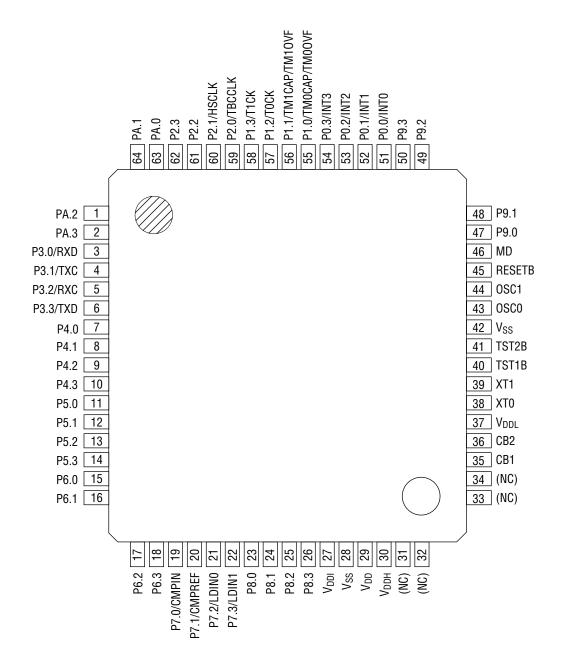

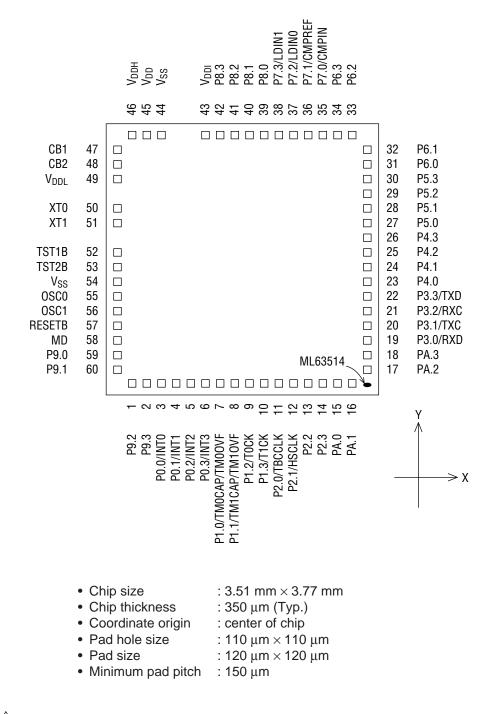

The 48-pin package (48TQFP) pin configuration, 64-pin package ((64TQFP) pin configuration, chip pin configuration, and pad coordinates of the ML63512A and ML63514A are shown in Figure 1-2, 1-3, 1-4, and Table 1-1, respectively.

NC (not connected) indicates an unused pin that is left unconnected (open).

Figure 1-2 ML63512A, ML63514A 48-Pin TQFP Pin Configuration (Top View) (Package : TQFP48-P-0707-0.50-K)

Figure 1-3 ML63512A, ML63514A 64-Pin TQFP Pin Configuration (Top View) (Package : TQFP64-P-1010-0.50-K)

Note: The chip substrate voltage is  $V_{SS}$ .

Figure 1-4 ML63512A, ML63514A Chip Pin Configuration (Top View)

|         |          |        |        |         |                  | Chip cent | er: X = 0, Y = 0 |

|---------|----------|--------|--------|---------|------------------|-----------|------------------|

| Pad No. | Pad Name | X (µm) | Υ (μm) | Pad No. | Pad Name         | X (μm)    | Y (µm)           |

| 1       | P9.2     | -1175  | -1717  | 31      | P6.0             | 1604      | 1018             |

| 2       | P9.3     | -1018  | -1717  | 32      | P6.1             | 1604      | 1175             |

| 3       | P0.0     | -862   | -1717  | 33      | P6.2             | 1175      | 1717             |

| 4       | P0.1     | -705   | -1717  | 34      | P6.3             | 1018      | 1717             |

| 5       | P0.2     | -548   | -1717  | 35      | P7.0             | 862       | 1717             |

| 6       | P0.3     | -392   | -1717  | 36      | P7.1             | 705       | 1717             |

| 7       | P1.0     | -235   | -1717  | 37      | P7.2             | 548       | 1717             |

| 8       | P1.1     | -78    | -1717  | 38      | P7.3             | 392       | 1717             |

| 9       | P1.2     | 78     | -1717  | 39      | P8.0             | 235       | 1717             |

| 10      | P1.3     | 235    | -1717  | 40      | P8.1             | 78        | 1717             |

| 11      | P2.0     | 392    | -1717  | 41      | P8.2             | -78       | 1717             |

| 12      | P2.1     | 548    | -1717  | 42      | P8.3             | -235      | 1717             |

| 13      | P2.2     | 705    | -1717  | 43      | V <sub>DDI</sub> | -392      | 1717             |

| 14      | P2.3     | 862    | -1717  | 44      | V <sub>SS</sub>  | -934      | 1717             |

| 15      | PA.0     | 1018   | -1717  | 45      | V <sub>DD</sub>  | -1090     | 1717             |

| 16      | PA.1     | 1175   | -1717  | 46      | V <sub>DDH</sub> | -1247     | 1717             |

| 17      | PA.2     | 1604   | -1175  | 47      | CB1              | -1604     | 1127             |

| 18      | PA.3     | 1604   | -1019  | 48      | CB2              | -1604     | 971              |

| 19      | P3.0     | 1604   | -862   | 49      | V <sub>DDL</sub> | -1604     | 814              |

| 20      | P3.1     | 1604   | -705   | 50      | XT0              | -1604     | 502              |

| 21      | P3.2     | 1604   | -549   | 51      | XT1              | -1604     | 345              |

| 22      | P3.3     | 1604   | -392   | 52      | TST1B            | -1604     | 76               |

| 23      | P4.0     | 1604   | -235   | 53      | TST2B            | -1604     | -81              |

| 24      | P4.1     | 1604   | -79    | 54      | V <sub>SS</sub>  | -1640     | -236             |

| 25      | P4.2     | 1604   | 78     | 55      | OSC0             | -1604     | -392             |

| 26      | P4.3     | 1604   | 235    | 56      | OSC1             | -1604     | -548             |

| 27      | P5.0     | 1604   | 391    | 57      | RESETB           | -1604     | -705             |

| 28      | P5.1     | 1604   | 548    | 58      | MD               | -1604     | -862             |

| 29      | P5.2     | 1604   | 705    | 59      | P9.0             | -1604     | -1018            |

| 30      | P5.3     | 1604   | 861    | 60      | P9.1             | -1604     | -1175            |

Table 1-1 ML63512A, ML63514A Pad Coordinates

1

#### 1.5 Pin Descriptions

#### 1.5.1 Descriptions of the Basic Functions of Each Pin

The basic functions of each pin of the ML63512A and ML63514A are listed in Table 1-2. Use of a backslash ("/") in a pin name indicates that the pin has a secondary function. Refer to section 1.5.2, "Descriptions of the Secondary Functions of Each Pin."

In the I/O column, "—" indicates a power supply pin, "I" indicates an input pin, "O" indicates an output pin, and "I/O" indicates an input/output pin.

For pin, "TB" denotes a 48-pin flat package (48TQFP), and "TP" a 64-pin flat package (64TQFP).

| <b>F</b> unction | Symphol          | Pin    | No.    | Pad    | Туре | Description                                                                                                                                                                                                                                      |  |

|------------------|------------------|--------|--------|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Function         | Symbol           | тв     | TP     | No.    |      | Description                                                                                                                                                                                                                                      |  |

|                  | V <sub>DD</sub>  | 23     | 29     | 45     | —    | Positive power supply                                                                                                                                                                                                                            |  |

|                  | V <sub>SS</sub>  | 22, 32 | 28, 42 | 44, 54 | —    | Negative power supply                                                                                                                                                                                                                            |  |

|                  | V <sub>DDI</sub> | 21     | 27     | 43     | _    | Positive power supply pin for external interface<br>(PORT8 supply)                                                                                                                                                                               |  |

| Power<br>Supply  | V <sub>DDL</sub> | 27     | 37     | 49     |      | Positive power supply pin for internal logic (internally generated).<br>A capacitor $C_{I}$ (0.1 $\mu$ F) should be connected between this pin and $V_{SS}$ .                                                                                    |  |

|                  | Vddh             | 24     | 30     | 46     |      | Voltage multiplier pin for power supply backup (internally generated). A capacitor $C_h$ (1.0 $\mu$ F) should be connected between this pin and $V_{SS}$ .                                                                                       |  |

|                  | CB1              | 25     | 35     | 47     | —    | Pins to connect a capacitor for voltage multiplier.                                                                                                                                                                                              |  |

|                  | CB2              | 26     | 36     | 48     | —    | A capacitor (1.0 $\mu$ F) should be connected between CB1 and CB2.                                                                                                                                                                               |  |

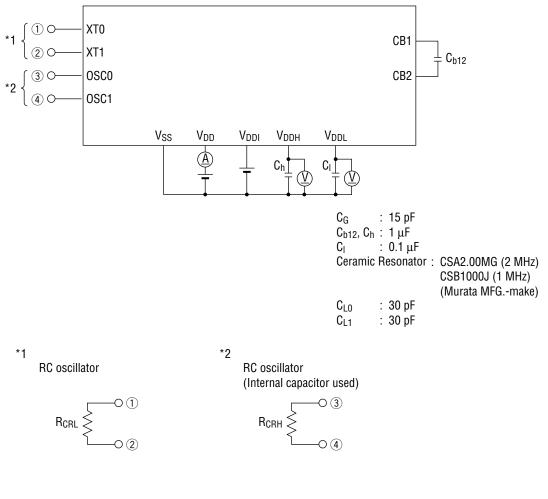

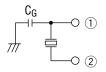

|                  | XT0              | 28     | 38     | 50     | I    | Low-speed clock oscillation pins.<br>Crystal oscillation or RC oscillation is selected by the mask<br>option.                                                                                                                                    |  |

|                  | XT1              | 29     | 39     | 51     | 0    | If crystal oscillation is selected, connect a crystal between XT0 and XT1, and connect capacitor ( $C_G$ ) between XT0 and $V_{SS}$ .<br>If RC oscillation is selected, connect external oscillation resistor ( $R_{CRL}$ ) between XT0 and XT1. |  |

| Oscillation      | OSC0             | 33     | 43     | 55     | I    | High-speed clock oscillation pins.<br>Ceramic oscillation or RC oscillation is selected by the mask<br>option.<br>If ceramic oscillation is selected, connect a ceramic resonator                                                                |  |

|                  | OSC1             | 34     | 44     | 56     | 0    | between OSCO and OSC1, and connect capacitor ( $C_{L0}$ , $C_{L1}$ )<br>between OSCO and $V_{SS}$ , OSC1 and $V_{SS}$ .<br>If RC oscillation is selected, connect external oscillation<br>resistor ( $R_{CRH}$ ) between OSCO and OSC1.          |  |

| Toot             | TST1B            | 30     | 40     | 52     | I    | Input pins for testing.                                                                                                                                                                                                                          |  |

| Test             | TST2B            | 31     | 41     | 53     |      | A pull-up resistor is internally connected to these pins.                                                                                                                                                                                        |  |

Table 1-2 Pin Description (Basic Functions)

| Function | Symbol                     | Pin | No. | Pad | <b>T</b> | Description                                                                                                                                                                                                                                                    |  |

|----------|----------------------------|-----|-----|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Function | Symbol                     | тв  | TP  | No. | Туре     | Description                                                                                                                                                                                                                                                    |  |

| Reset    | RESETB                     | 35  | 45  | 57  | I        | Reset input pin.<br>Setting this pin to "L" level puts this device into a reset state<br>Then, setting this pin to "H" level starts executing an<br>instruction from address 0000H.<br>An internal or external pull-up resistor is selected by<br>mask option. |  |

| Melody   | MD                         | 36  | 46  | 58  | 0        | Melody output pin (non-inverted output)                                                                                                                                                                                                                        |  |

|          | P0.0/INT0                  | 37  | 51  | 3   |          | 4-bit input-output ports.                                                                                                                                                                                                                                      |  |

|          | P0.1/INT1                  | 38  | 52  | 4   | 1/0      | In input mode, pull-up resistor input or high-impedance                                                                                                                                                                                                        |  |

|          | P0.2/INT2                  | 39  | 53  | 5   | 1/0      | input is selectable for each bit.                                                                                                                                                                                                                              |  |

|          | P0.3/INT3                  | 40  | 54  | 6   |          | In output mode, N-channel open drain output or CMOS                                                                                                                                                                                                            |  |

|          | P1.0/<br>TM0CAP/<br>TM0OVF | 41  | 55  | 7   |          | output is selectable for each bit.                                                                                                                                                                                                                             |  |

|          | P1.1/<br>TM1CAP/<br>TM1OVF | 42  | 56  | 8   | I/O      |                                                                                                                                                                                                                                                                |  |

|          | P1.2/T0CK                  | 43  | 57  | 9   |          |                                                                                                                                                                                                                                                                |  |

|          | P1.3/T1CK                  | 44  | 58  | 10  |          |                                                                                                                                                                                                                                                                |  |

|          | P2.0/TBCCLK                | 45  | 59  | 11  |          |                                                                                                                                                                                                                                                                |  |

| Dout     | P2.1/HSCLK                 | 46  | 60  | 12  | - 1/0    |                                                                                                                                                                                                                                                                |  |

| Port     | P2.2                       | 47  | 61  | 13  |          |                                                                                                                                                                                                                                                                |  |

|          | P2.3                       | 48  | 62  | 14  | ]        |                                                                                                                                                                                                                                                                |  |

|          | P3.0/RXD                   | 1   | 3   | 19  |          |                                                                                                                                                                                                                                                                |  |

|          | P3.1/TXC                   | 2   | 4   | 20  | 1/0      |                                                                                                                                                                                                                                                                |  |

|          | P3.2/RXC                   | 3   | 5   | 21  | 1/0      |                                                                                                                                                                                                                                                                |  |

|          | P3.3/TXD                   | 4   | 6   | 22  |          |                                                                                                                                                                                                                                                                |  |

|          | P4.0                       | 5   | 7   | 23  |          |                                                                                                                                                                                                                                                                |  |

|          | P4.1                       | 6   | 8   | 24  | I/O      |                                                                                                                                                                                                                                                                |  |

|          | P4.2                       | 7   | 9   | 25  | 1/0      |                                                                                                                                                                                                                                                                |  |

|          | P4.3                       | 8   | 10  | 26  |          |                                                                                                                                                                                                                                                                |  |

|          | P5.0                       | 9   | 11  | 27  |          |                                                                                                                                                                                                                                                                |  |

|          | P5.1                       | 10  | 12  | 28  | I/O      |                                                                                                                                                                                                                                                                |  |

|          | P5.2                       | 11  | 13  | 29  |          |                                                                                                                                                                                                                                                                |  |

|          | P5.3                       | 12  | 14  | 30  |          |                                                                                                                                                                                                                                                                |  |

#### Table 1-2 Pin Description (Basic Functions) (continued)

1

| <b>F</b> unction | Symbol      | Pin No. |    | Pad | Turne | Description                                                                              |  |

|------------------|-------------|---------|----|-----|-------|------------------------------------------------------------------------------------------|--|

| Function         |             | тв      | TP | No. | Туре  | Description                                                                              |  |

|                  | P6.0        | _       | 15 | 31  |       | 4-bit input-output port.<br>In input mode, pull-up resistor input or high-impedance      |  |

|                  | P6.1        | _       | 16 | 32  | - 1/0 | input is selectable for each bit.<br>In output mode, N-channel open drain output or CMOS |  |

|                  | P6.2        | _       | 17 | 33  | 1/0   | output is selectable for each bit.                                                       |  |

|                  | P6.3        | —       | 18 | 34  |       | Note that these pins are available for a 64-pin package and chip.                        |  |

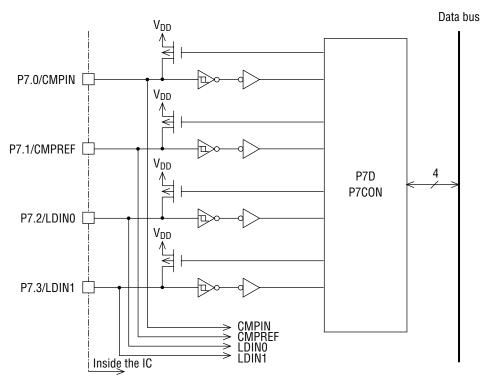

|                  | P7.0/CMPIN  | 13      | 19 | 35  |       | 4-bit input port.                                                                        |  |

|                  | P7.1/CMPREF | 14      | 20 | 36  | ·     | Pull-up resistor input or high-impedance input is selectable for each bit.               |  |

|                  | P7.2/LDIN0  | 15      | 21 | 37  |       |                                                                                          |  |

|                  | P7.3/LDIN1  | 16      | 22 | 38  |       |                                                                                          |  |

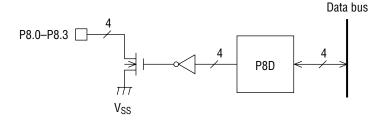

| Port             | P8.0        | 17      | 23 | 39  |       | 4-bit output port.                                                                       |  |

|                  | P8.1        | 18      | 24 | 40  | 0     | N-channel open drain output.                                                             |  |

|                  | P8.2        | 19      | 25 | 41  |       |                                                                                          |  |

|                  | P8.3        | 20      | 26 | 42  |       |                                                                                          |  |

|                  | P9.0        | _       | 47 | 59  |       | 4-bit input-output ports.                                                                |  |

|                  | P9.1        | _       | 48 | 60  | 1/0   | In input mode, pull-up resistor input or high-impedance                                  |  |

|                  | P9.2        | —       | 49 | 1   | 1/0   | input is selectable for each bit.                                                        |  |

|                  | P9.3        | —       | 50 | 2   |       | In output mode, N-channel open drain output or CMOS                                      |  |

|                  | PA.0        | _       | 63 | 15  |       | output is selectable for each bit.                                                       |  |

|                  | PA.1        | _       | 64 | 16  | 1/0   | Note that these pins are available for a 64-pin package                                  |  |

|                  | PA.2        | _       | 1  | 17  | 1/0   | and chip.                                                                                |  |

|                  | PA.3        | _       | 2  | 18  | 1     |                                                                                          |  |

#### Table 1-2 Pin Description (Basic Functions) (continued)

#### 1.5.2 Descriptions of the Secondary Functions of Each Pin

The secondary functions of each pin of the ML63512A and ML63514A are listed in Table 1-3.

| Function    | Symbol      | Pin | No. | Pad | Tunc | Description                                                           |  |

|-------------|-------------|-----|-----|-----|------|-----------------------------------------------------------------------|--|

| Function    | Symbol      | тв  | TP  | No. | Туре | Description                                                           |  |

|             |             |     |     |     |      | External 0 interrupt input pin.                                       |  |

|             | P0.0/INT0   | 37  | 51  | 3   | 1    | Edge detection can be selected from one of a rising edge,             |  |

|             |             |     |     |     |      | a falling edge, or both rising and falling edges.                     |  |

|             |             |     |     |     |      | External 1 interrupt input pin.                                       |  |

|             | P0.1/INT1   | 38  | 52  | 4   | I    | Edge detection can be selected from one of a rising edge,             |  |

| External    |             |     |     |     |      | a falling edge, or both rising and falling edges.                     |  |

| Interrupt   |             |     |     |     |      | External 2 interrupt input pin.                                       |  |

|             | P0.2/INT2   | 39  | 53  | 5   | 1    | Edge detection can be selected from one of a rising edge,             |  |

|             |             |     |     |     |      | a falling edge, or both rising and falling edges.                     |  |

|             |             |     |     |     |      | External 3 interrupt input pin.                                       |  |

|             | P0.3/INT3   | 40  | 54  | 6   | 1    | Edge detection can be selected from one of a rising edge,             |  |

|             |             |     |     |     |      | a falling edge, or both rising and falling edges.                     |  |

| Conturo     | P1.0/TM0CAP | 41  | 55  | 7   | I    | Timer 0 (TM0) capture trigger input pin.                              |  |

| Capture     | P1.1/TM1CAP | 42  | 56  | 8   | I    | Timer 1 (TM1) capture trigger input pin.                              |  |

|             | P1.0/TM00VF | 41  | 55  | 7   | 0    | Timer 0 (TM0) overflow flag output pin.                               |  |

| Timer       | P1.1/TM10VF | 42  | 56  | 8   | 0    | Timer 1 (TM1) overflow flag output pin.                               |  |

| Timer       | P1.2/T0CK   | 43  | 57  | 9   | I    | Timer 0 (TM0) external clock input pin.                               |  |

|             | P1.3/T1CK   | 44  | 58  | 10  | I    | Timer 1 (TM1) external clock input pin.                               |  |

| Oscillation | P2.0/TBCCLK | 45  | 59  | 11  | 0    | Low-speed oscillation clock output pin.                               |  |

| Output      | P2.1/HSCLK  | 46  | 60  | 12  | 0    | High-speed oscillation clock output pin.                              |  |

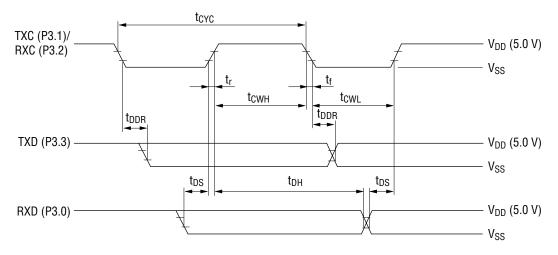

|             | P3.0/RXD    | 1   | 3   | 19  | I    | Serial port receive data input pin.                                   |  |

|             |             |     | 4   |     |      | Sync serial port clock input-output pin.                              |  |

|             |             |     |     | 20  |      | Transmit sync clock input-output pin when a serial port is used       |  |

|             | P3.1/TXC    | 2   |     |     | I/0  | synchronously.                                                        |  |

|             |             |     |     |     |      | Transmit clock output when this device is used as a master processor. |  |

| Serial      |             |     |     |     |      | Transmit clock input when this device is used as a slave processor.   |  |

| Port        |             |     |     |     |      | Sync serial port clock input-output pin.                              |  |

|             |             |     |     |     |      | Receive sync clock input-output pin when a serial port is used        |  |

|             | P3.2/RXC    | 3   | 5   | 21  | I/0  | synchronously.                                                        |  |

|             |             |     |     |     |      | Receive clock output when this device is used as a master processor.  |  |

|             |             |     |     |     |      | Receive clock input when this device is used as a slave processor.    |  |

|             | P3.3/TXD    | 4   | 6   | 22  | 0    | Serial port transmit data output pin.                                 |  |

| Comparator  | P7.0/CMPIN  | 13  | 19  | 35  | I    | Comparator analog input pin.                                          |  |

| Comparator  | P7.1/CMPREF | 14  | 20  | 36  | I    | Comparator reference voltage input pin.                               |  |

| Level       | P7.2/LDIN0  | 15  | 21  | 37  | I    | Level detector analog input pin.                                      |  |

| Detector    | P7.3/LDIN1  | 16  | 22  | 38  | I    | Level detector analog input pin.                                      |  |

#### 1.5.3 Unused Pin Processing

Table 1-4 lists the handling of unused pins.

| Pin          | Recommended pin handling           |

|--------------|------------------------------------|

| TST1B, TST2B | Open or V <sub>DD</sub>            |

| MD           | Open                               |

| OSCO, OSC1   | Open                               |

| CB1, CB2     | Open                               |

| P0.0-P0.3    | Open                               |

| P1.0-P1.3    | V <sub>DD</sub> or V <sub>SS</sub> |

| P2.0-P2.3    | V <sub>DD</sub> or V <sub>SS</sub> |

| P3.0–P3.3    | V <sub>DD</sub> or V <sub>SS</sub> |

| P4.0-P4.3    | V <sub>DD</sub> or V <sub>SS</sub> |

| P5.0–P5.3    | V <sub>DD</sub> or V <sub>SS</sub> |

| P6.0-P6.3    | Open                               |

| P7.0-P7.3    | V <sub>DD</sub> or V <sub>SS</sub> |

| P8.0–P8.3    | Open                               |

| P9.0–P9.3    | Open                               |

| PA.0-PA.3    | Open                               |

#### Table 1-4 Unused Pin Handling

Notes:

- 1. If a pin set as a high impedance input is left unconnected, the supply current may become excessive. Therefore, it is recommended that unused input ports and input/output ports be set as inputs with either a pull-down or pull-up resistor.

- When test pins TST1 and TST2 are left unconnected, malfunction may result if there is a large amount of external noise. Therefore, it is recommended to permanently connect TST1 and TST2 to V<sub>DD</sub>.

#### 1.6 Basic Timing

#### 1.6.1 Basic Timing of CPU Operation

The low-speed oscillation clock from the XT0/XT1 pins or the high-speed oscillation clock from the OSC0/OSC1 pins are used without frequency division as the system clock (CLK). The system clock signal is in phase with the signal from the XT0 pin or the OSC0 pin.

As shown in Figure 1-5, a single machine cycle is composed of two states, S1 and S2. One state is the interval from a falling edge of CLK to the falling edge of the next CLK.

Instructions are processed in machine cycle units and each instruction is executed in 1 to 3 machine cycles. Instructions are classified according to the number of machine cycles: 1 machine cycle instructions (M1), 2 machine cycle instructions (M1 + M2), and 3 machine cycle instructions (M1 + M2 + M3).

M1 M1 M2 M1 M2 M3 CLK S2 S1 S1 S2 S1 S2 S1 S2 **S1** S2 S1 S2 ł. (2 clocks) (4 clocks) (6 clocks) 1 machine cycle 2 machine cycles 3 machine cycles

Most instructions are executed in 1 machine cycle.

Figure 1-5 Clock Configuration of Each Machine Cycle

#### 1.6.2 Port I/O Basic Timing

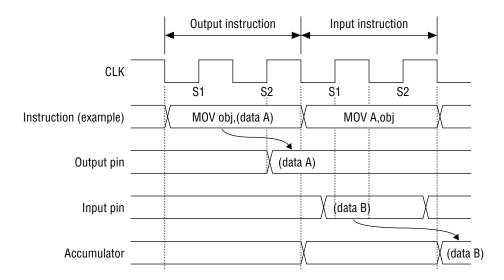

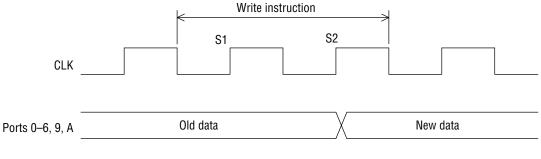

Figure 1-6 shows the basic I/O timing.

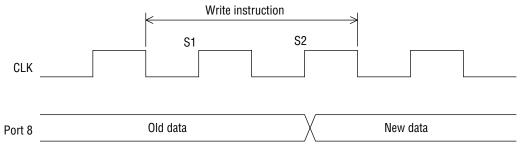

During the execution of an instruction that outputs data to a port, setting data (data A) is output at the rising edge of the clock in the S2 state during the machine cycle of that instruction.

During the execution of an instruction that inputs data from a port, data at the input pin (data B) is captured internally while the clock is at a "H" level in the S1 state during the machine cycle of that instruction. That data is transferred to the accumulator at the start of the next machine cycle.

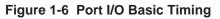

Note:

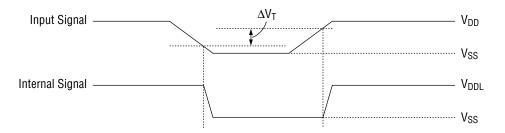

Regarding input signals

"0" will be captured in the internal register if a "L" level is input to the input pin even once ( $\bigcirc$  of Figure 1-7) during the data capture interval.

"1" will be captured in the internal register only if a "H" level is maintained (② of Figure 1-7) throughout the data capture interval.

Therefore, if noise occurs in the input data, implement noise reduction measures with the program and peripheral devices.

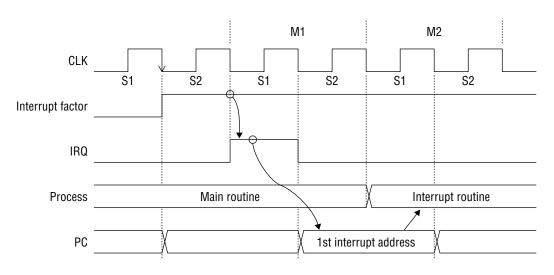

#### 1.6.3 Interrupt Basic Timing

Figure 1-8 shows the basic interrupt timing.

As shown in the figure, when an interrupt factor is generated, the interrupt factor is sampled at the falling edge of CLK and an interrupt request (IRQ) is set at the first half of S1.

When an interrupt condition is established and the CPU receives an interrupt, the interrupt routine will start beginning from the next machine cycle.

Figure 1-8 Interrupt Basic Timing

## Chapter 2

# **CPU and Memory Spaces**

### Chapter 2 CPU and Memory Spaces

#### 2.1 Overview

The ML63512A and ML63514A have an internal Oki's original CPU core nX-4/250.

The instruction set of the nX-4/250 core consists of 407 types of instructions.

The memory space consists of a 16-bit wide program memory space and a 4-bit wide data memory space. A stack for saving the program counter during a subroutine call or interrupt (call stack) and a stack for saving registers during a PUSH instruction (register stack) are provided separately from the memory space.

The program memory space is used for program data, ROM table data and melody note data.

In the data memory space, special function registers (SFRs) are located in bank 0, and data RAM in bank 1 (128 nibbles for the ML63512A, 256 nibbles for the ML63514A).

#### 2.2 Registers

The nX-4/250 core processes data mainly with the accumulator and register set.

The register set is a programming model consisting of the HL and XY registers that store data memory addresses, the current bank register (CBR), the extra bank register (EBR), the RA register that stores program memory addresses, registers that control program flow, and registers that control flags and memory.

#### 2.2.1 Accumulator (A)

The accumulator (A) is the central register for various arithmetic operations.

At system reset, the accumulator is initialized to "0". When an interrupt occurs, a "PUSH HL" instruction can be used if necessary to save the accumulator on the register stack. The accumulator can be restored with a "POP HL" instruction.

#### 2.2.2 Flag Register

The flag register consists of 3 flags: the carry flag (C), the zero flag (Z) and the G flag (G). When an interrupt occurs, a "PUSH HL" instruction can be used if necessary to save the flag register on the register stack. The flag register can be restored with a "POP HL" instruction.

| G             | С | Ζ |  |  |  |  |  |

|---------------|---|---|--|--|--|--|--|

| Flag register |   |   |  |  |  |  |  |

#### 2.2.2.1 Carry Flag (C)

The carry flag (C) is a 1-bit flag that is loaded with a carry during addition or a borrow during subtraction. At system reset, the carry flag is initialized to "0".

#### 2.2.2.2 Zero Flag (Z)

The zero flag (Z) is a 1-bit flag that is set to "1" when the contents of the accumulator (A) are loaded with "0H". The zero flag is set to "0" when the contents of the accumulator (A) are loaded with a value other than "0H". However, the XCH instruction does not change the zero flag. At system reset, the zero flag is initialized to "0".

#### 2.2.2.3 G Flag (G)

The G flag (G) changes to "1" when the HL, XY or RA registers overflow as the result of execution of a post-increment register indirect addressing instruction or as the result of an increment instruction for the HL, XY or RA registers. At system reset, the G flag is initialized to "0".

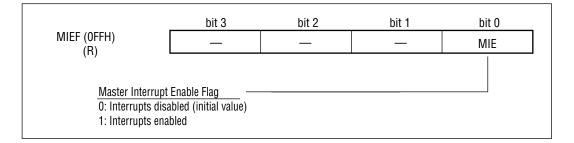

#### 2.2.3 Master Interrupt Enable Flag (MIE)

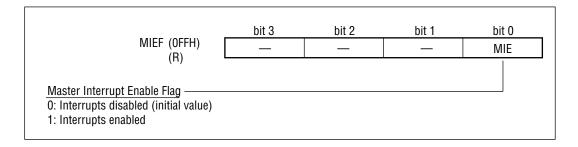

MIE (bit 0 of MIEF) is a flag that disables or enables all interrupts. MIEF is a 4-bit register in which bit 0 is the master interrupt enable flag (MIE).

If MIE is "0", all interrupts are disabled. If MIE is "1", all interrupts are enabled.

When any interrupt is received, MIE is cleared to "0". MIE is set to "1" by execution of a return from interrupt instruction (RTI instruction).

If multi-level interrupt processing is to be performed, execute a RTI instruction (MIE $\leftarrow$ "1") during the interrupt processing routines.

At system reset, MIE is initialized to "0". MIEF only supports data reference (R) of data memory through addressing instructions.

Note:

When setting MIE, use "EI" instructions (MIE $\leftarrow$ "1") and "DI" instructions (MIE $\leftarrow$ "0").

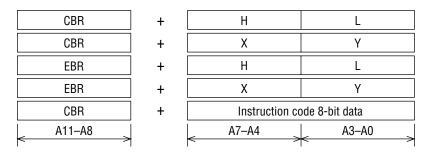

# 2.2.4 Current Bank Register (CBR), Extra Bank Register (EBR), HL Register (HL), XY Register (XY)

The CBR, EBR, HL, and XY registers are used for indirect addressing of data memory.

The CBR and EBR registers indicate the data memory bank. The HL and XY registers indicate addresses in the bank. CBR is also used in combination with 8-bit data in the instruction code for direct addressing within the current bank.

Figure 2-1 shows the various register combinations.

Figure 2-1 Various Register Combinations

A11 to A0 in Figure 2-1 indicate data memory addresses (4K nibbles max.).

At system reset, the CBR, EBR, HL, and XY registers are initialized to "0".

When an interrupt occurs, a "PUSH HL" or "PUSH XY" instruction can be used if necessary to save the CBR, EBR, HL, and XY registers on the register stack. These registers can be restored with a "POP HL" or "POP XY" instruction.

The CBR, EBR, HL, and XY registers are assigned to special function register (SFR) addresses 0F9H to 0FEH.

|            | bit 3          | bit 2          | bit 1          | bit 0          |

|------------|----------------|----------------|----------------|----------------|

| EBR (OFEH) | e <sub>3</sub> | e2             | е1             | eo             |

| (R/W)      | bit 3          | bit 2          | bit 1          | bit 0          |

| CBR (OFDH) | C3             | C2             | C1             | C <sub>0</sub> |

| (R/W)      | bit 3          | bit 2          | bit 1          | bit 0          |

| H (OFCH)   | h <sub>3</sub> | h <sub>2</sub> | h <sub>1</sub> | h <sub>0</sub> |

| (R/W)      | bit 3          | bit 2          | bit 1          | bit 0          |

| L (OFBH)   | l <sub>3</sub> | l <sub>2</sub> | l <sub>1</sub> | I <sub>0</sub> |

| (R/W)      | bit 3          | bit 2          | bit 1          | bit 0          |

| X (OFAH)   | x <sub>3</sub> | Х <sub>2</sub> | Х <sub>1</sub> | X0             |

| (R/W)      | bit 3          | bit 2          | bit 1          | bit 0          |

| Y (0F9H)   | У3             | У2             | У1             | Уо             |

#### 2.2.5 Program Counter (PC)

The program counter (PC) is a counter with 16 valid bits that specifies the program memory space.

#### 2.2.6 RA Registers (RA3, RA2, RA1, RA0)

The RA registers are used for indirect program memory addressing (ROM table reference instructions).

Figure 2-2 shows the address configuration of the RA registers.

| RA3     | RA2    | RA1   | RA0   |

|---------|--------|-------|-------|

| A15-A12 | A11-A8 | A7-A4 | A3-A0 |

Figure 2-2 Address Configuration of RA3 to RA0 Registers

Within the A15 to A0 of Figure 2-2, A14 to A0 indicate program memory addresses (32K words max.).

RA3 to RA0 are assigned to special function register (SFR) addresses 0F2H to 0F5H.

|            | bit 3           | bit 2           | bit 1           | bit 0           |

|------------|-----------------|-----------------|-----------------|-----------------|

| RA3 (0F5H) | a <sub>15</sub> | a <sub>14</sub> | a <sub>13</sub> | a <sub>12</sub> |

| (R/W)      | bit 3           | bit 2           | bit 1           | bit 0           |

| RA2 (0F4H) | a <sub>11</sub> | a <sub>10</sub> | a <sub>g</sub>  | a <sub>8</sub>  |

| (R/W)      | hit 0           | hit 0           | h:t 1           | hit O           |

|            | bit 3           | bit 2           | bit 1           | bit 0           |

| RA1 (0F3H) | a <sub>7</sub>  | a <sub>6</sub>  | a <sub>5</sub>  | a <sub>4</sub>  |

| (R/W)      |                 |                 |                 |                 |

|            | bit 3           | bit 2           | bit 1           | bit 0           |

| RA0 (0F2H) | a <sub>3</sub>  | a <sub>2</sub>  | a <sub>1</sub>  | a <sub>0</sub>  |

| (R/W)      |                 |                 |                 |                 |

At system reset, RA3 to RA0 are initialized to "0".

Note:

When executing a ROM table reference instruction that uses RA registers, do not use addresses located in the SFR area to transfer ROM table data to RA registers, otherwise indirect addressing of program memory will not operate properly.

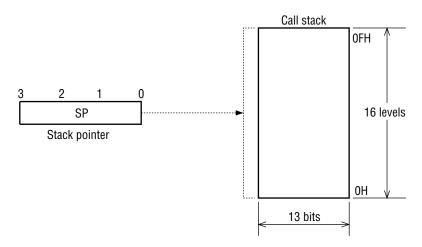

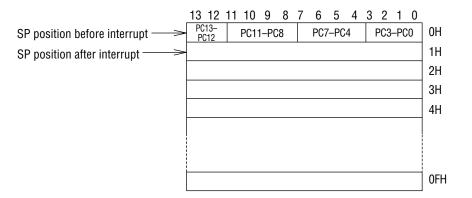

#### 2.2.7 Stack Pointer (SP) and Call Stack

The stack pointer (SP) is a pointer that indicates the call stack address where the program counter is saved when a subroutine call or interrupt occurs.

The SP is a 4-bit up/down counter that is incremented during stack saves and is decremented during stack restores.

The call stack has 16 levels from address 0H to address 0FH. Because the hardware requires 1 level of the call stack during program execution, only 15 levels can be used for stack saves. The contents of the call stack cannot be read or written by the program.

Figure 2-3 shows the relation between SP and the call stack.

Figure 2-3 Relation Between SP and Call Stack

SP is assigned to special function register (SFR) address 0F7H.

|           | bit 3 | bit 2 | bit 1 | bit 0 |

|-----------|-------|-------|-------|-------|

| SP (0F7H) | SP3   | SP2   | SP1   | SP0   |

| (R)       |       |       |       |       |

At system reset, SP is initialized to "0" and points to address "0H" of the call stack. SP is a read-only register and writes are invalid.

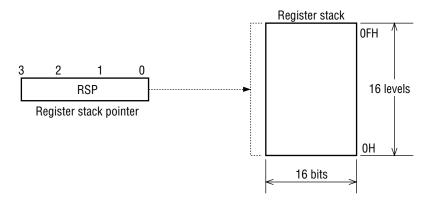

#### 2.2.8 Register Stack Pointer (RSP) and Register Stack

The register stack pointer (RSP) is a pointer that indicates the register stack address for saving various registers.

RSP is a 4-bit up/down counter that is incremented during stack saves (execution of PUSH instructions) and is decremented during stack restores (execution of POP instructions).

The register stack has 16 levels from address 0H to address 0FH. The contents of the register stack cannot be read or written by the program.

Figure 2-4 shows the relation between RSP and the register stack.

Figure 2-4 Relation Between RSP and Register Stack

The various registers shown in Figure 2-5 are saved onto and restored from the register stack by PUSH and POP instructions.

| "PU       | "PUSH HL" and "POP HL" instruction execution |    |    |    |    |    |   |   |   |        |   |   |          |   |   |   |

|-----------|----------------------------------------------|----|----|----|----|----|---|---|---|--------|---|---|----------|---|---|---|

|           | 15                                           | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6      | 5 | 4 | 3        | 2 | 1 | 0 |

| — G C Z A |                                              |    | -  |    | ŀ  | 1  | I |   |   | _<br>I |   |   |          |   |   |   |

|           | Register stack                               |    |    |    |    |    |   |   |   |        |   |   |          |   |   |   |

| "PU       | "PUSH XY" and "POP XY" instruction execution |    |    |    |    |    |   |   |   |        |   |   |          |   |   |   |

|           | 15                                           | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6      | 5 | 4 | 3        | 2 | 1 | 0 |

|           | EBR                                          |    |    |    | CB | R  | - |   | ) | (      |   |   | <b>۱</b> | 1 |   |   |

|           | Register stack                               |    |    |    |    |    |   |   |   |        |   |   |          |   |   |   |

```

Figure 2-5 Register Save/Restore by Execution of PUSH/POP Instructions

```

RSP is assigned to special function register (SFR) address 0F6H.

|            | bit 3 | bit 2 | bit 1 | bit 0 |

|------------|-------|-------|-------|-------|

| RSP (0F6H) | rsp3  | rsp2  | rsp1  | rsp0  |

| (R/W)      |       |       |       |       |

At system reset, RSP is initialized to "0" and points to address "0H" of the register stack.

#### 2.3 Memory Spaces

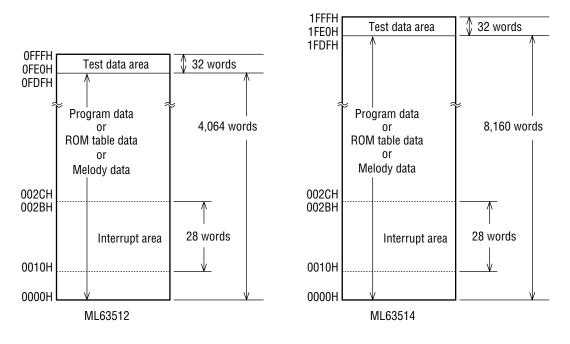

#### 2.3.1 Program Memory Space

The program memory space is the read-only memory that stores program data.

The program memory space has a data length of 16 bits and extends from address 0000H to address 0FFFH in the ML63512A and from address 0000H to address 1FFFH in the ML63514A.

In addition to program data, the program memory can also store ROM table data and the melody data. Figure 2-6 shows the configuration of the program memory space.

Figure 2-6 Program Memory Space Configuration

After system reset, instruction execution begins at address 0000H. The interrupt area from address 0010H to address 002BH contains starting addresses of the interrupt processing routines that are executed when interrupts are generated. (Refer to Chapter 4, "Interrupt.")

ROM table data is transferred to data memory by ROM table reference instructions.

The melody data defines the tone, tone length, and end tone used in the melody circuit of the ML63512A/514A. After an MSA instruction specifies the starting address, the melody data is automatically transferred to the melody circuit when a melody data interrupt occurs. (Refer to Chapter 10, "Melody Driver.")

Because the test data area contains program data for testing, it cannot be used as a program data area.

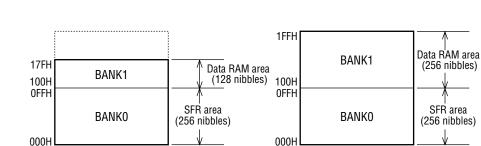

#### 2.3.2 Data Memory Space

ML63512A

The data memory space contains data RAM and special function registers (SFRs).

The data memory consists of 2 banks. One bank unit is 256 nibbles. Bank 0 is allocated as a SFR area, and bank 1 is data RAM (from address 100H to address 17FH for the ML63512A; from address 100H to address 1FFH for the ML63514A).

Figure 2-7 shows the configuration of the data memory space.

Figure 2-7 Data Memory Space Configuration

ML63514A

## **Chapter 3**

# **CPU Control Functions**

### Chapter 3 CPU Control Functions

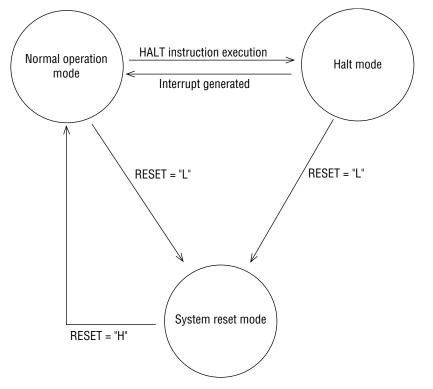

#### 3.1 Overview

Operating states, including system reset, are classified as follows.

- Normal operation mode

- System reset mode

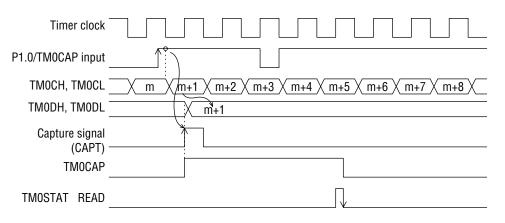

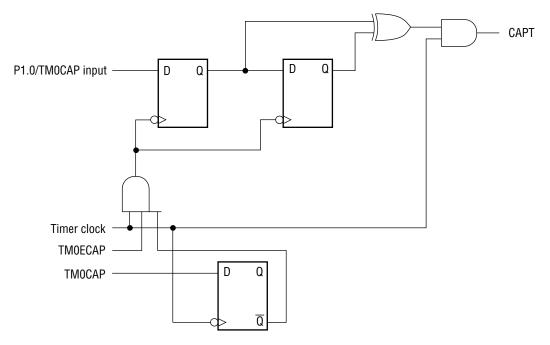

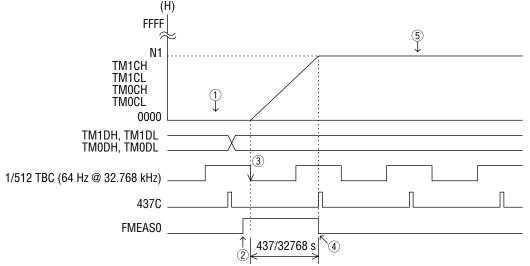

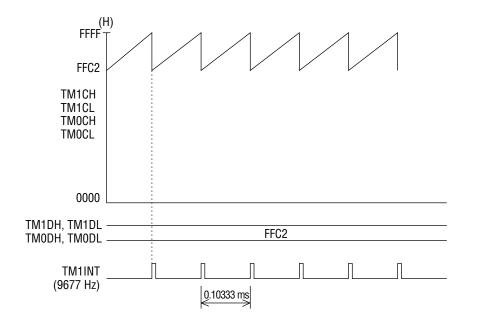

- Halt mode