# **MSM6352**

Built-in DTMF Generator 4-Bit Microcontroller

# **GENERAL DESCRIPTION**

The MSM6352 is a high-performance 4-bit microcontroller employing complementary metal oxide semiconductor technology. The use of this device for a repertory telephone, which employed a conventional microcomputer that was difficult to be configured in a single-chip device, allows a compact and high-performance telephone set to be monufactured easily.

# FEATURES

| <ul> <li>Lower power consumption</li> </ul>        |                                           |

|----------------------------------------------------|-------------------------------------------|

| · ·                                                | : $2048 \times 14$ bits                   |

| • ROM                                              | : $640 \times 4$ bits                     |

| • I/O port                                         |                                           |

| *                                                  | : 1 port $\times$ 4 bits                  |

|                                                    | : $3 \text{ ports} \times 4 \text{ bits}$ |

| Output port                                        | : $3 \text{ ports} \times 4 \text{ bits}$ |

| • DTMF generator                                   | L .                                       |

| • Built-in programmable timer                      |                                           |

| Applicable for dial pulse output                   |                                           |

| (Positive phase/negative phase, 34%/40%,           | , 10 pps/20 pps selectable)               |

| • Watch dog timer                                  |                                           |

| • Stack                                            | : 5 Level                                 |

| <ul> <li>Power down by STOP instruction</li> </ul> |                                           |

| • Instructions useful for data management (d       | data search and block data transfer)      |

| • Operating voltage                                | : 2.0 to 5.5V (2.2 to 5.5V in Tone mode)  |

| • 3.58 MHz oscillator                              |                                           |

| <ul> <li>Instruction execution time</li> </ul>     | :17.9 μs                                  |

| <ul> <li>Package options:</li> </ul>               |                                           |

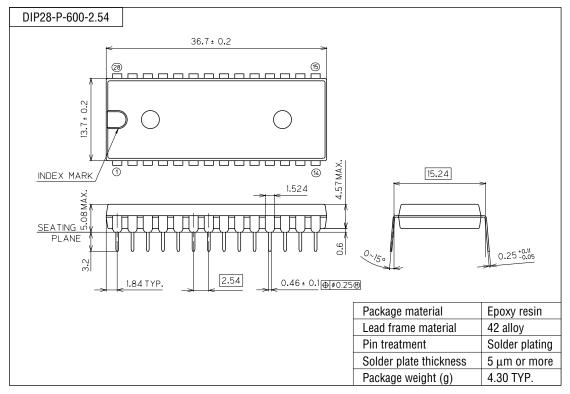

| 28-pin plastic DIP (DIP28-P-600-2.54)              | : (Product name: MSM6352-××RS)            |

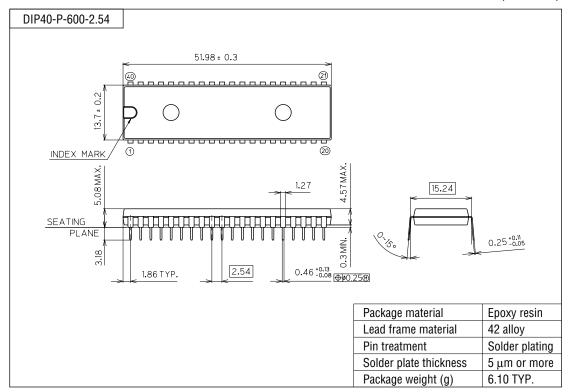

| 40-pin plastic DIP (DIP40-P-600-2.54)              | : (Product name: MSM6352-××RS)            |

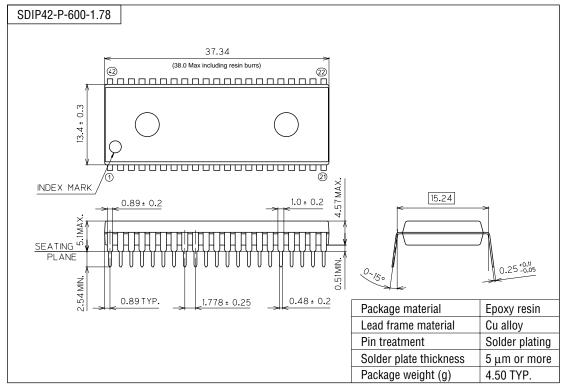

| 42-pin plastic shrink DIP (SDIP42-P-600-           | -1.78) : (Product name: MSM6352-××SS)     |

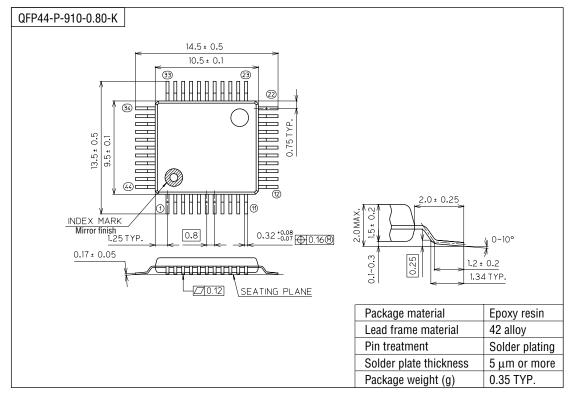

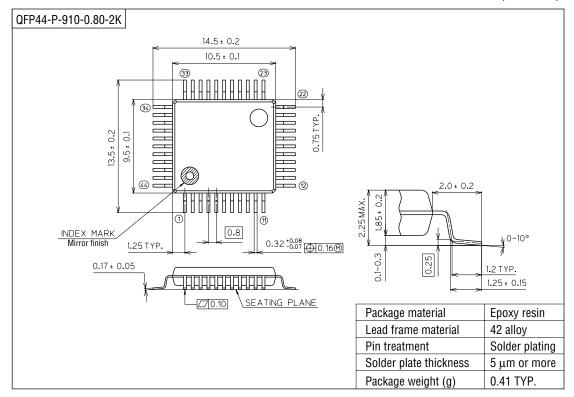

| 44-pin plastic QFP (QFP44-P-910-0.80-K)            | () : (Product name: MSM6352-××GS-K)       |

| 44-pin plastic QFP (QFP44-P-910-0.80-2)            |                                           |

|                                                    | ×× indicates the code number.             |

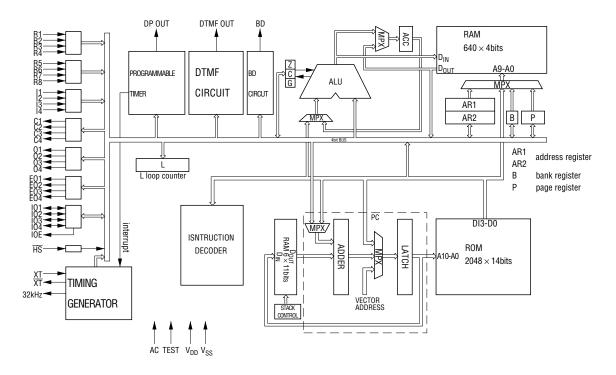

# **BLOCK DIAGRAM**

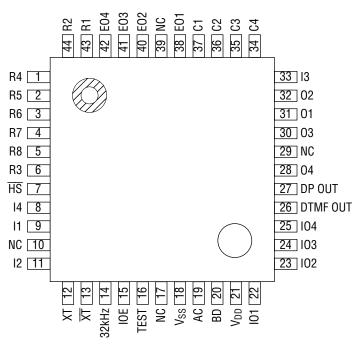

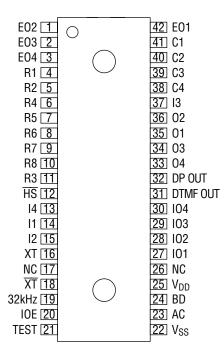

# **PIN CONFIGURATION (TOP VIEW)**

NC : No-connection pin

44-Pin Plastic QFP

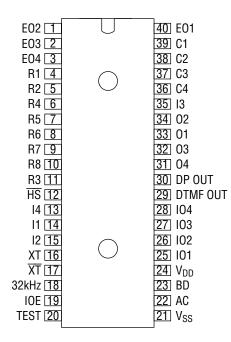

# PIN CONFIGURATION (TOP VIEW) (Continued)

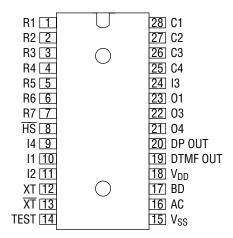

28-Pin Plastic DIP

#### **40-Pin Plastic DIP**

NC : No-connection pin

42-Pin Plastic Shrink DIP

# **PIN DESCRIPTIONS**

| Symbol          | Description                                                                                 |  |  |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------|--|--|--|--|--|

| V <sub>DD</sub> | Power source                                                                                |  |  |  |  |  |

| V <sub>SS</sub> | Circuit ground potential                                                                    |  |  |  |  |  |

| 4.0             | Pin to clear internal logic, pulled down to Vss.                                            |  |  |  |  |  |

| AC              | After power is turned on, the MSM6352 must be reset by this pin.                            |  |  |  |  |  |

| тгот            | Pin to test internal logic, pulled down to Vss.                                             |  |  |  |  |  |

| TEST            | This pin must be open in normal operation.                                                  |  |  |  |  |  |

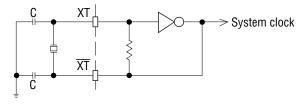

|                 | Input and output pins of oscillator inverter.                                               |  |  |  |  |  |

| XT, XT          | 3.58 MHz ceramic resonator and capacitors is connedted to these pins.                       |  |  |  |  |  |

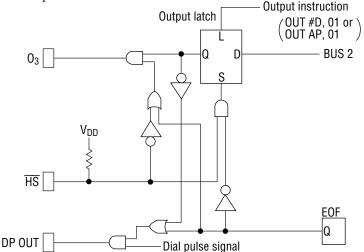

| HS              | Input pin connected to the hook switch, pulled up to VDD.                                   |  |  |  |  |  |

|                 | Output pin of dial pulse                                                                    |  |  |  |  |  |

| DP OUT          | Dial pulse rate (10 pps or 20 pps) and Make Break ratio (40% or 33%) can be selected by     |  |  |  |  |  |

|                 | software.                                                                                   |  |  |  |  |  |

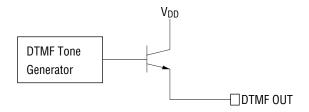

| DTMF OUT        | Output pin of DTMF signal                                                                   |  |  |  |  |  |

| BD              | Output pin of buzzer sound                                                                  |  |  |  |  |  |

| 32 kHz          | Output pin of 32 kHz clock                                                                  |  |  |  |  |  |

| R1 to R4        | In much mouth multipal electron de Mar                                                      |  |  |  |  |  |

| R5 to R8        | Input port pulled down to Vss                                                               |  |  |  |  |  |

|                 | Input port having clocked pull-down resistor to Vss                                         |  |  |  |  |  |

| l1 to l4        | Only when this port is accessed, pull-down resistors are connected to this port.            |  |  |  |  |  |

| C1 to C4        | Output port                                                                                 |  |  |  |  |  |

| 01 to 04        | Output port                                                                                 |  |  |  |  |  |

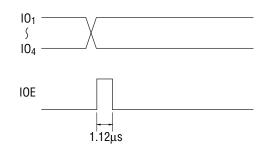

| 101 to 104      | Tri-state bidirectional port                                                                |  |  |  |  |  |

|                 | Output pin                                                                                  |  |  |  |  |  |

| IOE             | When IO1-IO4 is accessed, input completion signal (when read) or load signal (when written) |  |  |  |  |  |

|                 | is output from IOE pin.                                                                     |  |  |  |  |  |

# **ABSOLUTE MAXIMUM RATINGS**

V<sub>DD</sub>=0 V (V<sub>SS1</sub>=Battery Voltage)

| Parameter            | Symbol           | Condition | Rating                       | Unit |

|----------------------|------------------|-----------|------------------------------|------|

| Power Supply Voltage | V <sub>DD</sub>  |           | –0.3 to 6                    |      |

| Input Voltage        | VI               | Ta=25°C   | -0.3 to V <sub>DD</sub> +0.3 | V    |

| Output Voltage       | V <sub>0</sub>   | 1a=25 0   | -0.3 to V <sub>DD</sub> +0.3 |      |

| Power Dissipation    | PD               |           | 200 max.                     | mW   |

| Storage Temperature  | T <sub>STG</sub> | —         | -55                          | °C   |

# **RECOMMENDED OPERATING CONDITIONS**

V<sub>DD</sub>=0 V (V<sub>SS1</sub>=Battery Voltage)

| Parameter                | Symbol           | Condition                                | Range       | Unit |

|--------------------------|------------------|------------------------------------------|-------------|------|

| Operating Voltage        | V <sub>DD</sub>  | Pulse Mode<br>f <sub>OSC</sub> =3.58 MHz | 2.0 to 5.5* | V    |

| Memory Retention Voltage | V <sub>DDM</sub> | —                                        | 1.2 to 5.5  | V    |

| Operating Temperature    | T <sub>op</sub>  |                                          | -20 to +75  | °C   |

\* During the time that tone sending is stopped. During tone sending, 2.2 to 5.5 V.

# **ELECTRICAL CHARACTERISTICS**

# **DC Characteristics**

| Parameter                 | Symbol           | Conc                               | lition                 | Supply<br>Voltage | Min. | Тур. | Max. | Unit | Mea-<br>suring<br>Circui |

|---------------------------|------------------|------------------------------------|------------------------|-------------------|------|------|------|------|--------------------------|

| "H" Output Current (1)    | I <sub>OH1</sub> | 03, 04                             | V <sub>0H</sub> =2.6 V | 3.0 V             | -0.2 | _    | —    | mA   |                          |

| "L" Output Current (1)    | I <sub>OL1</sub> | DP OUT                             | V <sub>0L</sub> =0.4 V | 3.0 V             | 0.5  | _    | —    | mA   |                          |

| "H" Output Current (2)    | I <sub>OH2</sub> |                                    | V <sub>0H</sub> =2.6 V | 3.0 V             | -1.0 | _    | —    | mA   |                          |

| "L" Output Current (2)    | I <sub>OL2</sub> | $C_1$ to $C_4$                     | V <sub>0L</sub> =0.4 V | 3.0 V             | 10   | —    | —    | μA   |                          |

| "H" Output Current (3)    | I <sub>OH3</sub> | 0 <sub>1</sub> , 0 <sub>2</sub>    | V <sub>0H</sub> =2.6 V | 3.0 V             | -20  |      | —    | μA   | 1                        |

| "L" Output Current (3)    | I <sub>OL3</sub> | BD                                 | V <sub>0L</sub> =0.4 V | 3.0 V             | 10   | —    | —    | μA   |                          |

| "H" Output Current (4)    | I <sub>OH4</sub> | 10 <sub>1</sub> to 10 <sub>4</sub> | V <sub>0H</sub> =2.6 V | 3.0 V             | -150 | _    | _    | μA   |                          |

| "L" Output Current (4)    | I <sub>OL4</sub> | $EO_1$ to $EO_4$                   | V <sub>OL</sub> =0.4 V | 3.0 V             | 300  | _    | _    | μA   |                          |

| "H" Output Current (5)    | I <sub>OH5</sub> | - 32 kHz                           | V <sub>0H</sub> =2.6 V | 3.0 V             | -40  | —    | —    | μA   |                          |

| "L" Output Current (5)    | I <sub>OL5</sub> | JZ KIIZ                            | V <sub>0L</sub> =0.4 V | 3.0 V             | 25   | _    | —    | μA   |                          |

| "H" Input Voltage         | VIH              |                                    |                        | 3.0 V             | 2.2  | —    | —    | V    |                          |

| n input voltage           | VIH              |                                    |                        | 5.5 V             | 4.0  | —    | —    | v    | 2                        |

| 'L" Input Voltage         | V <sub>IL</sub>  | _                                  | _                      | 3.0 V             | _    |      | 0.8  | v    | 2                        |

| L input voltage           | ۷IL              |                                    | _                      | 5.5 V             | _    |      | 1.4  | v    |                          |

| 'H" Input Current (1)     | I <sub>IH1</sub> |                                    | V <sub>IH</sub> =5.5 V | 5.5 V             | _    | —    | 2    | μA   |                          |

| 'L" Input Current (1)     | I                | HS                                 | V <sub>IL</sub> =0 V   | 3.0 V             | -20  |      | -180 |      |                          |

|                           | l <sub>IL1</sub> |                                    | VIL=0 V                | 5.5 V             | -40  | —    | -360 | μA   |                          |

| 'H" Input Current (2)     | I <sub>IH2</sub> |                                    | V <sub>IH</sub> =5.5 V | 5.5 V             | 20   | —    | 180  |      |                          |

|                           | 1H2              | R <sub>1</sub> to R <sub>8</sub>   | V <sub>IH</sub> =3.0 V | 3.0 V             | 10   | —    | 90   | μA   |                          |

| 'L" Input Current (2)     | I <sub>IL2</sub> |                                    | V <sub>IL</sub> =0 V   | 5.5 V             | —    | —    | -2   | μA   | 3                        |

| Ul Input Ourrept (2)      | l                | l <sub>1</sub> to l <sub>4</sub>   | V <sub>IH</sub> =5.5 V | 5.5 V             | 60   | _    | 600  |      |                          |

| 'H" Input Current (3)     | I <sub>IH3</sub> | AC,                                | V <sub>IH</sub> =3.0 V | 3.0 V             | 30   | —    | 300  | μA   |                          |

| 'L" Input Current (3)     | I <sub>IL3</sub> | TEST                               | V <sub>IL</sub> =0 V   | 5.5 V             | —    | _    | -2   | μA   |                          |

| "H" Input Current (4)     | I <sub>IH4</sub> | 10 to 10                           | V <sub>IH</sub> =5.5 V | 5.5 V             | —    | _    | 2    | μA   |                          |

| "L" Input Current (4)     | I <sub>IL4</sub> | 10 <sub>1</sub> to 10 <sub>4</sub> | V <sub>IL</sub> =0 V   | 5.5 V             | —    | _    | -2   | μA   |                          |

| Oursent Consumption (1)   |                  | While tone sending is              |                        | 2.5 V             | —    | 0.25 | 0.5  |      |                          |

| Current Consumption (1)   | I <sub>DDP</sub> | stopped w                          | ith no load            | 5.0 V             |      | 1.5  | 2.4  | mA   |                          |

| Current Concurrentian (0) |                  | During ton                         | e sending,             | 2.5 V             | -    | 1.3  | 2.4  | m A  |                          |

| Current Consumption (2)   | I <sub>DDT</sub> | with n                             | o load                 | 5.0 V             | _    | 4.2  | 6.8  | mA   | 4                        |

| Current Consumption (3)   | I <sub>DDM</sub> | On hook,<br>With n                 |                        | 2.5 V             | -    | _    | 0.2  | μA   |                          |

## **AC Characteristics**

|                      |                   |                                              |                   |      |      | (Ta= | ≔20 to | o +75°C)                  |

|----------------------|-------------------|----------------------------------------------|-------------------|------|------|------|--------|---------------------------|

| Parameter            | Symbol            | Conditions                                   | Supply<br>Voltage | Min. | Тур. | Max. | Unit   | Mea-<br>suring<br>Circuit |

| Cycle Time           | t <sub>CY</sub>   | f=3.579545 MHz                               | 3.0 V             | —    | 17.9 | —    | μs     |                           |

|                      |                   | R <sub>ow</sub> side only                    | 2.2 V             | _    | 180  | _    | mV     |                           |

| Tone Output          | V <sub>OUT</sub>  | $R_{L}=1 k\Omega$                            | 4.0 V             | _    | 260  | —    |        |                           |

|                      |                   | nL=1 K22                                     | 5.5 V             |      | 330  | _    | rms    |                           |

| High/Low Loval Datio | dP                |                                              | 3.0 V             | 1    | 2    | 3    | dD     |                           |

| High/Low Level Ratio | dB <sub>CR</sub>  |                                              | 5.5 V             | 1    | 2    | 3    | dB     |                           |

| Distortion Datio     | 0/ d .            | P 1ko                                        | 3.0 V             | _    | —    | 5    | %      |                           |

| Distortion Ratio     | %d <sub>IS</sub>  | $R_L=1 k\Omega$                              | 5.5 V             | _    | —    | 5    | 70     |                           |

| Switch Input Time    | t <sub>KIN</sub>  | _                                            | _                 | 16   | —    | _    | ms     | 5                         |

| Diag/Fall Time (1)   | t <sub>TLH1</sub> | 03, 04, DP OUT                               | 3.0 V             | _    | —    | 0.5  |        |                           |

| Rise/Fall Time (1)   | t <sub>THL1</sub> | С <sub>L</sub> =50 рF                        | 3.0 V             | _    | —    | 0.5  | μs     |                           |

| Dies/Fall Time (2)   | t <sub>TLH2</sub> | C <sub>1</sub> to C <sub>4</sub>             | 3.0 V             | _    | —    | 0.5  |        |                           |

| Rise/Fall Time (2)   | t <sub>THL2</sub> | С <sub>L</sub> =50 рF                        | 3.0 V             | —    | —    | 10   | μs     |                           |

| Dice/Fell Time (2)   | t <sub>TLH3</sub> | 0 <sub>1</sub> , 0 <sub>2</sub> , BD, 32 kHz | 3.0 V             | _    | —    | 5    |        |                           |

| Rise/Fall Time (3)   | t <sub>THL3</sub> | С <sub>L</sub> =50 рF                        | 3.0 V             | _    | —    | 10   | μs     |                           |

|                      | t <sub>TLH4</sub> | 10 <sub>1</sub> to 10 <sub>4</sub> , 10E     | 3.0 V             | _    |      | 1    |        | ]                         |

| Rise/Fall Time (4)   |                   | EO1 to EO4,                                  |                   |      |      |      | μs     |                           |

|                      | t <sub>THL4</sub> | C <sub>L</sub> =50 pF                        | 3.0 V             |      |      | 1    |        |                           |

# **DTMF** Tone Output Frequency

|    | Reference Frequency (Hz) | Output Frequency (Hz) | Deviation (%) |

|----|--------------------------|-----------------------|---------------|

| R1 | 697                      | 699.1                 | +0.30         |

| R2 | 770                      | 766.2                 | -0.49         |

| R3 | 852                      | 847.4                 | -0.54         |

| R4 | 941                      | 948.0                 | +0.74         |

| C1 | 1209                     | 1215.9                | +0.57         |

| C2 | 1336                     | 1331.7                | -0.32         |

| C3 | 1477                     | 1471.9                | -0.35         |

f<sub>OSC</sub>=3.579545 MHz

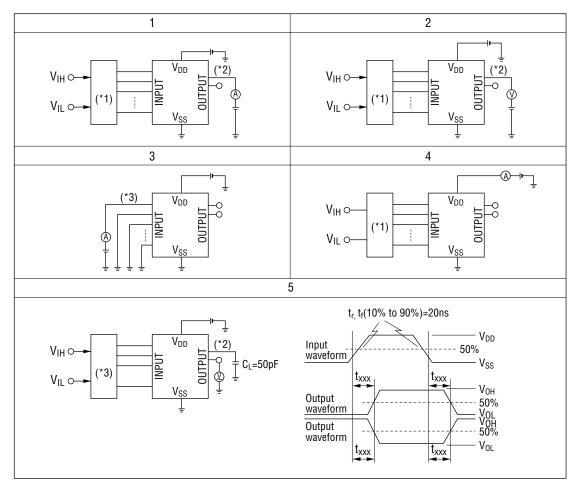

## **Measuring circuits**

- \*1 Input logic to select a specified state.

- \*2 To be repeated for the specified output pin.

- \*3 To be repeated for the specified input pin.

# FUNCTIONAL DESCRIPTION

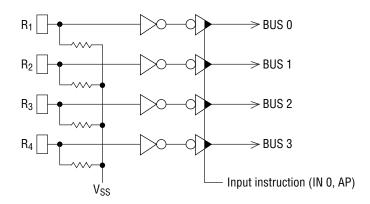

#### Input Port (R<sub>1</sub>-R<sub>4</sub>)

Input only port that consists of 4 bits ( $R_1$ ,  $R_2$ ,  $R_3$ ,  $R_4$ ). The port status is determined by the input instruction. Each input pin, which is pulled down to  $V_{SS}$  (low level) through a resistor, can be used as a keyboard input pin.

Figure 1. Input Port (R<sub>1</sub>-R<sub>4</sub>) Configuration

#### Input Port (R<sub>5</sub>-R<sub>8</sub>)

Input only port that consists of 4 bits (R<sub>5</sub>, R<sub>6</sub>, R<sub>7</sub>, R<sub>8</sub>). The port status is determined by the input instruction.

Figure 2. Input Port (R<sub>5</sub>-R<sub>8</sub>) Configuration

#### Input Port (I<sub>1</sub>-<sub>4</sub>)

Input only port that consists of 4 bits ( $I_1$ ,  $I_2$ ,  $I_3$ ,  $I_4$ ). The port status is determined by the input instruction. Each input pin is pulled down to  $V_{SS}$  (low level) through a transistor. The resistors are connected only when the port status is determined or a low level signal is input. Since the input current is limited, this port can be fixed at high level ( $V_{DD}$ ) for use.

Figure 3. Input port (I<sub>1</sub>-I<sub>4</sub>) Configuration

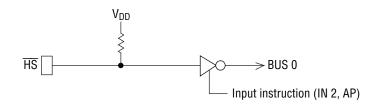

#### **HS** Input Pin

$\overline{\text{HS}}$  1-bit input pin, whose status can be fetched by the input instruction. It is pulled up to high level (V<sub>DD</sub>) by a resistor and used as a hook switch input pin.

Figure 4. Configuration of HS Input Pin

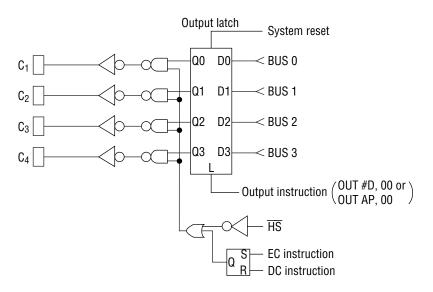

## Output Port (C<sub>1</sub>-C<sub>4</sub>)

Output only port that consists of 4 bits ( $C_1$ ,  $C_2$ ,  $C_3$ ,  $C_4$ ). The contents of the output latch can be rewritten by the output instruction.

A low level signal is output to each output pin at the time of the system reset.

When the HS input pin is open or at high level, a low level signal is output to each output pin irrespective of the contents of the output latch.

By setting this port to the enable state by the EC instruction, the contents of the output latch can be output to each output pin irrespective of the  $\overline{\text{HS}}$  input pin status. The port goes into the disable state (the output depends on the  $\overline{\text{HS}}$  input pin status) at the time of the system reset. C<sub>1</sub> to C<sub>4</sub> are CMOS outputs.

Figure 5. Output Port (C<sub>1</sub>-C<sub>4</sub>) Configuration

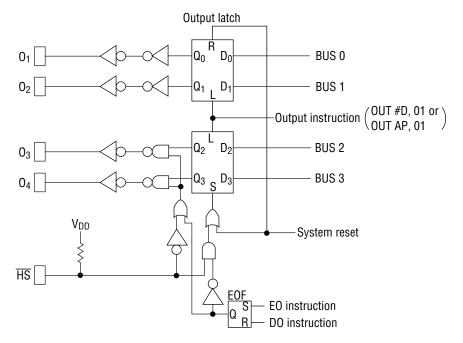

## Output Port (O<sub>1</sub>-O<sub>4</sub>)

Output only port that consists of 4 bits  $(O_1, O_2, O_3, O_4)$ . The contents of the output latch can be rewritten by the output instruction.

At the time of system reset, the output latch for  $O_1$  and  $O_2$  is reset and that of  $O_3$  and  $O_4$  is set. When the  $\overline{\text{HS}}$  input pin is open or at high level, a low level signal is output to the  $O_3$  and  $O_4$  output pins, allowing the contents of the output latch for  $O_3$  and  $O_4$  to be output to each output pin, if EOF, the selection flag for the on-hook dialing and off-hook dialing, is reset.

When EOF is set, the contents of the output latch for  $O_3$  and  $O_4$  can be rewritten irrespective of the HS input pin status.

$O_1$  to  $O_4$  are CMOS outputs.

Figure 6. Output Port (O<sub>1</sub>-O<sub>4</sub>) Configuration

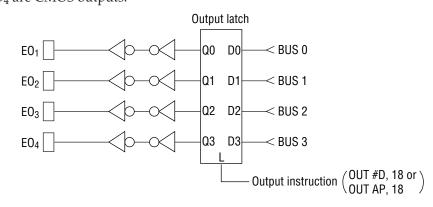

## Output Port (EO<sub>1</sub>-EO<sub>4</sub>)

Output only port that consists of 4 bits  $(EO_1, EO_2, EO_3, EO_4)$ . The contents of the output latch can be rewritten by the output instruction.

A low level signal is output to each output pin at the time of the system reset.  $EO_1$  to  $EO_4$  are CMOS outputs.

Figure 7. Output Port (EO<sub>1</sub>-EO<sub>4</sub>) Configuration

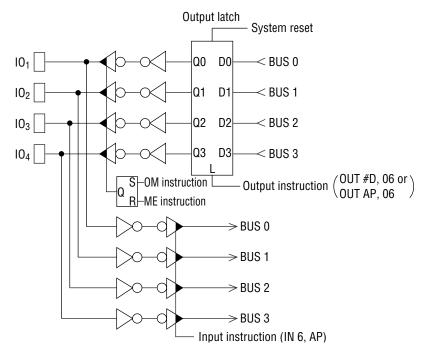

## Input/Output Port (IO1~IO4)

Input-output port that consists of 4 bits ( $IO_1$ ,  $IO_2$ ,  $IO_3$ ,  $IO_4$ ). The port status is determined and the output latch is rewritten by the input-output instruction.

This port goes into the output by the OM instruction and the input mode by the IM instruction. During the input mode, each pin is at a high impedance state irrespective of the contents of the output latch.

At the time of the system reset, this port enters output mode and a low level signal is output to each pin.

During the output mode, IO1 to IO4 are CMOS at outputs.

Figure 8. Input-Output Port (IO1~IO4) Configuration

#### **IOE Output Pin**

IOE is 1-bit output pin. A load signal is output at this pin when the output latch's (IO<sub>1</sub> to IO<sub>4</sub>) contents are rewritten.

IOE is CMOS output.

Figure 9. IOE Output Timing

## **DTMF Output Pin**

DTMF output pin to output DTMF signals. Start and stop of the DTMF output are done by the output instruction.

Figure 10. DTMF Output Pin Configuration

## **DP Output Pin**

Dial pulse output pin. Start and stop of the dial pulse output can be done by the output instruction.

When "1" is written to the output latch for  $O_3$  of output port ( $O_1$ ,  $O_2$ ,  $O_3$ ,  $O_4$ ), a low level signal is always output tot he DP OUT pin even if dial pulse output is started, if the EOF flag for the programmable timer is reset and the off-hook dial mode is selected.

When the EOF flag is set and the on-hook dial mode is selected, dial pulses can be output irrespective of the contents of the latch for  $O_3$ .

DP OUT is CMOS output.

Figure 11. DP Output Pin Configuration

#### **BD Output Pin**

BD output pin for the buzzer output. The buzzer output can be started and stopped by the output instruction. BD is CMOS output.

#### 32 kHz Output Pin

It is an output pin to output 31.960 kHz clock (duty: 50%) which is obtained by dividing the 3.579545 MHz system clock by 112. This clock outputs as long as the system clock is in oscillation.

32 kHz output pin is CMOS output.

## XT, XT Pins

These are input and output pins of the oscillator inverter, and the oscillator circuit is provided with the built in feed back resistor. By connecting to them oscillation of system clock status. 3.579545 MHz ceramic resonator and capacitors.

Figure 12. Oscillator Circuit

# AC input pin

Input pin for system reset. This pin is pulled down to  $V_{SS}$  (low level) through a resistor.

When a high level  $(V_{DD})$  signal is input to this pin, the system clock starts oscillation. If this pin is held at the high level for more than 1 machine cycle after the oscillation has gone into the stationary state, the internal state is reset. While a high level signal is applied to the AC pin, the execution of the instruction stored at address 0H is repeated. The system reset is released 0 to 17.9 microseconds after the AC pin is opened, and then the PC is incremented by 1.

Note that the following cannot be stored at address 0H: RDAR instruction, MVAR instruction, subroutine instructions, jump instructions, and branch instructions.

An AC input takes precedence over any other signal and has the following functions:

- Resets all the bits in the program counter to "0".

- Resets the output latch for the output port ( $C_1$ - $C_4$ ) to "0" and puts it into the disable (the output depends on the HS input pin status) state.

- Resets the output latch for  $O_1$  and  $O_2$  of the output port and sets the output latch for  $O_3$  and  $O_4$  to "1".

- Resets the output latch for the output port  $(EO_1-EO_4)$  to "0".

- Puts the input-output port  $(IO_1 IO_4)$  into output mode and resets the output latch.

- Resets the ETAF and TMF of the timer start circuit and realtime interrupt circuit to "0".

- Resets the 1/100 dividing circuit, PTC, IRQF, EIF, EOF and DPF of the programmable timer to "0".

- Resets the ETAF, TMF, and ACTF of the halt mode release control circuit and sets the HSTF to "1".

- Resets the HSF1, HSF2, and RF of the stop mode release control circuit to "0" and sets the HSTF to "1".

- Stops the watchdog timer.

- Resets the DTMF register of the DTMF output circuit to "0" and sets the HSTF to "1".

- Resets the BD register of the BD output circuit to "0".

- The contents of the accumulator (ACC), condition flags (Z, C, G), bank register (B), page register (P), address registers (AR<sub>1</sub>, AR<sub>2</sub>), loop counter (L), dividing circuit (DIV), and RAM are undefined.

## TEST input pin

Input pin for IC testing. This pin is pulled down to  $V_{SS}$  (low level) through a resistor and used to test the internal logic circuits of the IC during manufacturing process. Connect this pin to  $V_{SS}$ .

# PACKAGE DIMENSIONS

(Unit : mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage.

(Unit : mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage.

(Unit : mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage.

(Unit : mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage.