# **OKI Semiconductor**

| Oki, | Network Solutions    |

|------|----------------------|

|      | for a Global Society |

FEDL6650DIGEST-05 Issue Date: Jan. 11, 2002

# MSM6652/53/54/55/56-xxx, MSM6652A/53A/54A/55A/56A/58A-xxx, MSM66P54-xx, MSM66P56-xx, MSM6650

Internal Mask ROM Voice Synthesis IC, Internal One-Time-Programmable (OTP) ROM Voice Synthesis IC, External ROM Drive Voice Synthesis IC

This document contains minimum specifications. For full specifications, please contact your nearest Oki office or representative.

# **GENERAL DESCRIPTION**

The MSM6650 family is the successor to OKI's MSM6375 family. To ensure high-quality voice synthesis, the MSM6650 family members offer adaptive differential pulse-code modulation (ADPCM) playback, pulse-code modulation (PCM) playback, 12-bit D/A conversion, and on-chip –40 dB/octave low-pass filter (LPF).

The conventional "beep" tones and 2-channel playback are now easier to use. OKI has added additional functions such as melody play, fade-out, and random playback. OKI has improved external control by adding an Edit ROM. The Edit ROM can be used to form sentences by linking phrases.

The MSM6650 family members can support a variety of applications as it can function in either Standalone Mode or Microcontroller Interface Mode. In Microcontroller Interface Mode, serial input control is available. Serial input control minimizes the number of microcontroller port pins required for voice synthesis control. The MSM6650 family includes an internal mask ROM version, internal one-time-programmable (OTP) ROM version, and external ROM version. The features of the MSM6650 family devices are as follows.

• MSM6652/53/54/55/56-xxx

These devices are single-chip voice synthesizers with an on-chip mask ROM using the CMOS technology. Standalone Mode or Microcontroller Interface Mode can be selected by mask option.

• MSM6652A/53A/54A/55A/56A/58A-xxx The trial production period for these devices is shorter than those described above. These devices are suitable for developing prototype models and concept demonstration of new products.

• MSM66P54-xx, MSM66P56-xx

The device is a single-chip CMOS voice synthesizer with one-time-programmable (OTP) ROM.

Standalone and Microcontroller Interface Modes are selected by using a code (01-04).

The user can easily write voice data using the development tool AR761 or AR762, or P54 adapter. Unlike the mask ROM version, the OTP version is suited to applications which requires a small lot production of different type devices or short delivery time.

• MSM6650

The MSM6650 device can directly connect external ROM or EPROM of up to 64 Mbits, which stores voice data. This device is ideally suited to an evaluation IC for the MSM6650 family because its circuit configuration is identical to those of the mask ROM-based and OTP version devices.

#### **OKI Semiconductor**

#### MSM6650 Family

• Option Table

|                                                         | Pin Name | Microcontroller | interface Mode | Standalor    | ne Mode    | _  |

|---------------------------------------------------------|----------|-----------------|----------------|--------------|------------|----|

|                                                         | Pin Name | Serial Input    | Parallel Input | With Standby | No Standby | _  |

| MSM6652/53/54/55/56<br>MSM6652A/53A/54A/<br>55A/56A/58A | _        |                 | Mask C         | Option       |            | *1 |

| MSM66P54/P56                                            | —        | -01             | -02            | -03          | -04        | *2 |

|                                                         | CPU      | "H"             | "H"            | "L"          | "L"        | _  |

| MSM6650                                                 | SERIAL   | "H"             | "L"            | "上"          | "L"        |    |

|                                                         | STBY     |                 |                | "L"          | "H"        | _  |

\*1. The options for the mask ROM-based devices are mask options. The user should send OKI an

option list before starting development. A sample of option list is shown below. A code of OTP version device corresponds to one of the options. The user should specify either MSM66P54-03 or MSM66P54-04 or MSM66P56-03 or MSM66P56-04. (In this case, no option list \*2. is required.)

|                      |                         |                               |                          |               |                                                      | Date: |

|----------------------|-------------------------|-------------------------------|--------------------------|---------------|------------------------------------------------------|-------|

|                      |                         | (                             | Option Li                | st            |                                                      |       |

| You are              | requested to de         | velop MSM665X                 | -XXX or                  | the following | conditions.                                          |       |

| . Option<br>There ar | s                       | or the MSM6650                |                          |               |                                                      |       |

|                      | Option                  | Interface mod                 | e                        | Input         | Standby conversion                                   |       |

|                      | Option A                | Microcontrolle                | r                        | Serial        | —                                                    |       |

|                      | Option B                | Microcontrolle                | Microcontroller Parallel |               | _                                                    |       |

|                      | Option C                | Standalone                    |                          | _             | Yes                                                  |       |

|                      | Option D                | Standalone                    |                          | _             | No                                                   |       |

|                      |                         |                               |                          |               |                                                      |       |

| . Packag             |                         | Package<br>he desired one)    |                          | Quantity      | Note                                                 |       |

|                      | - · · ·                 |                               | chip                     | Quantity      | Note<br>Up to 10 samp<br>Operating tem<br>10 to 30°C |       |

| Item<br>Ceramic      | (circle t<br>18-pin DIP | he desired one)<br>24-pin SOP | chip                     |               | Up to 10 samp<br>Operating temp                      | D. :  |

#### **STANDALONE MODE**

# FEATURES

| Device name    | ROM size       | Maximum playback time (sec) |                            |                             |                           |  |

|----------------|----------------|-----------------------------|----------------------------|-----------------------------|---------------------------|--|

| Device name    | ROW SIZE       | $f_{SAM} = 4.0 \text{ kHz}$ | f <sub>SAM</sub> = 6.4 kHz | $f_{SAM} = 8.0 \text{ kHz}$ | f <sub>SAM</sub> = 16 kHz |  |

| MSM6652, 6652A | 288 Kbits      | 16.9                        | 10.5                       | 8.4                         | 4.2                       |  |

| MSM6653, 6653A | 544 Kbits      | 31.2                        | 19.5                       | 15.6                        | 7.8                       |  |

| MSM6654, 6654A | 1 Mbit         | 63.8                        | 39.9                       | 31.9                        | 15.9                      |  |

| MSM6655, 6655A | 1.5 Mbits      | 96.5                        | 60.3                       | 48.2                        | 24.1                      |  |

| MSM6656, 6656A | 2 Mbits        | 129.1                       | 80.7                       | 64.5                        | 32.2                      |  |

| MSM6658A       | 4 Mbits        | 259.7                       | 162.9                      | 129.8                       | 64.9                      |  |

| MSM66P54       | 1 Mbit         | 63.8                        | 39.9                       | 31.9                        | 15.9                      |  |

| MSM66P56       | 2 Mbit         | 129.1                       | 80.7                       | 64.5                        | 32.2                      |  |

| MSM6650        | 64 Mbits (Max) | 4194.3                      | 2620.5                     | 2096.4                      | 1048.2                    |  |

Note: Actual voice ROM area is smaller by 22 Kbits.

- 4-bit ADPCM or 8-bit PCM sound generation

- Melody function

- Edit ROM function

- Two-channel mixing function

- Built-in random playback function

- Fade-out function via four-step sound volume attenuation

- Built-in beep tone of 0.5 kHz, 1.0 kHz, 1.3 kHz, or 2.0 kHz selectable with a specific code

- Sampling frequency of 4.0 kHz, 5.3 kHz, 6.4 kHz, 8.0 kHz, 10.6 kHz, 12.8 kHz, 16.0 kHz, or 32.0 kHz (32 kHz sampling is not possible when using RC oscillation)

- Up to 120 phrases

- Built-in 12-bit D/A converter

- Built-in -40 dB/octave low-pass filter

- Standby function

- Selectable RC or ceramic oscillation

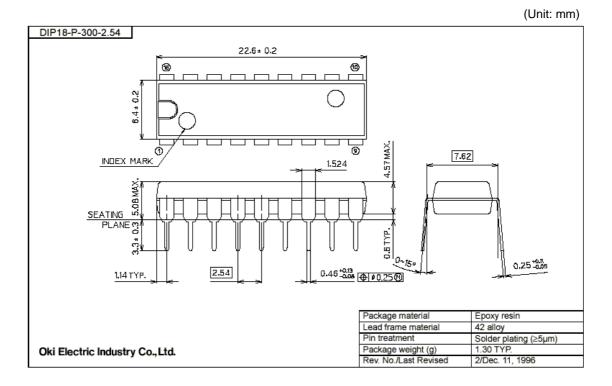

- Package options:

| 18-pin plastic DIP (DIP18-P-300-2.54) (Product name:    | MSM6652-xxxRS/MSM6653-xxxRS/       |

|---------------------------------------------------------|------------------------------------|

|                                                         | MSM6654-xxxRS/MSM6655-xxxRS/       |

|                                                         | MSM6656-xxxRS/MSM6652A-xxxRS/      |

|                                                         | MSM6653A-xxxRS/MSM6654A-xxxRS/     |

|                                                         | MSM6655A-xxxRS/MSM6656A-xxxRS/     |

|                                                         | MSM6658A-xxxRS)                    |

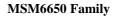

| 24-pin plastic SOP (SOP24-P-430-1.27-K) (Product name:  | MSM6652-xxxGS-K/MSM6653-xxxGS-K/   |

|                                                         | MSM6654-xxxGS-K/MSM6655-xxxGS-K/   |

|                                                         | MSM6656-xxxGS-K/MSM6652A-xxxGS-K/  |

|                                                         | MSM6653A-xxxGS-K/MSM6654A-xxxGS-K/ |

|                                                         | MSM6655A-xxxGS-K/MSM6656A-xxxGS-K/ |

|                                                         | MSM6658A-xxxGS-K/MSM66P54-03GS-K/  |

|                                                         | MSM66P54-04GS-K/MSM66P56-03GS-K/   |

|                                                         | MSM66P56-04GS-K)                   |

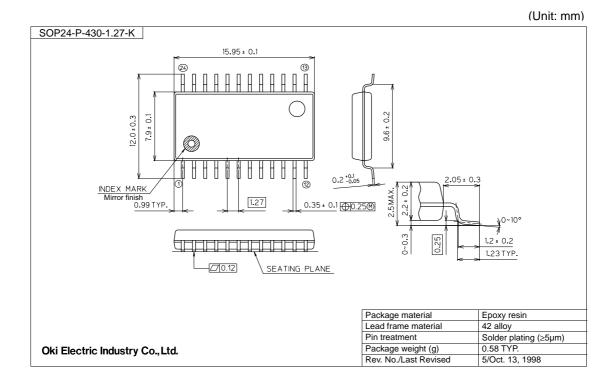

| 20-pin plastic DIP (DIP20-P-300-2.54-W1) (Product name: | MSM66P54-03RS/MSM66P54-04RS/       |

|                                                         | MSM66P56-03RS/MSM66P56-04RS)       |

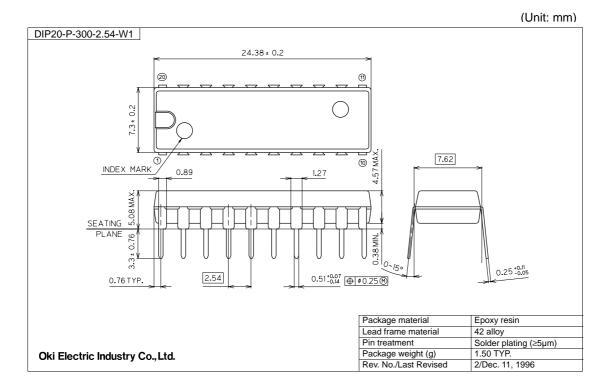

| 64-pin plastic QFP (QFP64-P-1420-1.00-BK) (Product name | e: MSM6650GS-BK)                   |

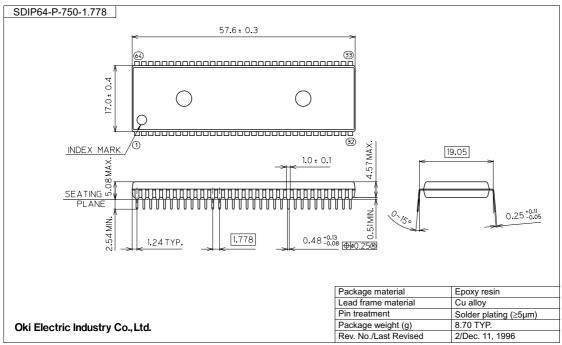

| 64-pin plastic SDIP (SDIP64-P-750-1.778) (Product name: | MSM6650SS)                         |

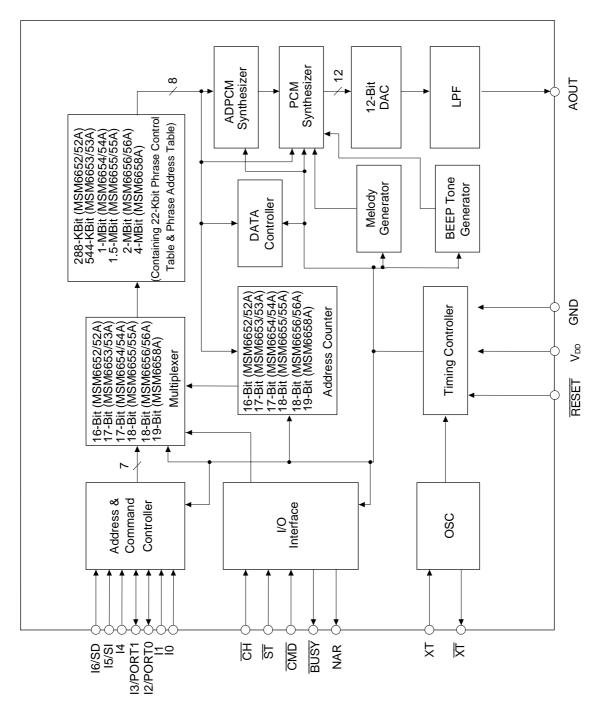

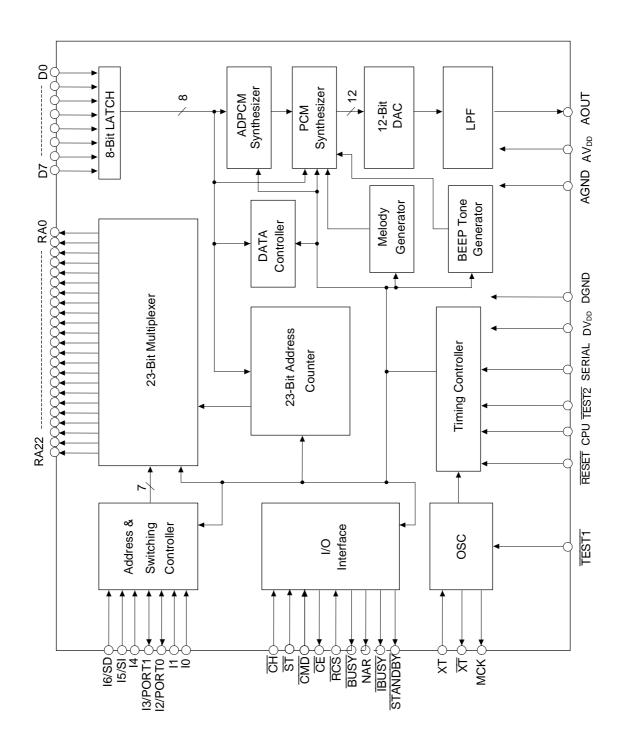

#### **BLOCK DIAGRAMS**

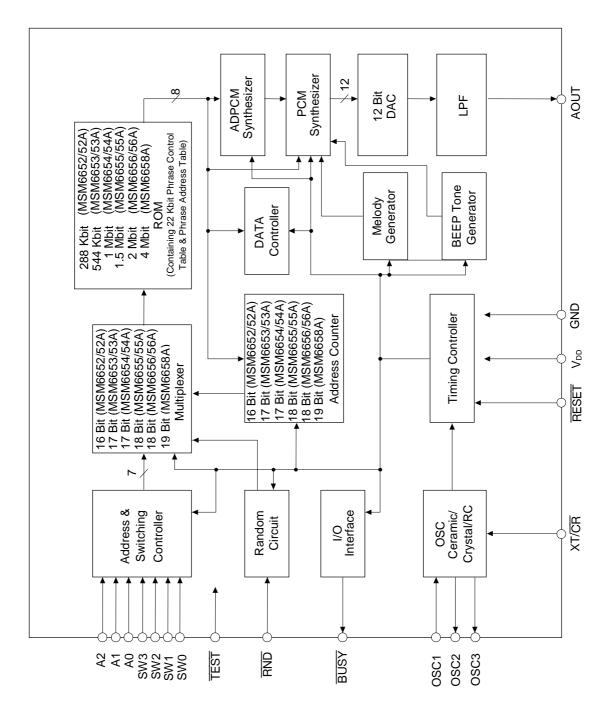

#### MSM6652/53/54/55/56-xxx MSM6652A/53A/54A/55A/56A/58A-xxx

# FEDL6650DIGEST-05

#### **OKI** Semiconductor

# MSM6650 Family

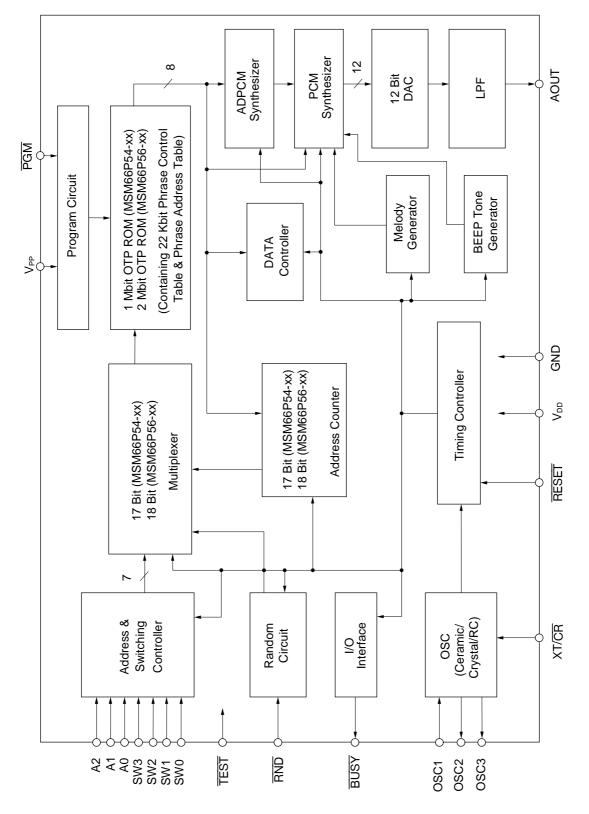

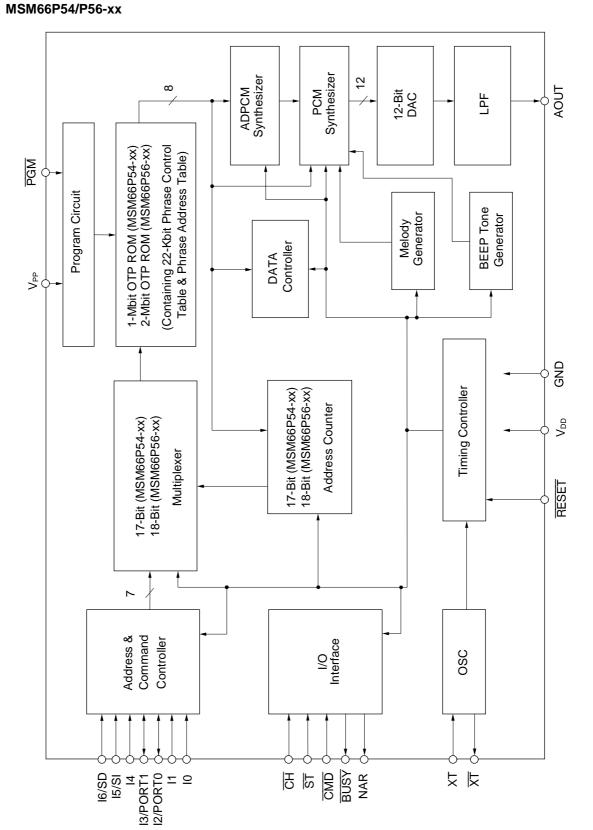

# MSM66P54/P56-xx

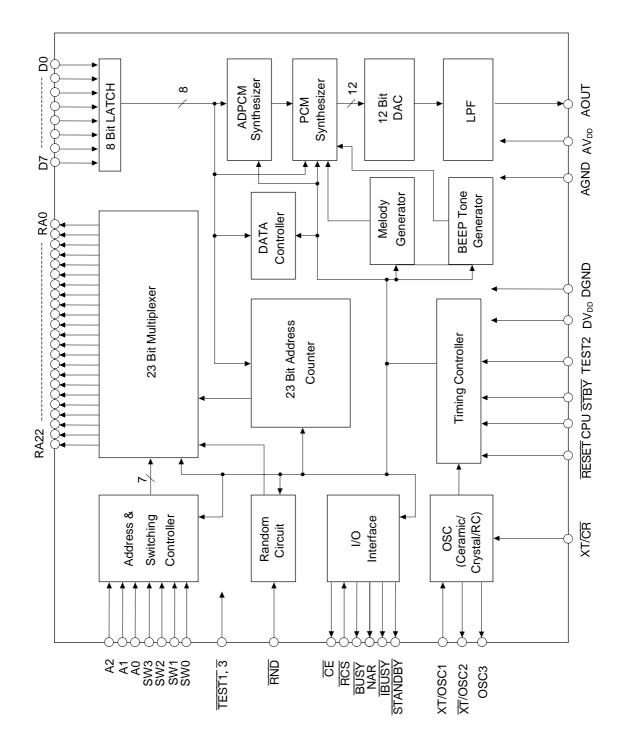

# MSM6650

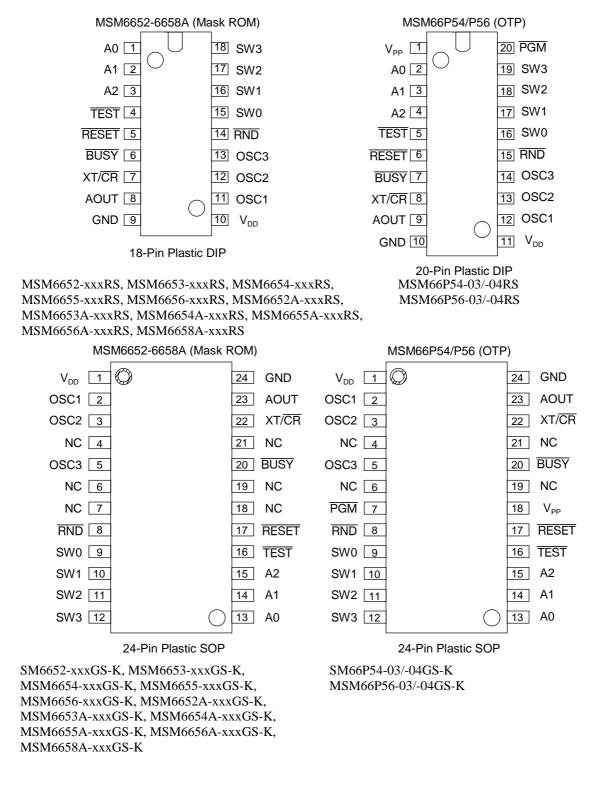

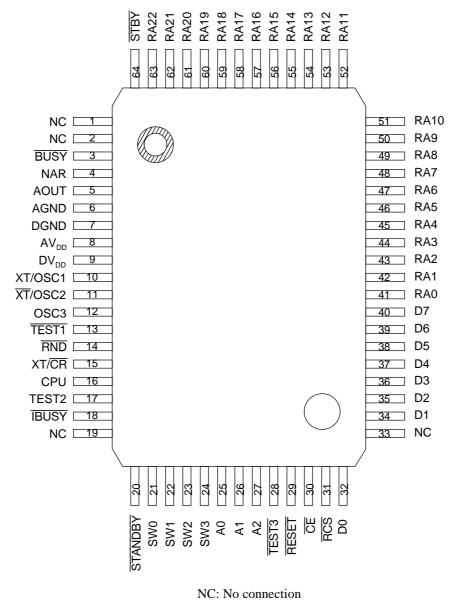

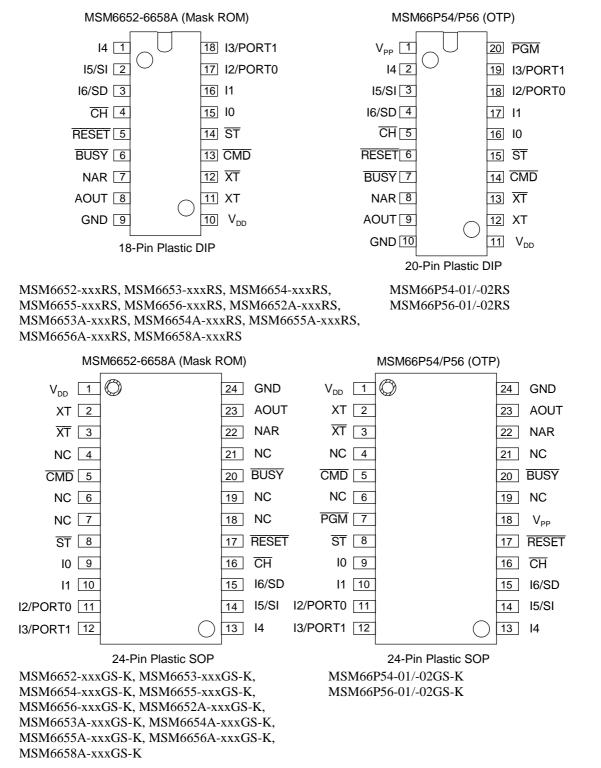

#### **PIN CONFIGURATION (TOP VIEW)**

The MSM66P54-xx and MSM66P56-xx has two more pins than the MSM6652-6658A while their pin configurations are identical.

The additional two pins ( $V_{PP}$ ,  $\overline{PGM}$ ) of the MSM66P54-xx/P56-xx may be open at playback after completion of writing.

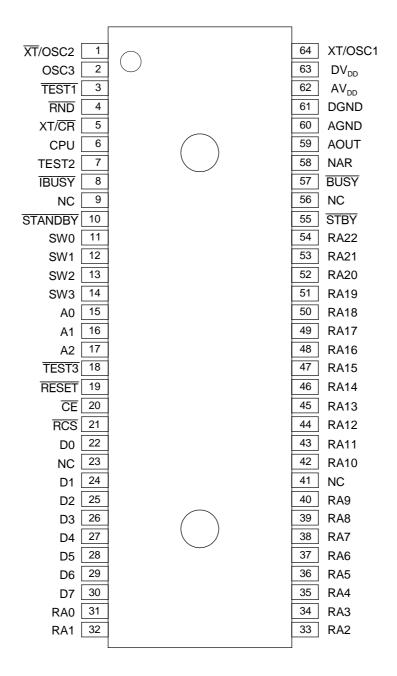

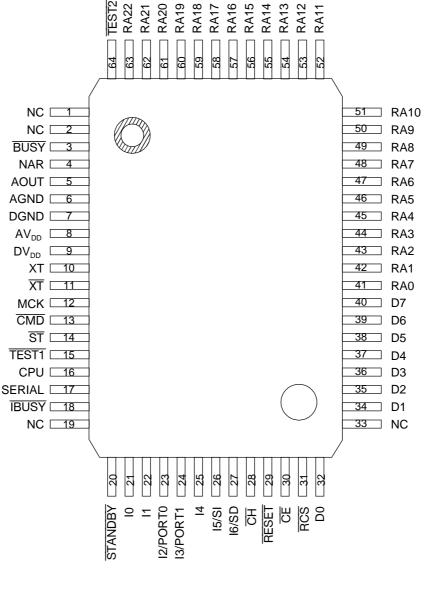

#### **MSM6650**

Product name: MSM6650GS-BK

**64-Pin Plastic QFP**

#### **OKI** Semiconductor

MSM6650 Family

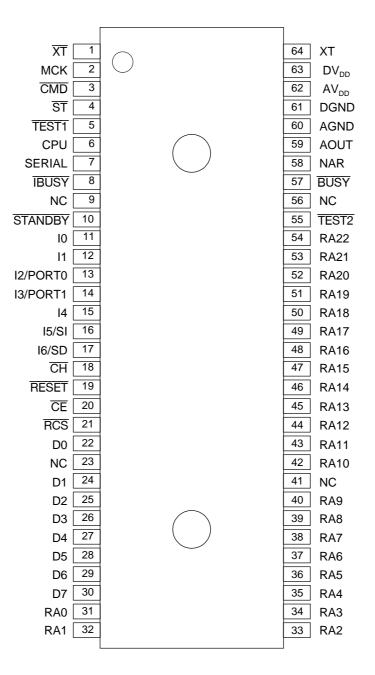

Product name: MSM6650SS

NC: No connection

**64-Pin Plastic SDIP**

# **PIN DESCRIPTIONS**

#### 1. MSM6652/53/54/55/56-xxx, MSM6652A/53A/54A/55A/56A/58A-xxx 18-Pin plastic DIP

| Pin   | Symbol          | Туре | Description                                                                                                                                                                                                                                                                                                              |

|-------|-----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5     | RESET           | I    | Reset. Setting this pin to "L" puts the LSI In standby status. At this time, oscillation stops, AOUT is pulled to GND, and the deveice is initialized. This pin has an internal pull-up resistor.                                                                                                                        |

| 6     | BUSY            | 0    | Busy. This pin outputs a "L" level during playback. At power-on, this pin Is at "H" level.                                                                                                                                                                                                                               |

| 7     | XT/CR           | Ι    | $XT/\overline{CR}$ selectable pin. Set to "H" level when using ceramic oscillation. Set to "L" level when using RC oscillation.                                                                                                                                                                                          |

| 8     | AOUT            | 0    | Sound Output. This is the synthesized output pin of the internal low-pass filter.                                                                                                                                                                                                                                        |

| 11    | OSC1            | I    | Oscillator 1. This pin is a ceramic oscillator connection pin when using ceramic oscillation. This pin is an RC connection pin when using RC oscillation. When using an external clock, use this pin as the clock input.                                                                                                 |

| 12    | OSC2            | ο    | Oscillator 2. This pin is a ceramic oscillator connection pin when using a ceramic oscillator. This is an RC connection pin when using RC oscillation. Leave open if using an external clock. OSC2 outputs a "L" level in standby status.                                                                                |

| 13    | OSC3            | 0    | Oscillator 3. Leave open if using a ceramic oscillator. This pin is the RC connection pin when using RC oscillation. When RC oscillation is selected, OSC3 outputs a "H" level in standby status.                                                                                                                        |

| 14    | RND             | I    | Random Playback. Random playback starts when the $\overline{\text{RND}}$ pin is set to a "L" level. At the fall of $\overline{\text{RND}}$ , addresses from the random address playback circuit inside the IC are fetched. Set to a "H" level if random playback is not used. This pin has an Internal pull-up resistor. |

| 15-18 | SW0-SW3         | Ι    | Phrase Inputs. These pins are phrase input pins corresponding to playback. If the Input changes, SW0 to SW3 pins capture address data after 16 ms and speech playback commences. These pins have internal pull-down resistors.                                                                                           |

| 1-3   | A0-A2           | Ι    | Phrase Inputs. Phrase input pins correspoding to playback. The A0 input becomes invalid when the random playback function is used.                                                                                                                                                                                       |

| 9     | GND             |      | Ground.                                                                                                                                                                                                                                                                                                                  |

| 10    | V <sub>DD</sub> | _    | Power supply. Insert a 0.1 $\mu F$ or more bypass capacitor between this pin and GND.                                                                                                                                                                                                                                    |

| 4     | TEST            | Ι    | Test Mode. Set to "H" level. This pin has an Internal pull-up resistor                                                                                                                                                                                                                                                   |

# 2. MSM66P54-xx, MSM66P56-xx 20-Pin plastic DIP

| Pin   | Symbol          | Туре | Description                                                                                                                                                                                                                                                                     |

|-------|-----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6     | RESET           | I    | Reset. Setting this pin to "L" puts the LSI in standby status. At this time, oscillation stops, AOUT is pulled to GND, and the deveice is initialized. This pin has an internal pull-up resistor.                                                                               |

| 7     | BUSY            | 0    | Busy. This pin outputs a "L" level during playback. At power-on, this pin Is at "H" level.                                                                                                                                                                                      |

| 8     | XT/CR           | Ι    | $XT/\overline{CR}$ selectable pin. Set to "H" level when using ceramic oscillation. Set to "L" level when using RC oscillation.                                                                                                                                                 |

| 9     | AOUT            | 0    | Sound Output. This is the synthesized output pin of the internal low-pass filter.                                                                                                                                                                                               |

| 12    | OSC1            | Ι    | Oscillator 1. This pin is a ceramic oscillator connection pin when using ceramic oscillation. This pin is an RC connection pin when using RC oscillation. When using an external clock, use this pin as the clock input.                                                        |

| 13    | OSC2            | ο    | Oscillator 2. This pin Is a ceramic oscillator connection pin when using a ceramic oscillator. This is an RC connection pin when using RC oscillation. Leave open if using an external clock. OSC2 outputs a "L" level in standby status.                                       |

| 14    | OSC3            | 0    | Oscillator 3. Leave open if using a ceramic oscillator. This pin is the RC connection pin when using RC oscillation. When RC oscillation is selected, OSC3 outputs a "H" level In standby status.                                                                               |

| 15    | RND             | I    | Random Playback. Random playback starts when the RND pin is set to a "L" level. At the fall of RND, addresses from the random address playback circuit inside the IC are fetched. Set to a "H" level if random playback is not used. This pin has an Internal pull-up resistor. |

| 16-19 | SW0-SW3         | I    | Phrase Inputs. These pins are phrase Input pins corresponding to playback. If the Input changes, SW0 to SW3 pins capture address data after 16 ms and speech playback commences. These pins have internal pull-down resistors.                                                  |

| 2-4   | A0-A2           | I    | Phrase Inputs. Phrase input pins correspoding to playback. The A0 input becomes invalid when the random playback function is used.                                                                                                                                              |

| 10    | GND             | —    | Ground.                                                                                                                                                                                                                                                                         |

| 11    | V <sub>DD</sub> | _    | Power supply. Insert a 0.1 $\mu F$ or more bypass capacitor between this pin and GND.                                                                                                                                                                                           |

| 5     | TEST            | I    | Test Mode. Set to "H" level. This pin has an Internal pull-up resistor.                                                                                                                                                                                                         |

| 1     | V <sub>PP</sub> |      | Power supply used when writing data to Internal OTP ROM. Leave open or set to "H" level during playback.                                                                                                                                                                        |

| 20    | PGM             | Ι    | Interface with voice analysis edit tool AR203 or AR204. Set to "L" level or leave open during playback.                                                                                                                                                                         |

#### FEDL6650DIGEST-05

#### **OKI** Semiconductor

# MSM6650 Family

# 3. MSM6652/53/54/55/56-xxx, MSM6652A/53A/54A/55A/56A/58A-xxx, MSM66P54-xx, MSM66P56-xx 24-Pin plastic SOP

| Pin   | Symbol            | Туре | Description                                                                                                                                                                                                                                                                     |

|-------|-------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17    | RESET             | I    | Reset. Setting this pin to "L" puts the LSI in standby status. At this time, oscillation stops, AOUT is pulled to GND, and the deveice is initialized. This pin has an internal pull-up resistor.                                                                               |

| 20    | BUSY              | 0    | Busy. This pin outputs a "L" level during playback. At power-on, this pin Is at "H" level.                                                                                                                                                                                      |

| 22    | XT/CR             | I    | XT/CR selectable pin. Set to "H" level when using ceramic oscillation. Set to "L" level when using RC oscillation.                                                                                                                                                              |

| 23    | AOUT              | 0    | Sound Output. This is the synthesized output pin of the internal low-pass filter.                                                                                                                                                                                               |

| 2     | OSC1              | I    | Oscillator 1. This pin is a ceramic oscillator connection pin when using ceramic oscillation. This pin is an RC connection pin when using RC oscillation. When using an external clock, use this pin as the clock input.                                                        |

| 3     | OSC2              | 0    | Oscillator 2. This pin Is a ceramic oscillator connection pin when using a ceramic oscillator. This is an RC connection pin when using RC oscillation. Leave open if using an external clock. OSC2 outputs a "L" level in standby status.                                       |

| 5     | OSC3              | 0    | Oscillator 3. Leave open if using a ceramic oscillator. This pin is the RC connection pin when using RC oscillation. When RC oscillation is selected, OSC3 outputs a "H" level In standby status.                                                                               |

| 8     | RND               | I    | Random Playback. Random playback starts when the RND pin is set to a "L" level. At the fall of RND, addresses from the random address playback circuit inside the IC are fetched. Set to a "H" level if random playback is not used. This pin has an Internal pull-up resistor. |

| 9-12  | SW0-SW3           | I    | Phrase Inputs. These pins are phrase Input pins corresponding to playback. If the Input changes, SW0 to SW3 pins capture address data after 16 ms and speech playback commences. These pins have internal pull-down resistors.                                                  |

| 13-15 | A0-A2             | I    | Phrase Inputs. Phrase input pins correspoding to playback. The A0 input becomes invalid when the random playback function is used.                                                                                                                                              |

| 24    | GND               | —    | Ground.                                                                                                                                                                                                                                                                         |

| 1     | V <sub>DD</sub>   | _    | Power supply. Insert a 0.1 $\mu F$ or more bypass capacitor between this pin and GND.                                                                                                                                                                                           |

| 16    | TEST              | Ι    | Test Mode. Set to "H" level. This pin has an Internal pull-up resistor.                                                                                                                                                                                                         |

| 18    | V <sub>PP</sub> * | _    | Power supply used when writing data to Internal OTP ROM. Leave pen or set to "H" level during playback.                                                                                                                                                                         |

| 7     | PGM*              | Ι    | Interface with voice analysis edit tool AR203 or AR204. Set to "L" level or leave open during playback.                                                                                                                                                                         |

\* Pins for MSM66P54/56-xx only

#### **OKI** Semiconductor

#### Pin Symbol Туре Description Reset. Setting this pin to "L" puts the LSI in standby status. At this time, 29 (19) RESET I oscillation stops, AOUT is pulled to GND, and the deveice is initialized. This pin has an internal pull-up resistor. Busy. This pin outputs a "L" level during playback. At power-on, this pin Is at 3 (57) BUSY 0 "H" level. XT/CR selectable pin. Set to "H" level when using ceramic oscillation. Set to "L" 15 (5) XT/CR L level when using RC oscillation. 5 (59) AOUT 0 Sound Output. This is the synthesized output pin of the internal low-pass filter. Oscillator 1. This pin is a ceramic oscillator connection pin when using ceramic I 10 (64) XT/OSC1 oscillation. This pin is an RC connection pin when using RC oscillation. When using an external clock, use this pin as the clock input. Oscillator 2. This pin Is a ceramic oscillator connection pin when using a ceramic oscillator. This is an RC connection pin when using RC oscillation. 0 11 (1) **XT**/OSC2 Leave open if using an external clock. OSC2 outputs a "L" level in standby status. Oscillator 3. Leave open if using a ceramic oscillator. This pin is the RC 0 12 (2) OSC3 connection pin when using RC oscillation. When RC oscillation is selected, OSC3 outputs a "H" level In standby status. Random Playback. Random playback starts when the RND pin is set to a "L" level. At the fall of RND, addresses from the random address playback circuit RND 14 (4) I inside the IC are fetched. Set to a "H" level if random playback is not used. This pin has an Internal pull-up resistor. Phrase Inputs. These pins are phrase Input pins corresponding to playback. If 21-24 SW0-SW3 I the input changes, SW0 to SW3 pins capture address data after 16 ms and (11-14)speech playback commences. These pins have internal pull-down resistors. 25-27 Phrase Inputs. Phrase input pins correspoding to playback. The A0 input A0-A2 I (15-17)becomes invalid when the random playback function is used.

#### 4. MSM6650 64-Pin plastic QFP (64-Pin plastic SDIP)

#### FEDL6650DIGEST-05

#### **OKI** Semiconductor

# MSM6650 Family

| Pin                         | Symbol    | Туре | Description                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------|-----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6 (60)                      | AGND      |      | Analog ground pin.                                                                                                                                                                                                                                                                                                                                      |

| 7 (61)                      | DGND      |      | Digital ground pin.                                                                                                                                                                                                                                                                                                                                     |

| 8 (62)                      | $AV_{DD}$ | _    | Analog power pin. Insert a 0.1 $\mu F$ or more bypass capacitor in between this pin and AGND.                                                                                                                                                                                                                                                           |

| 9 (63)                      | $DV_{DD}$ | _    | Digital power pin. Insert a 0.1 $\mu F$ or more bypass capacitor in between this pin and DGND.                                                                                                                                                                                                                                                          |

| 16 (6)                      | CPU       | I    | CPU Mode. Set to "L" level to select Standalone Mode. Set to "H" level to select Microcontroller Interface Mode.                                                                                                                                                                                                                                        |

| 13, 28<br>(3, 18)           | TEST1, 3  | I    | Test. Set these pins to "H" level. The TEST1 and TEST3 pins have internal pull-up resistor.                                                                                                                                                                                                                                                             |

| 17 (7)                      | TEST2     | I    | Test Set this pin to "L" level.                                                                                                                                                                                                                                                                                                                         |

| 18 (8)                      | IBUSY     | 0    | I Busy. Outputs a "L" level during voice playback (except during standby conversion time), or when the AOUT pin is at half $V_{DD}$ level.                                                                                                                                                                                                              |

| 20 (10)                     | STANDBY   | 0    | Standby indicator. This output pin remains at "L" level during oscillation.                                                                                                                                                                                                                                                                             |

| 30 (20)                     | CE        | 0    | Chip Enable. $\overline{CE}$ is a timing output pin to control read of external memory. This pin outputs when $\overline{RCS}$ is at the "L" level. This pin outputs "H" level when $\overline{RCS}$ is at the "H" level.                                                                                                                               |

| 31 (21)                     | RCS       | I    | Read Chip Select. The data bits D0-D7 are internally pulled down when $\overline{\text{RCS}}$ is high. Addresses and $\overline{\text{CE}}$ are output when $\overline{\text{RCS}}$ is at "L" level. The RA22-RA0 address pins become high impedance and $\overline{\text{CE}}$ pin outputs "H" level when $\overline{\text{RCS}}$ is at the "H" level. |

| 32 34-40<br>(22, 24-<br>30) | D0-D7     | I    | External Memory Data Bus. Data Is input when $\overline{\text{RCS}}$ Is low When $\overline{\text{RCS}}$ is high, these pins become low due to Internal pull-down resistors.                                                                                                                                                                            |

| 41-63<br>(31-40,<br>42-54)  | RA0-RA22  | 0    | External Memory Address. These are address pins for an external memory output when $\overline{\text{RCS}}$ is low. These pins become high impedance status If $\overline{\text{RCS}}$ is in "H" level.                                                                                                                                                  |

| 64 (55)                     | STBY      | I    | Standby Contorl. If set to "L" level, the MSM6650 enters standby mode 0.2 seconds after voice ends. If set to "H" level, the MSM6650 AOUT output maintains half $V_{\text{DD}}$ after voice ends.                                                                                                                                                       |

# ABSOLUTE MAXIMUM RATINGS

| (GND  | = | 0 | V)  |

|-------|---|---|-----|

| (0.10 |   | - | • / |

| Parameter            | Symbol           | Condition | Rating                        | Unit |

|----------------------|------------------|-----------|-------------------------------|------|

| Power supply voltage | V <sub>DD</sub>  | Ta = 25°C | -0.3 to +7.0                  | V    |

| Input voltage        | V <sub>IN</sub>  | Ta = 25 C | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Storage temperature  | T <sub>STG</sub> | _         | –55 to +150                   | °C   |

# **RECOMMENDED OPERATING CONDITIONS**

|                          |                   |                                         |            |            | (    | (GND = 0 V) |

|--------------------------|-------------------|-----------------------------------------|------------|------------|------|-------------|

| Parameter                | Symbol            | Condition                               |            | Range      |      |             |

| Power supply voltage     | V <sub>DD</sub>   | MSM6652-56,<br>MSM6650,<br>MSM6652A-56A |            | 2.4 to 5.5 |      | V           |

|                          | V <sub>DD</sub>   | MSM6658A,<br>MSM66P54/P56               | 3.5 to 5.5 |            |      | V           |

| Operating temperature    | T <sub>OP</sub>   | —                                       | -40 to +85 |            | °C   |             |

| Maatan alaak franssaan ( | 4                 | \//honomustal aslastad                  | Min.       | Тур.       | Max. | N 41 1-     |

| Master clock frequency 1 | f <sub>OSC1</sub> | When crystal selected                   | 3.5        | 4.096      | 4.5  | MHz         |

| Master clock frequency 2 | f <sub>OSC2</sub> | When RC selected (*)                    | 200        | 256        | 300  | kHz         |

\* If RC oscillation is selected, 32 kHz sampling frequency cannot be selected.

# **ELECTRICAL CHARACTERISTICS**

## **DC Characteristics**

|                             |                  |                                              | $(V_{DD} = 5.0)$ | ) V, GND = ( | ) V, Ta = −40 | ) to +85°C) |

|-----------------------------|------------------|----------------------------------------------|------------------|--------------|---------------|-------------|

| Parameter                   | Symbol           | Condition                                    | Min.             | Тур.         | Max.          | Unit        |

| "H" input voltage           | V <sub>IH</sub>  | —                                            | 4.2              |              | _             | V           |

| "L" input voltage           | VIL              | —                                            |                  |              | 0.8           | V           |

| "H" output voltage          | V <sub>OH</sub>  | I <sub>OH</sub> = -1 mA                      | 4.6              |              | _             | V           |

| "L" output voltage          | V <sub>OL</sub>  | I <sub>OL</sub> = 2 mA                       |                  |              | 0.4           | V           |

| "H" input current 1         | I <sub>IH1</sub> | $V_{IH} = V_{DD}$                            |                  |              | 10            | μA          |

| "H" input current 2         | I <sub>IH2</sub> | Internal pull-down resistance                | 30               | 90           | 200           | μA          |

| "L" input current 1         | I <sub>IL1</sub> | V <sub>IL</sub> = GND                        | -10              |              | _             | μA          |

| "L" input current 2 (note)  | I <sub>IL2</sub> | Internal pull-up<br>resistance               | -200             | -90          | -30           | μΑ          |

| Operating power consumption | I <sub>DD</sub>  | _                                            | _                | 6            | 10            | mA          |

| Standby power               |                  | $Ta = -40^{\circ}C \text{ to } +50^{\circ}C$ | _                |              | 10            | μA          |

| consumption                 | I <sub>DS</sub>  | Ta = -40°C to +85°C                          | _                | _            | 30            | μΑ          |

# **DC Characteristics**

|                             |                   |                                              | (V <sub>DD</sub> = 3.1 | 1 V, GND = 0 | O V, Ta = −40 | ) to +85°C) |

|-----------------------------|-------------------|----------------------------------------------|------------------------|--------------|---------------|-------------|

| Parameter                   | Symbol            | Condition                                    | Min.                   | Тур.         | Max.          | Unit        |

| "H" input voltage           | V <sub>IH</sub>   | —                                            | 2.7                    | _            | _             | V           |

| "L" input voltage           | V <sub>IL</sub>   | —                                            | _                      |              | 0.5           | V           |

| "H" output voltage          | V <sub>OH</sub>   | I <sub>он</sub> = –1 mA                      | 2.6                    |              | _             | V           |

| "L" output voltage          | V <sub>OL</sub>   | l <sub>oL</sub> = 2 mA                       |                        |              | 0.4           | V           |

| "H" input current 1         | I <sub>IH1</sub>  | $V_{IH} = V_{DD}$                            |                        |              | 10            | μΑ          |

| "H" input current 2         | I <sub>IH2</sub>  | Internal pull-down resistance                | 10                     | 30           | 100           | μΑ          |

| "L" input current 1         | I <sub>IL1</sub>  | $V_{IL} = GND$                               | -10                    |              | —             | μΑ          |

| "L" input current 2         | I <sub>IL2</sub>  | Internal pull-up<br>resistance               | -100                   | -30          | -10           | μA          |

| Operating power consumption | I <sub>DD</sub>   | _                                            | _                      | 4            | 7             | mA          |

| Standby power               |                   | $Ta = -40^{\circ}C \text{ to } +50^{\circ}C$ |                        |              | 5             | μΑ          |

| consumption                 | I <sub>DS</sub>   | Ta = -40°C to +85°C                          | _                      |              | 20            | μΑ          |

| LPF driving resistance      | R <sub>AOUT</sub> | When LPF output is<br>selected               | 50                     | _            | _             | kΩ          |

| LPF output impedance        | $R_{LPF}$         | I <sub>F</sub> = 100 μA                      | _                      | 1            | 3             | kΩ          |

# **APPLICATION CIRCUITS**

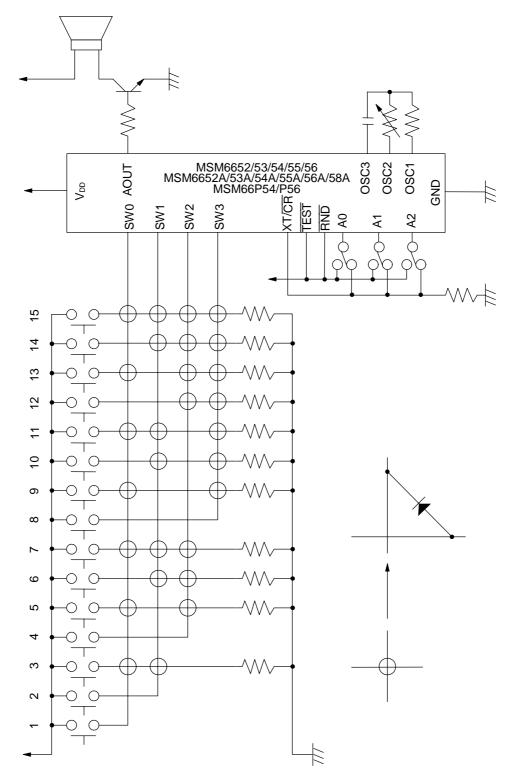

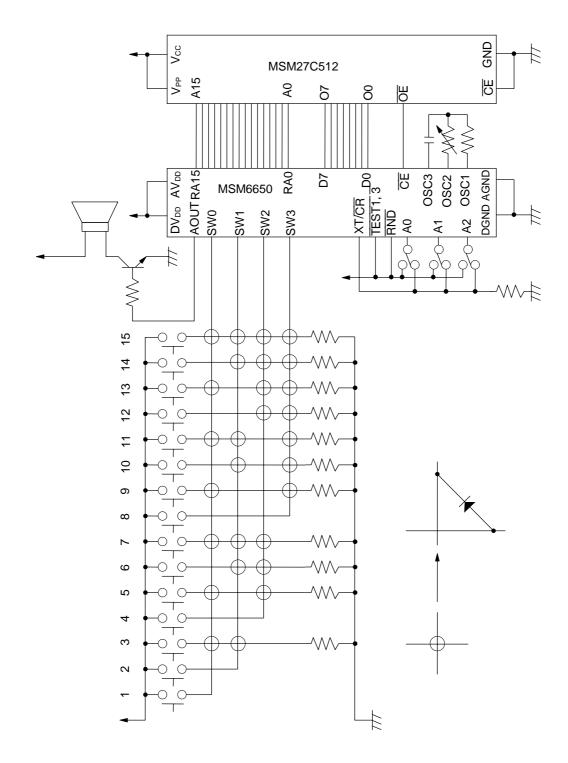

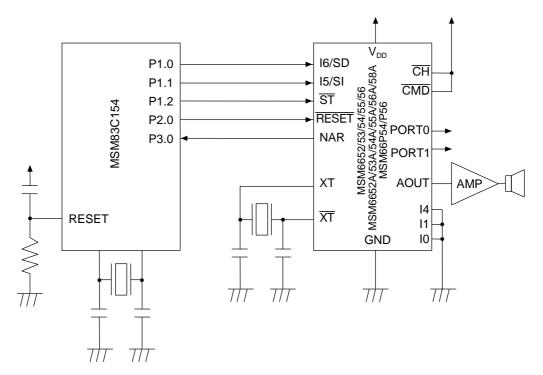

(MSM6652/53/54/55/56-xxx, MSM6652A/53A/54A/55A/56A/58A-xxx, MSM66P54/P56-xx)

Application Circuit in Standalone Mode Supporting 15 Switch-Selected Phrases

### **OKI** Semiconductor

#### MSM6650 Family

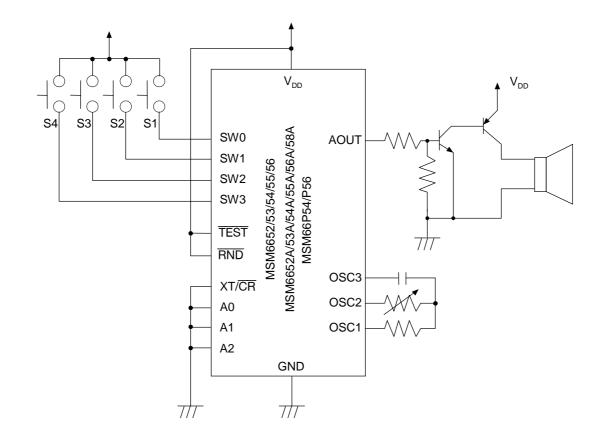

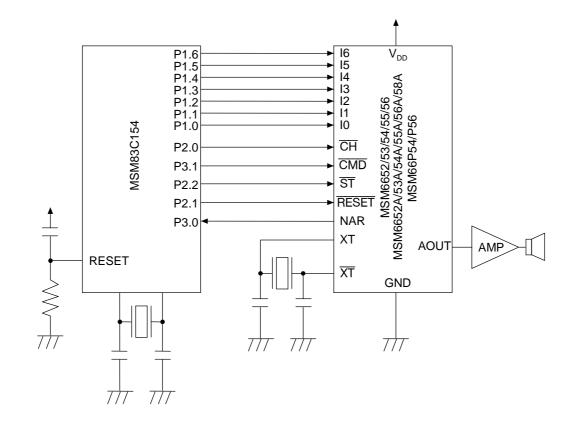

(MSM6652/53/54/55/56-xxx, MSM6652A/53A/54A/55A/56A/58A-xxx, MSM66P54/P56-xx)

# Application Circuit in Standalone Mode Supporting Four Switch-Selected Words

|    | A2 | A1 | A0 | SW3 | SW2 | SW1 | SW0 | ADR |

|----|----|----|----|-----|-----|-----|-----|-----|

| S1 | 0  | 0  | 0  | 0   | 0   | 0   | 1   | 01  |

| S2 | 0  | 0  | 0  | 0   | 0   | 1   | 0   | 02  |

| S3 | 0  | 0  | 0  | 0   | 1   | 0   | 0   | 04  |

| S4 | 0  | 0  | 0  | 1   | 0   | 0   | 0   | 08  |

## **Switches and Playback Addresses**

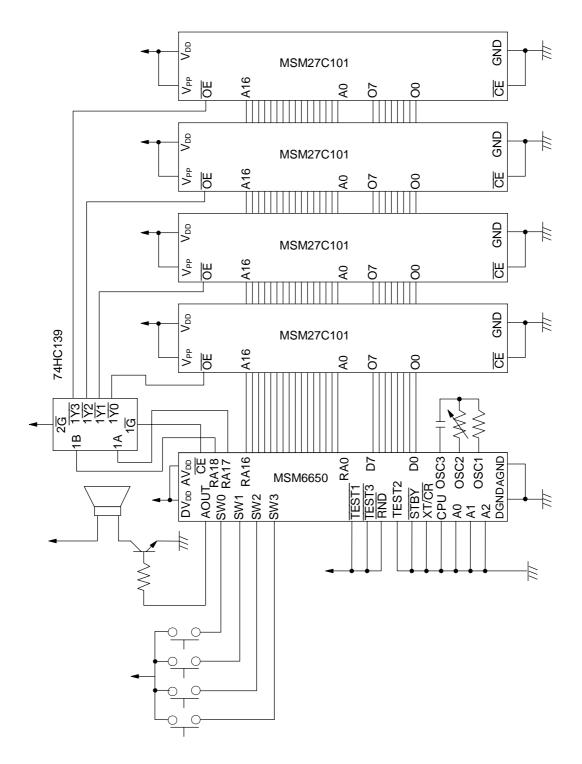

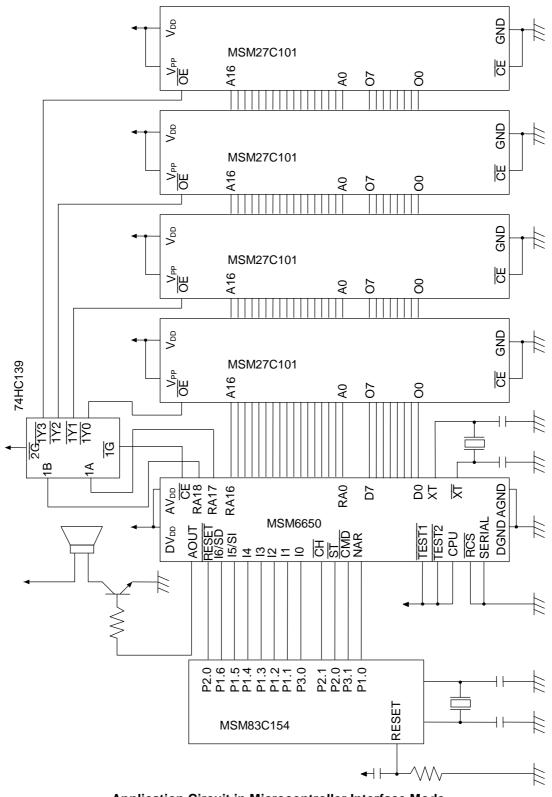

(MSM6650)

Application Circuit in Standalone Mode Supporting 15 Switch-Selected Phrases

## (MSM6650)

Application Circuit in Standalone Mode Supporting Four 1 Mbit EPROMs

# MICROCONTROLLER INTERFACE MODE

# FEATURES

|                | DATA ROM       | Maximum playback time (sec)   |                               |                               |                              |                              |  |  |

|----------------|----------------|-------------------------------|-------------------------------|-------------------------------|------------------------------|------------------------------|--|--|

| Device name    | size           | f <sub>SAM</sub> = 4.0<br>kHz | f <sub>SAM</sub> = 6.4<br>kHz | f <sub>SAM</sub> = 8.0<br>kHz | f <sub>SAM</sub> = 16<br>kHz | f <sub>sam</sub> = 32<br>kHz |  |  |

| MSM6652, 6652A | 288 Kbits      | 16.9                          | 10.5                          | 8.4                           | 4.2                          | 2.1                          |  |  |

| MSM6653, 6653A | 544 Kbits      | 31.2                          | 19.5                          | 15.6                          | 7.8                          | 3.9                          |  |  |

| MSM6654, 6654A | 1 Mbit         | 63.8                          | 39.9                          | 31.9                          | 15.9                         | 7.9                          |  |  |

| MSM6655, 6655A | 1.5 Mbits      | 96.5                          | 60.3                          | 48.2                          | 24.1                         | 12.0                         |  |  |

| MSM6656, 6656A | 2 Mbits        | 129.1                         | 80.7                          | 64.5                          | 32.2                         | 16.1                         |  |  |

| MSM6658A       | 4 Mbits        | 259.7                         | 162.9                         | 129.8                         | 64.9                         | 32.4                         |  |  |

| MSM66P54       | 1 Mbit         | 63.8                          | 39.9                          | 31.9                          | 15.9                         | 7.9                          |  |  |

| MSM66P56       | 2 Mbit         | 129.1                         | 80.7                          | 64.5                          | 32.2                         | 16.1                         |  |  |

| MSM6650        | 64 Mbits (Max) | 4194.3                        | 2620.5                        | 2096.4                        | 1048.2                       | 524.1                        |  |  |

Note: Actual voice ROM area is smaller by 22 Kbits.

- 4-bit ADPCM or 8-bit PCM sound generation

- Melody function

- Edit ROM function

- Two-channel mixing function

- Fade-out function via four-step sound volume attenuation

- Serial input or parallel input selectable

- Built-in beep tone of 0.5 kHz, 1.0 kHz, 1.3 kHz, or 2.0 kHz selectable with a specific code

- Sampling frequency of 4.0 kHz, 5.3 kHz, 6.4 kHz, 8.0 kHz, 10.6 kHz, 12.8 kHz, 16.0 kHz, or 32.0 kHz (32 kHz sampling is not possible when using RC oscillation)

- Up to 127 phrases

- Built-in 12-bit D/A converter

- Built-in -40 dB/octave low-pass filter

- Standby function

- Package options:

| MSM6652-xxxRS/MSM6653-xxxRS/       |

|------------------------------------|

| MSM6654-xxxRS/MSM6655-xxxRS/       |

| MSM6656-xxxRS/MSM6652A-xxxRS/      |

| MSM6653A-xxxRS/MSM6654A-xxxRS/     |

| MSM6655A-xxxRS/MSM6656A-xxxRS/     |

| MSM6658A-xxxRS)                    |

| MSM6652-xxxGS-K/MSM6653-xxxGS-K/   |

| MSM6654-xxxGS-K/MSM6655-xxxGS-K/   |

| MSM6656-xxxGS-K/MSM6652A-xxxGS-K/  |

| MSM6653A-xxxGS-K/MSM6654A-xxxGS-K/ |

| MSM6655A-xxxGS-K/MSM6656A-xxxGS-K/ |

| MSM6658A-xxxGS-K/MSM66P54-01GS-K/  |

| MSM66P54-02GS-K/MSM66P56-01GS-K/   |

| MSM66P56-02GS-K)                   |

| MSM66P54-01RS/MSM66P54-02RS/       |

| MSM66P56-01RS/MSM66P56-02RS)       |

| e:MSM6650GS-BK)                    |

| MSM6650SS)                         |

|                                    |

#### **BLOCK DIAGRAMS**

#### MSM6652/53/54/55/56-xxx MSM6652A/53A/54A/55A/56A/58A-xxx

# OKI Semiconductor

#### FEDL6650DIGEST-05

MSM6650 Family

# MSM6650

#### **PIN CONFIGURATION (TOP VIEW)**

The MSM66P54/P56-xx has two more pins than the MSM6652-6658A while their pin configurations are identical. The additional two pins ( $V_{PP}$ ,  $\overline{PGM}$ ) of the MSM66P54/P56-xx may be open at playback after completion of writing.

#### MSM6650

Product name: MSM6650GS-BK

NC: No connection

**64-Pin Plastic QFP**

#### **OKI** Semiconductor

#### MSM6650 Family

Product name: MSM6650SS

NC: No connection

**64-Pin Plastic SDIP**

# **PIN DESCRIPTIONS**

#### 1. MSM6652/53/54/55/56-xxx, MSM6652A/53A/54A/55A/56A/58A-xxx 18-Pin plastic DIP

| Pin    | Symbol          | Туре | Description                                                                                                                                                                                                                                                                      |

|--------|-----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5      | RESET           | I    | Reset. The devices enter stanby status when a low level is input to this pin.<br>When RESET, oscillation stops The AOUT output goes to ground and the IC<br>status is reinitialzed. This pin has an internal pull-up resistor.                                                   |

| 6      | BUSY            | 0    | Busy. Outputs a "L" level during playback and a "H" level when power is turned ON.                                                                                                                                                                                               |

| 7      | NAR             | 0    | The CMD and ST inputs become effective when high. NAR indicates whether the address bus (10 through 16) is ready to accept another address. When high, it is ready to accept. NAR goes high when power is turned ON.                                                             |

| 8      | AOUT            | 0    | Analog Speech Output. D/A converter output or LPF output is selected by entering the command.                                                                                                                                                                                    |

| 11     | ХТ              | Ι    | Ceramic Oscillator Input. This pin has an internal 0.5 to 5 M $\Omega$ feedback resistor between XT and $\overline{\text{XT}}$ . If an external clock is used, this is the clock input pin.                                                                                      |

| 12     | XT              | 0    | Ceramic Oscillator Output. If an external clock is used, leave this pin open.                                                                                                                                                                                                    |

| 13     | CMD             | I    | Command Input and Option Control. This pin is used as command and option input when CMD is at the high level with $\overline{ST}$ low. If this pin is not used or serial input is optioned, set this pin to "H" level This pin has an Internal pull up resistor.                 |

| 14     | ST              | Ι    | Start. Speech playback starts at the fall of the $\overline{ST}$ pulse. The 10-16 addresses are latched at the rise of the $\overline{ST}$ pulse. Input a $\overline{ST}$ pulse when NAR goes to the high level for channels 1 and 2. This pin has an internal pull-up resistor. |

| 4      | CH              | Ι    | Channel Control. Channel 1 is selected when the input Is pulled high. Channel 2 is selected when the Input is low. This pin has an internal pull-up resistor.                                                                                                                    |

| 3      | I6/SD           | I    | This pin is command and user-defined phrase input when parallel input is optioned. This pin is serial data (command and address) input when serial input is optioned.                                                                                                            |

| 2      | 15/SI           | I    | This pin is command and user-defined phrase input when parallel input is optioned. This pin is used as serial clock input when serial input is optioned.                                                                                                                         |

| 1      | 14              | Ι    | This pin is command and user-defined phrase input when parallel input is optioned. When serial input is optioned, set this pin to "L" level. This pin has an internal pull-down resistor.                                                                                        |

| 18     | I3/PORT1        | I/O  | This pin is command and user-defined phrase input when parallel input is optioned. When serial input is optioned, this pin is a port output. The port output is controlled by entering external silence insertion code.                                                          |

| 17     | I2/PORT0        | I/O  | This pin is command and user-defined phrase input when parallel input is optioned. When serial input is optioned, this pin is a port output. The port output is controlled by entering external silence insertion code.                                                          |

| 15, 16 | 10, 11          | I    | This pin is command and user-defined phrase input when parallel input is optioned. When serial input is optioned, set this pin to "L" level. This pin has an internal pull-down resistor.                                                                                        |

| 9      | GND             | _    | Ground pin.                                                                                                                                                                                                                                                                      |

| 10     | V <sub>DD</sub> |      | Power supply. Insert a 0.1 $\mu F$ ro more bypass capacitor between this pin and GND.                                                                                                                                                                                            |

# 2. MSM66P54/P56-xx 20-Pin plastic DIP

| Pin    | Symbol          | Туре | Description                                                                                                                                                                                                                                                                      |

|--------|-----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6      | RESET           | I    | Reset. The devices enter stanby status when a low level is input to this pin.<br>When RESET, oscillation stops. The AOUT output goes to ground and the IC<br>status is reinitialized This pin has an internal pull-up resistor.                                                  |

| 7      | BUSY            | ο    | Busy. Outputs a "L" level during playback and a "H" level when power is turned ON.                                                                                                                                                                                               |

| 8      | NAR             | 0    | The CMD and ST inputs become effective when high. NAR indicates whether<br>the address bus (10 through 16) is ready to accept another address. When<br>high, it is ready to accept. NAR goes high when power is turned ON.                                                       |

| 9      | AOUT            | 0    | Analog Speech Output. D/A converter output or LPF output is selected by entering the command.                                                                                                                                                                                    |

| 12     | ХТ              | Ι    | Ceramic Oscillator Input. This pin has an internal 0.5 to 5 M $\Omega$ feedback resistor between XT and $\overline{XT}$ . If an external clock is used, this is the clock input pin.                                                                                             |

| 13     | TX              | 0    | Ceramic Oscillator Output. If an external clock is used, leave this pin open.                                                                                                                                                                                                    |

| 14     | CMD             | I    | Command Input and Option Control. This pin is used as command and option input when CMD is at the high level with $\overline{ST}$ low. If this pin is not used or serial input is optioned, set this pin to "H" level. This pin has an internal pull-up resistor.                |

| 15     | डा              | I    | Start. Speech playback starts at the fall of the $\overline{ST}$ pulse. The 10-16 addresses are latched at the rise of the $\overline{ST}$ pulse. Input a $\overline{ST}$ pulse when NAR goes to the high level for channels 1 and 2. This pin has an internal pull-up resistor. |

| 5      | CH              | I    | Channel Control. Channel 1 is selected when the input is pulled high. Channel 2 is selected when the input is low. This pin has an internal pull-up resistor.                                                                                                                    |

| 4      | I6/SD           | I    | This pin is command and user-defined phrase input when parallel input is optioned. This pin is serial data (command and address) input when serial input is optioned.                                                                                                            |

| 3      | 15/SI           | I    | This pin is command and user-defined phrase input when parallel input is optioned. This pin is used as serial clock input when serial input is optioned.                                                                                                                         |

| 2      | 14              | I    | This pin is command and user-defined phrase input when parallel input is optioned. When serial input is optioned, set this pin to "L" level. This pin has an internal pull-down resistor.                                                                                        |

| 19     | I3/PORT1        | I/O  | This pin is command and user-defined phrase input when parallel input is optioned. When serial input is optioned, this pin is a port output. The port output is controlled by entering external silence insertion code.                                                          |

| 18     | I2/PORT0        | I/O  | This pin is command and user-defined phrase input when parallel input is optioned. When serial input is optioned, this pin is a port output. The port output is controlled by entering external silence insertion code.                                                          |

| 16, 17 | 10, 11          | I    | This pin is command and user-defined phrase input when parallel input is optioned. When serial input is optioned, set this pin to "L" level. This pin has an internal pull-down resistor.                                                                                        |

| 10     | GND             |      | Ground pin.                                                                                                                                                                                                                                                                      |

| 11     | V <sub>DD</sub> | _    | Power supply. Insert a 0.1 $\mu\text{F}$ ro more bypass capacitor between this pin and GND.                                                                                                                                                                                      |

| 1      | V <sub>PP</sub> |      | Supply voltage for writing data to internal OTP ROM.                                                                                                                                                                                                                             |

| 20     | PGM             | I    | Interface with voice analysis edit tools AR203 and AR204. Set to "L" level or leave open during playback. This pin has an internal pull-down resistor.                                                                                                                           |

#### **OKI** Semiconductor

# 3. MSM6652/53/54/55/56-xxx, MSM6652A/53A/54A/55A/56A/58A-xxx, MSM66P54/P56-xx 24-Pin plastic SOP

| Pin | Symbol   | Туре | Description                                                                                                                                                                                                                                                                      |

|-----|----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17  | RESET    | Ι    | Reset. The devices enter stanby status when a low level is input to this pin.<br>When RESET, oscillation stops. The AOUT output goes to ground and the IC<br>status is reinitialized This pin has an internal pull-up resistor.                                                  |

| 20  | BUSY     | 0    | Busy. Outputs a "L" level during playback and a "H" level when power is turned ON.                                                                                                                                                                                               |

| 22  | NAR      | 0    | The CMD and ST inputs become effective when high. NAR indicates whether<br>the address bus (10 through 16) is ready to accept another address. When<br>high, it is ready to accept. NAR goes high when power is turned ON.                                                       |

| 23  | AOUT     | 0    | Analog Speech Output. D/A converter output or LPF output is selected by entering the command.                                                                                                                                                                                    |

| 2   | ХТ       | I    | Ceramic Oscillator Input. This pin has an internal 0.5 to 5 M $\Omega$ feedback resistor between XT and $\overline{XT}$ . If an external clock is used, this is the clock input pin.                                                                                             |

| 3   | T        | 0    | Ceramic Oscillator Output. If an external clock is used, leave this pin open.                                                                                                                                                                                                    |

| 5   | CMD      | I    | Command Input and Option Control. This pin is used as command and option input when CMD is at the high level with $\overline{ST}$ low. If this pin is not used or serial input is optioned, set this pin to "H" level. This pin has an internal pull-up resistor.                |

| 8   | ST       | I    | Start. Speech playback starts at the fall of the $\overline{ST}$ pulse. The 10-16 addresses are latched at the rise of the $\overline{ST}$ pulse. Input a $\overline{ST}$ pulse when NAR goes to the high level for channels 1 and 2. This pin has an internal pull-up resistor. |

| 16  | CH       | I    | Channel Control. Channel 1 is selected when the input is pulled high. Channel 2 is selected when the input is low. This pin has an internal pull-up resistor.                                                                                                                    |

| 15  | I6/SD    | I    | This pin is command and user-defined phrase input when parallel input is optioned. This pin is serial data (command and address) input when serial input is optioned.                                                                                                            |

| 14  | 15/SI    | I    | This pin is command and user-defined phrase input when parallel input is optioned. This pin is used as serial clock input when serial input is optioned.                                                                                                                         |

| 13  | 14       | I    | This pin is command and user-defined phrase input when parallel input is optioned. When serial input is optioned, set this pin to "L" level. This pin has an internal pull-down resistor.                                                                                        |

| 12  | I3/PORT1 | I/O  | This pin is command and user-defined phrase input when parallel input is optioned. When serial input is optioned, this pin is a port output. The port output is controlled by entering external silence insertion code.                                                          |

| 11  | I2/PORT0 | I/O  | This pin is command and user-defined phrase input when parallel input is optioned. When serial input is optioned, this pin is a port output. The port output is controlled by entering external silence insertion code.                                                          |

#### FEDL6650DIGEST-05

## **OKI** Semiconductor

# MSM6650 Family

| Pin   | Symbol            | Туре | Description                                                                                                                                                                               |

|-------|-------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9, 10 | 10, 11            | I    | This pin is command and user-defined phrase input when parallel input is optioned. When serial input is optioned, set this pin to "L" level. This pin has an internal pull-down resistor. |

| 24    | GND               | —    | Ground pin.                                                                                                                                                                               |

| 1     | V <sub>DD</sub>   | _    | Power supply. Insert a 0.1 $\mu F$ ro more bypass capacitor between this pin and GND.                                                                                                     |

| 18    | V <sub>PP</sub> * | —    | Supply voltage for writing data to internal OTP ROM.                                                                                                                                      |

| 7     | PGM *             | I    | Interface with voice analysis edit tools AR761 and AR762. Set to "L" level or leave open during playback. This pin has an internal pull-down resistor.                                    |

\* Pins for MSM66P54/56-xx only

#### **OKI** Semiconductor

#### Pin Symbol Туре Description Reset. The devices enter stanby status when a low level is input to this pin. 29 (19) RESET I When RESET, oscillation stops The AOUT output goes to ground and the IC status is reinitialized. This pin has an internal pull-up resistor. Busy. Outputs a "L" level during playback and a "H" level when power is turned 3 (57) BUSY 0 ON. The CMD and ST Inputs become effective when high. NAR indicates whether 0 4 (58) NAR the address bus (10 through 16) is ready to accept another address. When high, it is ready to accept. NAR goes high when power is turned ON. Analog Speech Output. D/A converter output or LPF output is selected by AOUT 0 5 (59) entering the command. Ceramic Oscillator Input. This pin has an internal 0.5 to 5 M $\Omega$ feedback resistor 10 (64) XT I between XT and $\overline{XT}$ . If an external clock is used, this is the clock input pin. ΧT 11 (1) 0 Ceramic Oscillator Output. If an external clock is used, leave this pin open. Command Input and Option Control. This pin is used as command and option input when CMD is at the high level with ST low. If this pin is not used or serial 13 (3) CMD L input is optioned, set this pin to "H" level This pin has an Internal pull up resistor. Start. Speech playback starts at the fall of the $\overline{ST}$ pulse. The 10-16 addresses ST 14 (4) L are latched at the rise of the ST pulse. Input a ST pulse when NAR goes to the high level for channels 1 and 2. This pin has an internal pull-up resistor. Channel Control. Channel 1 is selected when the input Is pulled high. Channel CH I 28 (18) 2 is selected when the Input is low. This pin has an internal pull-up resistor. This pin is command and user-defined phrase input when parallel input is 27 (17) 16/SD I optioned. This pin is serial data (command and address) input when serial input is optioned. This pin is command and user-defined phrase input when parallel input is I 15/SI 26 (16) optioned. This pin is used as serial clock input when serial input is optioned. This pin is command and user-defined phrase input when parallel input is 25 (15) 14 L optioned. When serial input is optioned, set this pin to "L" level. This pin has an internal pull-down resistor. This pin is command and user-defined phrase input when parallel input is 24 (14) I3/PORT1 I/O optioned. When serial input is optioned, this pin is a port output. The port output is controlled by entering external silence insertion code. This pin is command and user-defined phrase input when parallel input is I2/PORT0 I/O 23 (13) optioned. When serial input is optioned, this pin is a port output. The port output is controlled by entering external silence insertion code. This pin is command and user-defined phrase input when parallel input is 21, 22 10.11 L optioned. When serial input is optioned, set this pin to "L" level. This pin has an (11, 12)internal pull-down resistor.

#### 4. MSM6650 64-Pin plastic QFP (64-Pin plastic SDIP)

#### FEDL6650DIGEST-05

#### **OKI** Semiconductor

# MSM6650 Family

| Pin                              | Symbol    | Туре | Description                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------|-----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6 (60)                           | AGND      |      | Analog ground pin.                                                                                                                                                                                                                                                                                                                                      |

| 7 (61)                           | DGND      | _    | Digital ground pin.                                                                                                                                                                                                                                                                                                                                     |

| 8 (62)                           | $AV_{DD}$ | _    | Analog power pin. Insert a 0.1 $\mu\text{F}$ or more bypass capacitor between this pin and AGND.                                                                                                                                                                                                                                                        |

| 9 (63)                           | $DV_{DD}$ | _    | Digital power pin. Insert a 0.1 $\mu F$ or more bypass capacitor between this pin and DGND.                                                                                                                                                                                                                                                             |

| 12 (2)                           | MCK       | 0    | Main clock output pin. Use MCK as a connection pin for the MSC1192, etc.<br>When the IC is standby status, MCK is held high.                                                                                                                                                                                                                            |

| 16 (6)                           | CPU       | I    | CPU Mode. Set to "H" level to select Microcontroller Interface mode.                                                                                                                                                                                                                                                                                    |

| 17 (7)                           | SERIAL    | I    | Serial/Parallel Interface Select. This input selects either the parallel or the serial input interface. The serial input interface is selected with a high level; the parallel input interface is selected with a low level.                                                                                                                            |

| 30 (20)                          | CE        | 0    | Chip Enable. $\overline{CE}$ is a timing output pin to control read of external memory. This pin outputs when $\overline{RCS}$ is at the "L" level. This pin outputs "H" level when $\overline{RCS}$ is at the "H" level.                                                                                                                               |

| 31 (21)                          | RCS       | I    | Read Chip Select. The data bits D0-D7 are internally pulled down when $\overline{\text{RCS}}$ is high. Addresses and $\overline{\text{CE}}$ are output when $\overline{\text{RCS}}$ is at "L" level. The RA22-RA0 address pins become high impedance and $\overline{\text{CE}}$ pin outputs "H" level when $\overline{\text{RCS}}$ is at the "H" level. |

| 32, 34-<br>40<br>(22, 24-<br>30) | D0-D7     | I    | External Memory Data Bus. Data is input when RCS is low. When RCS is high, these pins become low due to internal pull-down resistors.                                                                                                                                                                                                                   |

| 41-63<br>(31-40,<br>42-54)       | RA0-RA22  | 0    | External Memory Address. These are address pins for an external memory output when $\overline{\text{RCS}}$ is low. These pins become high impedance status if $\overline{\text{RCS}}$ is in "H" level.                                                                                                                                                  |

| 15, 64<br>(5, 55)                | TEST1, 2  | Ι    | Test. Set these pins to "H" level.                                                                                                                                                                                                                                                                                                                      |

| 18 (8)                           | IBUSY     | 0    | Outputs a "L" level during playback or when AOUT is at 1/2 $V_{\mbox{\scriptsize DD}}$ (except standby conversion)                                                                                                                                                                                                                                      |