### OKI

# MSM66587 Family

### User's Manual

**CMOS 16-bit microcontroller**

**SECOND EDITION**

ISSUE DATE: Jan. 2000

FEUL66587-02

<u>NOTICE</u>

- 1. The information contained herein can change without notice owing to product and/or technical improvements. Before using the product, please make sure that the information being referred to is up-to-date.

- 2. The outline of action and examples for application circuits described herein have been chosen as an explanation for the standard action and performance of the product. When planning to use the product, please ensure that the external conditions are reflected in the actual circuit, assembly, and program designs.

- 3. When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating temperature.

- 4. Oki assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified operating range.

- 5. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of the product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

- 6. The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g., office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not authorized for use in any system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or application may result in the loss or damage of property, or death or injury to humans. Such applications include, but are not limited to, traffic and automotive equipment, safety devices, aerospace equipment, nuclear power control, medical equipment, and life-support systems.

- 7. Certain products in this document may need government approval before they can be exported to particular countries. The purchaser assumes the responsibility of determining the legality of export of these products and will take appropriate and necessary steps at their own expense for these.

- 8. No part of the contents contained herein may be reprinted or reproduced without our prior permission.

- 9. MS-DOS is a registered trademark of Microsoft Corporation.

Copyright 2000 Oki Electric Industry Co., Ltd.

### Preface

This user's manual describes the hardware of Oki-original CMOS 16-bit microcontrollers MSM66587 family. In addition to this manual, Oki also provides the following manuals which should be read with regard to the MSM66587 family.

nX-8/500S Core Instruction Manual

- nX-8/500S core instruction set

- Addressing modes

CC665S User's Manual

- Optimized compiler CC665S operation

- C-language specifications in CC665S

CL665S User's Manual

• Compiler loader CL665S operation

RTL665S Run Time Library Reference

• C run time library explanation

MAC66K Assembler Package User's Manual

- Package overview

- RAS66K (relocatable assembler) operation

- RAS66K assembly language explanation

- RL66K (linker) operation

- LIB66K (librarian) operation

- OH66K (object converter) operation

Macroprocessor MP User's Manual

- MP operation

- Macro language

Ultra-66K User's Manual

- Ultra-66K (Emulator) explanation

- PathFinder-66K (Debugger) explanation

PW66K Flash Writer System User's Manual

• PW66K Flash Writer System operation

This document is subject to change without notice.

| Classification  | Notation                                                                                                                         | Description                                                                                                                                                                                                                                                                                              |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ■ Numeric value | xxH<br>xxb                                                                                                                       | Represents a hexadecimal number<br>Represents a binary number                                                                                                                                                                                                                                            |

| ■ Unit          | Word, W<br>byte, B<br>nibble, N<br>mega-, M<br>kilo-, K<br>kilo-, k<br>mil-, m<br>micro-, µ<br>nano-, n<br>second, s<br>KB<br>MB | 1 word = 16 bits<br>1 byte = 2 nibbles = 8 bits<br>1 nibble = 4 bits<br>10 <sup>6</sup><br>$2^{10} = 1024$<br>$10^3 = 1000$<br>$10^{-3}$<br>$10^{-6}$<br>$10^{-9}$<br>second<br>1KB = 1 kilobyte = 1024 bytes<br>1MB = 1 megabyte = 2 <sup>20</sup> bytes<br>= 1,048,576 bytes                           |

| Terminology     | "H" level<br>"L" level                                                                                                           | The signal level of the high side of the voltage;<br>indicates the voltage level of $V_{IH}$ and $V_{OH}$ described in the electrical characteristics.<br>The signal level of the low side of the voltage; indicates voltage level of $V_{IL}$ and $V_{OL}$ described in the electrical characteristics. |

|                 | Opcode trap                                                                                                                      | Operation code trap. Occurs when an empty<br>area that has not been assigned an<br>instruction is fetched, or when an instruction<br>code combination that does not contain an<br>instruction is addressed.                                                                                              |

#### Notation

### Table of Contents

| Chap | ter 1 Overview         | 1-1 |

|------|------------------------|-----|

| 1.1  | Features               | 1-1 |

| 1.2  | Block Diagram          |     |

| 1.3  | Pin Configuration      |     |

| 1.4  | Basic Operation Timing | 1-5 |

|      |                        |     |

| Chap | •                      |     |

| 2.1  | P0_0-P0_7              | 2-1 |

| 2.2  | P1_0-P1_7              | 2-1 |

| 2.3  | P2_0-P2_7              | 2-1 |

| 2.4  | P4_0-P4_7              | 2-2 |

| 2.5  | P5_4, P5_5             | 2-2 |

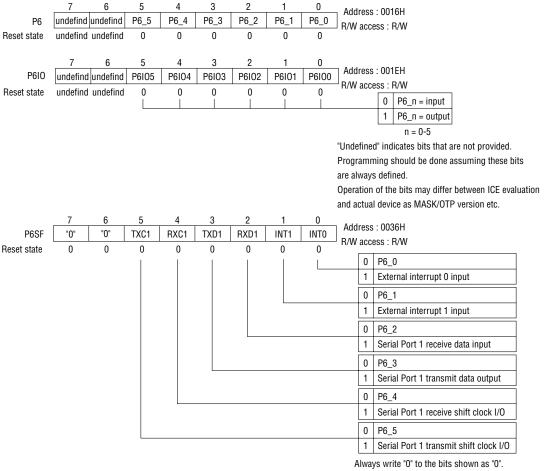

| 2.6  | P6_0-P6_5              | 2-3 |

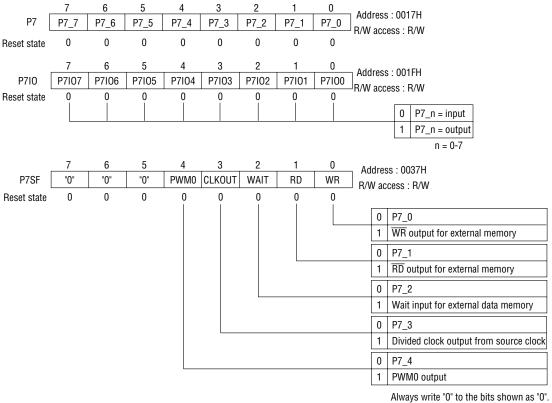

| 2.7  | P7_0-P7_7              | 2-4 |

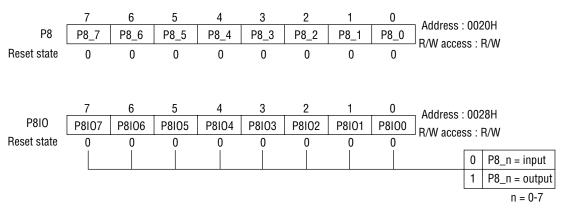

| 2.8  | P8_0-P8_7              |     |

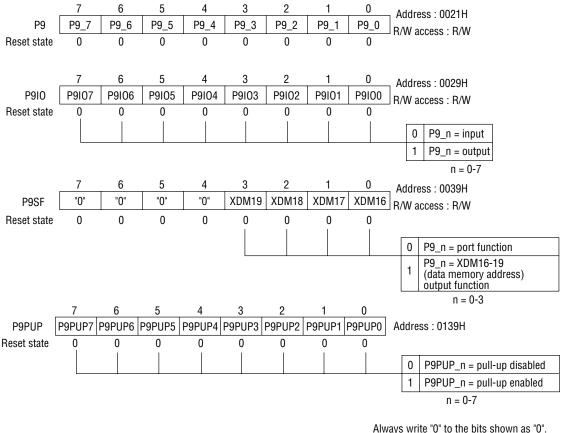

| 2.9  | P9_0-P9_7              | 2-5 |

| 2.10 | P10_0-P10_7            | 2-5 |

| 2.11 | P12_0-P12_7            |     |

| 2.12 | AI0-AI3                |     |

| 2.13 | V <sub>REF</sub>       | 2-6 |

| 2.14 | AGND                   |     |

| 2.15 | OSC0, OSC1             | 2-6 |

| 2.16 | <u>NMI</u>             |     |

| 2.17 | RES                    |     |

| 2.18 | EA                     |     |

| 2.19 | V <sub>DD</sub>        | 2-6 |

| 2.20 | GND                    |     |

| 2.21 | Pin Configurations     |     |

| 2.22 | Unused Pins            | 2-9 |

| Chapter 3 | CPU Architecture                                       | 3-1 |

|-----------|--------------------------------------------------------|-----|

| 3.1 Men   | nory Space                                             | 3-1 |

|           | Memory Space Expansion                                 |     |

|           | Program Memory Space                                   |     |

| (1)       | Accessing Program Memory Space                         | 3-4 |

|           | Vector Table Area                                      |     |

| (3)       | VCAL Table Area                                        | 3-5 |

|           | ACAL Area                                              |     |

| 3.1.3     | Data Memory Space                                      | 3-7 |

| (1)       | Special Function Register (SFR) Area                   | 3-9 |

| (2)       | Expanded Special Function Register (Expanded SFR) Area | 3-9 |

| (3)       | Internal RAM Area                                      | 3-9 |

| (4)       | Fixed Page (FIX) Area                                  | 3-9 |

|           |                                                        |     |

|      | (5)        | Area for Setting Local Registers  | 3-11 |

|------|------------|-----------------------------------|------|

|      |            | External Memory Area              |      |

|      | • • •      | Common Area                       |      |

| 3.   | 1.4        | Accessing Data Memory             |      |

|      | (1)        |                                   |      |

|      | · · ·      | Word Operation                    |      |

| 3.2  |            | isters                            |      |

|      | -          | Arithmetic Register (ACC)         |      |

|      |            |                                   |      |

|      |            | Program Status Word (PSW)         |      |

|      | (2)        |                                   |      |

|      | • • •      | Local Register Base (LRB)         |      |

|      |            | System Stack Pointer (SSP)        |      |

| 3    | 2.3        | Pointing Register (PR)            |      |

|      | 2.4        | Local Registers (R, ER)           |      |

|      | 2.5        | Segment Registers                 |      |

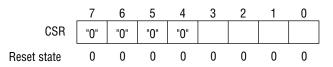

| 0.   |            | Code Segment Register (CSR)       |      |

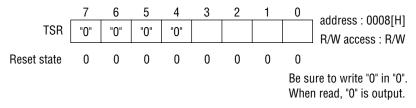

|      |            | Table Segment Register (TSR)      |      |

|      | . ,        | Data Segment Register (DSR)       |      |

| 3.3  |            | ressing Modes                     |      |

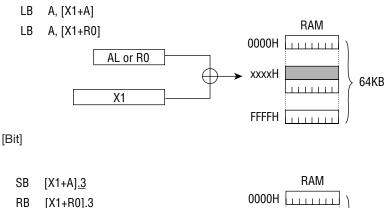

|      | 3.1        | RAM Addressing                    |      |

| 0.   | (1)        |                                   |      |

|      | (2)        |                                   |      |

|      | (2)        |                                   |      |

|      | (4)        |                                   |      |

|      | (5)        |                                   | 3-38 |

| 3    | (3)<br>3.2 | ROM Addressing                    |      |

| 0.   | 3.2<br>(1) |                                   |      |

|      | · · ·      | Table Data Addressing             |      |

|      |            |                                   |      |

|      | (3)        | ROM Window Addressing             |      |

|      | (4)        |                                   | 3-43 |

|      |            |                                   |      |

| Chap | oter 4     | CPU Control Functions             | 4-1  |

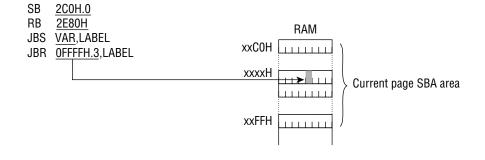

| 4.1  | Star       | ndby Function                     | 4-1  |

| 4.   |            | Standby Control Register (SBYCON) |      |

|      |            | Operation in Standby Modes        |      |

|      |            | HALT Mode                         |      |

|      |            | STOP Mode                         |      |

| 4.2  | • • •      | et Function                       |      |

|      | 1.000      |                                   | + 0  |

|      |            |                                   |      |

| Chap | oter 5     | Memory Control Functions          | 5-1  |

| 5.1  | RON        | / Window Function                 | 5-1  |

| 5.2  | REA        | DY Function                       | 5-2  |

| 5.3  | WAI        | T Function                        | 5-4  |

|      |            |                                   |      |

| Chapter 6           | Port Functions                                                         | 6-1  |

|---------------------|------------------------------------------------------------------------|------|

| 6.1 Port            | Hardware Configurations                                                | 6-3  |

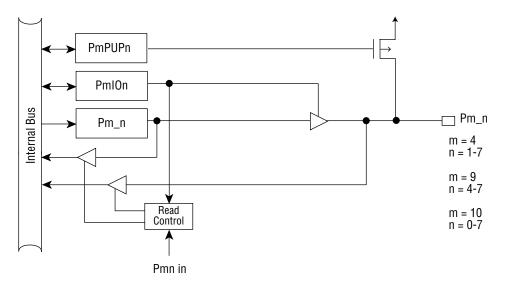

| 6.1.1               | Type A (P0_0-P0_7) Configuration                                       |      |

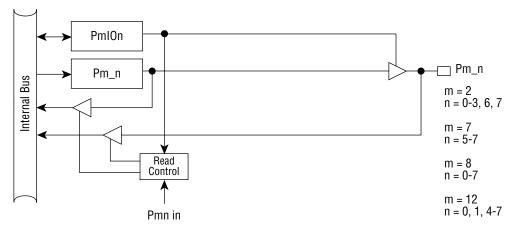

| 6.1.2               | Type B (P1_0-P1_7, P4_0, P9_0-P9_3) Configuration                      |      |

| 6.1.3               | Type C (P2_4, P2_5, P5_4, P5_5, P6_0-P6-5, P7_0-P7_4, P12_2, P12_3)    |      |

|                     | Configuration                                                          | 6-5  |

| 6.1.4               | Type D (P4_1-P4_7, P9_4-P9_7, P10_0-P10_7) Configuration               | 6-6  |

| 6.1.5               | Type E (P2_0-P2_3, P2_6, P2_7, P7_5-P7_7,                              |      |

|                     | P8_0-P8_7, P12_0, P12_1, P12_4-P12_7) Configuration                    | 6-6  |

| 6.2 Port            | Control Registers                                                      | 6-7  |

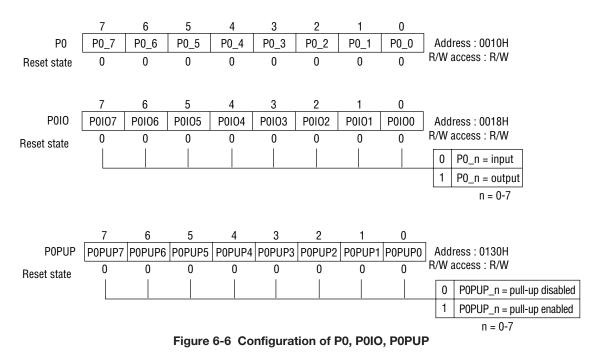

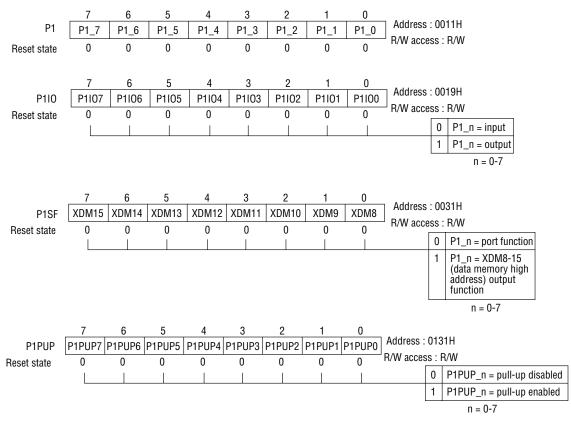

| 6.2.1               | Port Data Registers (Pn: n = 0-2, 4-10,12)                             | 6-7  |

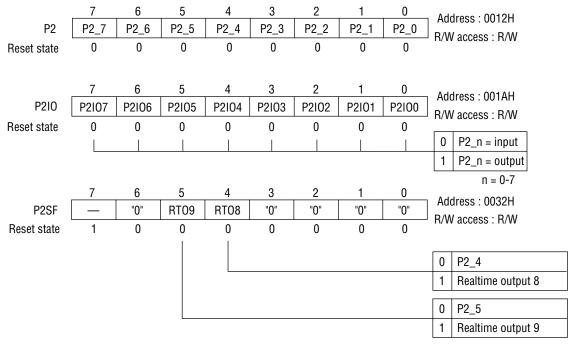

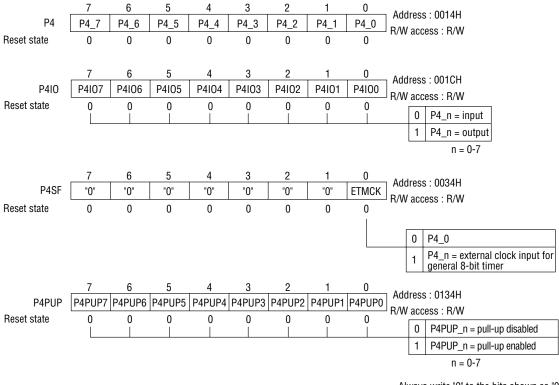

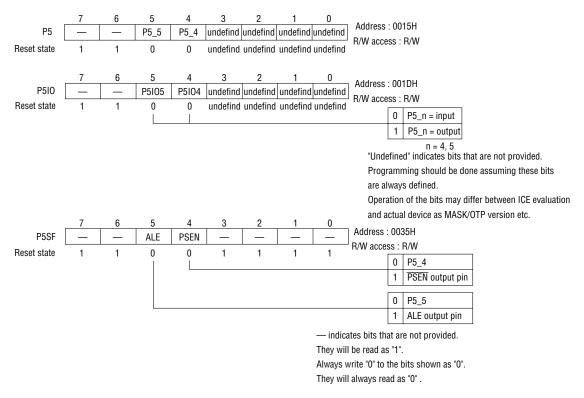

| 6.2.2               | Port Mode Registers (PnIO: n = 0-2, 4-10,12)                           | 6-7  |

| 6.2.3               | Port Secondary Function Control Registers (PnSF: n = 1, 2, 4-7, 9, 12) | 6-7  |

| 6.2.4               | Port Pull-Up Control Registers (PnPUP: n = 0, 1, 4, 9, 10)             | 6-8  |

| 6.3 Port            | 0 (P0)6                                                                | 6-10 |

| 6.4 Port            | : 1 (P1)6                                                              | 6-11 |

|                     | 2 (P2)6                                                                |      |

|                     | 6 4 (P4)                                                               |      |

|                     | .5 (P5)6                                                               |      |

|                     | 6 (P6)6                                                                |      |

|                     |                                                                        |      |

|                     | 8 (P8)6                                                                |      |

|                     | 9 (P9)                                                                 |      |

|                     | 10 (P10)                                                               |      |

| 6.13 Port           | . 12 (P12)                                                             | 6-25 |

|                     |                                                                        |      |

| Chapter 7           | Clock Generator Circuit                                                | 7-1  |

| •                   |                                                                        |      |

| <b>O</b> h an tau 0 | Time Deve Occurter (TDO)                                               |      |

| Chapter 8           |                                                                        |      |

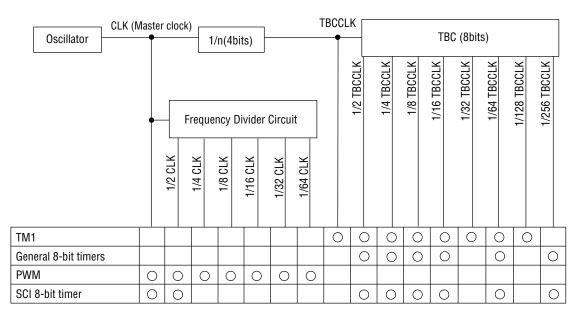

| 8.1 1/n (           | Counter                                                                | 8-2  |

|                     |                                                                        |      |

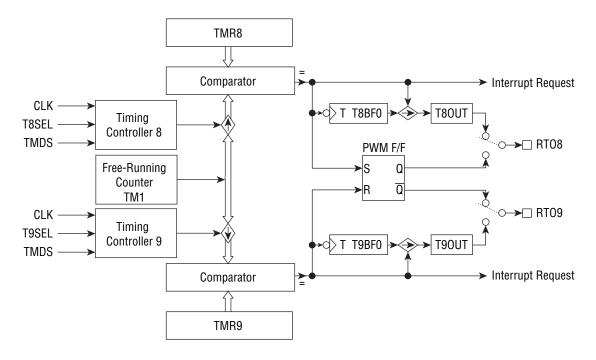

| Chapter 9           | 16-Bit RTO/PWM Timer                                                   | 9-1  |

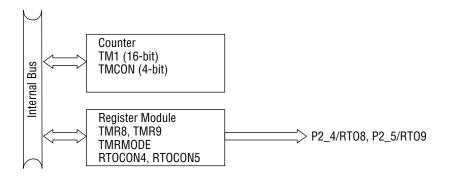

| 9.1 Cou             | nter Configuration                                                     | 9-2  |

|                     | Select Register                                                        |      |

|                     | ister Modules (TMR8, TMR9)                                             |      |

| 9.3.1               | Register Module (TMR8, TMR9) Configuration                             |      |

| (1)                 |                                                                        |      |

| (2)                 | <b>o</b>                                                               |      |

| (3)                 |                                                                        |      |

| 9.3.2               | Register Module (TMR8, TMR9) Operation                                 |      |

| (1)                 |                                                                        |      |

| (2)                 |                                                                        |      |

| (3)                 | PWM Mode Operation                                                     | 9-7  |

| Chap | ter 10 General 8-Bit Timer                                      | 10-1  |

|------|-----------------------------------------------------------------|-------|

| 10.1 | General 8-Bit Timer                                             |       |

|      | (1) General 8-Bit Counter (GTMC)                                |       |

|      | (2) General 8-bit Register (GTMR)                               |       |

|      | (3) General 8-Bit Timer Control Register (GTMCON)               |       |

| Ohan |                                                                 |       |

| -    | ter 11 PWM Function                                             |       |

|      | Clock Divider Circuit                                           |       |

| 11.2 | PWM Configuration                                               |       |

|      | <ul><li>(1) PWM Counter (PWC0)</li></ul>                        |       |

|      | <ul><li>(3) PWM Register (PWR0)</li></ul>                       |       |

|      | (4) PWM Buffer Register (PW0BF)                                 |       |

|      | (5) Comparator Circuit                                          |       |

|      | (6) Output Flip/Flop                                            |       |

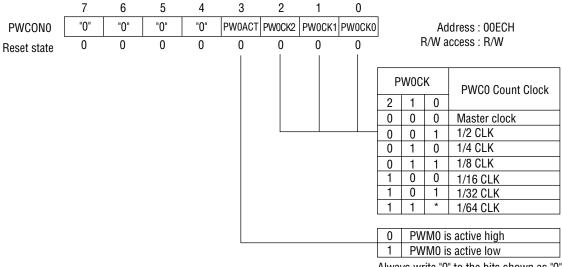

|      | (7) PWM Control Register (PWCON0)                               |       |

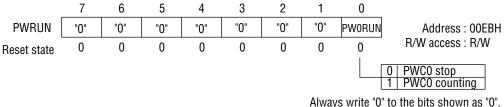

|      | (8) PWM Run Register (PWRUN)                                    |       |

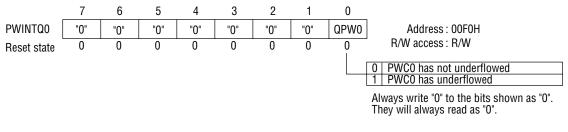

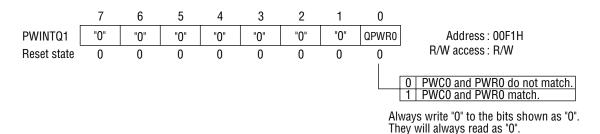

|      | (9) PWM Interrupt Registers (PWINTQ0, PWINTQ1)                  |       |

|      | (10) PWM Interrupt Enable Registers (PWINTE0, PWINTE1)          |       |

| 11.3 | PWM Operation                                                   | 11-7  |

|      |                                                                 |       |

| -    | ter 12 Baud Rate Generator Functions                            |       |

| 12.1 | SCI1 Timer (S1TM) Configuration                                 |       |

|      | (1) SCI1 Timer Counter                                          |       |

|      | (2) SCI1 Timer Register                                         |       |

| 10.0 | (3) SCI1 Timer Control Register (S1CON)<br>SCI1 Timer Operation |       |

| 12.2 |                                                                 | 12-4  |

| Chap | ter 13 Serial Port Functions                                    |       |

| 13.1 | Serial Port Configuration                                       | 13-1  |

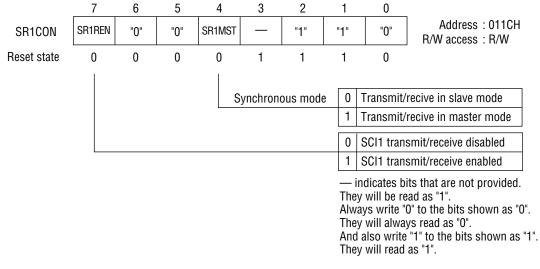

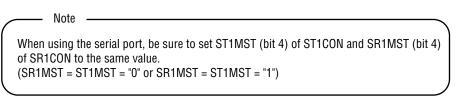

|      | .1.1 SCI1 Transmit/Receive Control Register (SR1CON)            |       |

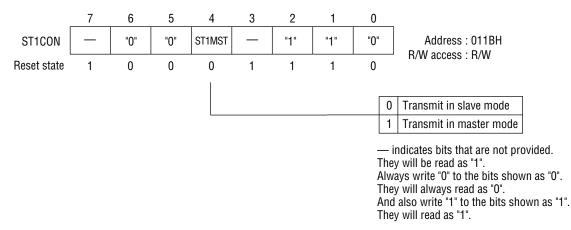

|      | .1.2 SCI1 Transmit Control Register (ST1CON)                    |       |

| 13   | .1.3 SCI1 Transmit/Receive Buffer Register (S1BUF)              | 13-5  |

|      | .1.4 SCI1 Transmit/Receive Register                             |       |

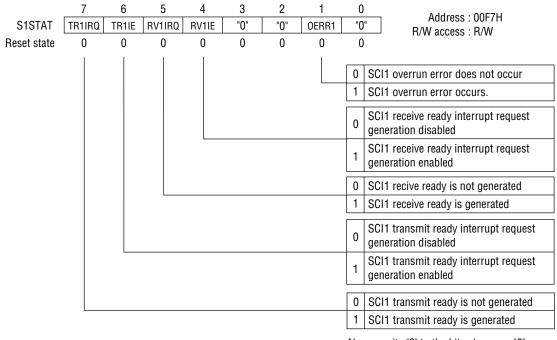

|      | .1.5 SCI1 Status Register (S1STAT)                              |       |

|      | Serial Port Operation                                           |       |

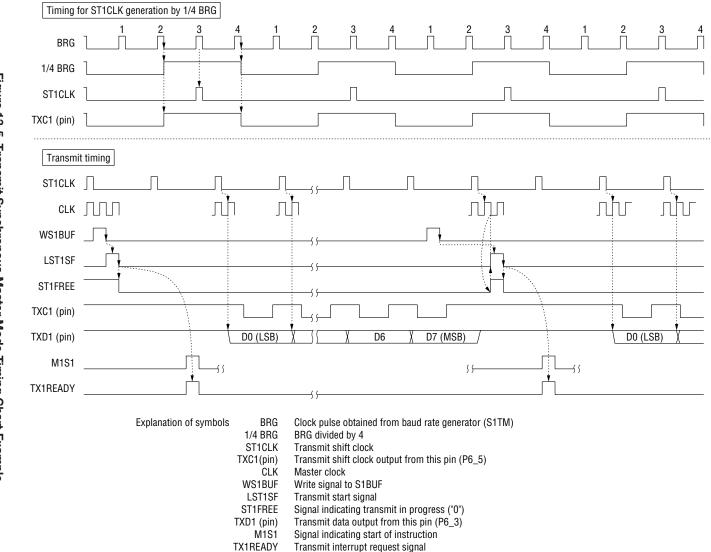

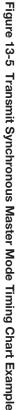

|      | .2.1 Transmit Operation                                         |       |

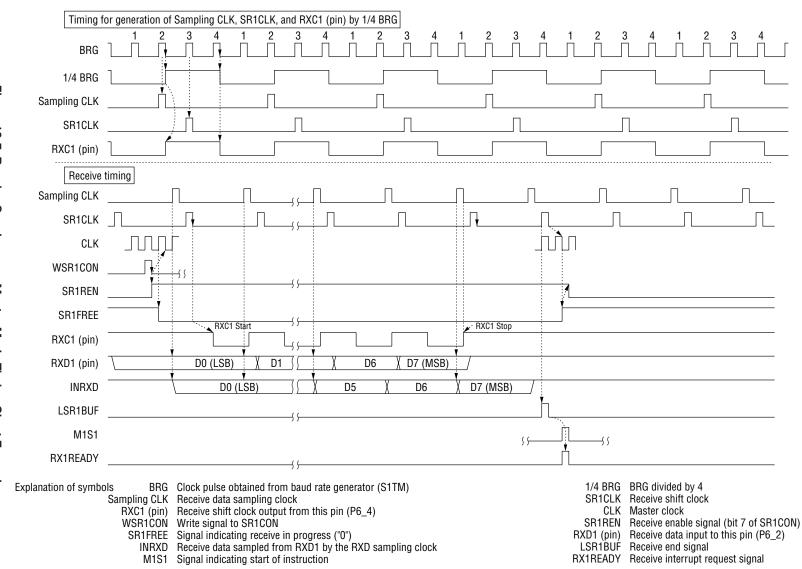

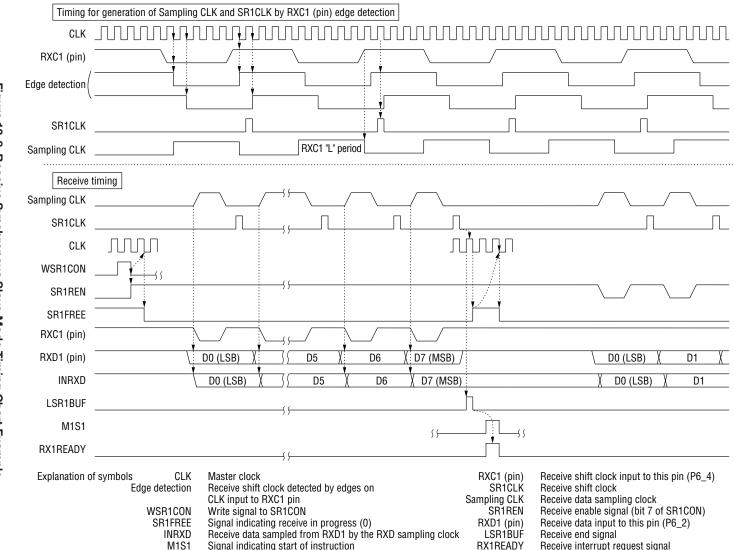

| 13   | .2.2 Receive Operation                                          | 13-11 |

| Chan | ter 14 A/D Converter Functions                                  |       |

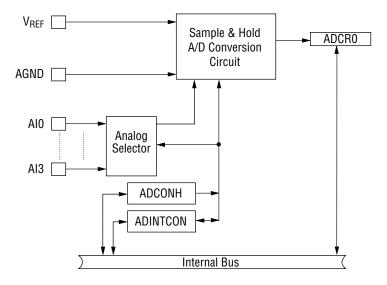

|      | A/D Converter Configuration                                     |       |

| 14.1 | (1) A/D Control Register High (ADCONH)                          |       |

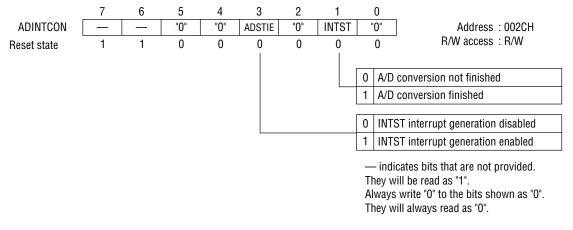

|      | <ul><li>(2) A/D Interrupt Control Register (ADINTCON)</li></ul> |       |

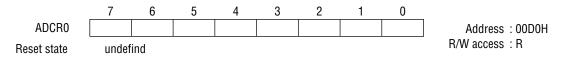

|      | <ul><li>(3) A/D Result Register (ADCR0)</li></ul>               |       |

| Chap | ter 15   | Peripheral Functions                                    |      |

|------|----------|---------------------------------------------------------|------|

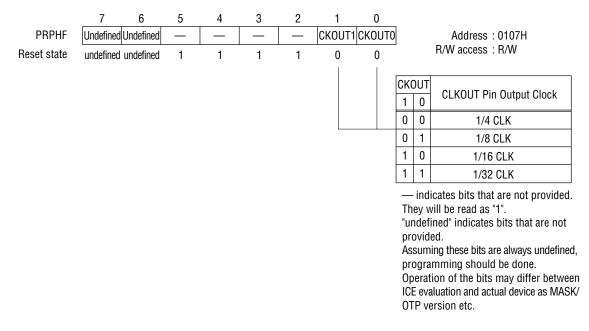

| 15.1 | Clock (  | Dut Function                                            |      |

|      |          |                                                         | 10.1 |

| Chap | ter 16   | External Interrupt Requests                             | 16-1 |

| Chap | ter 17   | Interrupt Request Processing                            |      |

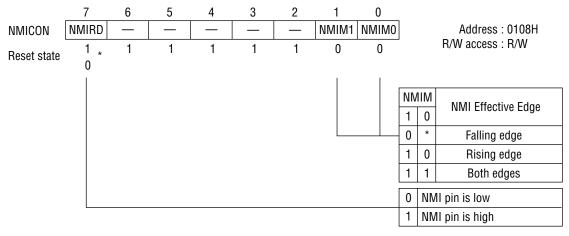

| 17.1 | Non-M    | askable Interrupt (NMI)                                 |      |

| 17.2 |          | ble Interrupts                                          |      |

|      | (1) Ir   | terrupt Request Registers IRQ (IRQ0L, IRQ0H, IRQ1L)     |      |

|      |          | terrupt Enable Registers IE (IE0L, IE0H, IE1L)          |      |

|      | (3) N    | laster Interrupt Enable Flag                            |      |

|      | (4) N    | laster Interrupt Priority Flag                          |      |

|      | (5) Ir   | terrupt Priority Control Registers                      |      |

|      |          | IPX0 (IP00L, IP00H, IP10L)                              |      |

|      |          | IPX1 (IP01L, IP01H)                                     |      |

| 17.3 | Maskal   | ble Interrupt Operation                                 |      |

|      |          |                                                         |      |

| Chap | ter 18   | Bus Port Functions                                      |      |

| 181  | Rus Po   | rt (P0, P1, P9_0-P9_3) Functions                        | 18-1 |

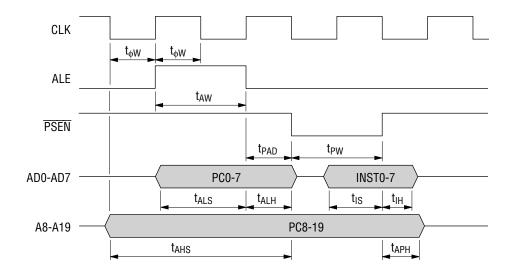

|      |          | 9, P1, P9_0-P9_3 Operation During Program Memory Access |      |

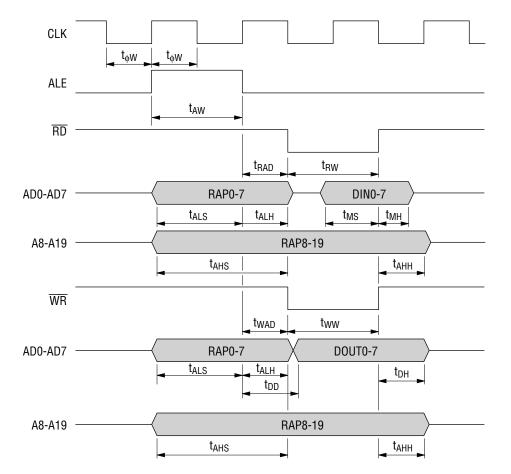

|      |          | , P1, P9_0-P9_3 Operation During Data Memory Access     |      |

|      |          | I Memory Access                                         |      |

|      |          | ternal Program Memory Access                            |      |

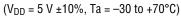

|      |          | ternal Program Memory Access Timing                     |      |

|      |          | ternal Data Memory Access                               |      |

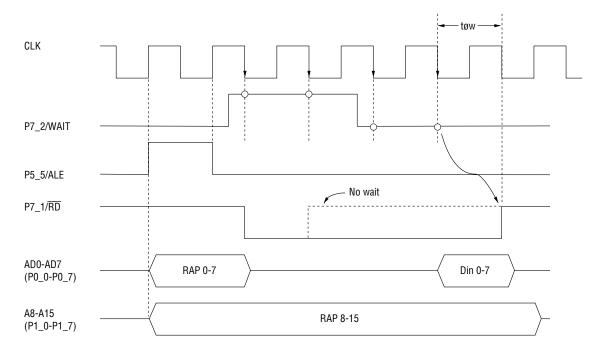

|      |          | ternal Data Memory Access Timing                        |      |

|      |          | ,                                                       |      |

| Chap | ter 19   | Flash Memory                                            |      |

| 19.1 | Summa    | ary                                                     |      |

|      |          | )S                                                      |      |

| 19.3 | Reprog   | ramming Modes                                           |      |

| 19.4 | Serial N | Node                                                    |      |

| 19   | .4.1 Se  | rial Mode Summary                                       |      |

| 19   | .4.2 Se  | tting the Serial Mode                                   |      |

|      | (1) Pir  | ns Used for Serial Mode                                 |      |

|      | (2) Se   | rial Mode Connections                                   |      |

|      | (3) Se   | rial Mode Reprogramming Method                          |      |

|      |          | tes Regarding Serial Mode Usage                         |      |

| 19.5 |          | ode                                                     |      |

|      |          | er Mode Summary                                         |      |

| 19   |          | er Mode Reprogramming                                   |      |

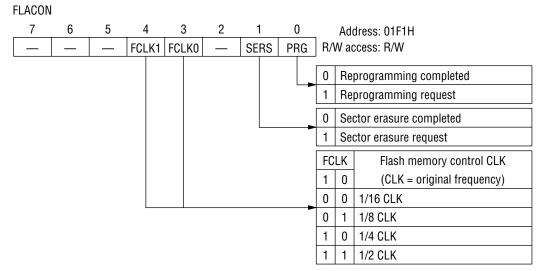

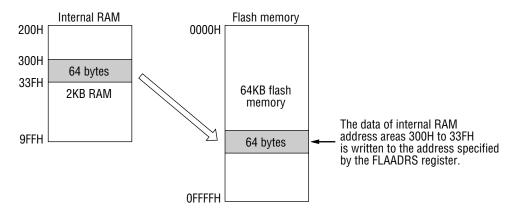

|      |          | ish Memory Address Register (FLAADRS)                   |      |

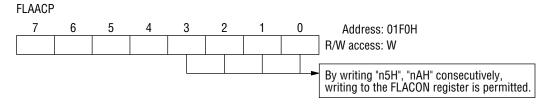

|      |          | Ish Memory Acceptor (FLAACP)                            |      |

|      |          | Ish Memory Control Register (FLACON)                    |      |

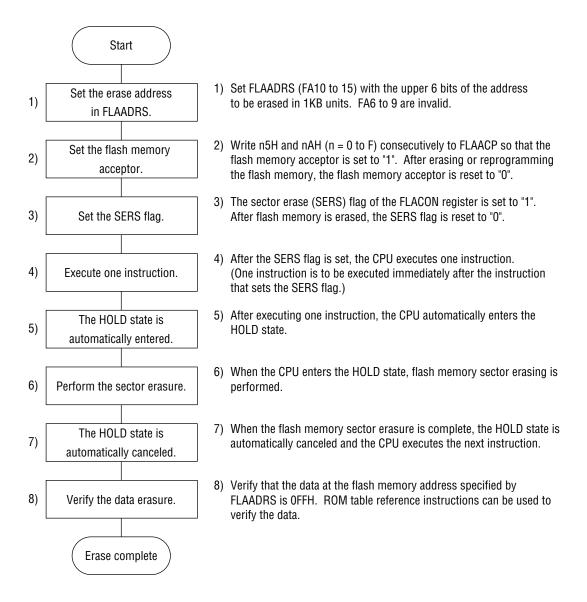

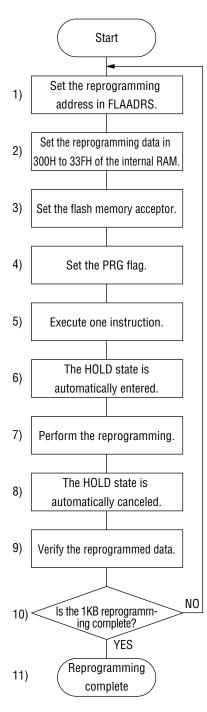

|      | (4) Flo  | wchart Examples for User Mode                           |      |

|      | (5) Example Data Verification Programs to Check Erased or Reprogrammed Data | 19-13 |

|------|-----------------------------------------------------------------------------|-------|

|      | (6) Notes on Usage Regarding User Mode                                      | 19-14 |

| 19.6 | Programming Notes                                                           | 19-15 |

|      | (1) Reprogramming Immediately after Power is Supplied to Flash Memory       | 19-15 |

|      | (2) Note when STOP Mode is Canceled                                         | 19-15 |

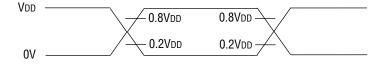

| Chapter 20 Electrical Characteristics                            | 20-1  |

|------------------------------------------------------------------|-------|

| 20.1 Absolute Maximum Ratings                                    | 20-1  |

| 20.2 Recommended Operating Conditions                            |       |

| 20.3 Allowable Output Current                                    |       |

| 20.4 DC Characteristics                                          |       |

| 20.4.1 DC Characteristics ( $V_{DD} = 5 V \pm 10\%$ )            | 20-3  |

| 20.4.2 DC Characteristics (V <sub>DD</sub> = 2.7 to 5.5 V)       | 20-4  |

| 20.5 AC Characteristics                                          |       |

| 20.5.1 AC Characteristics ( $V_{DD} = 5 V \pm 10\%$ )            |       |

| (1) External Program Memory Control                              |       |

| (2) External Data Memory Control                                 |       |

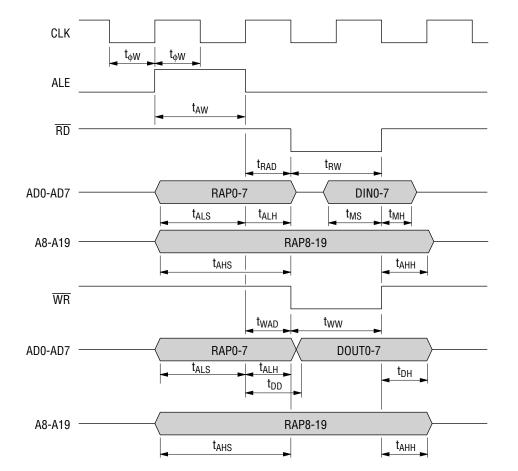

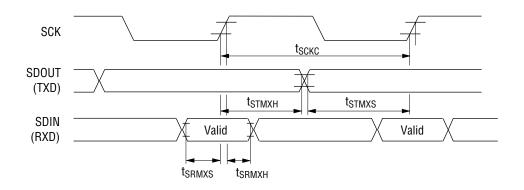

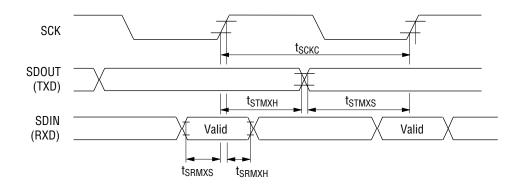

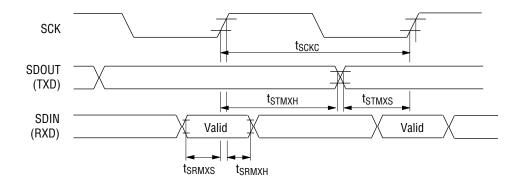

| (3) Serial Port Control                                          |       |

| 20.5.2 AC Characteristics ( $V_{DD}$ = 2.7 to 5.5 V)             |       |

| (1) External Program Memory Control                              |       |

| (2) External Data Memory Control                                 |       |

| (3) Serial Port Control                                          |       |

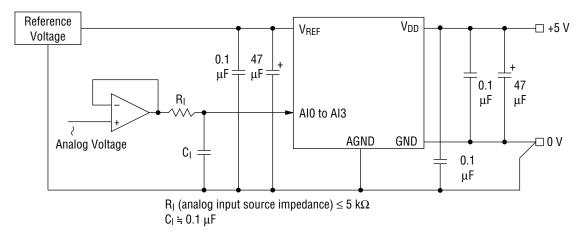

| 20.6 A/D Converter Characteristics                               |       |

| 20.6.1 A/D Converter Characteristics ( $V_{DD} = 5 V \pm 10\%$ ) |       |

| 20.6.2 A/D Converter Characteristics ( $V_{DD} = 3 V \pm 10\%$ ) | 20-14 |

| Chapter 21 Special Function Registers (SFRs)                     | 21-1  |

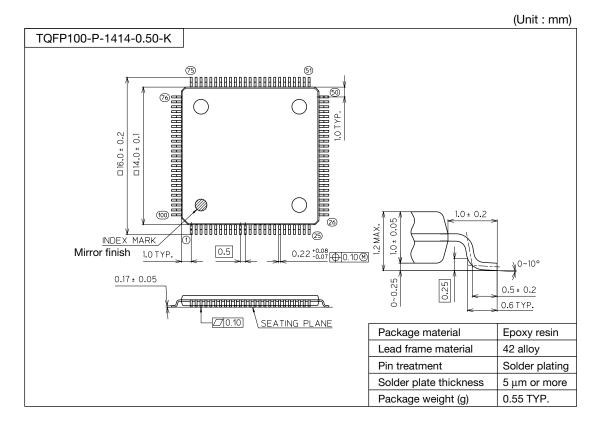

| Chapter 22 Package Dimensions                                    | 22-1  |

| Chapter 1     | Overview                          | 1  |

|---------------|-----------------------------------|----|

| Chapter 2     | Pin Descriptions                  | 2  |

| Chapter 3     | CPU Architecture                  | 3  |

| Chapter 4     | CPU Control Functions             | 4  |

| Chapter 5     | Memory Control Functions          | 5  |

| Chapter 6     | Port Functions                    | 6  |

| Chapter 7     | Clock Generator Circuit           | 7  |

| <br>Chapter 8 | Time-Base Counter (TBC)           | 8  |

| Chapter 9     | 16-Bit RTO/PWM Timer              | 9  |

| Chapter 10    | General 8-Bit Timer               | 10 |

| Chapter 11    | PWM Function                      | 11 |

| Chapter 12    | Baud Rate Generator Functions     | 12 |

| Chapter 13    | Serial Port Functions             | 13 |

| Chapter 14    | A/D Converter Functions           | 14 |

| Chapter 15    | Peripheral Functions              | 15 |

| Chapter 16    | External Interrupt Requests       | 16 |

| Chapter 17    | Interrupt Request Processing      | 17 |

| Chapter 18    | Bus Port Functions                | 18 |

| Chapter 19    | Flash Memory                      | 19 |

| Chapter 20    | Electrical Characteristics        | 20 |

| Chapter 21    | Special Function Registers (SFRs) | 21 |

| Chapter 22    | Package Dimensions                | 22 |

# Chapter 1

Overview

#### 1. Overview

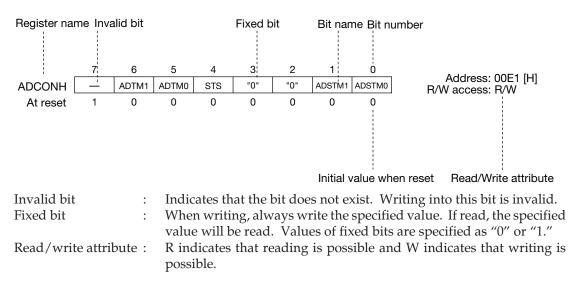

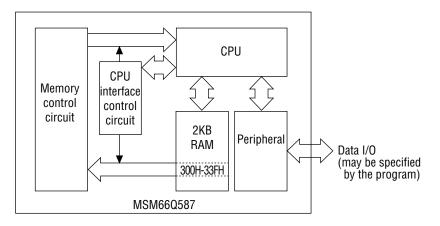

The MSM66587 family of devices are high-performance CMOS 16-bit microcontrollers that integrate a 16-bit CPU (nX-8/500S), ROM, RAM, 8-bit A/D converter, serial port, timers, and PWM. They also allow ROM and RAM to be expanded externally.

The MSM66P587 is of OTP (One-Time PROM) version, the MSM66Q587 is of Flash EEPROM version, and the MSM66X587A is of version with no ROM.

#### 1.1 Features

Powerful instruction set Instruction set superior in orthogonal matrics 8/16-bit arithmetic instructions Multiply/divide instructions Bit manipulation instructions Bit logical operation instructions ROM table reference instructions Abundant addressing modes Register addressing Page addressing Pointer register indirect addressing Stack addressing Immediate addressing Minimum instruction cycle 100 ns at 20 MHz (4.5 V to 5.5 V) 200 ns at 10 MHz (2.7 V to 5.5 V) Program memory (ROM) 64KB (The MSM66X587A includes no internal ROM) Internal: External: 1MB, EA pin active Data memory (RAM) Internal: 2KB External: 1022KB I/O ports Analog input-only port: 4 lines Input/output port: 80 lines Maximum (40 lines with programmable pull-up) Timers Free-run counter: One 16-bit Two 16-bit Realtime output: General autoreload timer: One 8-bit 16-bit PWM Input clock divider: 1 divider 8-bit serial port Synchronous with BRG: 1 port A/D converter 8-bit resolution: 4 channels Interrupts Non-maskable 1 interrupt 9 internal, 4 external (12 vectors) Maskable 3-level priority ROM window function Standby modes HALT mode STOP mode

Package

100-pin plastic TQFP (TQFP100-P-1414-0.50-K) (For external dimensions, refer to Chapter 22)

#### MSM66587 Family Products List

| Туре                        | MSM66587A                                    | MSM66X587A   |  |  |

|-----------------------------|----------------------------------------------|--------------|--|--|

| Operating Temperature       | -30°C to +70°C                               |              |  |  |

| Minimum Instruction         | 100 nsec @20 MHz (4.5 to 5                   | .5V)         |  |  |

| Execution Time              | 200 nsec @10 MHz (2.7 to 5                   | .5V)         |  |  |

| Internal ROM Size           | 64KB                                         | Not included |  |  |

| (Maximum External ROM Size) | (1MB)                                        |              |  |  |

| Internal RAM Size           | 2КВ                                          |              |  |  |

| (Maximum External RAM Size) | (1MB)                                        |              |  |  |

| 1/0 Dort                    | 80 input/output lines (ma                    | x)           |  |  |

| I/O Port                    | (includes 40 lines with programma            | ble pull-up) |  |  |

|                             | 16-bit free-run counter × 1                  | lch          |  |  |

|                             | 16-bit real-time-out × 2ch                   |              |  |  |

|                             | (RTO/toggle output RTO mode selectable)      |              |  |  |

|                             | (Configure 2-ch RTO as 1-ch PWM)             |              |  |  |

| Timer                       | 16-bit PWM × 1ch                             |              |  |  |

|                             | 8-bit geneal auto-reload $\times$ 1ch        |              |  |  |

|                             | (Capable of counting external events)        |              |  |  |

|                             | Used as 8-bit auto-reload × 1ch              |              |  |  |

|                             | serial communication and baud-rate generator |              |  |  |

| Serial Port                 | Synchronous × 1ch                            |              |  |  |

| A/D Converter               | 8-bit × 4ch                                  |              |  |  |

| External Interrunt          | Nonmaskable 1ch                              |              |  |  |

| External Interrupt          | Maskable 4ch                                 |              |  |  |

| Other                       | OTP ROM version : MSM66P587 (2.7 to 5.5      | V)           |  |  |

| Other                       | FLASH ROM version : MSM66Q587 (4.5 to 5.5 V) |              |  |  |

\* The MSM66X587A includes no internal ROM

1

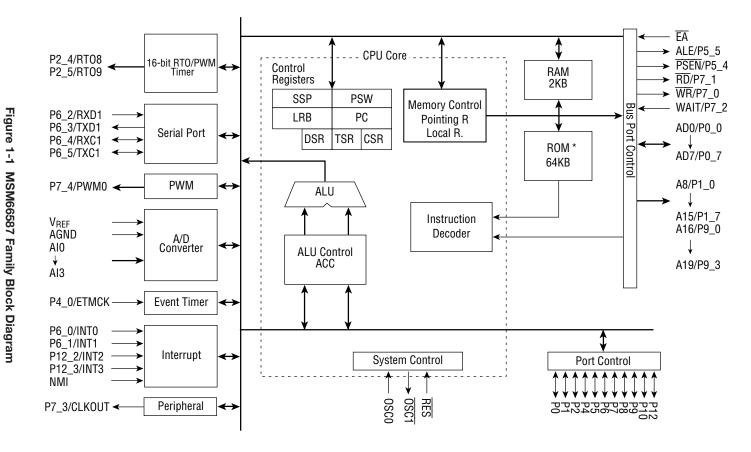

#### 1.3 Pin Configuration (Top View)

Figure 1-2 MSM66587 Family Pin Configuration (100-pin TQFP)

\* For the external dimensions of the package, refer to Chapter 22, "Package Dimensions". For the connections of unused pins, refer to Section 2.22.

#### 1.4 Basic Operation Timing

The MSM66587 family of devices integrate an OKI-original 16-bit CPU Core (nX-8/500S). In the nX-8/500S, each instruction code consists of one byte to six bytes on the basis of 8 bits. There are two types of instruction groups: one is NATIVE instructions and the other is COMPOSIT instruction.

The NATIVE instructions are used frequently and the COMPOSIT instructions are used to implement a wide range of addressing.

The NATIVE instructions consist of one to three bytes to achieve a high code utilization and high instruction execution efficiency.

The COMPOSIT instructions are composed of an address

specification field (PREFIX: 1 to 3 bytes) and operation

specification field (SUFFIX: 1 to 3 bytes).

The combination of PREFIX and SUFFIX can achieve a wide range of addressing.

The basic clock executes one state in a single pulse (CLK). One state is 50 ns (at 20 kHz). Execution of a single instruction takes multiple states (S2, S3,...Sn).

The number of states required for instruction execution differs by instruction. The minimum is 2 states;

The maximum is 48 states (For details refer to the nX-8/500S Core Instruction Manual).

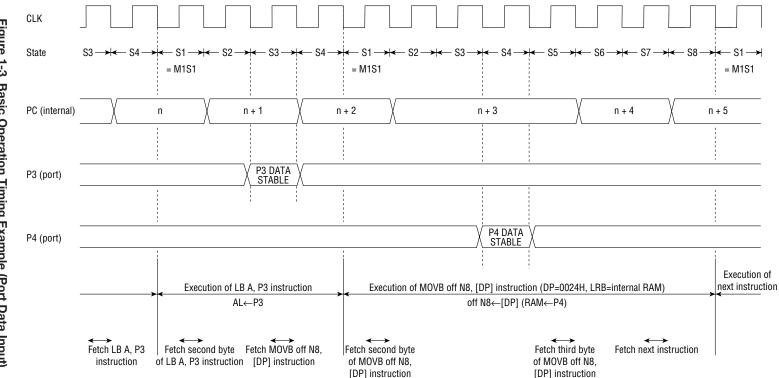

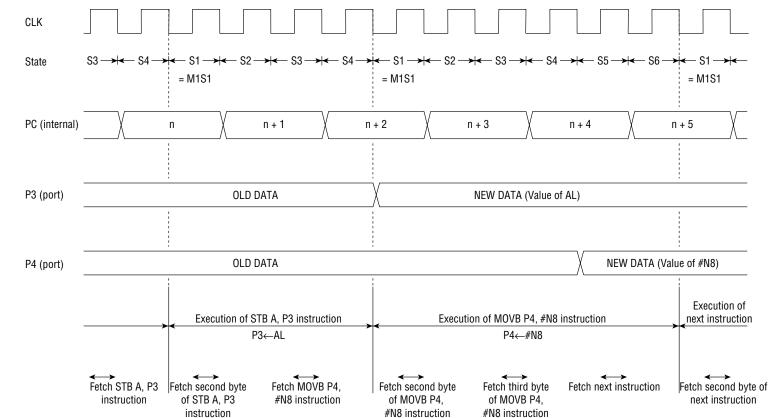

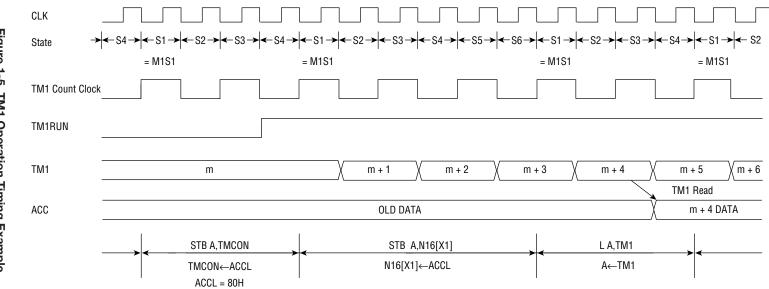

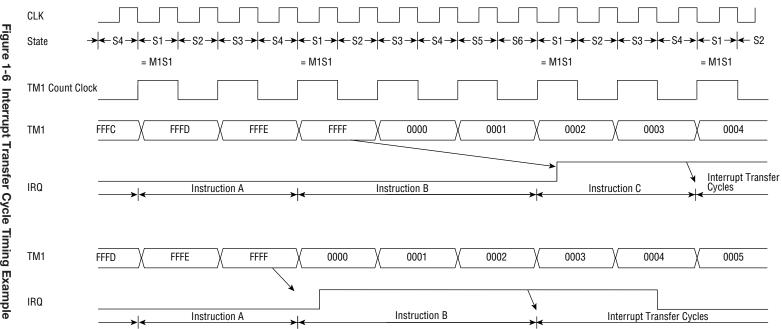

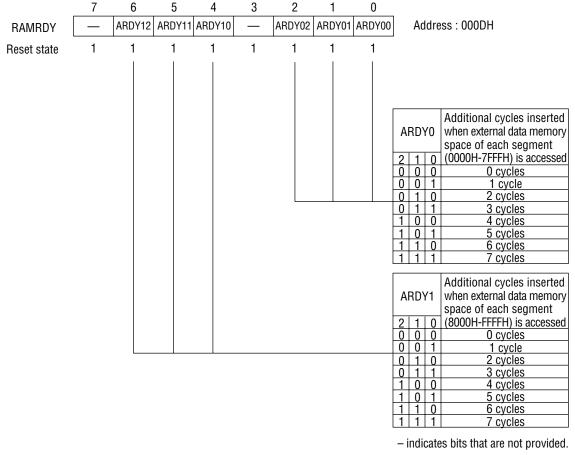

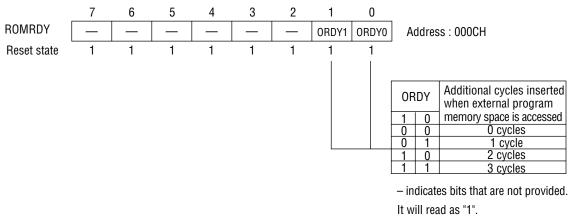

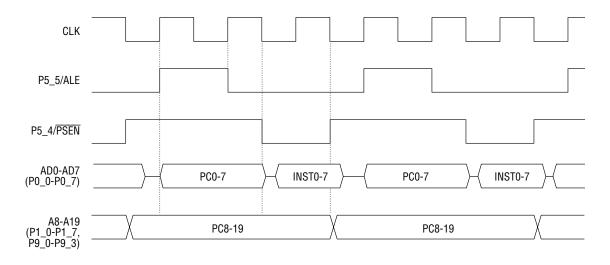

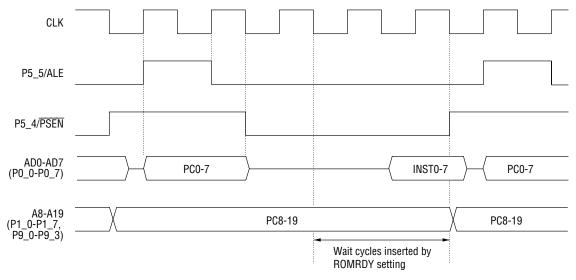

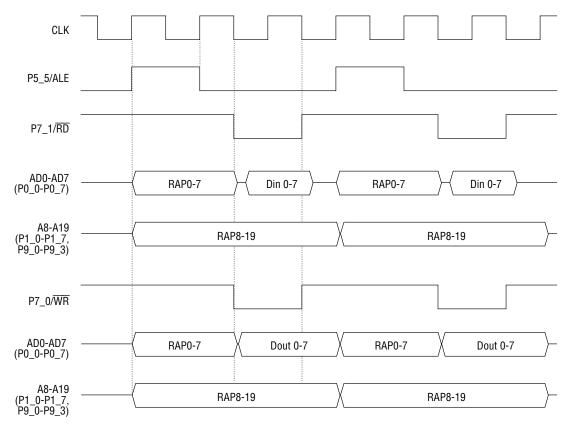

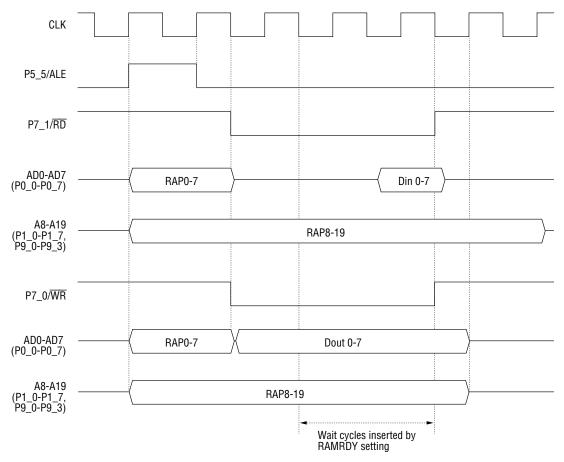

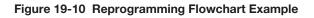

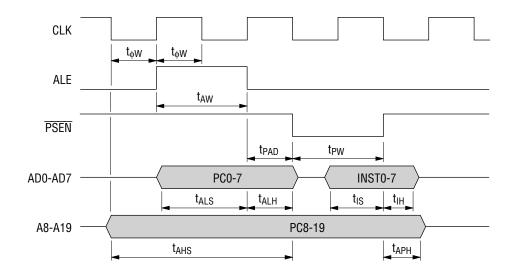

In addition, when program memory is accessed externally, one cycle is inserted automatically for each one-byte read (fetch), and furthermore wait cycles (0 to 3) that are set by the ROM Ready Control Register (ROMRDY), are added. When data memory is accessed externally, three or four cycles (1 cycle=1 state) are inserted automatically for each one byte read or write, and moreover, wait cycles (0 to 7) that are set by the RAM Ready Control Register (RAMRDY) are added. Figures 1-3 and 1-6 show basic timing examples.

#### [Note]

Some COMPOSIT instruction used to write data to external data memory outputs a meaningless RD signal (dummy RD signal) before actual access (PREFIX specifies external data memory). One dummy RD signal is output for byte/bit access and two dummy RD signals are output for word access.

Table 1-1 and 1-2 list instructions with PREFIX and SUFFIX to output dummy RD signals when external data memory is accessed.

In the tables, \* of SUFFIX describes an addressing of PREFIX.

| SUFFIX                 |                  |   | PREFIX  |                  |

|------------------------|------------------|---|---------|------------------|

| Instruction desciption | Instruction code |   | *       | Instruction code |

| SB *                   | 08+bit           |   | Rn      | 68+n             |

| RB *                   | 00+bit           |   | [X1]    | B0               |

| SBR *                  | B8               |   | [DP]    | B2               |

| RBR *                  | B9               |   | [DP-]   | B1               |

| TBR *                  | CA               |   | [DP+]   | B3               |

| MB *.bit, C            | 18+bit           | + | off     | B5               |

| MBR *.bit, C           | BB               |   | dir     | B7               |

| MBR C, *.bit           | BA               |   | N16[X1] | B8               |

| MOVB *,A               | AA               |   | N16[X2] | B9               |

| MOVB *,#N8             | AB               |   | n7[DP]  | 9B               |

| CLRB *                 | C7               |   | n7[USP] | 9B               |

| FILLB *                | D7               |   | [X1+A]  | BA               |

|                        |                  |   | [X1+R0] | BB               |

#### Table 1-1 Instructions (Byte/Bit Manipulations) In Which a Dummy RD Occurs Once (PREFIX and SUFFIX Combinations)

#### Table 1-2 Instructions (Word Manipulations) In Which a Dummy RD Occurs Twice (PREFIX and SUFFIX Combinations)

SUFFIX

| Instruction desciption | Instruction code |

|------------------------|------------------|

| MOVB *,A               | AA               |

| MOVB *,#N16            | AB               |

| CLR *                  | C7               |

| FILL *                 | D7               |

| PREFIX  |                  |  |

|---------|------------------|--|

| *       | Instruction code |  |

| ERn     | 64+n             |  |

| [X1]    | A0               |  |

| [DP]    | A2               |  |

| [DP]    | A1               |  |

| [DP+]   | A3               |  |

| off     | A5               |  |

| dir     | A7               |  |

| N16[X1] | A8               |  |

| N16[X2] | A9               |  |

| n7[DP]  | 8B               |  |

| n7[USP] | 8B               |  |

| [X1+A]  | AA               |  |

| [X1+R0] | AB               |  |

-1  $\overline{}$

MSM66587 Family User's Manual

Chapter 1 Overview

1 - 9

## Chapter 2

# **Pin Descriptions**

2

#### 2. Pin Descriptions

This chapter describes each pin.

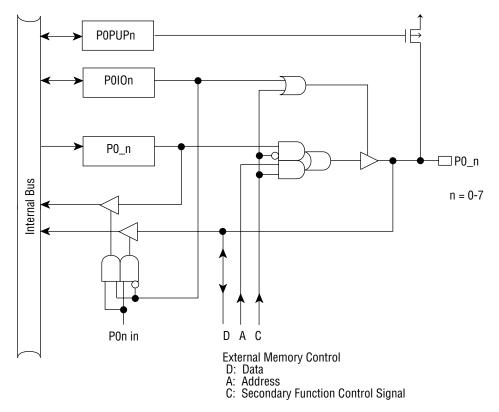

#### 2.1 P0\_0-P0\_7: Input/Output Pins

Port 0 is 8 input/output pins. Input or output can be specified for each bit with the Port 0 Mode Register (P0IO). Pull-up resistors can be specified for each bit with the Port 0 Pull-Up Register (P0PUP).

These pins also function as time-multiplexed address outputs and data input/output pins (AD0-AD7) when accessing memory that has been expanded externally (program or data memory).

After reset (by RES signal input, BRK instruction execution, or op code trap), P0 will be high-impedance inputs.

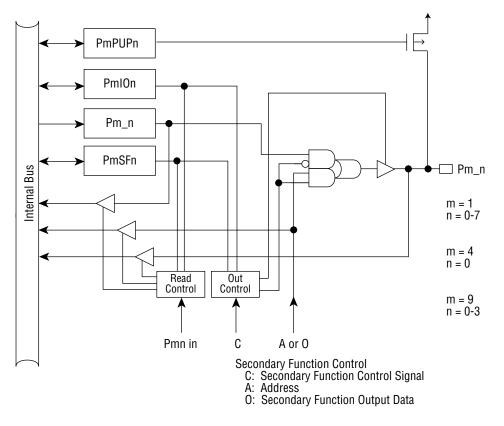

#### 2.2 P1\_0-P1\_7: Input/Output Pins

Port 1 is 8 input/output pins. Input or output can be specified for each bit with the Port 1 Mode Register (P1IO). Pull-up resistors can be specified for each bit with the Port 1 Pull-Up Register (P1PUP).

P1\_0-P1\_7 also have a secondary function as input/output pins for internal operation. Their secondary function can be set for each bit with the Port 1 Secondary Function Control Register (P1SF). The input/output settings by P1IO will be ignored for pins that have been set to the secondary function by P1SF.

< Secondary function of each pin >

A8-A15 (P1\_0-P1\_7)

These pins function as output pins for address A8-A15 when accessing program memory or data memory that has been expanded externally. When the  $\overline{EA}$  pin is low, A8-A15 will be output regardless of P1SF settings.

After reset (by RES signal input, BRK instruction execution, or op code trap), P1 will be high-impedance inputs.

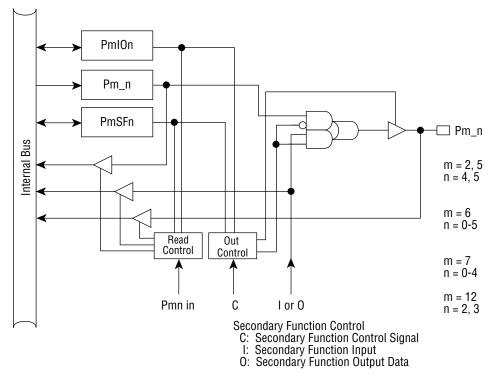

#### 2.3 P2\_0-P2\_7: Input/Output Pins

Port 2 is 8 input/output pins. Input or output can be specified for each bit with the Port 2 Mode Register (P2IO).

P2\_4 and P2\_5 also have a secondary function as input/output pins for internal operation. Their secondary function can be set for each bit with the Port 2 Secondary Function Control Register (P2SF). The input/output settings of P2IO will be ignored for pins that have been set to the secondary function by P2SF.

< Secondary function of each pin >

RTO8 (P2\_4), RTO9 (P2\_5)

These pins output a previously set level when the value of Timer Registers 8 and 9 matches a selected counter value.

After reset (by RES signal input, BRK instruction execution, or op code trap), P2 will be high-impedance inputs.

#### 2.4 P4\_0-P4\_7: Input/Output Pins

Port 4 is 8 input/output pins. Input or output can be specified for each bit with the Port 4 Mode Register (P4IO). Pull-up resistors can be specified for each bit with the Port 4 Pull-Up Register (P4PUP).

P4\_0 also has a secondary function as an input pin for internal operation. Its secondary function can be set for the bit with the Port 4 Secondary Function Control Register (P4SF). The input/output settings by P4IO will be ignored for pins that have been set to the secondary function by P4SF.

< Secondary function of each pin >

ETMCK (P4\_0)

This is the external clock input pin for the counter of a general 8-bit timer.

After reset (by RES signal input, BRK instruction execution, or op code trap), P4 will be high-impedance inputs.

#### 2.5 P5\_4, P5\_5: Input/Output Pins

Port 5 is 2 input/output pins. Input or output can be specified for each bit with the Port 5 Mode Register (P5IO).

P5\_4 and P5\_5 also have a secondary function as output pins for internal operation. Their secondary function can be set for each bit with the Port 5 Secondary Function Control Register (P5SF). The input/output settings of P5IO will be ignored for pins that have been set to the secondary function by P5SF.

2

< Secondary function of each pin >

**PSEN** (P5\_4)

This pin outputs the strobe signal for read operations when external program memory is accessed. Operation will automatically switch to the secondary function when the  $\overline{EA}$  pin is low. This pin will be pulled up when both the  $\overline{EA}$  pin and  $\overline{RES}$  pin are low.

ALE (P5\_5)

This pin outputs the strobe for externally latching the lower 8 address bits output from P0 when external memory is accessed. Operation will automatically switch to the secondary function when the  $\overline{EA}$  pin is low. This pin will be pulled up when both the  $\overline{EA}$  pin and  $\overline{RES}$  pin are low.

After reset (by RES signal input, BRK instruction execution, or op code trap), P5 will be high-impedance inputs.

#### 2.6 P6\_0-P6\_5

Port 6 is 6 input/output pins. Input or output can be specified for each bit with the Port 6 Mode Register (P6IO).

P6\_0-P6\_5 also have a secondary function as input/output pins for internal operation. Their secondary function can be set for each bit with the Port 6 Secondary Function Control Register (P6SF). The input/output settings of P6IO will be ignored for pins that have been set to the secondary function by P6SF.

< Secondary function of each pin >

INT0 (P6\_0), INT1 (P6\_1)

These pins input external interrupts 0 and 1.

RXD1 (P6\_2)

This pin inputs receive data to the Serial Port 1 receive circuit.

TXD1 (P6\_3)

This pin outputs transmit data to the Serial Port 1 transmit circuit.

RXC1 (P6\_4)

This pin outputs the shift clock when the Serial Port 1 receive circuit is in master mode. It inputs the shift clock when the receive circuit is in slave mode.

TXC1 (P6\_5)

This pin outputs the shift clock when the Serial Port 1 transmit circuit is in master mode. It inputs the shift clock when the transmit circuit is in slave mode.

After reset (by RES signal input, BRK instruction execution, or op code trap), P6 will be high-impedance inputs.

#### 2.7 P7\_0-P7\_7: Input/Output Pins

Port 7 is 8 input/output pins. Input or output can be specified for each bit with the Port 7 Mode Register (P7IO).

P7\_0-P7\_4 also have a secondary function as input/output pins for internal operation. Their secondary function can be set for each bit with the Port 7 Secondary Function Control Register (P7SF). The input/output settings of P7IO will be ignored for pins that have been set to the secondary function by P7SF.

< Secondary function of each pin >

WR (P7\_0)

This pin outputs the strobe signal for write operations when external data memory is accessed.

#### RD (P7\_1)

This pin outputs the strobe signal for read operations when external data memory is accessed.

WAIT (P7\_2)

This pin inputs a wait to the internal CPU when external data memory with a slow access time is accessed. CPU is driven to "WAIT" state during WAIT pin high.

#### CLKOUT (P7\_3)

This pin outputs the clock pulses set by the Peripheral Control Register (PRPHF).

PWM0 (P7\_4)

This pin outputs PWM0.

After reset (by RES signal input, BRK instruction execution, or op code trap), P7 will be high-impedance inputs.

When P7\_0 and P7\_1 are used as their secondary functions (WR, RD), they need to be connected externally to pull-up resistors.

#### 2.8 P8\_0-P8\_7: Input/Output Pins

Port 8 is 8 input/output pins. Input or output can be specified for each bit with the Port 8 Mode Register (P8IO).

After reset (by RES signal input, BRK instruction execution, or op code trap), P8 will be high-impedance inputs.

2

#### 2.9 P9\_0-P9\_7: Input/Output Pins

Port 9 is 8 input/output pins. Input or output can be specified for each bit with the Port 9 Mode Register (P9IO). Pull-up resistors can be specified for each bit with the Port 9 Pull-Up Register (P9PUP).

P9\_0-P9\_3 also have a secondary function as output pins for internal operation. Their secondary function can be set for each bit with the Port 9 Secondary Function Control Register (P9SF). The input/output settings of P9IO will be ignored for pins that have been set to the secondary function by P9SF.

< Secondary function of each pin >

A16-A19 (P9\_0-P9\_3)

These pins function as output pins for address A16-A19 when accessing program memory or data memory that has been expanded externally. Note that program memory address A16-A19 will be output even when accessing data memory that has been expanded externally. When the  $\overline{EA}$  pin is low and program memory that has been expanded externally is accessed, A16-A19 will be output regardless of P9SF settings.

After reset (by RES signal input, BRK instruction execution, or op code trap), P9 will be high-impedance inputs.

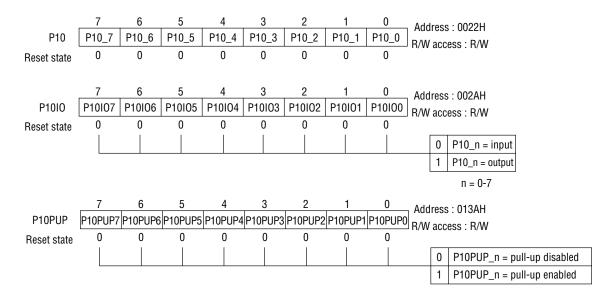

2.10 P10\_0-P10\_7: Input/Output Pins

Port 10 is 8 input/output pins. Input or output can be specified for each bit with the Port 10 Mode Register (P10IO). Pull-up resistors can be specified for each bit with the Port 10 Pull-Up Register (P10PUP).

After reset (by RES signal input, BRK instruction execution, or op code trap), P10 will be high-impedance inputs.

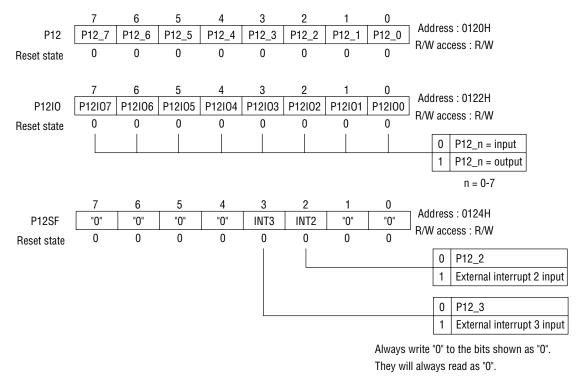

#### 2.11 P12\_0-P12\_7: Input/Output Pins

Port 12 is 8 input/output pins. Input or output can be specified for each bit with the Port 12 Mode Register (P12IO).

P12\_2 and P12\_3 also have a secondary function as input pins for internal operation. Their secondary function can be set for each bit with the Port 12 Secondary Function Control Register (P12SF). The input/output settings of P12IO will be ignored for pins that have been set to the secondary function by P12SF.

< Secondary function of each pin >

INT2 (P12\_2), INT3 (P12\_3)

These pins input external interrupts 2 and 3.

After reset (by RES signal input, BRK instruction execution, or op code trap), P12 will be highimpedance inputs.

#### 2.12 AlO-Al3: Input Pins

These are analog input pins for the A/D converter.

2.13 V<sub>REF</sub>: Input Pin

This is the reference voltage pin for the A/D converter.

2.14 AGND: Input Pin

This is the ground input pin for the A/D converter.

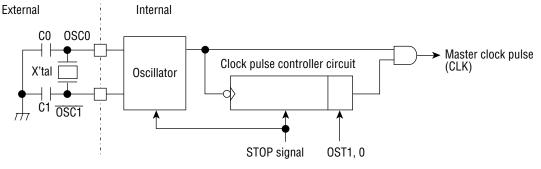

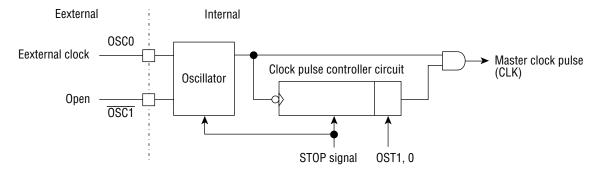

2.15 OSC0, OSC1: Input Pin, Output Pin

These pins connect to a crystal oscillator, ceramic oscillator, or capacitors for base clock oscillation. When the base clock is to be supplied externally, it should be input on the OSC0 pin with the OSC1 pin left open.

2.16 NMI: Input Pin

This input pin requests a non-maskable interrupt.

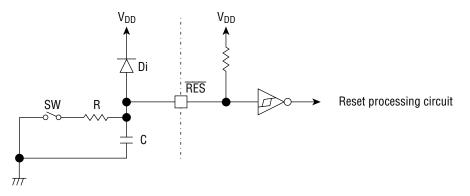

2.17 RES: Input Pin

This is an active-low reset input pin.

2.18 EA: Input Pin

When this pin is high, program addresses 0H-FFFFH will access internal program memory and program addresses 10000H-FFFFFH will access external program memory. <u>To access external program memory</u>, P1, P5, and P9 must be set with their secondary function control registers.

When this pin is low, all program addresses will access external program memory.

2.19 V<sub>DD</sub>: Input Pins

These are voltage pins. All V<sub>DD</sub> pins (9, 17, 37, 67, 93) should be connected to the supply voltage.

2.20 GND: Input Pins

These are ground pins. All GND pins (16, 40, 68, 94) should be connected to ground.

#### 2.21 Pin Configurations

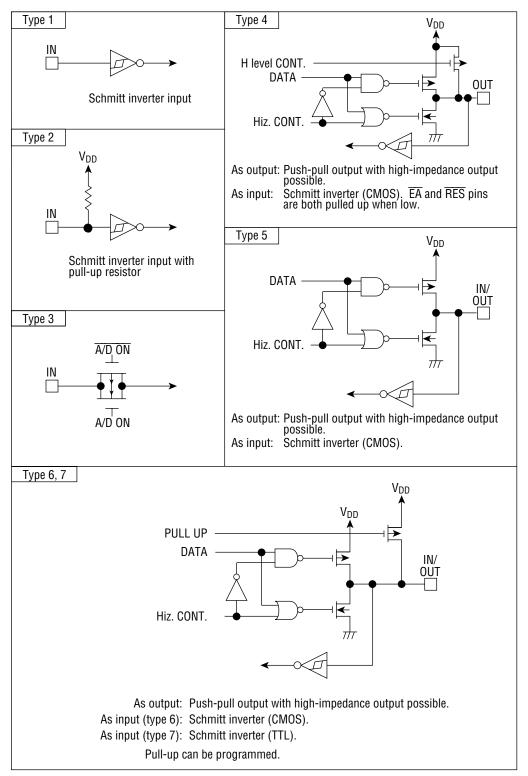

Table 2-1 and Figure 2-1 show a simplified configuration for each pin.

| Pin Name   | Type Number | Pin Name    | Type Number |

|------------|-------------|-------------|-------------|

| P0_0-P0_7  | 7           | P9_0-P9_7   | 6           |

| P1_0-P1_7  | 6           | P10_0-P10_7 | 6           |

| P2_0-P2_7  | 5           | P12_0-P12_7 | 5           |

| P4_0-P4_7  | 6           | AI0-AI3     | 3           |

| P5_4, P5_5 | 4           | NMI         | 1           |

| P6_0-P6_5  | 5           | RES         | 2           |

| P7_0-P7_7  | 5           | ĒĀ          | 1           |

| P8_0-P8_7  | 5           |             |             |

#### Table 2-1 Pin Configurations

#### 2.22 Unused Pins

Table 2-2 shows how to connect unused pins.

#### Table 2-2 Unused Pins

| Pin              | Connection when unused                 |

|------------------|----------------------------------------|

| P0_0-P0_7        |                                        |

| P1_0-P1_7        | When set as programmable pull-up: open |

| P4_0-P4_7        | When set as input: high or low level   |

| P9_0-P9_7        |                                        |

| P10_0-P10_7      | When set as output: open               |

| P2_0-P2_7        |                                        |

| P5_4, P5_5       |                                        |

| P6_0-P6_5        | When set as input: high or low level   |

| P7_0-P7_7        | When set as output: open               |

| P8_0-P8_7        |                                        |

| P12_0-P12_7      |                                        |

| AI0-AI3          | V <sub>REF</sub> or AGND               |

| V <sub>REF</sub> | V <sub>DD</sub>                        |

| AGND             | GND                                    |

| NMI              | High or Low level                      |

| ĒĀ               | High level                             |

2

## **Chapter 3**

3

# **CPU** Architecture

### 3. CPU Architecture

#### 3.1 Memory Space

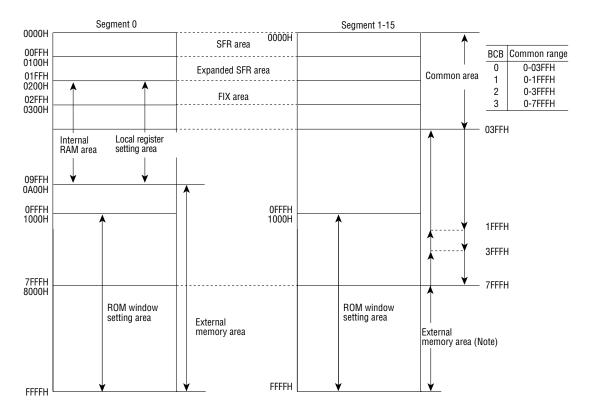

Two independent memory spaces, a program memory space and data memory space are provided. After reset both program memory space and data memory space can be accessed up to 64KB. By changing the Memory Size Control Register (allocated as an SFR), program memory space and data memory space can be expanded to a maximum of 1MB.

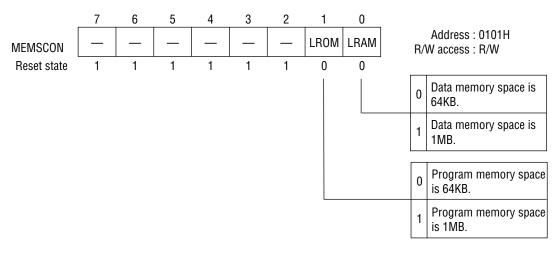

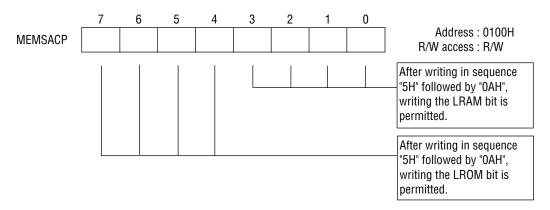

#### 3.1.1 Memory Space Expansion

The Memory Size Control Register (MEMSCON) is allocated in the expanded SFR area to specify the size of the memory spaces. By setting bit 1 (LROM) to "1", program memory space will be expanded to 1MB. By setting bit 0 (LRAM) to "1", data memory space will be expanded to 1MB.

"—" indecates bits that do not exist. When read, "1" is read.

Just before writing the LROM and LRAM bits of MEMSCON, you must write in sequence 5H followed by 0AH to the upper (for LROM) and lower (for LRAM) four bits of the Memory Size Acceptor Register (MEMSACP).

When the LROM and LRAM bits are written (set), the actual change in memory space will be after execution of the instruction after the instruction that wrote the LROM and LRAM bits. Here is a program example showing memory space expansion to each individual model.

• COMPACT model (pragram memory space 64KB, data memory space 1MB)

| MOVB | MEMSACP, #05H |

|------|---------------|

| MOVB | MEMSACP, #0AH |

| MOVB | MEMSCON, #01H |

- MEDIUM model (program memory space 1MB, data memory space 64KB) MOVB MEMSACP, #50H

- MOVB MEMSACP, #30H MOVB MEMSACP, #0A0H MOVB MEMSCON, #02H

- LARGE model (program memory space 1MB, data memory space 1MB)

- MOVB MEMSACP, #55H MOVB MEMSACP, #0AAH

- MOVB MEMSCON, #03H

After reset (RES signal input, BRK instruction execution, or OPTRP trap). <u>MEMSCON can be written one time only</u>. Therefore, once the memory space model has been set, it can be changed to other models only after a reset (RES signal input, BRK instruction, or OPTRP trap).

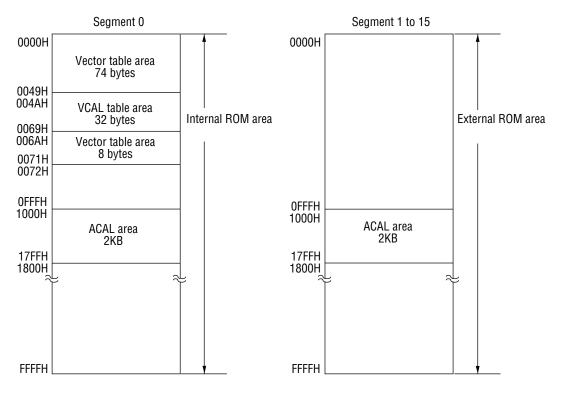

3.1.2 Program Memory Space

Up to 1MB (1,048,576 bytes) of program memory can be accessed as segments 0-15, with one segment equal to 64KB (65,536 bytes). However, to access above 64KB (segments 1-15), the LROM bit of MEMSCON (Memory Size Control Register) allocated as an SFR must be set to 1.

The segment is specified by the Code Segment Register (CSR). The address within a segment is specified by the Program Counter (PC). However, the segment when executing ROM table reference instructions (LCA obj, etc.) and ROM window functions is specified by the Table Segment Register (TSR).

The 64KB in segment 0 are the internal ROM area, and the 64KB in segments 1-15 are the external ROM area.

The following are allocated in segment 0.

Vector table area (82 bytes) VCAL table area (32 bytes)

The following are allocated in each segment.

ACAL area (2048 bytes)

Figure 3-1 shows a memory map of program memory space.

Figure 3-1 Program Memory Space Memory Map

(1) Accessing Program Memory Space

Program memory space is accessed using the Program Counter (PC) and Code Segment Register (CSR). However, when ROM table reference instructions (LC A, obj, etc.) and ROM window functions (refer to Section 5.1) are executed, program memory space will be accessed using the Table Segment Register (TSR) and a register specified by the instruction.

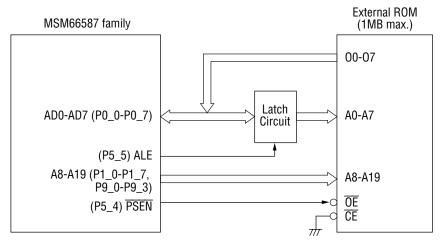

For program memory space, access of the internal ROM area and external memory area is switched automatically by the state of the EA pin (input: pin 36). When the EA pin is input high, program memory addresses 0000H-FFFFH will access the internal memory area, and 10000H-FFFFFH will access the external memory area. <u>To access the external memory area</u>, Port 1, 5, and 9 must be set by their secondary function control registers.

When the  $\overline{EA}$  pin is input low, program addresses across the entire memory space will be accessed in the external memory area.

When program memory space is accessed in the external memory area, Port 0 (I/O pins 51-58: AD0-AD7 outputs and data inputs), Port 1 (output pins 59-66: A8-A15 outputs), and Port 9 (output pins 69-72: A16-A19 outputs) operate as a bus port synchronized to the P5\_5/ALE pin (output pin 50). The P5\_4/PSEN pin (output pin 49) will also be active.

The internal program area that can be fetched is 0000H-FFFDH. Be sure that the last address of instruction codes does not exceed FFFDH. The last address of table data is FFFFH.

(2) Vector Table Area

In program memory space segment 0, the 74 bytes at 0000H-0049H and the 8 bytes at 006AH-0071H form a vector table area (16 types) that stores branch addresses for each type of interrupt request and for reset by RES pin input (input pin 34), by break instruction, or by op code trap (OPTRP).

When a reset or interrupt occurs, the corresponding 2-byte branch address stored in the vector table is loaded into the PC (even address is low data, odd address is high data), and simultaneously 0 is loaded into the CSR. Program execution then starts from the loaded address in segment 0. If, for example, a reset or interrupt occurs during execution of an instruction in segment 1, then execution will branch to an address in segment 0.

If not used as a vector table area, this area can be used as a normal program area.

Table 3-1 shows the vector table for reset and interrupt requests.

#### [Example] Program start address after RES pin input from 0200H

Program Address 0000H 0001H Data Code 00H 02H

Program start address low data Program start address high data

#### Table 3-1 Vector Table

| Program Address | Vector Source                            |

|-----------------|------------------------------------------|

| Address [H]     |                                          |

| 0000            | RES pin input reset                      |

| 0002            | BRK instruction execution reset          |

| 0006            | OPTRP (op code trap) reset               |

| 0008            | NMI pin input interrupt                  |

| 000A            | External interrupt pin INTO interrupt    |

| 000E            | TM1 overflow interrupt                   |

| 0020            | RT08 event generation interrupt          |

| 0022            | RT09 event generation interrupt          |

| 0028            | Serial port 1 transmit/receive interrupt |

| 002A            | S1TM overflow interrupt                  |

| 002C            | GTMC overflow interrupt                  |

| 0030            | A/D conversion completion interrupt      |

| 0032            | PWC0 underflow/matching interrupt        |

| 0038            | External interrupt pin INT1 interrupt    |

| 006E            | External interrupt pin INT2 interrupt    |

| 0070            | External interrupt pin INT3 interrupt    |

#### (3) VCAL Table Area

In program memory space segment 0, the 32 bytes at 004AH-0069H form the VCAL table area that stores branch addresses (VCAL: 16 types) for one-byte call instructions.

When a VCAL instruction is executed, the next address after the VCAL instruction is saved on the system stack, the System Stack Pointer (SSP) is decremented by two, the corresponding 2-byte branch address stored in the VCAL table is loaded into the PC (even address is low data, odd address is high data), and program execution then starts from the loaded address.

However, when program memory space has been expanded to 1MB, the value of CSR is saved at the same time the value of PC is saved, so SSP will be decremented by four. Also, at the same time the branch address is loaded into the PC, a 0 will be loaded into CSR. If, for example, a VCAL instruction in segment 1 is executed, then execution will branch to an address in segment 0.

When program memory space is 64KB with the LROM bit in MEMSCON set to 0, return from subroutines called by a VCAL instruction with an RT instruction. When program memory space is 1 MB with the LROM bit in MEMSCON set to 1, return from subroutines called by a VCAL instruction with an FRT instruction.

If not used as a VCAL table area, this area can be used as a normal program area.

Table 3-2 shows VCAL vector addresses.

[Example] Program start address after VCAL 4AH from 0400H

| <u>Program Address</u> | Data Code |                                 |

|------------------------|-----------|---------------------------------|

| 004AH                  | 00H       | Program start address low data  |

| 004BH                  | 04H       | Program start address high data |

| VCAL Table Address [H] | VCAL Instruction |

|------------------------|------------------|

| 004A                   | VCAL 4AH         |

| 004C                   | VCAL 4CH         |

| 004E                   | VCAL 4EH         |

| 0050                   | VCAL 50H         |

| 0052                   | VCAL 52H         |

| 0054                   | VCAL 54H         |

| 0056                   | VCAL 56H         |

| 0058                   | VCAL 58H         |

| 005A                   | VCAL 5AH         |

| 005C                   | VCAL 5CH         |

| 005E                   | VCAL 5EH         |

| 0060                   | VCAL 60H         |

| 0062                   | VCAL 62H         |

| 0064                   | VCAL 64H         |

| 0066                   | VCAL 66H         |

| 0068                   | VCAL 68H         |

#### Table 3-2 VCAL Vector Table Addresses

#### (4) ACAL Area

In each segment of program memory space, the 2KB at 1000H-17FFH is the area for direct subroutine calls with the 2-byte call instruction (ACAL).

When an ACAL instruction is executed, the next address after the ACAL instruction is saved on the system stack, the System Stack Pointer (SSP) is decremented by two, the 11-bit data including in the ACAL instruction code is loaded into the PC, and program execution then starts from the loaded address. The CSR value is not modified.

3

#### 3.1.3 Data Memory Space

Up to 1MB (1,048,576 bytes) of data memory can be accessed.

The following areas are allocated to data memory space: special function register area (SFR: 256 bytes), expanded SFR area (256 bytes), fixed page area (FIX: 256 bytes), internal RAM area (2,048 bytes), local register setting area (2,048 bytes), and external memory area (1,046,016 bytes).

In addition, the pointing register area (PR: 64 bytes) and special bit addressing area (sbafix: 64 bytes) are allocated to the fixed page area. The ROM window setting area (1000H-FFFFH in every segment) is allocated to the external memory area.

To enable exchange of data between multiple data segments, there is a common area that starts in data memory from address 0H. The SFR area, expanded SFR area, and fixed page area always reside in the common area.

Figure 3-2 shows the memory map of data memory space.

Note: The range of the external memory area in segments 1 to 15 depends on that of the common area to be set.

Figure 3-2 Data Memory Space Memory Map

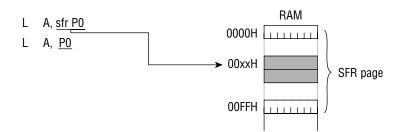

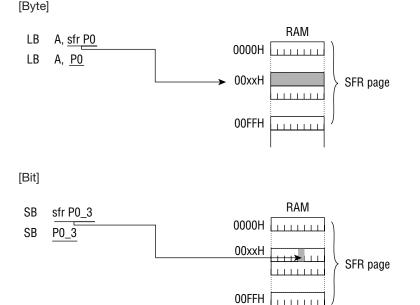

(1) Special Function Register (SFR) Area

In data memory space, the 256 bytes at 0000H-00FFH are allocated to a register group with special functions, like counters, control registers, and mode registers for internal peripheral hardware.

(2) Expanded Special Function Register (Expanded SFR) Area

In data memory space, the 256 bytes at 0100H-01FFH are allocated to a register group with special functions, just like the SFR area. However, note that the expanded SFR area is restricted in that it cannot use SFR addressing.

(3) Internal RAM Area

In data memory space, the 2KB (2,048 bytes) at 0200H-09FFH are allocated to internal RAM.

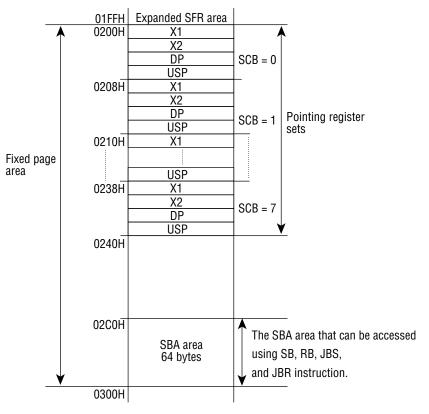

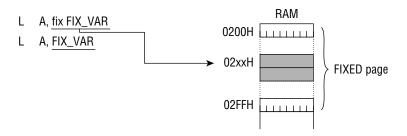

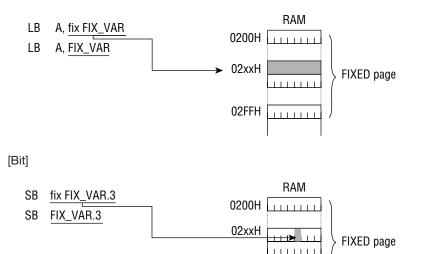

(4) Fixed Page (FIX) Area

In data memory space, the 256 bytes at 0200H-02FFH are allocated as a pointing register (PR) area and special bit address (sbafix) area.

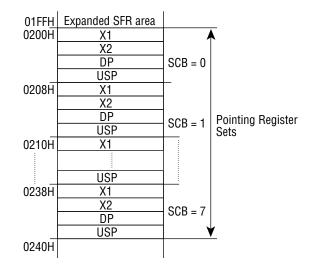

The pointing register area is allocated to 0200H-023FH. It provides eight sets of the following four registers.

- Index Registers (X1, X2)

- Data Pointer (DP)

- User Stack Pointer (USP)

All of the pointing registers are 16-bit registers, with the even address as low data and the subsequent odd address as high data.

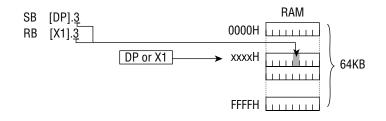

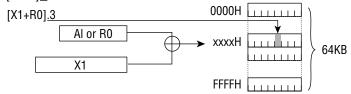

The special bit address area is allocated to 02C0H-02FF. This area enables efficient byte counts with SB, RB, JBR, and JBS instructions.

Figure 3-3 shows a map of the fixed page area.

3

Figure 3-3 Fixed Page Area Map

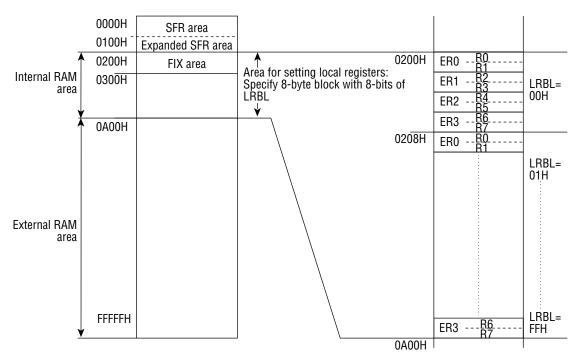

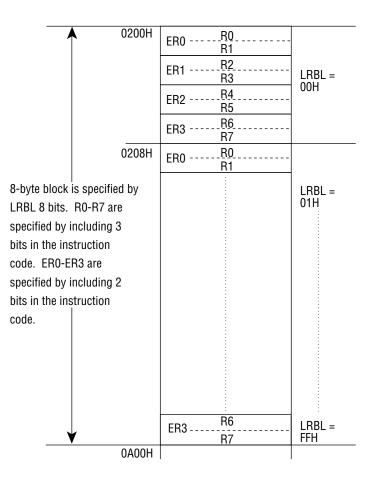

(5) Area for Setting Local Registers

In data memory space, the 2KB at 0200H-09FFH can be set for local registers. Local registers are set in 8-byte blocks with the lower 8 bits of LRB (LRBL). Figure 3-4 shows the map of the area for setting local registers.

Figure 3-4 Map of Area for Setting Local Registers

(6) External Memory Area

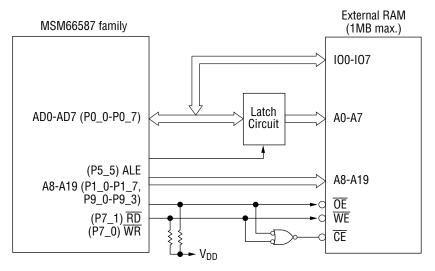

In data memory space, the 1022KB (1,046,016 bytes) at 0A00H-FFFFFH are an external memory area. This area is accessed by the following signals; port 0 (address output AD0-AD7, data input /output), port 1 (address output A8-A15), port 9 (address output A16-A19), P5\_5/ ALE (port 5 P5\_5 secondary function), P7\_0/WR (write strobe output function), and P7\_1/RD (read strobe output function). The ROM window function can also be set in this area with the ROM Window Setting Register. For a specified area in data memory space (1000H and above) the ROM window function makes instruction accesses (read operations) not on data in data memory space, but instead on the data in program memory space at the same address.

In the ROM window function, set the register for enabling it (ROMWIN) and access (read operations) addresses in external data memory.

#### (7) Common Area

Data memory space has a common area for exchanging data between segments. The area common to all segments is in the low end of data memory starting at offset address 0H of each segment. The range of the common area is determined by the values of the BCB bits in the PSW.

| BC | СВ | Common Area Pango |

|----|----|-------------------|

| 1  | 0  | Common Area Range |

| 0  | 0  | 0H-03FFH          |

| 0  | 1  | OH-1FFFH          |

| 1  | 0  | 0H-3FFFH          |

| 1  | 1  | 0H-7FFFH          |

#### 3.1.4 Accessing Data Memory

This section shows memory accesses in data memory space with byte and word operations performed by instructions.

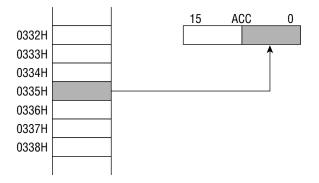

#### (1) Byte Operation

For byte operations, 8-bit data at the address obtained by the instruction is accessed.

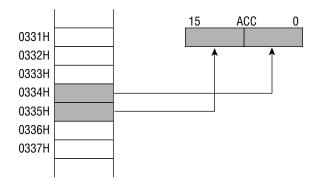

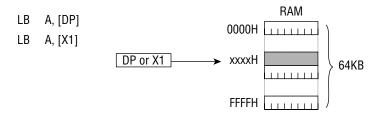

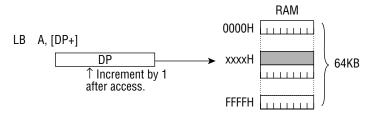

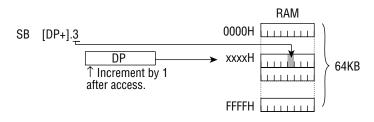

[Example] For LB A, [DP] assume that the value of DP is 0335H.

#### (2) Word Operation

For word operations, 8 bit-data at the address obtained by the instruction but with its least significant bit set to "0" (even address) is accessed as the low 8-bit data and 8bit-data at the obtained address but with its LSB set to "1" (odd address) is accessed as the high 8-bit data.

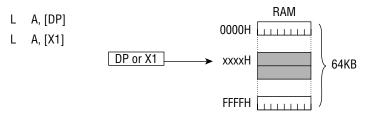

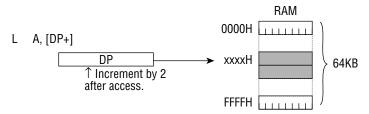

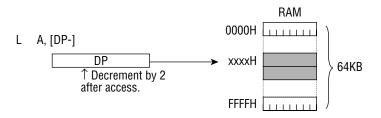

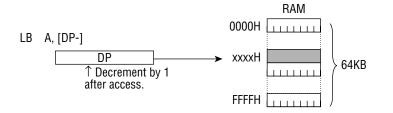

[Example] For L A, [DP] assume that the value of DP is 0334H (or 0335H).

#### 3.2 Registers

Registers are classified by their function: accumulator registers, control registers, pointing registers, special function registers, local registers, and segment registers. Figure 3-5 shows the configuration of the registers.

Pointing Registers

Local Registers

R1

R3

R5

R7

7

| 15 |     | 0 |

|----|-----|---|

|    | X1  |   |

|    | X2  |   |

|    | DP  |   |

|    | USP |   |

07

R0

R2

R4

R6

| Control Registers<br>15 | 0 |

|-------------------------|---|

| PSW                     |   |

| PC                      |   |

| LRB                     |   |

| SSP                     |   |

|                         |   |

Special Function Registers (SFR)

| 7 0 | 7 0 |

|-----|-----|

| 1   | 0   |

| 3   | 2   |

|     |     |

| 253 | 252 |

| 255 | 254 |

### Figure 3-5 Register Configuration

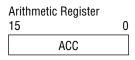

### 3.2.1 Arithmetic Register (ACC)

The accumulator (ACC) is a 16-bit register for all types of calculations. The arithmetic operation, shifting, and so on are performed with as follows.

• Word type: all 16 bits (bits 15-0) are performed

0

(ER0)

(ER1)

(ER2)

(ER3)

- Byte type: lower 8 bits (bits 7-0) are performed

- Nibble type: lower 4 bits (bits 3-0) are performed

When the accumulator specifies the object bit of a bit operation instruction (SBR, RBR, etc.) the upper 5 bits of the lower byte (bits 7-3) specify the address offset and the lower 3 bits (bits 2-0) specify the bit position.

ACC is allocated as an SFR. Its value after reset (by RES signal input, BRK instruction execution, op code trap) will be 0000H.

3 - 14

#### 3.2.2 Control Registers

This is a group of registers with specific functions to control program status, program sequence, local registers, stacks, etc. There are four 16-bit control registers.

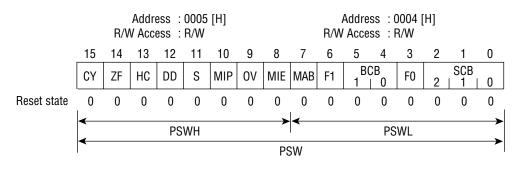

(1) Program Status Word (PSW)

The PSW is a 16-bit register configured as follows.

- Flag for instruction execution (DD)

- Flags set (1) or reset (0) by instruction execution results (CY, ZF, HC, S, OV)

- Flag to specify the pointing register set (SCB0-2)

- Flag to enable (1) or disable (0) all maskable interrupts (MIE)

- Flag to enable (1) or disable (0) priority of all maskable interrupts (MIP)

- Flag to set the segment 0 common area (BCB0, 1)

- Flags available for user use (F0, 1)

- Flag provided for future expansion of CPU core functions, but which is available for user use with the MSM66587 family (MAB)

PSW is divided into 8-bit registers, PSWH (bits 15-8) and PSWL (bits 7-0), so it can be operated on with 8-bit instruction operations in addition to 16-bit operations.

The high byte of PSW (PSWH) contains the following.

- Flag for instruction execution (DD)

- Flags set (1) or reset (0) by instruction execution results (CY, ZF, HC, S, OV)

<u>Please note that when the following instructions are executed, the actual operation of the PSW</u> or PSWH flags may differ from expected.

- Instructions that load contents of PSW or PSWH into ACC. (Value corresponding to ZF in ACC will be undefined.)

- ② Bit operation instructions on ZF.

(ZF will change based on its value immediately prior to execution of the bit operation instruction.)

- ③ Instructions that perform increment, decrement, arithmetic calculation, logical calculation, or comparison on PSW or PSWH (Value of PSW or PSWH after instruction execution will be undefined.)

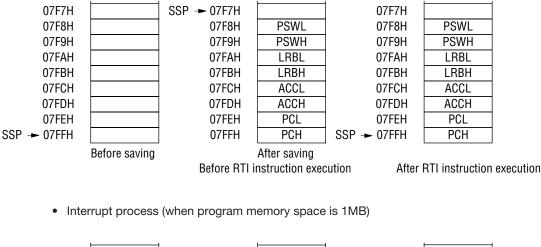

When an interrupt occurs, the PSW will be saved automatically during the interrupt process. It will be restored automatically by execution of an RTI instruction.

PSW is allocated as an SFR. Its value after reset (by RES signal input, BRK instruction execution, op code trap) will be 0000H.

Below is an explanation of each bit in PSW.

Bit 15: Carry Flag (CY)

The Carry Flag will be set (1) if the result of an arithmetic calculation or comparison instruction generates any of the following. Otherwise it will be reset (0).

- Carry is generated from bit 7 for byte calculations.

- Borrow is generated to bit 7 for byte calculations.

- Carry is generated from bit 15 for word calculations.

- Borrow is generated to bit 15 for word calculations.

The Carry Flag can be directly set and reset by instructions and data can also be sent and received to the bits specified by the register. The state of the Carry Flag can also be tested by conditional branch instructions.

Bit 14: Zero Flag (ZF)

The Zero Flag will be set (1) when the following occurs. Otherwise it will be reset (0).

- Result value of an arithmetic calculation instruction is 0.

- Execution of a load instruction to ACC loads a value of 0.

- Object bit of a bit operation instruction is 0.

The state of the Zero Flag can also be tested by conditional branch instructions.

Bit 13: Half-Carry Flag (HC)

The Half-Carry Flag will be set ("1") when the result of executing an arithmetic calculation or comparison instruction (byte and word calculations are the same) carrys or borrows from bit 3. Otherwise it will be reset (0).

Bit 12: Data Descriptor (DD)

The Data Descriptor flag indicates the attribute of data stored in ACC.

- When DD is 1, all 16 bits of ACC data are considered valid.

- When DD is 0, the lower 8 bits of ACC data are considered valid.

When calculation and data transfer instructions with ACC are executed, DD is referred and execution proceeds as follows.

- When DD is 1, calculation and transfer will be executed with words.

- When DD is 0, calculation and transfer will be executed with bytes.

DD can be set ("1") or reset ("0") when a data transfer instruction to ACC is executed and when flag-specific set or reset instructions are executed.

- DD will be set ("1") when a word load instruction to ACC is executed or the SDD instruction is executed.

- DD will be reset ("0") when a byte load instruction to ACC is executed or the RDD instruction is executed.

When DD is modified by execution of a load instruction to ACC or a flag-specific set or reset instruction, the following instruction will refer and execute the modified DD if that instruction is reference DD.

DD is a part of PSW, so it can be overwritten by instructions other than the ones described above. In this case, the following instruction will refer the value of DD before it is modified if that instruction is reference DD. For this use, insert a NOP instruction after the instruction that directly modifies DD.

Bit 11: Sign Flag (S)

The Sign Flag will be set if the MSB of the execution result of an arithmetic or logical operation instruction is "1", and will be reset if MSB = "0".

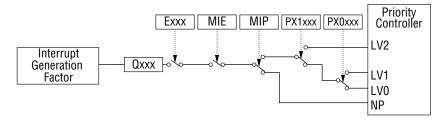

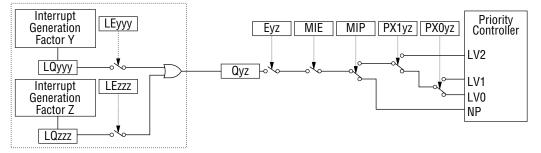

Bit 10: Master Interrupt Priority Flag (MIP)

The Master Interrupt Priority Flag controls the priority function for maskable interrupts. If "1", the priority function is enabled. If "0", the priority function is disabled.

Bit 9: Overflow Flag (OV)

The Overflow Flag will be set ("1") if the execution result of an arithmetic operation instruction exceeds the range that can be expressed as 2's complement (-128 to +127 for byte arithmetic, -32768 to +32767 for word arithmetic). Otherwise it will be reset ("0").

Bit 8: Master Interrupt Enable Flag (MIE)

The Master Interrupt Enable Flag controls whether all maskable interrupts are enabled ("1") or disabled ("0").

This flag will be reset ("0") after the PSW is saved on the system stack during a maskable interrupt transfer cycle. It will be restored when an RTI instruction is executed. When MIE is set ("1"), all maskable interrupts are enabled to occur from the instruction following the one that set MIE. When MIE is reset ("0"), all maskable interrupts are disabled to occur from the instruction following the one that set MIE.

Bit 7: Multiply-Accumulate Bank Flag (MAB)

This flag can be used as a user flag.

Bit 6: User Flag 1 (F1) Bit 3: User Flag 0 (F0)

The User Flags can be set ("1") and reset ("0") by instructions.

Bit 5: Bank Common Base 1 (BCB1) Bit 4: Bank Common Base 0 (BCB0)

The Bank Common Base specifies the last address of the common area between segments in data memory space. The relationship of BCB value and the common area is as follows.

| BC | CB | Common Area Range |  |  |  |

|----|----|-------------------|--|--|--|

| 1  | 0  | Common Area hange |  |  |  |

| 0  | 0  | 0H-03FFH          |  |  |  |

| 0  | 1  | 0H-1FFFH          |  |  |  |

| 1  | 0  | 0H-3FFFH          |  |  |  |

| 1  | 1  | 0H-7FFFH          |  |  |  |

(2) Program Counter (PC)

The Program Counter is a 16-bit counter that stores the program address within a segment to execute next. It is generally incremented by the number of bytes in each instruction executed. When branch and conditional jump instructions are executed, the PC will be loaded with immediate data or the contents of a register. Even if the PC overflows when incremented, the value of CSR will not change.

After reset (by  $\overline{\text{RES}}$  signal input, BRK instruction execution, or op code trap) or when an interrupt occurs, the PC will be loaded with a value from the vector table area.

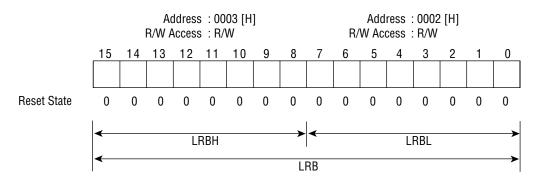

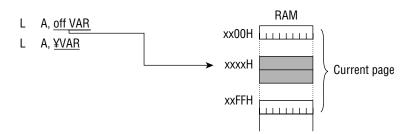

(3) Local Register Base (LRB)

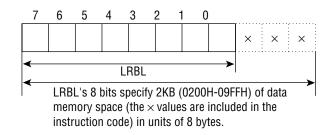

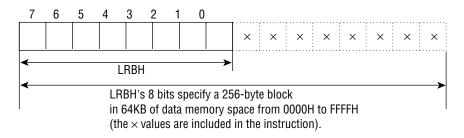

The Local Register Base is a 16-bit register. Its low-order 8 bits (LRBL) specify 2KB (0200H-09FFH) of data memory space (for local register addressing) in units of 8 bytes. Its high-order 8 bits (LRBH) specify 64KB of data memory space (for current page addressing) in units of 256 bytes. The 64 bytes at XXC0H-XXFFH in the current page are an area that can be accessed using the sba.bit of SB, RB, JBR, and JBS instructions.

LRBL (02H) and LRBH (03) are both allocated in the SFR area. After reset (by RES signal input, BRK instruction execution, or op code trap), their contents are undefined.

• LRBL's 8 bits specify 2KB (0200H-09FFH) of data memory space (the X values are included in the instruction code) in units of 8 bytes.

• LRBH's 8 bits specify 64KB of data memory space in units of 256 bytes.

- Bit 2: System Control Base 2 (SCB2)

- Bit 1: System Control Base 1 (SCB1)

- Bit 0: System Control Base 0 (SCB0)

The System Control Base specifies the Pointing Register (PR) set allocated in the fixed page area.

|   | SCB | SCB Pointing Register Set |                        |  |

|---|-----|---------------------------|------------------------|--|

| 2 | 1   | 0                         | Folliting Register Set |  |

| 0 | 0   | 0                         | PR0 (0200H-0207H)      |  |

| 0 | 0   | 1                         | PR1 (0208H-020FH)      |  |

| 0 | 1   | 0                         | PR2 (0210H-0217H)      |  |

| 0 | 1   | 1                         | PR3 (0218H-021FH)      |  |

| 1 | 0   | 0                         | PR4 (0220H-0227H)      |  |

| 1 | 0   | 1                         | PR5 (0228H-022FH)      |  |

| 1 | 1   | 0                         | PR6 (0230H-0237H)      |  |

| 1 | 1   | 1                         | PR7 (0238H-023FH)      |  |

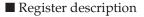

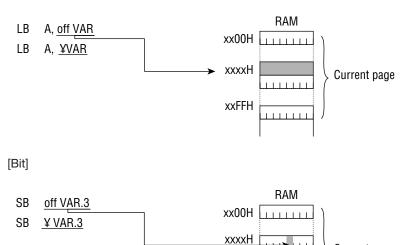

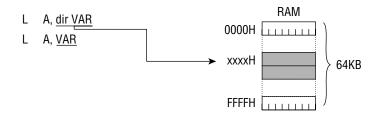

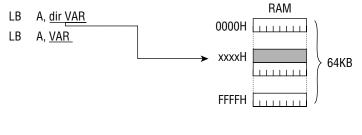

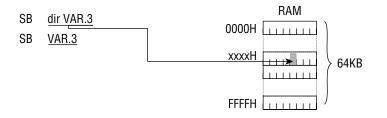

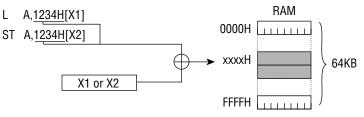

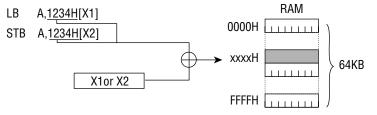

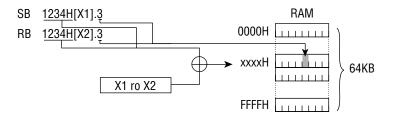

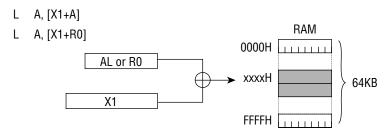

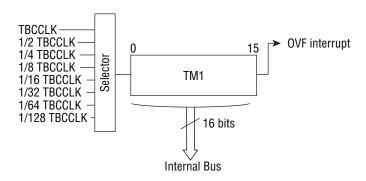

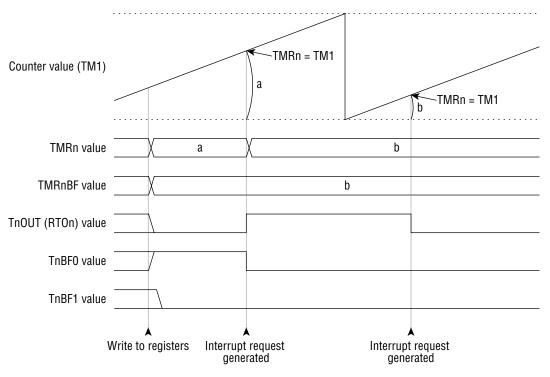

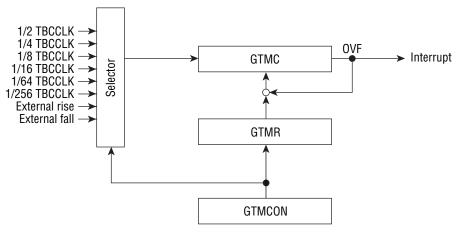

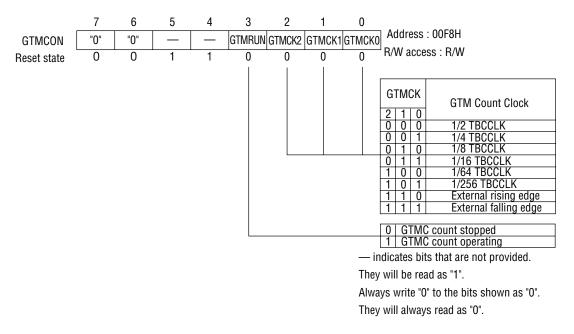

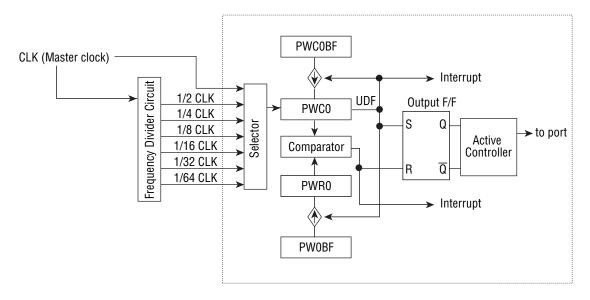

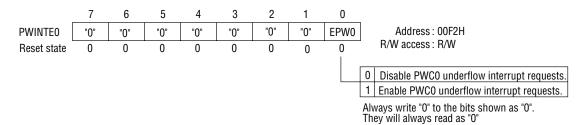

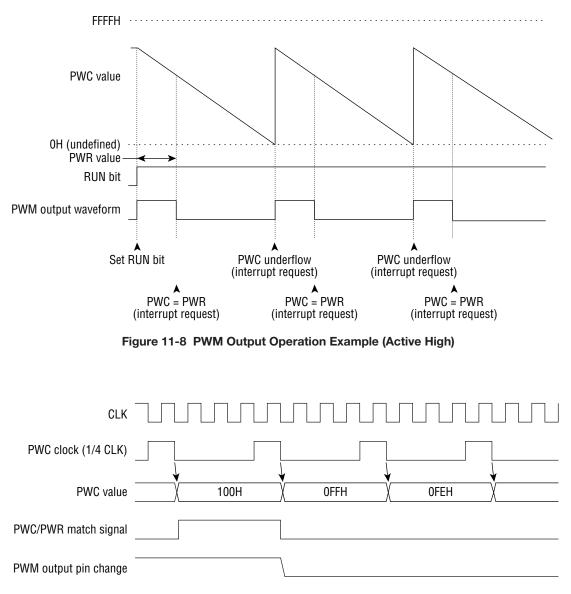

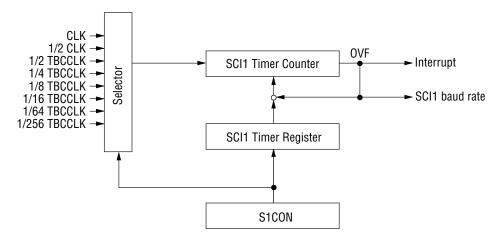

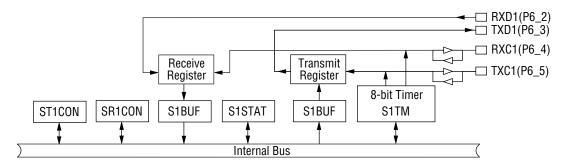

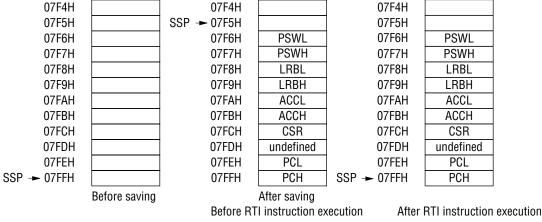

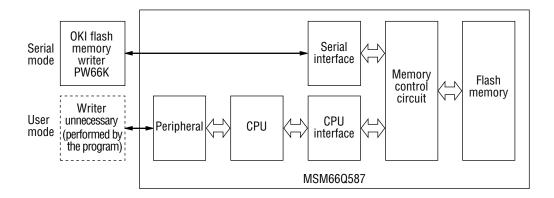

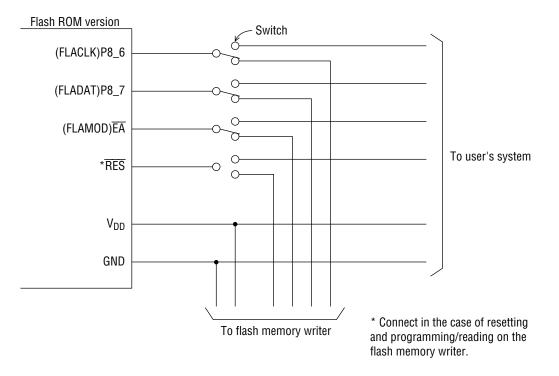

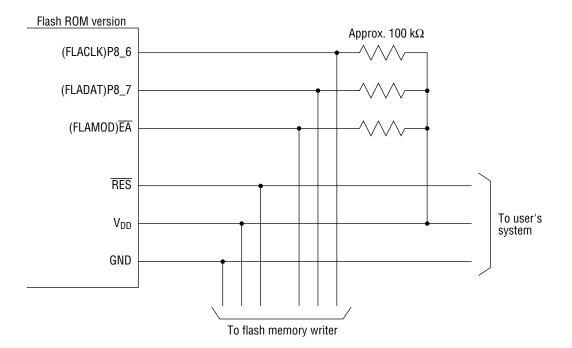

(4) System Stack Pointer (SSP)