# **OKI** Semiconductor MSM9225B

#### CAN (Controller Area Network) Controller

# **GENERAL DESCRIPTION**

The MSM9225B is a microcontroller peripheral LSI which conforms to the CAN protocol for high-speed LANs in automobiles.

# FEATURES

- Conforms to CAN protocol specification (Bosch, V2.0 part B/Active)

- Maximum of 1 Mbps bit rate

- Communication method:

- Transmission line is bi-directional, two-wire serial communication

- NRZ (Non-Return to Zero) system using bit stuff function

- Multi-master system

- Broadcast system

- Message boxes:

- Up to 16 message boxes can be used, and messages up to 8 bytes long can be transmitted or received for each message box.

- Number of received messages can be extended by group message function (up to 2 groups can be set)

- Overwrite flag is provided

- Priority control by identifier

- 2032 types in standard format,  $2032 \times 2^{18}$  types in extended format

- Microcontroller interface

- Corresponding to both parallel and serial interface

- Parallel interface: Separate address/data bus type (with address latch signal/no address latch signal) and multiplexed address/data bus type

- Serial interface: Synchronous communication type

#### • Three interrupt sources: Transmission/receive/error

- Error control:

- Bit error/stuff error/CRC error/form error/acknowledgment error detection functions

- Retransmission/error status monitoring function when error occurs

- Bit error flag/stuff error flag/CRC error flag/form error flag/acknowledge error flag are provided

- Communication control by remote data request function

- Sleep/Stop mode function

- Supply voltage: 5 V±10%

- Operating temperature: -40 to  $+125^{\circ}$ C

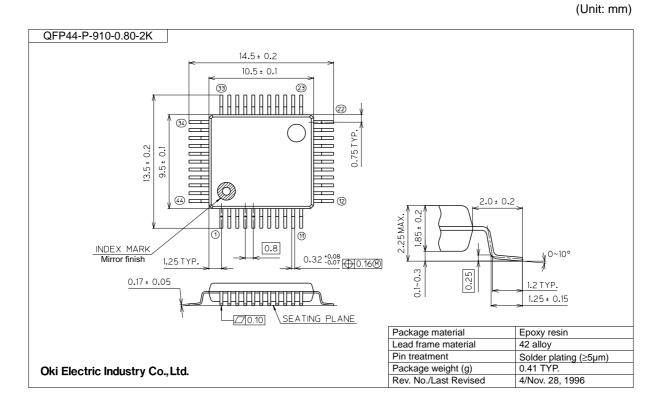

- Package: 44-pin plastic QFP (QFP44-P-910-0.80-2K) (Product name: MSM9225BGA-2K)

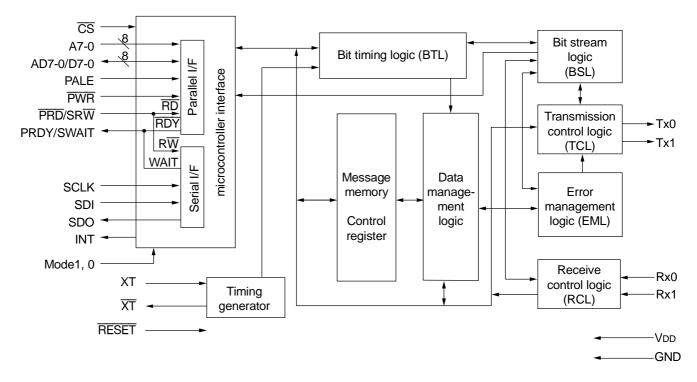

## **BLOCK DIAGRAM**

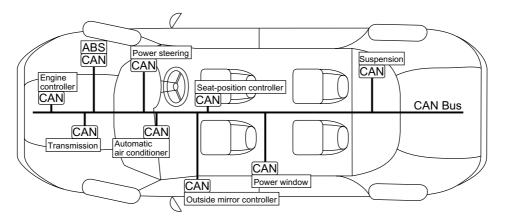

# **CONFIGURATION EXAMPLE**

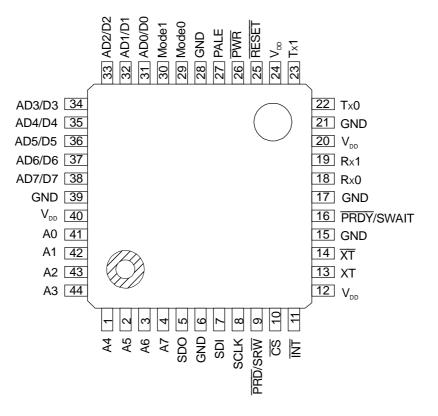

## **PIN CONFIGURATION**

44-Pin Plastic QFP (Top View)

#### MSM9225B

# PIN DESCRIPTIONS

| Symbol         | Pin        | Туре | Description                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|----------------|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| CS             | 10         | 1    | Chip select pin. When "L", PALE, $\overline{PWR}$ , $\overline{PRD}/SRW$ , SCLK and SDO pins (microcontroller interface pins) are valid.<br>When "H", these pins are invalid.                                                                                                                                                                        |  |  |  |  |

| A7-0           | 41-44, 1-4 | I    | Address bus pins (when using separate buses). If used with a multiplexed bus or if used in the serial mode, fix these pins at "H" or "L" levels.                                                                                                                                                                                                     |  |  |  |  |

| AD7-0/<br>D7-0 | 31-38      | I/O  | Multiplexed bus: Address/data pins (AD7-0)<br>Separate buses: Data pins (D7-0)<br>If used in the serial mode, fix these pins at a "L" levels.                                                                                                                                                                                                        |  |  |  |  |

| PWR            | 26         | I    | Write input pin if used in the parallel mode. Data is captured when this pin is at a "L" level.<br>If used in the serial mode, fix this pin at a "L" level.                                                                                                                                                                                          |  |  |  |  |

| PRD/<br>SRW    | 9          | I    | Parallel mode: Read signal pin (PRD)<br>When at a "L" level, data is output from the data pins.<br>Serial mode: Read/write signal pin (SRW)<br>When at a "H" level, data is output from the SDO pin.<br>When at a "L" level, the SDO pin is at high impedance, and data is<br>captured beginning with the second byte of data input from the SDI pin |  |  |  |  |

| PALE           | 27         | I    | Address latch signal pin<br>When at a "H" level, addresses are captured.<br>If used in the parallel mode and the address latch signal is unnecessary<br>or in the serial mode, fix this pin at a "H" or "L" level.                                                                                                                                   |  |  |  |  |

| SDI            | 7          | I    | Serial data input pin<br>Addresses (1st byte) and data (beginning from the 2nd byte) are input to<br>this pin, LSB first. If used in the parallel mode, fix this pin at a "H" or "L"<br>level.                                                                                                                                                       |  |  |  |  |

| SDO            | 5          | 0    | Serial data output pin<br>When the $\overline{CS}$ pin is at a "H" level, this pin is at high impedance. When<br>$\overline{CS}$ is at a "L" level, data is output from this pin, LSB first.<br>If used in the parallel mode, fix this pin at a "H" or "L" level.                                                                                    |  |  |  |  |

| SCLK           | 8          | I    | Shift clock input pin for serial data<br>At the rising edge of the shift clock, SDI pin data is captured. At the<br>falling edge, data is output from the SDO pin.                                                                                                                                                                                   |  |  |  |  |

| PRDY/<br>SWAIT | 16         | 0    | Ready output pin         When required by the MSM9225B, a signal may be output to extend the bus cycle until the internal access is completed.         Internal access in progress         After completion of access         Parallel mode (PRDY)         "L" level output                                                                          |  |  |  |  |

|                |            |      | Serial mode<br>(SWAIT) "H" level output "L" level output                                                                                                                                                                                                                                                                                             |  |  |  |  |

#### FEDL9225B-03

#### **OKI** Semiconductor

#### MSM9225B

|                 | 1                        |      |                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|-----------------|--------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Symbol          | Pin                      | Туре | Description                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Mode1, 0        | 29, 30                   | I    | Microcontroller interface select pins         Mode1       Mode0       Interface         0       0       Parallel       Separate       No address latch signal         0       1       mode       With address latch signal         1       0       Multiplexed buses         1       1       Serial mode |  |  |  |  |

| INT             | 11                       | 0    | Interrupt request output pin<br>When an interrupt request occurs, a "L" level is output. This pin<br>automatically outputs a "H" level after 32 Ts (T = 1/fosc).<br>Three types of interrupts share this pin: transmission complete, reception<br>complete, and error.                                   |  |  |  |  |

| RESET           | 25                       | I    | Reset pin<br>System is reset when this pin is at a "L" level.                                                                                                                                                                                                                                            |  |  |  |  |

| ХТ              | 13                       | I    | Clock pins. If internal oscillator is used, connect a crystal (ceramic                                                                                                                                                                                                                                   |  |  |  |  |

| XT              | 14                       | 0    | resonator).<br>If external clock is used, input clock via XT pin. The $\overline{\text{XT}}$ pin should be left open.                                                                                                                                                                                    |  |  |  |  |

| Rx0, Rx1        | 18, 19                   | Ι    | Receive input pin. Differential amplifier included.                                                                                                                                                                                                                                                      |  |  |  |  |

| Tx0, Tx1        | 22, 23                   | 0    | Transmission output pin                                                                                                                                                                                                                                                                                  |  |  |  |  |

| V <sub>DD</sub> | 12, 20, 24, 40           | _    | Power supply pin                                                                                                                                                                                                                                                                                         |  |  |  |  |

| GND             | 6, 15, 17, 21,<br>28, 39 | _    | GND pin                                                                                                                                                                                                                                                                                                  |  |  |  |  |

# ABSOLUTE MAXIMUM RATINGS

| Parameter             | Symbol           | Condition | Rating                       | Unit |

|-----------------------|------------------|-----------|------------------------------|------|

| Power Supply Voltage  | V <sub>DD</sub>  | Ta = 25°C | -0.3 to +7.0                 | V    |

| Input Voltage         | V                | —         | –0.3 to V <sub>DD</sub> +3.0 | V    |

| Output Voltage        | Vo               | _         | –0.3 to V <sub>DD</sub> +3.0 | V    |

| Power Dissipation     | P <sub>D</sub>   | Ta ≤ 25°C | 615                          | mW   |

| Operating Temperature | T <sub>OP</sub>  | —         | -40 to +125                  | °C   |

| Storage Temperature   | T <sub>stg</sub> | —         | -65 to +150                  | °C   |

# **RECOMMENDED OPERATING CONDITIONS**

| Parameter             | Symbol          | Condition          | Min. | Тур. | Max. | Unit |

|-----------------------|-----------------|--------------------|------|------|------|------|

| Power Supply Voltage  | V <sub>DD</sub> | $V_{DD} = AV_{DD}$ | 4.5  | 5.0  | 5.5  | V    |

| Operating Temperature | T <sub>OP</sub> | _                  | -40  | +25  | +125 | °C   |

# **ELECTRICAL CHARACTERISTICS**

#### **DC Characteristics**

|                        |                   |                          | $(V_{DD} = $                                                    | 4.5 to 5.5 V, <sup>-</sup>                            | Га = –40 to +        | -125°C) |

|------------------------|-------------------|--------------------------|-----------------------------------------------------------------|-------------------------------------------------------|----------------------|---------|

| Parameter              | Symbol            | Applicable pin           | Condition                                                       | Min.                                                  | Max.                 | Unit    |

| "H" Input Voltage      | V <sub>IH</sub>   | Applies to all inputs    | —                                                               | 0.8V <sub>DD</sub>                                    | V <sub>DD</sub> +0.3 | V       |

| "L" Input Voltage      | V                 | Applies to all inputs    | —                                                               | -0.3                                                  | +0.2 V <sub>DD</sub> | V       |

| "H" Input Current      | I <sub>IH1</sub>  | XT                       | V - V                                                           | 3                                                     | 25                   | μA      |

|                        | I <sub>IH2</sub>  | Other inputs             | $V_{I} = V_{DD} -1.0$ $V_{I} = 0V -25$ $-1.0$ $V_{I} = 0V -1.0$ | -1.0                                                  | +1.0                 | μA      |

| "I " Input Current     | $I_{IL1}$         | XT                       | $\lambda = 0 \lambda$                                           | -25                                                   | -3                   | μA      |

| "L" Input Current      | $I_{\parallel 2}$ | Other input              | $v_1 = 0 v$                                                     | -1.0                                                  | +1.0                 | μA      |

| "H" Output Voltage     | V <sub>OH1</sub>  | INT, PRDY/SWAIT          | I <sub>OH1</sub> = -80 μA                                       | $V_{DD}$ –1.0                                         | _                    | V       |

|                        | V <sub>OH2</sub>  | AD7-0/D7-0               | I <sub>OH2</sub> = -400 μA                                      | V <sub>DD</sub> -1.0                                  | —                    | V       |

| "L" Output Voltage     | V <sub>OL1</sub>  | INT, PRDY/SWAIT          | I <sub>OL1</sub> = 1.6 mA                                       | —                                                     | 0.4                  | V       |

|                        | V <sub>OL2</sub>  | AD7-0/D7-0               | I <sub>OL2</sub> = 3.2 mA                                       | —                                                     | 0.4                  | V       |

| Output Leakage Current | I <sub>IH1</sub>  | PRDY/SWAIT<br>AD7-0/D7-0 | $V_{I} = V_{DD}/0 V$                                            | -1.0                                                  | +1.0                 | μA      |

| Dynamic Supply Current | I <sub>DD</sub>   |                          | f <sub>OSC</sub> = 16 MHz,<br>No Load                           | _                                                     | 9                    | mA      |

| Static Supply Current  | 1                 | _                        | SLEEP Mode                                                      | _                                                     | 400                  | μA      |

|                        | DDS               | _                        | STOP Mode                                                       | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | 100                  | μA      |

#### **Rx0, Rx1** Characteristics

Differencial input mode

|   |            |        |       | · -   |           |         |

|---|------------|--------|-------|-------|-----------|---------|

| ( | $V_{DD} =$ | 4.5 to | 5.5 \ | /, Ia | = -40  to | +125°C) |

|                          |                 |                |                        |           |                    | /    |

|--------------------------|-----------------|----------------|------------------------|-----------|--------------------|------|

| Parameter                | Symbol          | Applicable pin | Condition              | Min.      | Max.               | Unit |

| 'dominant' Input Voltage | VRx0 (d)        | Rx0            | $VRx1 = 0.4 V_{DD}$    | -0.3      | VRx1 –0.4          | V    |

| 'recessive Input Voltage | VRx0 (r)        | Rx0            | to 0.6 $V_{DD}$        | VRx1 +0.4 | V <sub>DD</sub> +3 | V    |

| Input Leakage Current    | I <sub>LK</sub> | Rx0, Rx1       | $VR_{X1} = V_{DD}/0 V$ | -1        | +1                 | μA   |

# Tx0, Tx1 Characteristics

|                    |                 |                           | $(V_{DD} = 4.5 \text{ tc})$ | 5.5 V, Ta = −4 | 0 to +125°C) |

|--------------------|-----------------|---------------------------|-----------------------------|----------------|--------------|

| Parameter          | Symbol          | Condition                 | Min.                        | Max.           | Unit         |

| "H" Output Voltage | V <sub>OH</sub> | I <sub>он</sub> = –3.0 mA | V <sub>DD</sub> -0.4        |                | V            |

| "L" Output Voltage | V <sub>OL</sub> | I <sub>OL</sub> = 10.0 mA | _                           | 0.4            | V            |

#### MSM9225B

#### MSM9225B

#### **AC Characteristics**

Parallel mode

| Pa             | arameter                   | Symbol              | Condition | Min.             | Max.             | Unit |

|----------------|----------------------------|---------------------|-----------|------------------|------------------|------|

| ALE Address S  | Setup Time                 | t <sub>AS</sub>     | —         | 10               | _                | ns   |

| ALE Address H  | Hold Time                  | t <sub>AH</sub>     | —         | 10               | —                | ns   |

| PRD Output Da  | ita Delay Time             | t <sub>RDLY</sub>   | —         | _                | 60 <sup>*1</sup> | ns   |

| PRD Output Da  | ita Hold Time              | t <sub>RDH</sub>    | _         | 5                | —                | ns   |

| ALE "H" Level  |                            | t <sub>WALEH</sub>  |           | 16.5             | —                | ns   |

| Access Cycle   | When PRDY is not generated | t <sub>cyc</sub>    |           | 4T               | —                | ns   |

|                | When PRDY is generated     |                     |           | 7T               | —                | ns   |

| Address Hold   | Time from PRD              | t <sub>RAH</sub>    | _         | 0                | —                | ns   |

| ALE Delay Tim  | ne from PRD                | t <sub>HRA</sub>    | _         | 27               | —                | ns   |

| PRD "H" Level  | Width                      | t <sub>wrdh</sub>   | —         | 27               | —                | ns   |

| PRDY "L" Delay | / Time                     | t <sub>ARLDLY</sub> | —         | —                | 35               | ns   |

| PRDY "L" Level | Width                      | t <sub>wrdyl</sub>  | —         | 0                | 2.5T             | ns   |

| Data Output D  | elay Time from PRDY        | t <sub>ARDDLY</sub> | —         | —                | 35               | ns   |

| PWR Hold Time  | e from PRDY                | t <sub>ARWDLY</sub> | —         | 10               | _                | ns   |

| Input Data Set |                            | t <sub>wps</sub>    | —         | 30               | —                | ns   |

| nput Data Hol  |                            | t <sub>WDH</sub>    | —         | 4                | —                | ns   |

| PRD Delay Tim  | е                          | t <sub>RS</sub>     | —         | 10               | —                | ns   |

| PWR Delay Tin  | ne                         | t <sub>ws</sub>     | _         | 10               | —                | ns   |

| Address Hold   | Time from PWR              | t <sub>wan</sub>    | _         | 10               | —                | ns   |

| ALE Delay Tim  | ne from PWR                | t <sub>HWA</sub>    | —         | 27               | —                | ns   |

| PWR "H" Level  | Width                      | t <sub>wRH</sub>    | —         | 40               | —                | ns   |

| PWR "L" Level  | Width                      | t <sub>wRL</sub>    | _         | 20 <sup>*1</sup> | —                | ns   |

| CS Delay Time  | from PRD                   | t <sub>HRC</sub>    | —         | 0                | —                | ns   |

| CS Delay Time  | from PWR                   | t <sub>HWC</sub>    | _         | 0                |                  | ns   |

The values with \*1 indicate those when  $\overline{PRDY}$  is not generated. The values with \*1 when  $\overline{PRDY}$  is generated are defined by "Data Output Delay Time from  $\overline{PRDY}$ " t<sub>ARWDLY</sub> and " $\overline{PWR}$  Hold Time from  $\overline{PRDY}$ " t<sub>ARWDLY</sub>.

#### FEDL9225B-03

#### MSM9225B

Serial mode

| Serial mode                |                     | (V <sub>DD</sub> = 4.5 to 5. | 5 V, Ta = -40 te | o +125°C, f <sub>os</sub> | <sub>sc</sub> = 16 MH |

|----------------------------|---------------------|------------------------------|------------------|---------------------------|-----------------------|

| Parameter                  | Symbol              | Condition                    | Min.             | Max.                      | Unit                  |

| CS Setup Time              | t <sub>cs</sub>     | —                            | 10               | _                         | ns                    |

| CS Hold Time               | t <sub>cH</sub>     | —                            | 8T               | _                         | ns                    |

| SCLK Cycle                 | t <sub>CP</sub>     | —                            | 167              | _                         | ns                    |

| SCLK Pulse Width           | t <sub>cw</sub>     | —                            | 83               | _                         | ns                    |

| SDI Setup Time             | t <sub>DS</sub>     | —                            | 30               | _                         | ns                    |

| SDI Hold Time              | t <sub>DH</sub>     | —                            | 5                | _                         | ns                    |

| SDO Output Enable Time     | t <sub>CSODLY</sub> | —                            | _                | 30                        | ns                    |

| SDO Output Disable Time    | t <sub>CSZDLY</sub> | —                            | —                | 30                        | ns                    |

| SDO Output Delay Time      | t <sub>PD</sub>     | —                            | —                | 30                        | ns                    |

| SRW Setup Time             | t <sub>RS</sub>     | —                            | 10               | _                         | ns                    |

| $SR\overline{W}$ Hold Time | t <sub>RH</sub>     | _                            | 0                | _                         | ns                    |

| SWAIT Output Delay Time    | t <sub>SRDLY</sub>  | _                            | —                | 2T                        | ns                    |

| SWAIT "H" Level Width      | t <sub>WRDY</sub>   | _                            | —                | 6T                        | ns                    |

| Byte Delay                 | t <sub>WAIT</sub>   | _                            | 8T               |                           | ns                    |

|                            |                     |                              |                  |                           | T – 1/f               |

$T=1/f_{\rm OSC}$

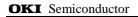

Other timing characteristics

$(V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, \text{ Ta} = -40 \text{ to } +125^{\circ}\text{C})$

|                             |                    | (         |      | - ,  |       |

|-----------------------------|--------------------|-----------|------|------|-------|

| Parameter                   | Symbol             | Condition | Min. | Max. | Unit  |

| System Clock Cycle          | t <sub>clkcy</sub> | —         | 62   | —    | ns    |

| RESET "H" Level Input Width | t <sub>wrsth</sub> | —         | 5    | —    | μs    |

| RESET "L" Level Input Width | t <sub>wrstl</sub> | —         | 5    | —    | μs    |

| INT "L" Level Output Width  | t <sub>WINTL</sub> | _         | 32T  | _    | ns    |

|                             |                    |           |      |      | T 4/4 |

$T=1/f_{\rm OSC}$

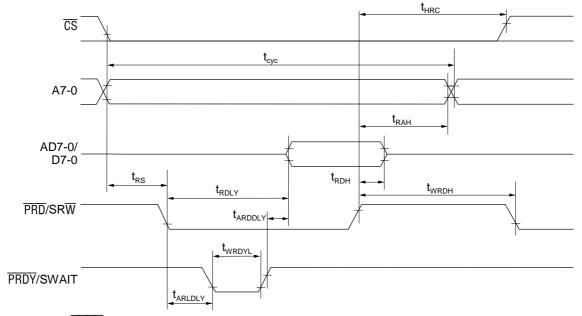

#### **TIMING DIAGRAMS**

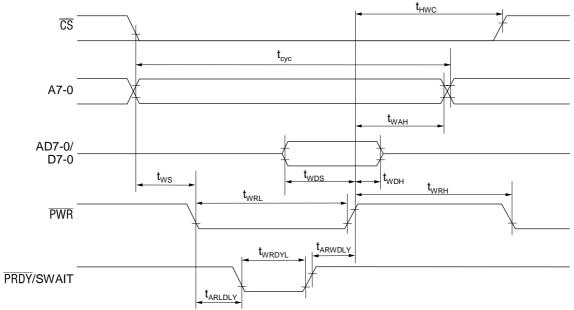

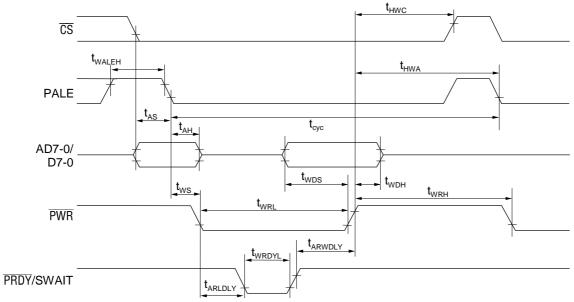

#### Separate Bus Mode

Read access timing

Note: The PRDY signal may be output depending on the internal state of the MSM9225B.

Write access timing

Note: The PRDY signal may be output depending on the internal state of the MSM9225B.

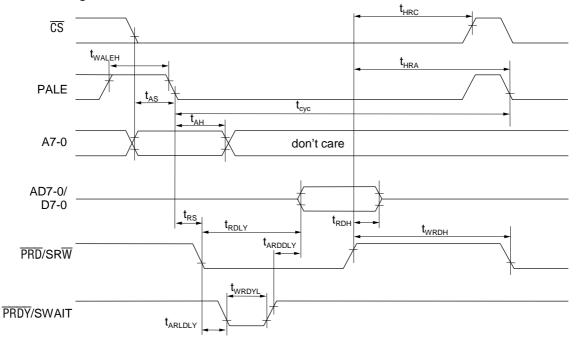

#### Separate Bus/Address Latch Mode

Read access timing

Note: The PRDY signal may be output depending on the internal state of the MSM9225B.

Write access timing

Note: The PRDY signal may be output depending on the internal state of the MSM9225B.

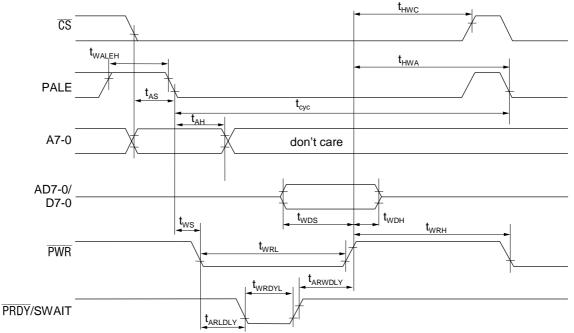

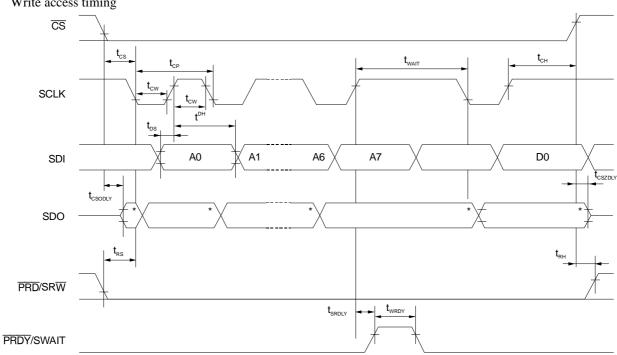

# **Multiplexed Bus Mode**

Read access timing

# Note: The PRDY signal may be output depending on the internal state of the MSM9225B.

Write access timing

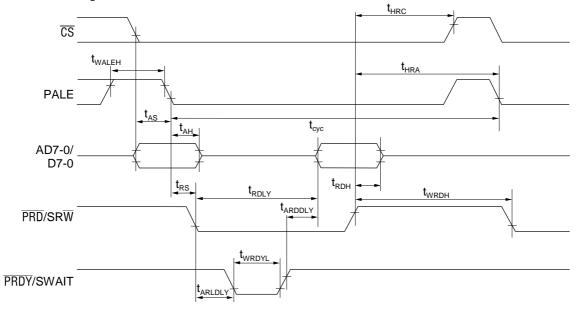

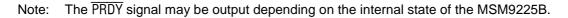

#### Serial Mode

#### The SWAIT signal will be output during the interval between address and data transfers. Note:

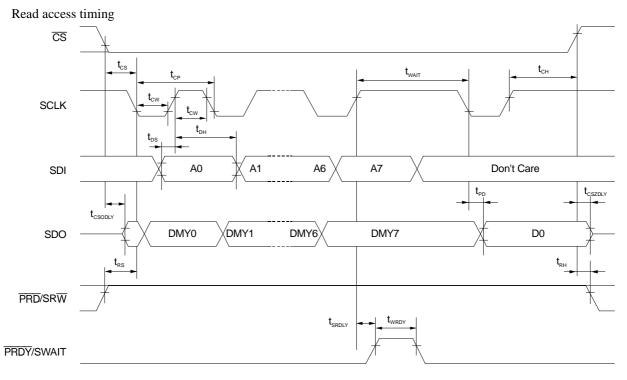

Write access timing

The SWAIT signal will be output during the interval between address and data transfers. Note: \* : don't care

# PACKAGE DIMENSIONS

Notes for Mounting the Surface Mount Type Package

The surface mount type packages are very susceptible to heat in reflow mounting and humidity absorbed in storage. Therefore, before you perform reflow mounting, contact Oki's responsible sales person on the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

#### <u>NOTICE</u>

- 1. The information contained herein can change without notice owing to product and/or technical improvements. Before using the product, please make sure that the information being referred to is up-to-date.

- 2. The outline of action and examples for application circuits described herein have been chosen as an explanation for the standard action and performance of the product. When planning to use the product, please ensure that the external conditions are reflected in the actual circuit, assembly, and program designs.

- 3. When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating temperature.

- 4. Oki assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified operating range.

- 5. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of the product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

- 6. The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g., office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not authorized for use in any system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or application may result in the loss or damage of property, or death or injury to humans. Such applications include, but are not limited to, traffic and automotive equipment, safety devices, aerospace equipment, nuclear power control, medical equipment, and life-support systems.

- 7. Certain products in this document may need government approval before they can be exported to particular countries. The purchaser assumes the responsibility of determining the legality of export of these products and will take appropriate and necessary steps at their own expense for these.

- 8. No part of the contents contained herein may be reprinted or reproduced without our prior permission.

Copyright 2001 Oki Electric Industry Co., Ltd.