# **OKI**

# nX-8/500S Core

Instruction Manual

**CMOS 16-bit microcontroller**

**SECOND EDITION**

ISSUE DATE: JUNE, 1999

## **NOTICE**

- 1. The information contained herein can change without notice owing to product and/or technical improvements. Please make sure before using the product that the information you are referring to is up-to-date.

- 2. The outline of action and examples of application circuits described herein have been chosen as an explanation of the standard action and performance of the product. When you actually plan to use the product, please ensure that the outside conditions are reflected in the actual circuit and assembly designs.

- 3. NO RESPONSIBILITY IS ASSUMED BY US FOR ANY CON-SEQUENCE RESULTING FROM ANY WRONG OR IMPROPER USE OR OPERATION, ETC. OF THE PRODUCT.

- 4. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of the product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

- 5. The products described herein fall within the category of strategical goods, etc. under the Foreign Exchange and Foreign Trade Control Law. Accordingly, before exporting the product you are required under the Law to file the application for the export license by your local Government.

- 6. No part of the contents contained herein may be reprinted or reproduced without our prior permission.

Copyright 1999 OKI ELECTRIC INDUSTRY CO., LTD.

## **Table of Contents**

## Chapter 0. Preface

## Chapter 1. Architecture

| 1-1. Overview                                         |  |

|-------------------------------------------------------|--|

| 1-1-1. Overview Of OLMS-66K Series And nX-8/500S Core |  |

| 1-2. CPU Resources And Programming Model              |  |

| 1-2-1. Register                                       |  |

| 1-2-1-1. Accumulator (A)                              |  |

| 1-2-1-2. Control Register (CR)                        |  |

| 1-2-1-2-1. Program Status Word (PSW)                  |  |

| 1-2-1-2-1. How Instructions Change PSW Flags          |  |

| 1-2-1-2-2. Program Counter (PC)                       |  |

| 1-2-1-2-3. Local Register Base (LRB)                  |  |

| 1-2-1-2-4. System Stack Pointer (SSP)                 |  |

| 1-2-1-3. Pointing Registers (PR)                      |  |

| 1-2-1-3-1. Addressing With Pointing Registers         |  |

| 1-2-1-4. Local Registers (ER)                         |  |

| 1-2-1-4-1. Addressing With Local Registers            |  |

| 1-2-1-5. Segment Registers                            |  |

| 1-2-1-5-1. Code Segment Register (CSR)                |  |

| 1-2-1-5-2. Table Segment Register (TSR)               |  |

| 1-2-1-5-3. Data Segment Register (DSR)                |  |

| 1-2-1-6. ROM Window Control Register (ROMWIN)         |  |

| 1-2-1-7. Special Function Registers (SFR)             |  |

| 1-2-2. Memory Space                                   |  |

| 1-2-2-1. Program Memory Space                         |  |

| 1-2-2-1-1. Vector Table Area                          |  |

| 1-2-2-1-1. Reset Vector Area                          |  |

| 1-2-2-1-1-2. Interrupt Vector Area                    |  |

| 1-2-2-1-1-3. VCAL Table Area                          |  |

| 1-2-2-1-1-4. Vector Table Coding Syntax               |  |

| 1-2-2-1-2. ACAL Area                                  |  |

| 1-2-2-1-3. ROM Window Area In Program Memory Space    |  |

| 1-2-2-1-4. Internal And External Program Memory Areas |  |

nX-8/500S Instruction Manual

| 1-2-2-2. Data Memory Space                                     |   |

|----------------------------------------------------------------|---|

| 1-2-2-1. SFR Area                                              |   |

| 1-2-2-2. Extended SFR Area                                     | 2 |

| 1-2-2-3. Fixed Page                                            |   |

| 1-2-2-3-1. Area Available For Pointing Registers               |   |

| 1-2-2-3-2. Fixed Page SBA Area                                 |   |

| 1-2-2-4. Current Page                                          |   |

| 1-2-2-4-1. Current Page SBA Area                               |   |

| 1-2-2-5. Area Available For Local Registers                    |   |

| 1-2-2-6. ROM Window Area In Data Memory Space                  |   |

| 1-2-2-7. Common Area                                           |   |

| 1-2-2-8. Other Memory                                          |   |

| 1-2-2-8-1. EEPROM Area                                         |   |

| 1-2-2-8-2. Dual Port RAM Area                                  |   |

| 1-2-2-9. Internal And External Data Memory Areas               |   |

| ·                                                              |   |

| 1-3. Data Types                                                |   |

|                                                                |   |

| 1-4. Address Allocation                                        | ; |

|                                                                |   |

| 1-5. Word Boundaries                                           | ; |

|                                                                |   |

| 1-6. ROM Window Function                                       | , |

|                                                                |   |

| 1-7. Memory Models                                             |   |

|                                                                |   |

| 1-8. Data Descriptor (DD)                                      |   |

| 1-8-1. Description And Use Of DD                               |   |

| 1-8-2. Instructions That Change DD                             |   |

| 1-8-2-1. Instructions That Change DD As Part Of Their Function |   |

| 1-8-2-2. Other Instructions That Change DD                     |   |

| 1-8-3. Instruction Affected By DD                              |   |

| 1-8-4. Pre-Fetched Instructions And DD                         |   |

|                                                                |   |

| 1-9. Changing The Stack                                        |   |

|                                                                |   |

| 1-10. Instruction Code Format                                  |   |

| 1-10-1. Native Instructions And Composite Instructions         |   |

| 1-11. Microcontrollers That Use The nX-8/500S Core             |   |

| 1-11. WILCIOCOTUTOTIETS THAT USE THE HA-0/3003 COTE            |   |

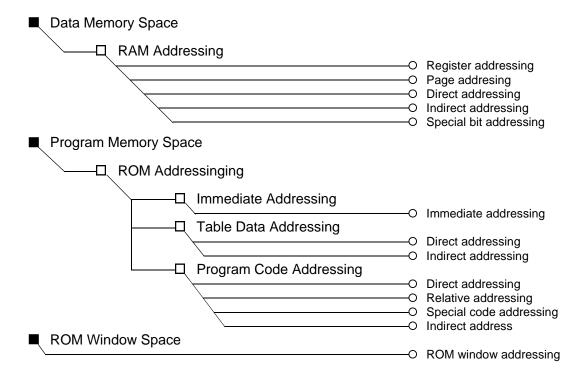

## Chapter 2. Addressing Modes

| 2. RAM Addressing                               |                                                         |

|-------------------------------------------------|---------------------------------------------------------|

| Α                                               | Accumulator Addressing                                  |

| PSW,LRB,SSP                                     | Control Register Addressing                             |

| X1,X2,DP,USP                                    | Pointing Register Addressing                            |

| ER <i>n</i> ,R <i>n</i>                         | Local Register Addressing                               |

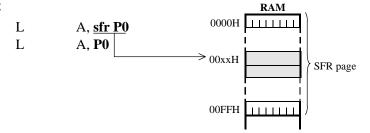

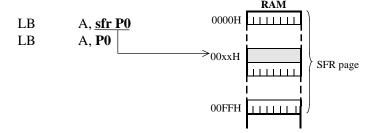

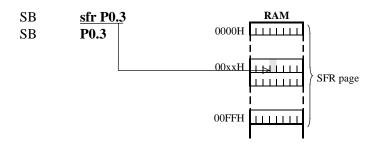

| sfr <i>Dadr</i>                                 | SFR Page Addressing                                     |

| fix <i>Dadr</i>                                 | Fixed Page Addressing                                   |

| off <i>Dadr</i>                                 | Current Page Addressing                                 |

| dir <i>Dadr</i>                                 | Direct Data Addressing                                  |

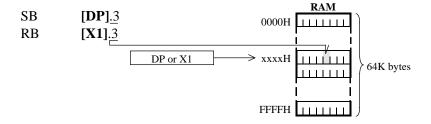

| [DP],[X1]                                       | DP/X1 Indirect Addressing                               |

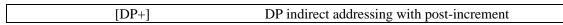

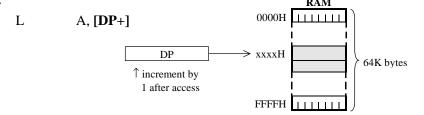

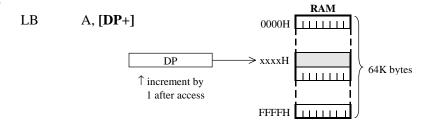

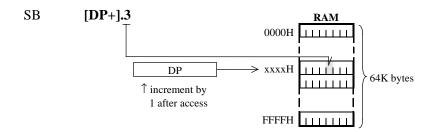

| [DP+]                                           | DP Indirect Addressing With Post-Increment              |

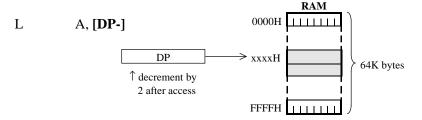

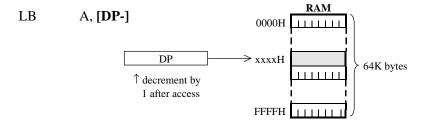

| [DP-]                                           | DP Indirect Addressing With Post-Decrement              |

| n <i>7</i> [DP],n <i>7</i> [USP]                | DP/USP With Indirect Addressing With 7-Bit Displacement |

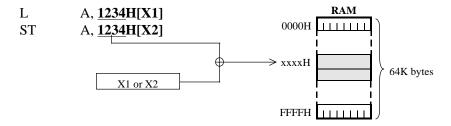

| D <i>16</i> [X1],D <i>16</i> [X2]               | X1/X2 Indirect Addressing With 16-Bit Base              |

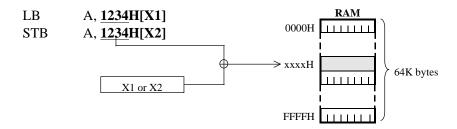

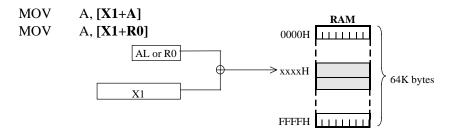

| [X1+A],[X1+R0]                                  | X1 Indirect Addressing With 8-Bit Register Displacement |

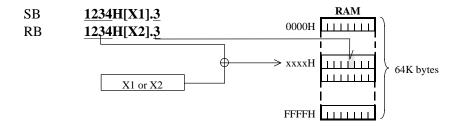

| sbafix <i>Badr</i>                              | Fixed Page SBA Area Addressing                          |

| sbaoff <i>Badr</i>                              | Current Page SBA Area Addressing                        |

|                                                 |                                                         |

| 3. ROM Addressing -                             |                                                         |

| 2-3-1. Immediate Add                            | dressing                                                |

| 2-3-2. Table Data Ad                            | dressing                                                |

| 2-3-3. Program Code                             | Addressing                                              |

|                                                 | Word/Byte Immediate Addressing                          |

| #N16,#N8                                        | 1101 a, 2) to a and 200g                                |

| #N16,#N8<br>Tadr                                | •                                                       |

|                                                 | Direct Table Addressing                                 |

| Tadr                                            | Direct Table Addressing                                 |

| <i>Tadr</i><br>[**]                             | Direct Table Addressing                                 |

| <i>Tadr</i><br>[**]<br><i>T16</i> [**]          | Direct Table Addressing                                 |

| Tadr<br>[**]<br>T16[**]<br>Cadr                 | Direct Table Addressing                                 |

| Tadr<br>[**]<br>T16[**]<br>Cadr<br>Fadr         | Direct Table Addressing                                 |

| Tadr<br>[**]<br>T16[**]<br>Cadr<br>Fadr<br>radr | Direct Table Addressing                                 |

## Chapter 3. Instruction Details

|   | nX-8/500S Instruction Set Listed By Function |                |                                        |  |  |  |  |

|---|----------------------------------------------|----------------|----------------------------------------|--|--|--|--|

|   | Symbols l                                    | Jsed In Opera  | and Expressions Of Instructions        |  |  |  |  |

|   | Symbols l                                    | Jsed In Instru | ction Code Expressions Of Instructions |  |  |  |  |

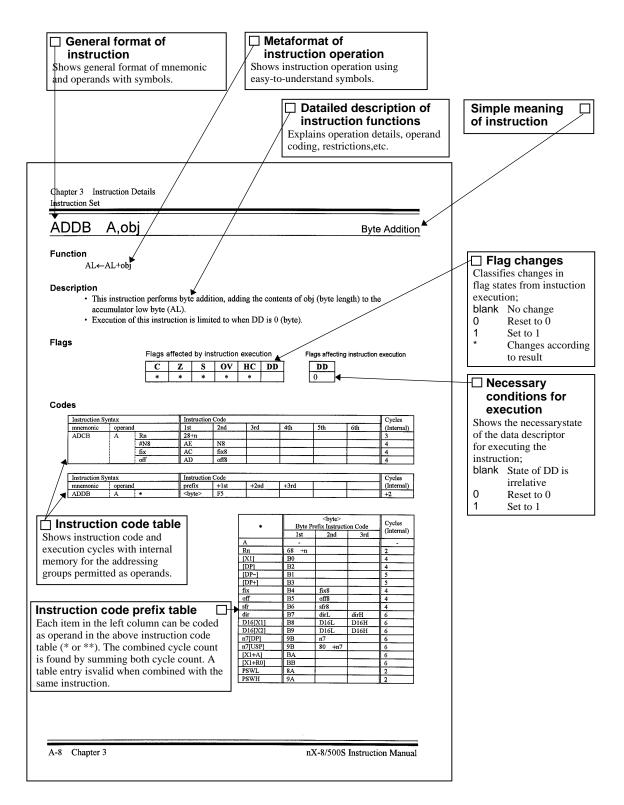

|   | General E                                    | xample for In  | struction Details                      |  |  |  |  |

|   |                                              |                |                                        |  |  |  |  |

| Α |                                              |                |                                        |  |  |  |  |

|   | ACAL                                         | Cadr11         | Special Area Call                      |  |  |  |  |

|   | ADC                                          | A,obj          | Word Addition With Carry               |  |  |  |  |

|   | ADC                                          | obj1,obj2      | Word Addition With Carry               |  |  |  |  |

|   | ADCB                                         | A,obj          | Byte Addition With Carry               |  |  |  |  |

|   | ADCB                                         | obj1,obj2      | Byte Addition With Carry               |  |  |  |  |

|   | ADD                                          | A,obj          | Word Addition                          |  |  |  |  |

|   | ADD                                          | obj1,obj2      | Word Addition                          |  |  |  |  |

|   | ADDB                                         | A,obj          | Byte Addition                          |  |  |  |  |

|   | ADDB                                         | obj1,obj2      | Byte Addition                          |  |  |  |  |

|   | AND                                          | A,obj          | Word Logical AND A                     |  |  |  |  |

|   | AND                                          | obj1,obj2      | Word Logical AND A                     |  |  |  |  |

|   | ANDB                                         | A,obj          | Byte Logical AND A                     |  |  |  |  |

|   | ANDB                                         | obj1,obj2      | Byte Logical AND A                     |  |  |  |  |

| В |                                              | • • •          | , ,                                    |  |  |  |  |

|   | BAND                                         | C,obj.bit      | Bit Logical AND                        |  |  |  |  |

|   | BANDN                                        | C,obj.bit      | Bit Complement and Bit Logical AND     |  |  |  |  |

|   | BOR                                          | C,obj.bit      | Bit Logical OR                         |  |  |  |  |

|   | BORN                                         | C,obj.bit      | Bit Complement and Bit Logical OR      |  |  |  |  |

|   | BRK                                          | -, <b>,</b>    | Break (System Reset)                   |  |  |  |  |

|   | BXOR                                         | C,obj.bit      | Bit Logical Exclusive OR               |  |  |  |  |

| С | 27.0                                         | C, C.C, I.C.I. |                                        |  |  |  |  |

|   | CAL                                          | Cadr           | 64K-Byte Space (Within Current         |  |  |  |  |

|   | <b>♥</b> / .=                                | 0 0.0.         | Physical Code Segment) Direct Call     |  |  |  |  |

|   | CAL                                          | [obj]          | 64K-Byte Space (Within Current         |  |  |  |  |

|   | 0, 12                                        | [00]           | Physical Code Segment) Indirect Call   |  |  |  |  |

|   | CLR                                          | Α              | Word Clear                             |  |  |  |  |

|   | CLR                                          | obj            | Word Clear                             |  |  |  |  |

|   | CLRB                                         | A              | Byte Clear                             |  |  |  |  |

|   | CLRB                                         | obj            | Byte Clear                             |  |  |  |  |

|   | CMP                                          | A,obj          | Word Comparison                        |  |  |  |  |

|   | CMP                                          | obj1,obj2      | Word Comparison                        |  |  |  |  |

|   | CIVIE                                        | שןטט, ו ןטט    | vvoiu Companson (                      |  |  |  |  |

|   | СМРВ         | A,obj                 | Byte Comparison                                           | <i>C-9</i>   |

|---|--------------|-----------------------|-----------------------------------------------------------|--------------|

|   | CMPB         | obj1,obj2             | •                                                         | C-10         |

|   | CMPC         | A,[obj]               | , ,                                                       | C-10<br>C-11 |

|   | CMPC         | A,[00]]<br>A,T16[obj] |                                                           | C-11<br>C-12 |

|   | CMPC         | A,TTO[OD]]<br>A,Tadr  | ,                                                         | C-12<br>C-13 |

|   | CMPCB        |                       | . ,                                                       | C-13<br>C-14 |

|   | CMPCB        | A,[obj]               | ,                                                         | C-14<br>C-15 |

|   |              | A,T16[obj]            | ,                                                         |              |

|   | CMPCB<br>CPL | A,Tadr                |                                                           | C-16         |

| D | CPL          | С                     | Complement Carry                                          | C-17         |

| _ | DEC          | Α                     | Word Decrement                                            | D-1          |

|   | DEC          | obj                   | Word Decrement                                            | D-2          |

|   | DECB         | Α                     | Byte Decrement                                            | D-3          |

|   | DECB         | obj                   | Byte Decrement                                            | D-4          |

|   | DI           |                       | Disable Interrupts                                        | D-5          |

|   | DIV          | obj                   | Word Division                                             | D-6          |

|   | DIVB         | obj                   | Byte Division                                             | D-7          |

|   | DIVQ         | obj                   | Word Quick Division                                       | D-8          |

|   | DJNZ         | obj,radr              | Loop                                                      | D-9          |

| Е |              | -                     |                                                           |              |

|   | El           | Enable Inte           | rrupts                                                    | E-1          |

|   | EXTND        | Byte to Wor           | d Sign Extend                                             | E-2          |

| F |              |                       |                                                           |              |

|   | FCAL         | Fadr                  | 24-Bit Space (16M Bytes: Entire Program Area) Direct Call | F-1          |

|   | FILL         | Α                     | Word Fill                                                 | F-2          |

|   | FILL         | obj                   | Word Fill                                                 | F-3          |

|   | FILLB        | Α                     | Byte Fill                                                 | F-4          |

|   | FILLB        | obj                   | Byte Fill                                                 | F-5          |

|   | FJ           | Fadr                  | 24-Bit Space (16M Bytes: Entire Program Area) Direct Jump | F-6          |

|   | FRT          |                       | Return From Far Subroutine                                | F-7          |

| I |              |                       |                                                           |              |

|   | INC          | Α                     | Word Increment                                            | I-1          |

|   | INC          | obj                   | Word Increment                                            | I-2          |

|   | INCB         | Α                     | Byte Increment                                            | <i>I-3</i>   |

|   | INCB         | obi                   | Byte Increment                                            | 1-4          |

| J       |       |                  |                                                |

|---------|-------|------------------|------------------------------------------------|

|         | J     | Cadr             | 64K-Byte Space (Within Current                 |

|         |       |                  | Physical Code Segment) Direct Jump             |

|         | J     | [obj]            | 64K-Byte Space (Within Current                 |

|         |       |                  | Physical Code Segment) Indirect Jump           |

|         | JBR   | obj.bit,radr     | Bit Test and Jump                              |

|         | JBRS  | obj.bit,radr     | Bit Test and Jump (With Bit Set)               |

|         | JBS   | obj.bit,radr     | Bit Test and Jump                              |

|         | JBSR  | obj.bit,radr     | Bit Test and Jump (With Bit Reset)             |

|         | Jcond | radr             | Conditional Jump J-                            |

|         | JRNZ  | DP,radr          | Loop <i>J</i> -                                |

| L       |       |                  |                                                |

|         | L     | A,obj            | Word Load L                                    |

|         | LB    | A,obj            | Byte Load L                                    |

|         | LC    | A,[obj]          | Word ROM Load (Indirect) L                     |

|         | LC    | A,T16[obj]       | Word ROM Load (Indirect With 16-Bit Base)      |

|         | LC    | A,Tadr           | Word ROM Load (Direct) L                       |

|         | LCB   | A,[obj]          | Byte ROM Load (Indirect) L                     |

|         | LCB   | A,T16[obj]       | Byte ROM Load (Indirect With 16-Bit Base)      |

|         | LCB   | A,Tadr           | Byte ROM Load (Direct) L                       |

| М       |       | •                |                                                |

|         | MAC   |                  | Multiply-Addition Calculation /                |

|         | MB    | C, obj.bit       | Move Bit //                                    |

|         | MB    | obj.bit ,C       | Move Bit //                                    |

|         | MBR   | C, obj           | Move Bit (Register Indirect Bit Specification) |

|         | MBR   | obj, C           | Move Bit (Register Indirect Bit Specification) |

|         | MOV   | obj1, obj2       | Word Move <i>N</i>                             |

|         | MOVB  | obj1, obj2       | Byte Move //                                   |

|         | MUL   | obj              | Word Multiplication <i>M</i> -                 |

|         | MULB  | obj              | Byte Multiplication M-                         |

| N       |       | 3.D <sub>j</sub> | 2,10 maniphoduon                               |

| . •     | NEG   | Α                | Word Negate Sign /                             |

|         | NEGB  | A                | Byte Negate Sign /                             |

|         | NOP   |                  | No Operation                                   |

| $\circ$ | NOF   |                  | No Operation                                   |

| 0       | ΩP    | Λ chi            | Word Logical OR                                |

|         | OR    | A, obj           | vvoid Logical Oil                              |

|         | OR    | obj1, obj2       | vvoid Logical Oit                              |

|         | ORB   | A, obj           | Byte Logical OR (                              |

|         | ORB   | obi1. obi2       | Byte Logical OR (                              |

| Р | DODG  |               | Dec Off Contain Otable                          |

|---|-------|---------------|-------------------------------------------------|

|   | POPS  | • –           | Pop Off System Stack                            |

| _ | PUSHS | register_list | Push On System Stack F                          |

| R | DD    | ahi hit       | Deart Dit (Dit Dearties Direct Consideration)   |

|   | RB    | obj.bit       | Reset Bit (Bit Position Direct Specification) R |

|   | RBR   | obj           | Reset Bit (Register Indirect Bit Specification) |

|   | RC    |               | Reset Carry R                                   |

|   | RDD   |               | Reset DD                                        |

|   | ROL   | A             | Word Left Rotate (With Carry)                   |

|   | ROL   | obj           | Word Left Rotate (With Carry) R                 |

|   | ROLB  | Α             | Byte Left Rotate (With Carry)                   |

|   | ROLB  | obj           | Byte Left Rotate (With Carry) R                 |

|   | ROR   | Α             | Word Right Rotate (With Carry) R                |

|   | ROR   | obj           | Word Right Rotate (With Carry) R-               |

|   | RORB  | Α             | Byte Right Rotate (With Carry) R-               |

|   | RORB  | obj           | Byte Right Rotate (With Carry) R-               |

|   | RT    |               | Return From Subroutine R-                       |

|   | RTI   |               | Return From Interrupt R-                        |

| S |       |               |                                                 |

|   | SB    | obj.bit       | Set Bit (Bit Position Direct Specification) S   |

|   | SBC   | A, obj        | Word Subtraction With Carry S                   |

|   | SBC   | obj1, obj2    | Word Subtraction With Carry                     |

|   | SBCB  | A, obj        | Byte Subtraction With Carry                     |

|   | SBCB  | obj1, obj2    | Byte Subtraction With Carry                     |

|   | SBR   | obj           | Set Bit (Register Indirect Bit Specification)   |

|   | SC    | -             | Set Carry                                       |

|   | SCAL  | Cadr          | 64K-Byte Space (Within Current                  |

|   |       |               | Physical Code Segment) Direct Call              |

|   | SDD          |            | Set DD                                         | S-9  |

|---|--------------|------------|------------------------------------------------|------|

|   | SJ           | radr       | Short Jump                                     | S-10 |

|   | SLL          | Α          | Word Left Shift (With Carry)                   | S-11 |

|   | SLL          | obj        | Word Left Shift (With Carry)                   | S-12 |

|   | SLLB         | A          | Byte Left Shift (With Carry)                   | S-13 |

|   | SLLB         | obj        | Byte Left Shift (With Carry)                   | S-14 |

|   | SQR          | A          | Word Square                                    | S-15 |

|   | SQRB         | Α          | Byte Square                                    | S-16 |

|   | SRA          | Α          | Word Arithmetic Right Shift (With Carry)       | S-17 |

|   | SRA          | obj        | Word Arithmetic Right Shift (With Carry)       | S-18 |

|   | SRAB         | A          | Byte Arithmetic Right Shift (With Carry)       | S-19 |

|   | SRAB         | obj        | Byte Arithmetic Right Shift (With Carry)       | S-20 |

|   | SRL          | A          | Word Right Shift (With Carry)                  | S-21 |

|   | SRL          |            | objWord Right Shift (With Carry)               | S-22 |

|   | SRLB         | Α          | Byte Right Shift (With Carry)                  | S-23 |

|   | SRLB         | obj        | Byte Right Shift (With Carry)                  | S-24 |

|   | ST           | A,obj      | Word Store                                     | S-25 |

|   | STB          | A,obj      | Byte Store                                     | S-26 |

|   | SUB          | A, obj     | Word Subtraction                               | S-27 |

|   | SUB          | obj1, obj2 | Word Subtraction                               | S-28 |

|   | SUBB         | A,obj      | Byte Subtraction                               | S-29 |

|   | SUBB         | obj1, obj2 | Byte Subtraction                               | S-30 |

|   | SWAP         |            | High/Low Byte Swap                             | S-31 |

| Т |              |            |                                                |      |

|   | TBR          | obj        | Test Bit (Register Indirect Bit Specification) | T-1  |

|   | TJNZ         | A, radr    | Word Test & Jump (Jump If Non-Zero)            | T-2  |

|   | TJNZ         | obj, radr  | Word Test & Jump (Jump If Non-Zero)            | T-3  |

|   | TJNZB        | A, radr    | Byte Test & Jump (Jump If Non-Zero)            | T-4  |

|   | TJNZB        | obj, radr  | Byte Test & Jump (Jump If Non-Zero)            | T-5  |

|   | TJZ          | A, radr    | Word Test & Jump (Jump If Zero)                | T-6  |

|   | TJZ          | obj, radr  | Word Test & Jump (Jump If Zero)                | T-7  |

|   | TJZB         | A, radr    | Byte Test & Jump (Jump If Zero)                | T-8  |

|   | TJZB         | obj, radr  | Byte Test & Jump (Jump If Zero)                | T-9  |

| V |              |            |                                                |      |

|   | $VC\Delta I$ | \/adr      | Vector Call                                    | 1/_1 |

| Χ |       |            |                           |         |

|---|-------|------------|---------------------------|---------|

|   | XCHG  | A, obj     | Word Exchange             | <br>X-1 |

|   | XCHGB | A, obj     | Byte Exchange             | <br>X-2 |

|   | XOR   | A, obj     | Word Logical Exclusive OR | <br>X-3 |

|   | XOR   | obj1, obj2 | Word Logical Exclusive OR | <br>X-4 |

|   | XORB  | A, obj     | Byte Logical Exclusive OR | <br>X-5 |

|   | XORB  | obi1, obi2 | Byte Logical Exclusive OR | <br>X-6 |

## Chapter 0. Preface

This chapter explains the configuration and usage of this manual.

## **Preface**

This manual describes the instruction set of the nX-8/500S core. The nX-8/500S core is used as the CPU core of Oki Electric's original CMOS 8/16-bit single-chip microcontrollers. As one of the OLMS-66K Series cores, the nX-8/500S core is higher end than nX-8/200 and nX-8/400. The first device to use the nX-8/500S core is the MSM66556/589.

The explanations in this manual presume the basic architecture of the nX-8/500S core. The basic architecture incorporates the maximum functionality of the nX-8/500S core. In this basic architecture data memory space and code memory space each have a capacity of 16M bytes (64K bytes×256 segments), and the architecture provides instructions for manipulating these spaces. Depending on the device you actually use, the actual capacity and instruction set may be subsets of the basic architecture. Refer to the user's manual of your device for information on any such limitations.

The following manuals are for products related to the nX-8/500S core. Please read them as well.

### ■MSM665xx User's Manual

The MSM665xx User's Manual describes the hardware of your target device.

## ■MAC66K Assembler Package User's Manual

The MAC66K Assembler Package User's Manual explains assembly language syntax and the use of the relocatable assembler, linker, librarian, and object converter.

## ■ Macroprocessor MP User's Manual

The Macroprocessor MP User's Manual explains macroprocessing language syntax and the use of the general-purpose macroprocessor.

### ■EASE665xx User's Manual

The EASE665xx User's Manual describes the EASE665xx emulator and SID665xx debugger.

This manual consists of three chapters.

## Chapter 1 describes the basic architecture of the nX-8/500S core.

This chapter explains how programs make use of major resources, such as registers and memory. It then describes particular features and restrictions of programming. This chapter provides the basic knowledge needed to understand Chapter 2 and Chapter 3.

## Chapter 2 describes addressing modes.

This chapter explains the coding syntax to access register and memory resources. It also explains the operation of these accesses in detail.

## Chapter 3 describes the functions of each instruction.

This chapter explains the functions and detailed operation of instructions, and provides instruction codes. It presents instructions in alphabetic order, so it can be used for reference.

This manual uses the following terminology.

### ■Values

Numeric expressions and address expressions are basically the same as those used with RAS66K. Refer to the manual for the assembler package for details.

## ■Ranges

A-B represents a range of values that includes A and B. A-B is used in some places where it clearly will not be confused with subtraction.

### ■Addresses

Complete address expressions for the nX-8/500S are coded using a physical segment number (#0 to #255) and an offset within the segment (0 to 0FFFFH), as shown below.

physical\_segment\_number : offset\_within\_segment

## ■Examples

0:0 Offset address 0 in physical segment #0.

0FFH:0FFFH Offset address 65535 in physical segment #255.

CSR:1000H Address 1000H in the code segment indicated by CSR.

TSR:1000H Address 1000H in the table segment indicated by TSR.

DSR:1000H Address 1000H in the data segment indicated by DSR.

However, the offset within a segment is sometimes coded alone as an address where there is no chance for confusion. In particular, an address and an offset within a segment are the same thing when programming for a device that does not access multiple segments or when a program exists entirely within one segment.

## Physical segments and logical segments

For the nX-8/500S, blocks of 64K bytes in memory space are called physical segments, but this manual often simply calls them segments. Blocks allocated to memory by a program are also called segments, but these are specifically logical segments.

## Chapter 1. Architecture

This chapter explains the basic architecture of the nX-8/500S. The basic architecture is the major functional specification of the nX-8/500S. Any microcontroller utilizing this core will have the same functions or a subset of them.

## 1-1. Overview

### 1-1-1. Overview Of OLMS-66K Series And nX-8/500S Core

The OLMS-66K Series of devices are single-chip microcontrollers that integrate Oki Electric's original 16-bit CPU as their core with various peripheral circuits. Currently the OLMS-66K Series provides the target cores listed below. This series has expanded with improvements in processing efficiency in the CPU cores while program compatibility has been maintained.

The nX-8/500S core maintains upward compatibility at the basic assembler level with the nX-8/200 and nX-8/400 cores, but adds instructions and speeds up frequently used instructions. At the same time is extends the accessible memory space and adds addressing modes.

| ~~~~~~~   | ~~~~~~~~     |                                                         |

|-----------|--------------|---------------------------------------------------------|

| Core      | Device       | Description                                             |

| ~~~~~~    | ~~~~~~~      | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~                 |

| nX-8/100  | MSM66101     | Reduced instruction version of nX-8/200.                |

| nX-8/200  | MSM66201/207 | Reduced instruction version of nX-8/300.                |

| nX-8/300  | MSM66301     | First core of OLMS-66K series.                          |

| nX-8/400  | MSM66417     | High-speed version of nX-8/200.                         |

| nX-8/500S | MSM66556/589 | Basic assembly language level upward compatibility with |

|           |              | nX-8/200 to nX-8/400.                                   |

|           |              |                                                         |

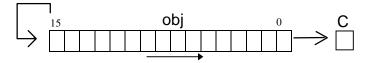

The nX-8/500S centers its processing around its accumulator and register set. It provides nearly identical functions for byte data processing and word data processing. A flag (the data descriptor) determines which type of data is being calculated in the accumulator. Thus the same instruction codes provide functions that are the same for byte data and word data calculations, but

are switched by the state of the data descriptor flag.

Instruction codes are configured in 8-bit units, with lengths of 1 to 6 bytes. Highly efficient programs can be coded by making use of both native instructions for frequent types of processing, and composite instructions for a wide variety of addressing modes.

Memory of the nX-8/500S is split into program memory space and data memory space. Each space can be 16M bytes, configured as 256 physical segments of 64K bytes each. Segments are specified by three segment registers. Code memory also has a vector type area for resets, interrupts, and 1-byte calls, and an ACAL area for 2-byte calls. Segments of data memory are configured as 256 pages of 256 bytes each. More efficient addressing is provided for the SFR page, in which peripheral function control registers are located, and the fixed page and current page.

## 1-2. CPU Resources And Programming Model

This section describe registers and memory configurations and their roles as CPU resources used in programming.

## 1-2-1. Registers

The nX-8/500S utilizes processing methods centered around an accumulator and register sets. The register sets includes a local register set for storing mainly data and a pointing register set for mainly storing addresses. In addition to these, the nX-8/500S has registers for controlling program flow and registers for controlling memory, which together make up the programming model for registers. This section lists the registers used in programs and then describes the functions of each in detail.

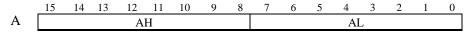

### ■ Accumulator

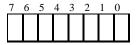

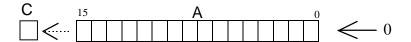

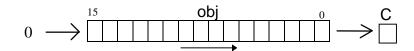

Needed for calculations. A(ACC)  $\begin{bmatrix} 15 & 8 & 7 & 0 \\ & & & \end{bmatrix}$

## ■ Control registers (CR)

This register group controls program flow and stores its current state.

| D G . W 1            | DOM | 15 | 8 7 | 0 |

|----------------------|-----|----|-----|---|

| Program Status Word  | PSW |    |     |   |

| Program Counter      | PC  |    |     |   |

| Local Register Base  | LRB |    |     |   |

| System Stack Pointer | SSP |    |     |   |

## ■ Pointing registers (PR)

There are eight pointing register sets, each with four 16-bit registers X1, X2, DP, and USP. The pointing register sets store memory addresses for indirect addressing. They also provide the same functions for word calculations as extended local registers, so they can be used as data registers too.

| Index Register 1   | X1  | 15 | 8 7 | 0 |

|--------------------|-----|----|-----|---|

| Index Register 2   | X2  |    |     |   |

| Data Pointer       | DP  |    |     |   |

| User Stack Pointer | USP |    |     |   |

## ■ Local registers (ER)

There are 256 local register sets, each with eight 8-bit registers. Each two adjacent 8-bit registers comprise an extended local register (ERn) for processing word data. This data register group is used for storage and calculations of byte and word data.

|                            |     | 15 | 8 7 0 |

|----------------------------|-----|----|-------|

| Extended local register #0 | ER0 | R1 | R0    |

| Extended local register #1 | ER1 | R3 | R2    |

| Extended local register #2 | ER2 | R5 | R4    |

| Extended local register #3 | ER3 | R7 | R6    |

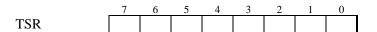

## ■ Segment registers

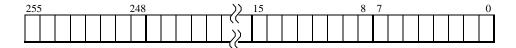

These three 8-bit registers each select a physical segment that contains program code, read-only data, and read/write data respectively. For devices with limited memory capacity, the number of bits implemented in the actual registers may be correspondingly limited. Some devices do not even implement segment registers.

| Code Segment Register  | CSR | 7 0 |

|------------------------|-----|-----|

| Table Segment Register | TSR |     |

| Data Segment Register  | DSR |     |

## ■ ROM window control register

This 8-bit register is used to open a ROM window.

|        | 7 | 4 3 | 0 |

|--------|---|-----|---|

| ROMWIN |   |     |   |

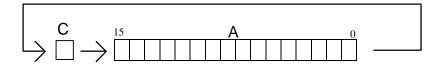

## 1-2-1-1. Accumulator (A)

The accumulator is a 16-bit register around which calculations are centered. It can process words and bytes data. The low byte of the accumulator (AL) can also specify a bit in a bit array. The accumulator is normally accessed by accumulator addressing. However, because it is allocated as a word register in SFR space, it can also be manipulated with SFR addressing (sfr ACC). The accumulator's value immediately after a reset is 0. After an interrupt, the accumulator's value is automatically pushed on the stack. When an RTI instruction is executed, that value is popped from the stack and stored back in A.

## ■ Example Accumulator usage

| L   | A,WORD_VAR   | ; Word instruction      | $(A \leftarrow WORD\_VAR)$     |

|-----|--------------|-------------------------|--------------------------------|

| LB  | A,BYTE_VAR   | ; Byte instruction      | $(AL \leftarrow BYTE\_VAR)$    |

| MB  | C,A.3        | ; Bit instruction       | (C←A.3)                        |

| SBR | BIT_ARRAY    | ; Bit array instruction | (AL is bit specifier)          |

| MOV | ACC,BASE[X2] | ; SFR addressing        | $(ACC \leftarrow (BASE + X2))$ |

## 1-2-1-2. Control Registers (CR)

The control register group controls program flow and stores its current state. Each 16-bit register has a specific function. The information stored in these registers is often collectively called the program context.

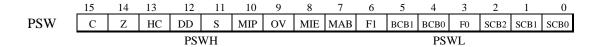

## 1-2-1-2-1. Program Status Word (PSW)

The PSW is configured as flags and fields that store and specify program status. The flag states can be tested with conditional branch instructions. The PSW is allocated as a word register in the SFR area, so it can also be accessed with SFR addressing (sfr APSW). After an interrupt, PSW contents are automatically pushed on the stack. When an RTI instruction is executed, those contents are popped from the stack and stored back in the PSW.

The high byte of the program status word (PSWH) consists of five flags that store the states of CPU calculation results, one flag that indicates the data type in the accumulator, and two flags that control interrupts.

The low byte of the program status word (PSWL) consists of a flag for multiply-accumulate calculations, a field that specifies the size of the common area, a field that selects the pointing register set, and two flags that are for the user.

The operation of each flag and field is described below.

## C Carry flag (bit 15)

The carry flag stores the carry or borrow from unsigned calculations. It is set to 1 when the most significant bit in a arithmetic or comparison instruction generated a carry or borrow. It is reset to 0 in all other cases. The most significant bit is bit 15 for word calculations and bit 7 for byte calculations. The carry flag is also used as a bit accumulator for bit moves and bit logical operations. The SC and RC instructions are provided to set and reset the carry flag.

## Z Zero flag (bit 14)

The zero flag indicates if the result of a calculation was 0. It is set to 1 when the execution result of any calculation instruction (such as arithmetic, logical, comparison, and accumulator data move instructions) or the object bit of any bit manipulation is zero. It is reset to 0 in all other cases.

## HC Half-Carry flag (bit 13)

The half-carry flag is provided for implementing decimal arithmetic. It is set to 1 when bit 3 in a arithmetic or comparison instruction generated a carry or borrow. It is reset to 0 in all other cases.

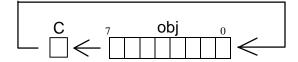

#### DD Data Descriptor (bit 12)

The data descriptor indicates the type of data in the accumulator (A). It is a flag that determines the type of calculation for which the accumulator (A) will be used. It indicates word data when 1, and byte data when 0. The SDD and RDD instructions are provided to set and reset the data descriptor.

#### S Sign flag (bit 11)

The sign flag indicates the sign of calculation results. It is set to 1 when the sign bit (most significant bit) of the execution result of an arithmetic, comparison, or logical calculation was 1. It is reset to 0 in all other cases. The most significant bit is bit 15 for word calculations and bit 7 for byte calculations.

#### MIP Mask Interrupt Priority flag (bit 10)

The mask interrupt priority flag controls the priority function of maskable interrupts. It enables the priority function when 1, and disables the priority function when 0.

#### OV Overflow flag (bit 9)

The overflow flag stores the carry or borrow from signed calculations. It is set to 1 when the result of a arithmetic or comparison instruction exceeds the range that can be expressed with 2's complement numbers. It is reset to 0 in all other cases. The range is -32767 to +32767 for word data, and -128 to +127 for byte data.

#### MIE Mask Interrupt Enable flag (bit 8)

The mask interrupt enable flag controls whether all maskable interrupts are enabled or disabled. It enables interrupts when 1, and disables interrupts when 0. The EI and DI instructions are provided to set and reset MIE.

#### MAB Multiply-Accumulate Register Bank flag (bit 7)

The multiply-accumulate register bank flag specifies the bank of registers used for multiplyaccumulate calculations (MAC instruction).

## F1,F0 User flags 1, 0 (bit 6, bit 3)

The user flags are available for the user in programs. Programs can be written such that these flags are automatically updated in the PSW after interrupts.

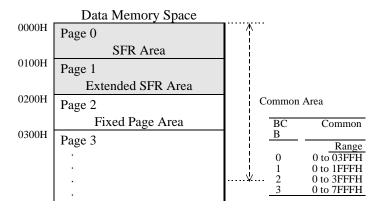

## BCB<sub>1-0</sub> Bank Common Base (bit 5 to 4)

The bank common base specifies the last address of the area that is common between segments. The table below shows the relation between these bits and the selected common area.

| No. | BCB<br>Value | Common Area Range |

|-----|--------------|-------------------|

|     | 1 0          |                   |

| 0   | 0 0          | 0 to 03FFH        |

| 1   | 0 1          | 0 to 1FFFH        |

| 2   | 1 0          | 0 to 3FFFH        |

| 3   | 1 1          | 0 to 7FFFH        |

## SCB<sub>2-0</sub> System Control Base (bit 2 to 0)

The system control base selects the pointing register set. The table below shows the relation between these bits and the selected pointing register set.

| No. | SCB Value | Addresses of Pointing |

|-----|-----------|-----------------------|

|     | 2 1 0     | Register Set          |

| 0   | 0 0 0     | 0200H to 0207H        |

| 1   | 0 0 1     | 0208H to 020FH        |

| 2   | 0 1 0     | 0210H to 0217H        |

| 3   | 0 1 1     | 0218H to 021FH        |

| 4   | 1 0 0     | 0220H to 0227H        |

| 5   | 1 0 1     | 0228H to 022FH        |

| 6   | 1 1 0     | 0230H to 0237H        |

| 7   | 1 1 1     | 0238H to 023FH        |

## 1-2-1-2-1. How Instructions Change PSW Flags

The next page lists the instructions that change PSW flags when executed. However, the list basically excludes instructions that directly write to PSW or PSWH (such as instructions with sfr addressing). The table shows the flag name where the flag changes. It shows 1 where the flag is set and 0 where the flag is reset. It is blank where the flag does not change.

## ■ How instructions change PSW flags

| Instruction  | Instruction Mnemonics           |   |   | Flag C | hange | b  |    |

|--------------|---------------------------------|---|---|--------|-------|----|----|

| Type         |                                 |   | Z | S      | OV    | НС | DD |

| Move         |                                 | • |   |        |       |    |    |

|              | L, LB                           |   | Z |        |       |    | DD |

| (            | CLR, CLRB (if destination is A) |   |   |        |       |    |    |

| Ī            | LC, LCB                         |   | Z |        |       |    |    |

| Increment/l  | Decrement                       |   |   |        |       |    |    |

|              | INC, INCB, DEC, DECB            |   | Z | S      | OV    | НС |    |

| Multiplicati | ion                             |   |   |        |       |    |    |

|              | MUL, MULB, SQR, SQRB            |   | Z |        |       |    |    |

| Division     |                                 |   |   |        |       |    |    |

|              | DIV, DIVB                       | С | Z |        |       |    |    |

| ı            | DIVQ                            | С | Z |        | OV    |    |    |

| Arithmetic/  | Comparison                      |   |   |        |       |    |    |

|              | NEG, ADD, ADC, SUB, SBC         |   |   |        |       |    |    |

|              | NEGB, ADDB, ADCB, SUBB, SBCB    | С | Z | S      | OV    | НС |    |

|              | CMP, CMPB, CMPC, CMPCB          |   |   |        |       |    |    |

| Logical      |                                 |   |   |        |       |    |    |

|              | AND, OR, XOR                    |   | 7 |        |       |    |    |

| 1            | ANDB, ORB, XORB                 |   | Z | S      |       |    |    |

| Sign Extend  | 1                               |   | • | •      | •     |    | •  |

|              | EXTND                           |   |   | S      |       |    | 1  |

| Bit Manipu   | lation/Bit Test                 |   | • | •      | •     |    | •  |

| -            | SB, RB, SBR, RBR, TBR           |   | Z |        |       |    |    |

| DD Manipu    | llation                         | • |   |        |       |    |    |

| ,            | SDD, RDD                        |   |   |        |       |    | DD |

| Carry Man    | ipulation                       | • |   |        | •     |    |    |

|              | SC, RC                          | С |   |        |       |    |    |

| Bit Move T   | o Carry                         |   | L |        |       | l  | I. |

|              | MB, MBR (if destination is C)   | С |   |        |       |    |    |

| Logical Wit  | th Carry                        |   | L |        |       | l  | I. |

|              | BAND, BOR, BXOR                 | С |   |        |       |    |    |

|              | BANDN, BORN                     |   |   |        |       |    |    |

|              | t With Carry                    | • |   |        |       |    |    |

|              | ROL, ROR, SLL, SRL, SRA         |   |   |        |       |    |    |

|              | ROLB, RORB, SLLB, SRLB, SRAB    | С |   |        |       |    |    |

|              | m Interrupt                     | • |   | •      | •     | •  |    |

|              | RTI                             | С | Z | S      | OV    | НС | DD |

| Pop Data T   |                                 | • |   | •      | •     | •  |    |

|              | POP (if operand is PSW or CR)   | С | Z | S      | OV    | НС | DD |

| Reset        | 1 1                             |   |   | 1      | 1     | 1  | ı  |

|              | BRK                             | 0 | 0 | 0      | 0     | 0  | 0  |

|              | =:-:-                           |   |   |        |       |    |    |

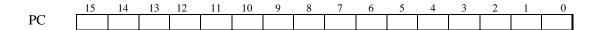

## 1-2-1-2-2. Program Counter (PC)

The PC is a 16-bit counter that stores the address of the program code to be executed next. It increments immediately after the program code is fetched from program memory. Repetition of this operation causes the flow of program execution. Branch instructions set the PC to new addresses of program code.

The PC exists as an independent register, and is not allocated in SFR space. The PC is overwritten by execution of branch instructions, but you do not need to be especially aware of the PC.

Immediately after a reset, the PC value will become the contents of the reset vector. After an interrupt, the address at which execution is to resume will be automatically pushed on the stack. That value will be popped back into the PC when an RTI instruction is executed.

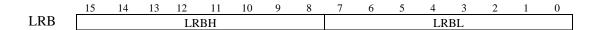

## 1-2-1-2-3. Local Register Base (LRB)

The LRB is a 16-bit register. Its high 8 bits and low 8 bits have independent functions.

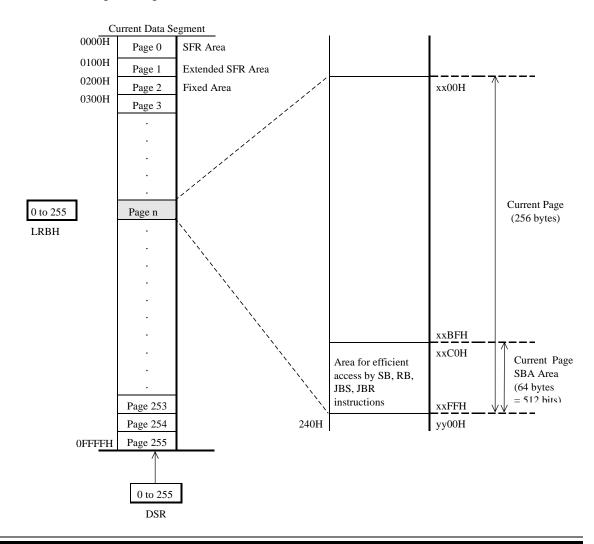

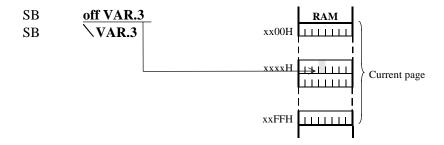

The high 8 bits of the LRB (LRBH) specify the location of the current page. The current page is one of the 256 pages in the data segment specified by DSR. A single page is a 256-byte space that starts at a page boundary. The starting address of the current page is given by LRBH×100H. Current page addressing (off Dadr) and current page SBA area addressing (sbaoff Badr) are provided for accessing the 256 bytes of the current page specified by LRBH.

The low 8 bits of the LRB (LRBL) specify the location of the local register set. The local register set is allocated in 8-bit units within the 2K bytes between offset 200H and 9FFH of physical segment #0 (0:200H to 0:9FFH). The starting address of the local register is given by LRBL×8+200H. Local registers are allocated in order R0, R1, R2, ..., R7 from this starting address. Local register addressing (Rn, ERn) is provided for accessing the local registers specified by LRBL.

LRB is allocated as a word register in SFR space, so it can be manipulated using SFR addressing. The value of LRB is undefined after reset, so its value should be set soon after program execution begins. If local register addressing or current page addressing is used before this, then an undefined memory address will be accessed. After an interrupt, the LRB's value is automatically pushed on the stack. When an RTI instruction is executed, that value is popped from the stack and stored back in LRB.

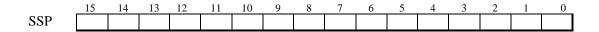

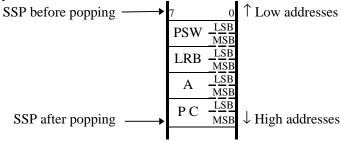

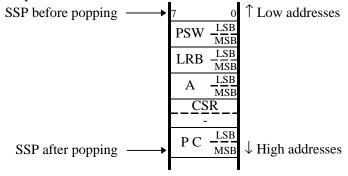

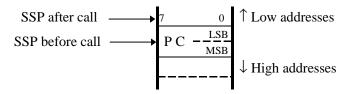

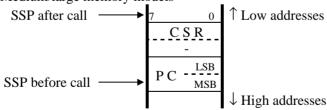

## 1-2-1-2-4. System Stack Pointer (SSP)

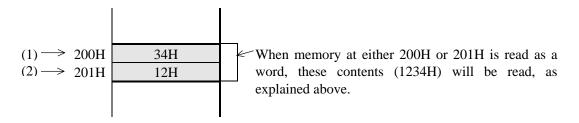

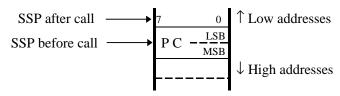

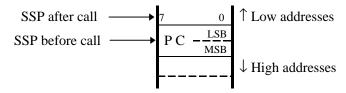

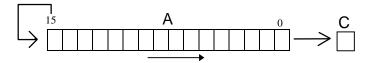

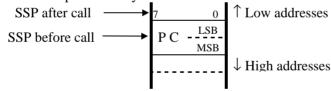

The SSP is a 16-bit register that stores the top stack address of the hardware stack. The hardware stack is a pushdown stack for pushing and popping registers upon execution of interrupt process transfers/returns, calls/returns, and PUSHS/POPS instructions. The SSP stores the top (lowest) address of this stack. The SSP is automatically decremented and incremented during execution processing.

Data is normally pushed on and popped off the stack in word units. When a word value is pushed on the stack, the word data is written to the stack address specified by SSP, and then SSP is decremented by 2. When a word value is popped off the stack, SSP is incremented by 2, and then the word data is read from the stack address specified by SSP. Reads and writes to the memory of this word data are affected by word boundaries, so even if the SSP value is odd, the word data handled will be at the next lower even address. Pushing and popping the stack through SSP is always performed in accordance with these rules.

The hardware stack pointed to by SSP is always allocated in data segment #0 (0:0 to 0:0FFFFH). To access the stack with RAM addressing other than that of stack manipulation instructions, the DSR must be set to 0.

SSP is allocated as a word register in SFR space, so it can also be manipulated with SFR addressing. Immediately after reset, the value of SSP is 0FFFFH, the last address of memory. If there is no memory up to address 0FFFFH, then the actual value for SSP must be set soon after program execution begins. If instructions that manipulate the stack are executed before then, program operation will not be predictable.

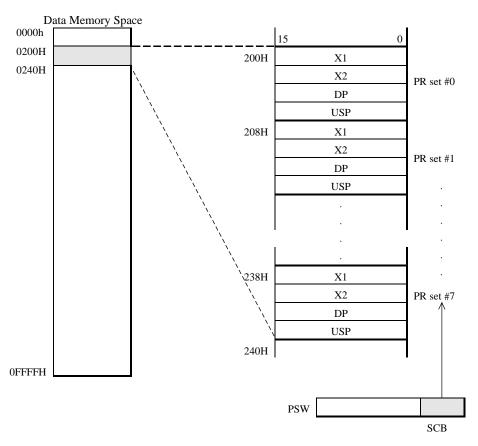

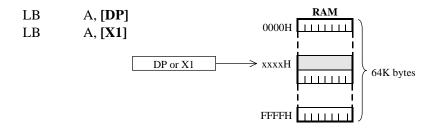

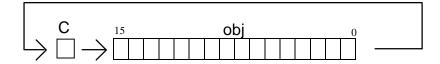

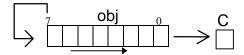

## 1-2-1-3. Pointing Registers (PR)

There are eight pointing register sets, each with four 16-bit registers X1, X2, DP, and USP. The pointing register sets store memory addresses for indirect addressing. They also provide the same functions for word calculations as extended local registers, so they can be used as data registers too.

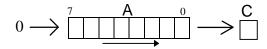

| Index Register 1   | X1  | 15 8 / | 0       |

|--------------------|-----|--------|---------|

| Index Register 2   | X2  |        |         |

| Data Pointer       | DP  |        |         |

| User Stack Pointer | USP |        | ×8 sets |

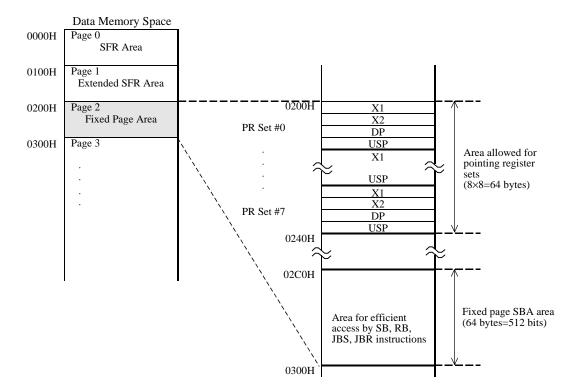

The pointing register sets are allocated in the 64 bytes starting from address 200H in the fixed page of data memory space. They are allocated in order #0, #1,..., #7 from low address to high. Within each pointing register set, X1, X2, DP, and USP are allocated to memory in that order from low address to high.

## ■ Pointing register sets in data memory

The pointing register set to be used is selected by the SCB field in the PSW. The following table shows the relation between SCB field values and the pointing register set selected. Immediately after reset, pointing register set #0 will be selected. The initial values of all pointing registers are undefined.

## ■ SCB field and pointing register set addresses

| No. | SCB V | 'alue | Pointing Register |

|-----|-------|-------|-------------------|

|     | 2 1   | 0     | Set Addresses     |

| 0   | 0 0   | 0     | 0200H to 0207H    |

| 1   | 0 0   | 1     | 0208H to 020FH    |

| 2   | 0 1   | 0     | 0210H to 0217H    |

| 3   | 0 1   | 1     | 0218H to 021FH    |

| 4   | 1 0   | 0     | 0220H to 0227H    |

| 5   | 1 0   | 1     | 0228H to 022FH    |

| 6   | 1 1   | 0     | 0230H to 0237H    |

| 7   | 1 1   | 1     | 0238H to 023FH    |

The pointing register sets overlap the first eight local register sets (R0, R1, ..., R7), which also start from address 200H. To ensure proper program execution, set SCB and LRBL appropriately, such that the pointing registers and local registers do not overlap.

## 1-2-1-3-1. Addressing With Pointing Registers

Pointing register addressing modes are provided to access the contents of pointing registers.

## ■Example Pointing register addressing

| L   | A,X1      | ; A←X1     |

|-----|-----------|------------|

| ADD | A,X2      | ; A←A+X2   |

| CMP | DP,#1234H | ; DP-1234H |

| ST  | A.USP     | : A→USP    |

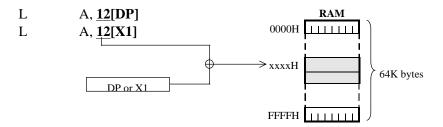

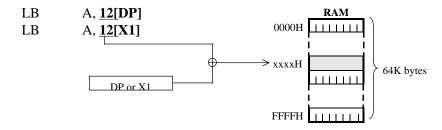

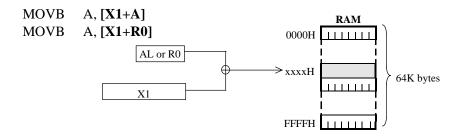

Index register 1 (X1) is used for indirect addressing ([X1]) where X1 itself specifies an address, indirect addressing with 16-bit base (D16[X1]) where an optional address within 64K bytes specifies a base address with X1 specifying an offset, and indirect addressing with 8-bit register displacement ([X1+A], [X1+R0]) where X1 specifies a base address anywhere in 64K bytes with an 8-bit register specifying an offset.

## ■Example■X1 indirect addressing

| L   | A,[X1]     | ; X1 indirect addressing                               |

|-----|------------|--------------------------------------------------------|

| ADD | A,1234[X1] | ; X1 indirect addressing with 16-bit base              |

| SUB | A,[X1+A]   | ; X1 indirect addressing with AL register displacement |

| AND | A,[X1+R0]  | ; X1 indirect addressing with R0 register displacement |

Index register 2 (X2) is used for indirect addressing with 16-bit base (D16[X2]) where an optional address within 64K bytes specifies a base address with X2 specifying an offset.

## ■Example ■X2 indirect addressing

```

ADD

A,1234H[X2]

; X2 indirect addressing with 16-bit base

```

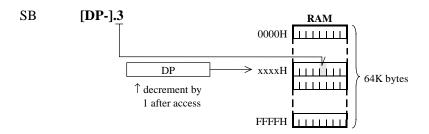

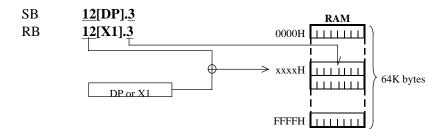

The data pointer (DP) is used for indirect addressing ([DP]) where DP itself specifies an address, indirect addressing with post-increment/decrement ([DP+],[DP-]) where DP is automatically incremented or decremented after the data access, and indirect addressing with 7-bit displacement (n7[DP]) where DP specifies a base address anywhere in 64K bytes with an offset -64 to +63.

## ■Example ■DP indirect addressing

| L   | A,[DP]    | ; DP indirect addressing                         |

|-----|-----------|--------------------------------------------------|

| ADD | A,[DP+]   | ; DP indirect addressing with post-increment     |

| SUB | A,[DP-]   | ; DP indirect addressing with post-decrement     |

| ADD | A,-12[DP] | ; DP indirect addressing with 7-bit displacement |

The user stack pointer (USP) is used for indirect addressing with 7-bit displacement (n7[USP]) where USP specifies a base address anywhere in 64K bytes with an offset -64 to +63.

## ■Example■USP indirect addressing

```

L

A,-12[USP]

; USP indirect addressing with 7-bit displacement

```

Like other byte objects, the low bytes of X1, X2, DP, and USP can be used as loop counter that specify 1 to 256 loops.

## ■Example ■Loop counter usage

```

DJNZ

X1L,LOOP

; X1 low byte (X1L) is loop counter

DJNZ

X2L,LOOP

; X2 low byte (X2L) is loop counter

DJNZ

DPL,LOOP

; DP low byte (DPL) is loop counter

DJNZ

USPL,LOOP

; USP low byte (USPL) is loop counter

```

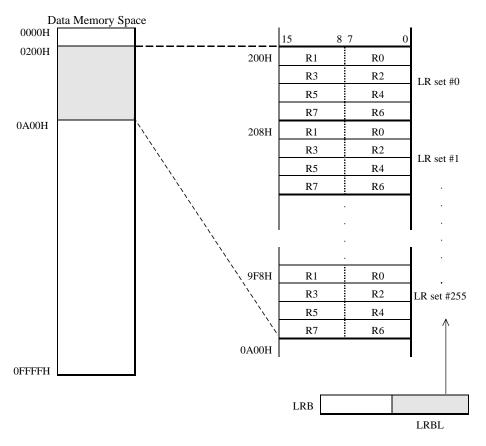

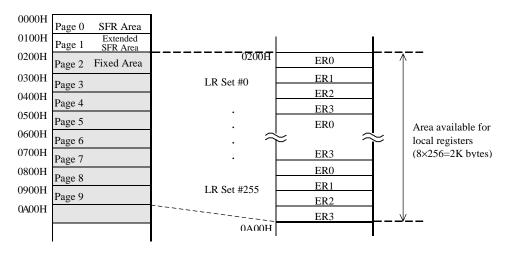

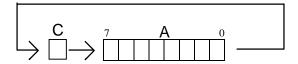

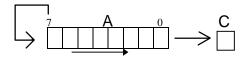

## 1-2-1-4. Local Registers (ER)

There are 256 local register sets, each with eight 8-bit registers. Each two adjacent 8-bit registers comprise an extended local register (ERn) for processing word data. This data register group is used for storage and calculations of byte and word data.

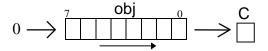

| T . 1 11 1 1               | EDA  | 15 8 | 7 0          | _                 |

|----------------------------|------|------|--------------|-------------------|

| Extended local register #0 | ER0  | R1   | R0           |                   |

| Extended local register #1 | ER1  |      | <del> </del> |                   |

| Extended local register #1 | LIXI | R3   | R2           |                   |

| Extended local register #2 | ER2  | D.5  | R4           | 1                 |

| Extended focul register #2 | LINZ | R5   | K4           |                   |

| Extended local register #3 | ER3  | R7   | R6           | $\times 256$ sets |

| Extended focul register #5 | LICS | 107  | i Ko         | 7230 BCts         |

The local register sets are allocated in the 2048 bytes starting from address 200H in the fixed page of data memory space. They are allocated in order #0, #1,..., #255 from low address to high. Within each local register set, R0 to R7 are allocated to memory in that order from low address to high.

## ■Local register sets in data memory

The local register set to be used is selected by the low byte of LRB (LRBL). The starting address of the local register set selected is given by LRBL $\times$  8 + 200H. Immediately after reset, the value of LRBL is undefined, so there is no way to tell which local register set is selected. The initial values of all local registers are undefined.

| No. | LRBL Value | Local Register Set Addresses |

|-----|------------|------------------------------|

| 0   | 0          | 0200H to 0207H               |

| 1   | 1          | 0208H to 020FH               |

| 2   | 2          | 0210H to 0217H               |

| 3   | 3          | 0218H to 021FH               |

| •   | •          | •                            |

| •   | •          | •                            |

| •   | •          | •                            |

| 254 | 254        | 09F0H to 09F7H               |

| 255 | 255        | 09F8H to 09FFH               |

The first eight local register sets overlap the pointing register sets (X1, X2, DP, USP), which also start from address 200H. To ensure proper program execution, set LRBL and SCB appropriately, such that the local registers and pointing registers do not overlap.

## 1-2-1-4-1. Addressing With Local Registers

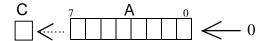

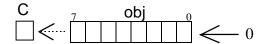

A byte-oriented local register addressing mode and word-oriented extended local register addressing mode are provided to access the contents of local registers.

## ■Example ■Local register addressing

| LB   | A,R0   | ; AL←R0    |

|------|--------|------------|

| ADDB | A,R3   | ; AL←AL+R3 |

| CMPB | R6,#12 | ; R6-12    |

| STB  | A.R7   | : A→R7     |

## ■Example ■Extended local register addressing

| L   | A,ER0      | ; A←ER0     |

|-----|------------|-------------|

| ADD | A,ER1      | ; A←A+ER1   |

| CMP | ER2,#1234H | ; ER2-1234H |

| ST  | A,ER3      | ; A→ER3     |

For INCB and DECB instructions, R0 to R3 give more efficient instruction codes than R4 to R7.

## ■Example■INCB/DECB instructions

| <b>INCB</b> | R0 | ; 1-byte instruction |

|-------------|----|----------------------|

| DECB        | R3 | ; 1-byte instruction |

| <b>INCB</b> | R4 | ; 2-byte instruction |

| DECB        | R7 | : 2-byte instruction |

For DJNZ instructions, R4 and R5 give more efficient instruction codes for jumps in the range -128 to -1.

**■**Example**■**Loop instructions

LOOP:

DJNZ R4,LOOP ; 2-byte instruction DJNZ R0,LOOP ; 3-byte instruction DJNZ R5,NEXT ; 3-byte instruction

NEXT:

For multiplication and division instructions, ER0, ER1, and R1 are used to store products, dividends, quotients, and remainders.

■Example ■ Multiplication and division instruction

MUL obj  $; <A,ER0>\leftarrow A\times obj$ DIV obj ; <A,ER0>←A÷ obj

;  $ER1 \leftarrow <A,ER0 > mod obj$

MULB obj ; A←A×obj DIVB obj ; A←A÷ obj

; R1←A mod obj

R0 is used as a 1-byte unsigned displacement for addressing with X1 as a base.

■Example ■X1 indirect addressing with R0 register displacement

MOV A,[X1+R0]; A←(X1+R0)

**INCB** [X1+R0] $; (X1+R0)\leftarrow(X1+R0)+1$

## 1-2-1-5. Segment Registers

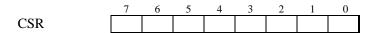

These 8-bit registers each select one of the 256 physical segments. CSR and TSR point to program memory space. CSR and TSR do not exist in devices with just one segment in program memory space. DSR points to data memory space. DSR does not exist in devices with just one segment in data memory space.

## 1-2-1-5-1. Code Segment Registers (CSR)

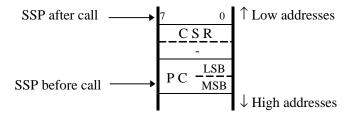

The CSR specifies which segment in program memory space contains the program code that is currently executing. It exists as an independent 8-bit register, so it is not allocated in SFR space. Writes to the CSR are performed by interrupts and by FJ, FCAL, FRT, and RTI instructions. The CSR cannot be written to by other methods.

A single segment has offset addresses 0 to 0FFFFH. Address calculations to determine the addressing of objects are performed with 16-bit offset addresses; overflows and underflows are ignored. Therefore, addressing alone will not change the CSR. Similarly, the CSR will not be changed if the PC overflows. Thus, program execution cannot proceed across code segment boundaries by any method other than those mentioned in the previous paragraph. Immediately after reset the CSR value will be 0.

When an interrupt occurs under the medium or large memory model, the current CSR will be automatically pushed on the stack along with the PC. The popped value will be restored to the CSR upon execution of an RTI instruction. (Refer to memory models.)

## 1-2-1-5-2. Table Segment Registers (TSR)

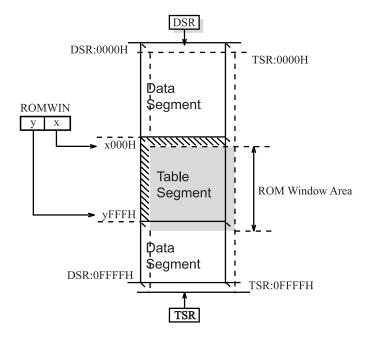

The TSR specifies which segment in program memory space contains table data. It is an 8-bit register allocated in SFR space, so it can be written by instructions that have SFR addressing. Data in the table segment is accessed using ROM reference instructions (LC, LCB, CMPC, CMPCB). RAM addressing of the table segment can also be performed by using the ROM window function.

A single segment has offset addresses 0 to 0FFFFH. Address calculations to determine the addressing of objects are performed with 16-bit offset addresses; overflows and underflows are ignored. Therefore, addressing alone will not change the TSR. Immediately after reset the TSR value will be 0.

## 1-2-1-5-3. Data Segment Registers (DSR)

The DSR specifies which segment in data memory space contains data. It is an 8-bit register allocated in SFR space, so it can be written by instructions that have SFR addressing. Data in the data segment is accessed using RAM addressing. The ROM window function opens a window in this data segment through which the table segment can be accessed.

A single segment has offset addresses 0 to 0FFFFH. Address calculations to determine the addressing of objects are performed with 16-bit offset addresses; overflows and underflows are ignored. Therefore, addressing alone will not change the DSR. Immediately after reset the DSR value will be 0.

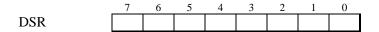

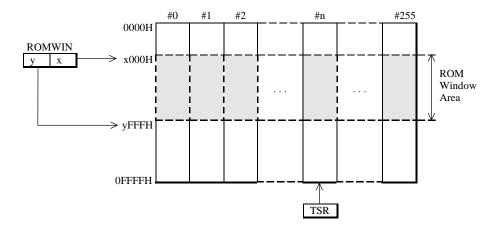

## 1-2-1-6. ROM Window Control Register (ROMWIN)

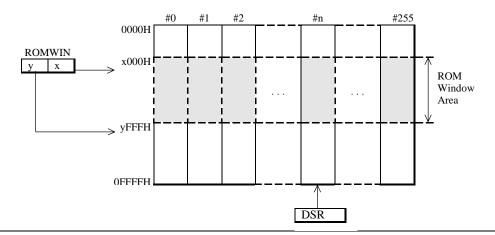

ROMWIN has the function of opening a ROM window. It is an 8-bit register allocated in SFR space. The lower 4 bits specify the starting address of the ROM window, and the upper 4 bits specify the ending address. The starting address will be ROMWIN<sub>3,0</sub>×1000H, and the ending address will be ROMWIN, ×1000H + 0FFFH. For example, if 71H is written to ROMWIN, then the ROM window will be 1000H to 7FFFH. If the value written to the lower 4 bits is 0, then the ROM window function will not operate.

ROMWIN may be written only once after reset. Second and later writes will be ignored. Immediately after reset, the value of ROMWIN will be 0, so the ROM window function will not operate. To use the ROM window function, it is recommended that you open the ROM window soon after reset.

## 1-2-1-7. Special Function Registers (SFR)

Special function registers are a register group for controlling peripheral functions. They are allocated to addresses 0 to 1FFH in data memory space. In other words, nX-8/500S utilizes the concept of memory-mapped I/O. Refer to the section on data memory space for details.

## 1-2-2. Memory Space

The memory of nX-8/500S is split into program space and data space. The configurations of each of these spaces are described below.

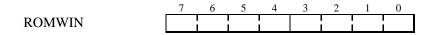

## 1-2-2-1. Program Memory Space

Program memory space of nX-8/500S has a total capacity of 16M bytes, configured as 256 segments of 64K bytes each. Program memory space contains executable instruction code (program code) and read-only data (table data).

The program code being executed is specified as 24 bits: CSR determines the high 8 bits, and PC determines the low 16 bits (CSR:PC). The segment selected by CSR is called the code segment. When instruction execution increments the PC or when relative jumps add displacements to the PC, overflows and underflows are ignored. This means that the CSR will not change.

The segment selected by TSR is called the table segment. The table segment can be accessed using table data addressing with the four instructions LC, LCB, CMPC, and CMPCB. RAM addressing can also access the table segment through use of the ROM window function.

A single segment has offset addresses 0 to 0FFFFH. Address calculations to determine the addressing of objects are performed with 16-bit offset addresses; overflows and underflows are ignored. Therefore, addressing alone will not change the TSR.

## ■Overview of program memory space

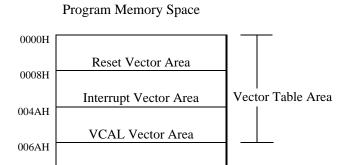

## 1-2-2-1-1. Vector Table Area

The 74 bytes from address 0 to 49H in segment #0 (0:0 to 0:49H) in program memory space are a vector table area for storing program process entry addresses (vectors) used after resets and interrupts. The 32 bytes from address 4AH to 69H (0:4AH to 0:69H) are a vector table area for storing program process entry addresses used when VCAL instructions are executed.

Each vector is a data word located at an even address. When control transfers to a program process, the CSR value is reset to 0 by hardware, selecting segment #0. Therefore entry addresses of program processes exist only in segment #0.

1-2-2-1-1. Reset Vector Area

The first four entries in the vector table are assigned as reset vectors corresponding to the sources of resets. Vector addresses and reset sources are as follows.

| Vector Address | Reset Source                             |

|----------------|------------------------------------------|

| 0000H          | Reset pin (RES) input                    |

| 0002H          | System reset instruction (BRK) execution |

| 0004H          | Watchdog timer (WDT)                     |

| 0006H          | Op-code trap (OPTRP)                     |

## 1-2-2-1-1-2. Interrupt Vector Area

Interrupt sources differ depending on the peripheral functions of each device. The interrupt vector area is assigned one non-maskable interrupt (NMI) and a maximum 32 maskable interrupts.

| Vector Address | Interrupt Source       |

|----------------|------------------------|

| 0008H          | NMI pin input          |

| 000AH          | Maskable interrupt #1  |

| 000CH          | Maskable interrupt #2  |

| •              |                        |

| •              |                        |

| •              |                        |

| 0048H          | Maskable interrupt #32 |

## 1-2-2-1-1-3. VCAL Table Area

The VCAL table area is a vector area for the 16 VCAL instructions (1-byte call instructions). Vector addresses and their corresponding VCAL instructions are as follows.

| Vector Address | VCAL Instruction |

|----------------|------------------|

| 004AH          | VCAL 4AH         |

| 004CH          | VCAL 4CH         |

| 004EH          | VCAL 4EH         |

| 0050H          | VCAL 50H         |

| 0052H          | VCAL 52H         |

| 0054H          | VCAL 54H         |

| 0056H          | VCAL 56H         |

| 0058H          | VCAL 58H         |

| 005AH          | VCAL 5AH         |

| 005CH          | VCAL 5CH         |

| 005EH          | VCAL 5EH         |

| 0060H          | VCAL 60H         |

| 0062H          | VCAL 62H         |

| 0064H          | VCAL 64H         |

| 0066H          | VCAL 66H         |

| 0068H          | VCAL 68H         |

### 1-2-2-1-1-4. Vector Table Coding Syntax

With the assembler, program process entry addresses are coded as labels in the operands of DW directives. An example program that defines the vector area is shown below. If the vector area other than the reset vector for reset pin (RES) input is not used for vectors, then it can be used for ordinary program code.

```

;Reset Vector Table

AT 0000H

CSEG

DW

START

; Power on reset

DW

BRK_RESET

; BRK instruction

DW

WDT_RESET

; Watch dog timer overflow

DW

OPTRP_RESET

; Opecode trap

;Interrupt Vector Table

DW

NMI_ENTRY

; Non-maskable interrupt

DW

INTO_ENTRY

; Maskable interrupt #1

DW

INTN_ENTRY

; Maskable interrupt #n

;Vcal Vector Table

AT 004AH

CSEG

VSUB0:

DW

SUB0

; VCAL subroutine #0

VSUB1:

DW

SUB1

; VCAL subroutine #1

VSUB15:

DW

SUB15

; VCAL subroutine #15

; Start of main procedure

EXTRN DATA:_$$SSP

; Stack pointer initial address

START:

MOV

SSP,#_$$SSP

; Set system stack pointer

```

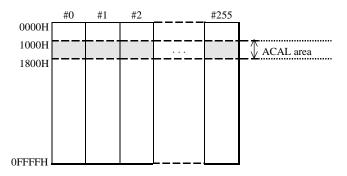

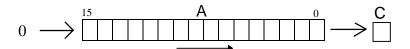

### 1-2-2-1-2 ACAL Area

The 2K bytes at addresses 1000H to 17FFH of each segment in program memory space (CSR:1000H to CSR:17FFH) are the ACAL area for placing the entry points of subroutines called by ACAL instructions. ACAL instructions are 2-byte instructions, so they are more efficient that 3-byte CAL instructions. An ACAL area exists in each physical segment.

### ■ACAL area in program memory space

### 1-2-2-1-3. ROM Window Area In Program Memory Space

The ROM window area is allows data in the table segment specified by TSR to be accessed using RAM addressing (ROM window addressing). It is a program memory area that can be seen through a window opened in a data segment. Table data at the same address value can be read through the window, which can only be opened in areas that are not mapped to internal data memory. The range of the ROM window area is set with the ROM window function control register (ROMWIN).

### ■ROM window area in program memory space

### 1-2-2-1-4. Internal And External Program Memory Areas

There are no logical differences in programming when using internal and external program memory areas. Use the linker to place program code in internal program memory areas, which are implemented in the target device, and in external program memory areas, which are mounted in the target system.

Internal program memory size depends on the device. Refer to the user's manual of the target device for details.

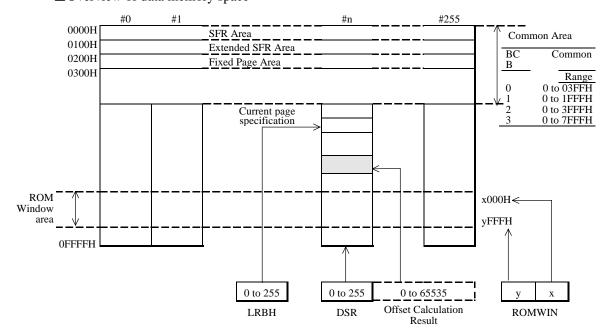

### 1-2-2. Data Memory Space

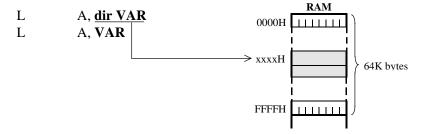

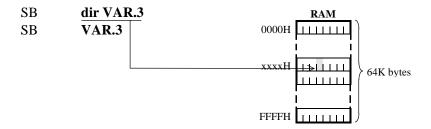

Data memory space of nX-8/500S has a total capacity of 16M bytes, configured as 256 segments of 64K bytes each. Data memory space normally contains memory that is readable and writable.

The segment selected by DSR is called the data segment. The data segment can be accessed using RAM addressing. RAM addressing can also access the table segment through use of the ROM window function.

A single segment has offset addresses 0 to 0FFFFH. Address calculations to determine the addressing of objects are performed with 16-bit offset addresses; overflows and underflows are ignored. Therefore, addressing alone will not change the DSR.

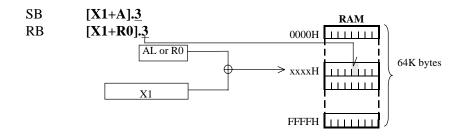

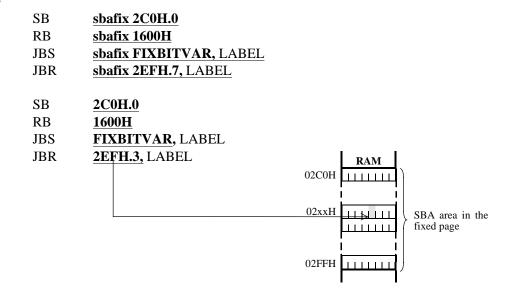

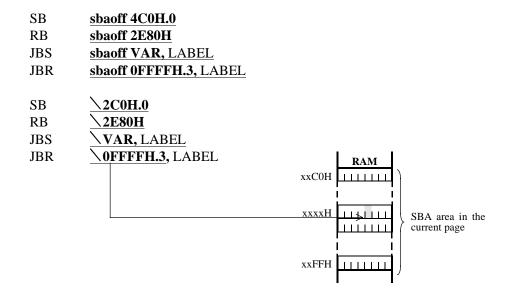

The nX-8/500S provides several special areas in data memory space to raise coding efficiency. These areas include special pages, such as the SFR, fixed, and current page, which allow addresses to be specified as one-byte offsets within the page. There is also an SBA area, which provides very efficient code for the instructions SB, RB, JBS, and JBR. If the programmer defines variables with consideration to the location of data, then the assembler will select the optimal addressing for data accesses.

Applications that use multiple data segments may need to exchange data between segments. To enable this exchange, nX-8/500S has a common area starting from address 0 in data memory. The SFR area, extended SFR area, and fixed page area always reside in the common area.

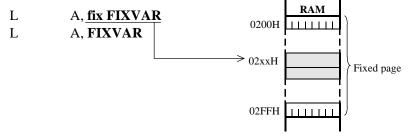

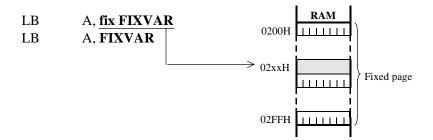

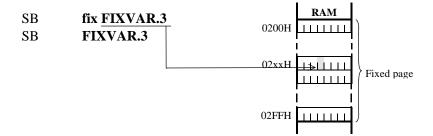

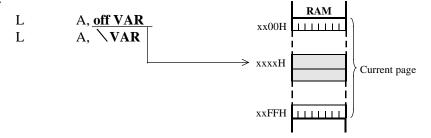

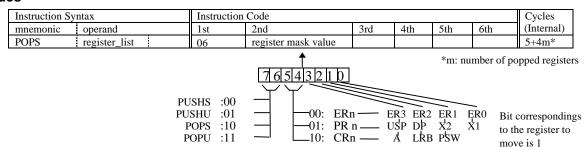

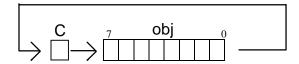

Local registers and pointing registers are located in data memory space. These registers can also be accessed with address specifications.