# MAC66K Assembler Package User's Manual

Program Development Support Software

Relocatable Assembler Linker Librarian Object Converter RAS66K RL66K LIB66K OH66K

> THIRD EDITION ISSUE DATE:Nov. 1993

#### <u>NOTICE</u>

- 1. The information contained herein can change without notice owing to product and/or technical improvements. Before using the product, please make sure that the information being referred to is up-to-date.

- 2. The outline of action and examples for application circuits described herein have been chosen as an explanation for the standard action and performance of the product. When planning to use the product, please ensure that the external conditions are reflected in the actual circuit, assembly, and program designs.

- 3. When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating temperature.

- 4. OKI assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified operating range.

- 5. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of the product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

- 6. The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g., office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not authorized for use in any system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or application may result in the loss or damage of property, or death or injury to humans. Such applications include, but are not limited to, traffic and automotive equipment, safety devices, aerospace equipment, nuclear power control, medical equipment, and life-support systems.

- 7. Certain products in this document may need government approval before they can be exported to particular countries. The purchaser assumes the responsibility of determining the legality of export of these products and will take appropriate and necessary steps at their own expense for these.

- 8. No part of the contents contained herein may be reprinted or reproduced without our prior permission.

- 9. MS-DOS is a registered trademark of Microsoft Corporation.

Copyright 1993 Oki Electric Industry Co., Ltd.

# TABLE OF CONTENTS

### **Chapter 1. Introduction**

| 1.1 | About  | t The MAC66K Assembler Package                       | 1-1  |

|-----|--------|------------------------------------------------------|------|

| 1.2 | System | m Requirements                                       | 1-2  |

| 1.3 | About  | t This Manual                                        | 1-3  |

| 1.4 | Relate | ed Documents                                         | 1-4  |

| 1.5 | CPU (  | Core                                                 | 1-5  |

| 1.6 | Symbo  | ol Usage In This Manual                              | 1-6  |

| 1.7 | Chang  | ges from Previous MAC66K Assembler Package Ver. 2.XX | 1-7  |

|     |        | RAS66K                                               |      |

|     | 1.7.2  | RL66K                                                | 1-13 |

|     | 1.7.3  | LIB66K                                               | 1-15 |

|     | 1.7.4  | ОН66К                                                | 1-15 |

### **Chapter 2.** Installation and Usage

| Introd                                      | luction                                                                                            | 2-1                                          |  |  |  |

|---------------------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------|--|--|--|

| Disk (                                      | Contents                                                                                           | 2-2                                          |  |  |  |

| Install                                     | lation                                                                                             | 2-3                                          |  |  |  |

| Enviro                                      | onment Variables                                                                                   | 2-5                                          |  |  |  |

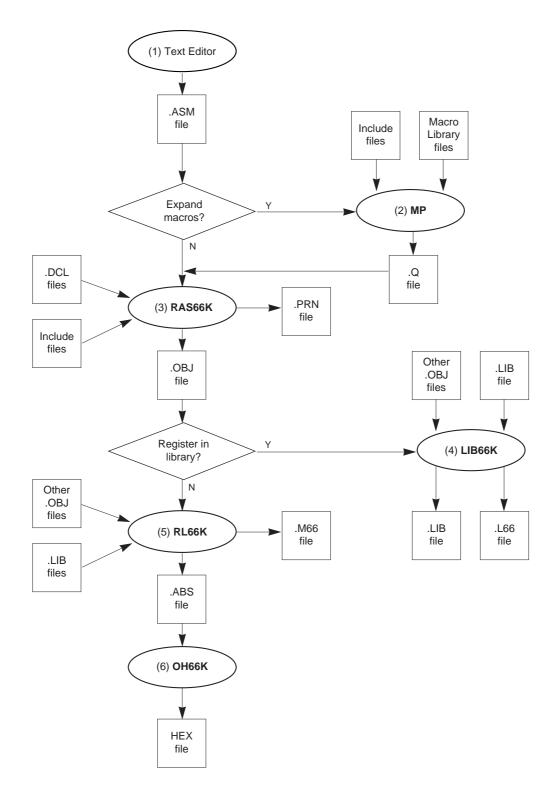

| Progra                                      | am Development Flow                                                                                | 2-6                                          |  |  |  |

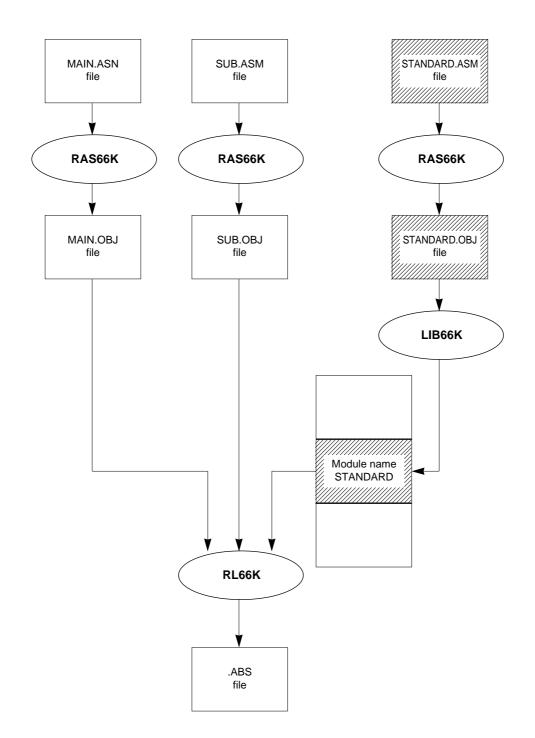

| Modu                                        | le Programming                                                                                     | 2-8                                          |  |  |  |

| Using The MAC66K Assembler Package Software |                                                                                                    |                                              |  |  |  |

| 2.7.1                                       | MP: Macro Expansion                                                                                | 2-10                                         |  |  |  |

| 2.7.2                                       | RAS66K: Assembler                                                                                  | 2-10                                         |  |  |  |

| 2.7.3                                       | LIB66K: Registering Object Modules In Library Files                                                | 2-11                                         |  |  |  |

| 2.7.4                                       | RL66K: Linker                                                                                      | 2-11                                         |  |  |  |

| 2.7.5                                       | OH66K: Changing File Format                                                                        | 2-11                                         |  |  |  |

| 2.7.6                                       | Generating Assembler Level Debugging Information                                                   | 2-12                                         |  |  |  |

|                                             | Disk (<br>Install<br>Envire<br>Progr<br>Modu<br>Using<br>2.7.1<br>2.7.2<br>2.7.3<br>2.7.4<br>2.7.5 | <ul> <li>2.7.1 MP: Macro Expansion</li></ul> |  |  |  |

# **Chapter 3. Basic Programming Knowledge**

| 3.1 | Introduction |          |                                           |     |  |

|-----|--------------|----------|-------------------------------------------|-----|--|

| 3.2 | Memo         | ry Space |                                           | 3-2 |  |

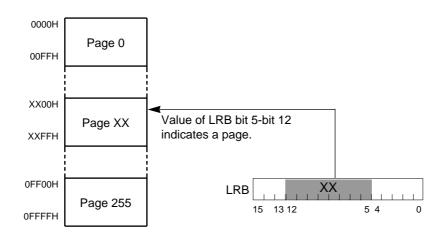

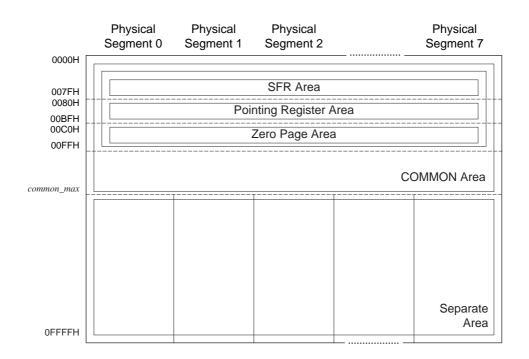

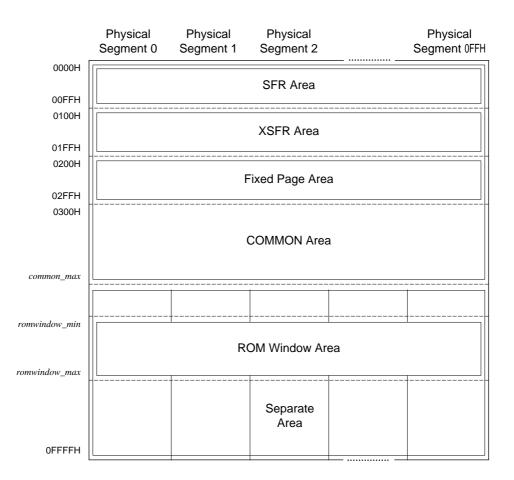

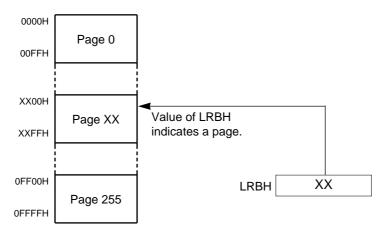

|     | 3.2.1        | Overvie  | w Of Memory Space                         | 3-2 |  |

|     | 3.2.2        | Memory   | v Space Of nX-8/100, nX-8/200, nX-8/400   | 3-3 |  |

|     |              | 3.2.2.1  | Program Memory Space                      | 3-3 |  |

|     |              |          | (1) Vector Table Area                     | 3-4 |  |

|     |              |          | (2) VCAL Table Area                       | 3-4 |  |

|     |              | 3.2.2.2  | Data Memory Space                         | 3-6 |  |

|     |              |          | (1) Special Function Register (SFR) Areas | 3-6 |  |

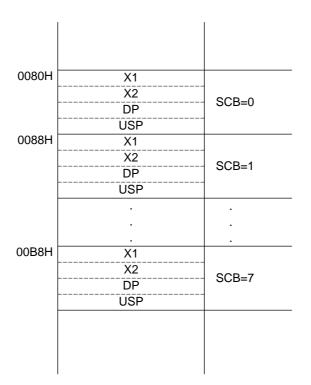

|     |              |          | (2) Pointing Register Area                | 3-6 |  |

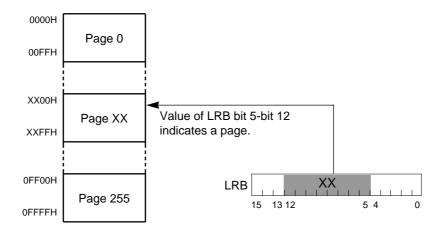

|     |              |          | (3) Current Page Areas                    | 3-7 |  |

|     |              |          | (4) Zero Page Area                        | 3-8 |  |

|     | 3.2.3        | Memory   | Space Of nX-8/300                         | 3-9 |  |

|     |              | 3.2.3.1  | Program Memory Space                      |     |  |

|     |              |          |                                           |     |  |

|     |         |             | (1) Vector Table Area                     | 3-10 |

|-----|---------|-------------|-------------------------------------------|------|

|     |         |             | (2) VCAL Table Area                       | 3-11 |

|     |         | 3.2.3.2     | Data Memory Space                         | 3-12 |

|     |         |             | (1) Special Function Register (SFR) Areas | 3-12 |

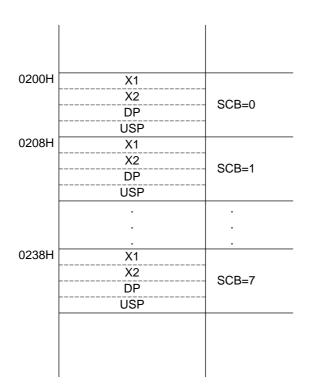

|     |         |             | (2) Pointing Register Area                | 3-13 |

|     |         |             | (3) Current Page Areas                    | 3-14 |

|     |         |             | (4) Zero Page Area                        | 3-15 |

|     |         |             | (5) COMMON and Separate Areas             | 3-15 |

|     | 3.2.4   | Memory      | Space Of nX-8/500                         | 3-16 |

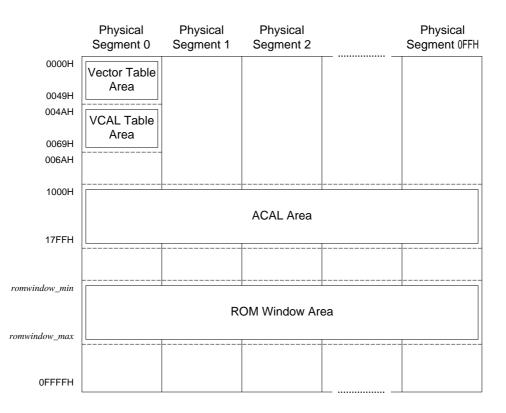

|     |         | 3.2.4.1     | Program Memory Space                      | 3-16 |

|     |         |             | (1) Vector Table Area                     | 3-17 |

|     |         |             | (2) VCAL Table Area                       | 3-18 |

|     |         |             | (3) ACAL Area                             | 3-18 |

|     |         |             | (4) ROM Window Area                       | 3-18 |

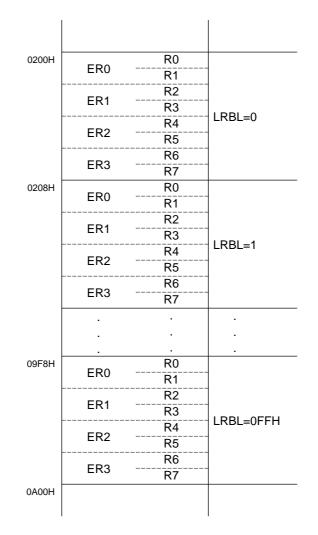

|     |         | 3.2.4.2     | Data Memory Space                         | 3-19 |

|     |         |             | (1) Special Function Register (SFR) Areas | 3-20 |

|     |         |             | (2) Current Page Area                     | 3-20 |

|     |         |             | (3) Fixed Page Area                       | 3-21 |

|     |         |             | (4) Pointing Register Area                | 3-21 |

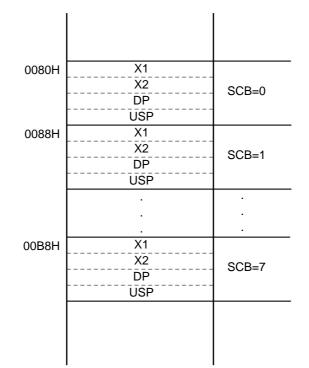

|     |         |             | (5) Local Register Area                   | 3-22 |

|     |         |             | (6) EEPROM Area                           |      |

|     |         |             | (7) Dual Port RAM Area                    | 3-24 |

|     |         |             | (8) SBA Area                              |      |

|     |         |             | (9) ROM Window Area                       |      |

|     |         |             | (10) COMMON and Separate Areas            | 3-25 |

|     |         | 3.2.4.3     | Memory Models                             | 3-25 |

|     | 3.2.5   | Memory      | Access                                    | 3-26 |

|     |         | 3.2.5.1     | Wraparound                                |      |

|     |         | 3.2.5.2     | Word Boundaries                           |      |

| 3.3 |         | -           |                                           |      |

| 3.4 |         |             | nts                                       |      |

| 3.5 |         |             | ondence With DCL Files                    |      |

|     | 3.5.1   |             | ion In DCL Files                          |      |

|     |         |             | ID Number                                 |      |

|     |         |             | ocontroller ID Number                     |      |

|     |         |             | le range of program memory space          |      |

|     |         |             | le range of data memory space             |      |

|     |         |             | area range and permitted range of access  |      |

|     |         |             | rved words representing addresses         |      |

|     |         | · /         | itted instructions                        |      |

| •   | 3.5.2   |             | CL66K.DOC                                 |      |

| 3.6 | File Sp | pecificatio | Dns                                       | 3-34 |

# Chapter 4. RAS66K

| Introd | luction                  | 4-1                                                                                                                                                  |

|--------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| File S | pecification Defaults    | 4-2                                                                                                                                                  |

| -      |                          |                                                                                                                                                      |

| 0      |                          |                                                                                                                                                      |

| 4.3.2  | Option Specifications    | 4-4                                                                                                                                                  |

|        | File S<br>Using<br>4.3.1 | Introduction         File Specification Defaults         Using RAS66K         4.3.1       Executing RAS66K         4.3.2       Option Specifications |

|     |       | 4.3.2.1 Li  | st Of Options                                                     | 4-4  |

|-----|-------|-------------|-------------------------------------------------------------------|------|

|     |       | 4.3.2.2 Oj  | ption Functions                                                   | 4-5  |

|     |       | (1          | ) Memory Model Specification (/MS, /MC, /MM, /ML)                 | 4-7  |

|     |       | (2          | ) Control of Branch Instruction Flag Attribute Checks (/CF, /NCF) | 4-8  |

|     |       |             | ) Suppression Of Upper And Lower Case Distinction (/CD, /NCD)     |      |

|     |       |             | ) Warning Check Control (/W, /NW)                                 |      |

|     |       |             | ) Include File Path Specification (/I)                            |      |

|     |       |             | ) Output of C Source Level Debugging Information (/CC)            |      |

|     |       |             | ) Saving File Read Buffer (/V)                                    |      |

|     |       |             | ) Print File Generation Control (/PR, /NPR)                       |      |

|     |       |             | ) Absolute Print File Generation (/A)                             |      |

|     |       |             | 0) Assembly List Output Control (/L, /NL)                         |      |

|     |       |             | 1) Symbol List Output Control (/S, /NS)                           |      |

|     |       |             | 2) Cross-Reference List Output Control (/R, /NR)                  |      |

|     |       |             | 3) Print File Characters Per Line Specification (/PW)             |      |

|     |       |             | 4) Print File Lines Per Page Specification (/PL)                  |      |

|     |       |             | 5) Tab Code Replacement (/T)                                      |      |

|     |       |             | 6) Object File Output Control (/O, /NO)                           |      |

|     |       |             | 7) Output of Assembly Level Debugging Information (/D, /ND)       |      |

|     |       |             |                                                                   |      |

|     |       |             | 8) Error Message Output Control (/E, /NE)                         |      |

|     | 122   |             | 9) Generation of EXTRN Declaration Files (/X)                     |      |

|     | 4.3.3 |             | 1 Code                                                            |      |

|     | 4.3.4 |             | ble                                                               |      |

| 4.4 |       | ng Program  |                                                                   |      |

|     | 4.4.1 |             | ram Code                                                          |      |

|     |       |             | arget Microcontroller Specification                               |      |

|     |       |             | OMMON Area Specification                                          |      |

|     |       |             | emory Model Specification                                         |      |

|     |       |             | OM Window Area Specification                                      |      |

|     |       |             | bde Position Restrictions                                         |      |

|     | 4.4.2 | U           | d Specification                                                   |      |

|     | 4.4.3 | -           | Irce Statements                                                   |      |

|     |       |             | riting Instruction Statements                                     |      |

|     |       |             | riting Directive Statements                                       |      |

|     |       |             | riting Special Statements                                         |      |

|     | 4.4.4 |             | ments                                                             |      |

| 4.5 |       |             | gments                                                            |      |

|     | 4.5.1 |             | ements Coded In Logical Segments                                  |      |

|     |       |             | statements coded mainly in the CODE segment                       |      |

|     |       |             | statements coded mainly in the DATA segment                       |      |

|     |       |             | statements coded mainly in the BIT segment                        |      |

|     |       |             | statements coded mainly in the EDATA segment                      |      |

|     |       |             | statements coded mainly in the EBIT segment                       |      |

|     | 4.5.2 | Absolute Se | egments And Relocatable Segments                                  | 4-31 |

|     |       | 4.5.2.1 Al  | bsolute Segments                                                  | 4-32 |

|     |       | 4.5.2.2 Re  | elocatable Segments                                               | 4-34 |

|     | 4.5.3 |             | Area                                                              |      |

|     |       | 4.5.3.1 Da  | ata Memory Space Seen By RAS66K                                   | 4-36 |

|     |       |             | gment Allocation To COMMON Area                                   |      |

|     | 4.5.4 |             | ents                                                              |      |

|     | 4.5.5 | Overlapping | g Logical Segments                                                | 4-40 |

|     |       |             |                                                                   |      |

| 4.6 |       |          | ter                                                     |        |

|-----|-------|----------|---------------------------------------------------------|--------|

|     | 4.6.1 |          | n Counter Initialization                                |        |

|     |       |          | alization of location counters of relocatable segments  |        |

|     |       |          | alization of location counters of absolute segments     |        |

|     | 4.6.2 |          | ng Location Counter Values                              |        |

|     | 4.6.3 |          | g Location Counter Values                               |        |

| 4.7 | Condi |          | sembly and Macros                                       |        |

|     | 4.7.1 | -        | onditional Assembly                                     |        |

|     |       |          | IF Directive                                            |        |

|     |       |          | IFDEF Directive                                         |        |

|     |       |          | IFNDEF Directive                                        |        |

|     | 4.7.2 | 0        | Iacros                                                  |        |

| 4.8 | Progr |          | ents                                                    |        |

|     | 4.8.1 |          | er Set                                                  |        |

|     |       | 4.8.1.1  | Letters, Digits, Underscore, Question Mark, Dollar Sign |        |

|     |       | 4.8.1.2  | White Space                                             |        |

|     |       | 4.8.1.3  | Line Feed Code, Carriage Return Code                    |        |

|     |       | 4.8.1.4  | Special Characters                                      |        |

|     |       | 4.8.1.5  | Operators                                               |        |

|     |       | 4.8.1.6  | Escape Sequences                                        | . 4-49 |

|     | 4.8.2 | Constan  | ts                                                      |        |

|     |       | 4.8.2.1  | Integer Constants                                       |        |

|     |       | 4.8.2.2  | Address Constants                                       |        |

|     |       | 4.8.2.3  | Character Constants                                     |        |

|     |       | 4.8.2.4  | String Constants                                        |        |

|     | 4.8.3 | Symbols  | S                                                       |        |

|     |       | 4.8.3.1  | User Symbols                                            | . 4-55 |

|     |       |          | (1) Absolute Symbols                                    |        |

|     |       |          | (2) Relocatable Symbols                                 | . 4-58 |

|     |       |          | (3) Referring User Symbols                              | . 4-62 |

|     |       |          | (4) Referring User Symbols From Multiple Source Files   |        |

|     |       |          | (5) Macro Symbols                                       | . 4-63 |

|     |       | 4.8.3.2  | Reserved Words                                          | . 4-63 |

|     |       |          | (1) Instructions                                        |        |

|     |       |          | (2) Directives                                          | . 4-64 |

|     |       |          | (3) Registers                                           |        |

|     |       |          | (4) Operators                                           |        |

|     |       |          | (5) Fixed microcontroller addresses                     |        |

|     |       |          | (6) Local register addresses                            |        |

|     |       |          | (7) Pointing register addresses                         | . 4-65 |

|     |       |          | (8) Addressing specifiers                               |        |

|     |       |          | (9) Special operands of instructions                    | . 4-65 |

|     |       |          | (10) Special operands of directives                     | . 4-65 |

|     | 4.8.4 | Location | n Counter Symbol                                        | . 4-66 |

|     | 4.8.5 | Value A  | .ttributes                                              |        |

|     |       | 4.8.5.1  | Numeric Values and Address Values                       | . 4-67 |

|     |       | 4.8.5.2  | Usage Types and Physical Segment Attributes             | . 4-68 |

|     |       |          | (1) Usage Types                                         | . 4-68 |

|     |       |          | (2) Physical Segment Attributes                         | . 4-68 |

|     |       | 4.8.5.3  | Flag Attributes                                         | . 4-73 |

|     |       | 4.8.5.4  | Addressing Attributes                                   | . 4-74 |

|   | -      |          | Expressions                                                                                                                   |        |

|---|--------|----------|-------------------------------------------------------------------------------------------------------------------------------|--------|

|   | 4.9.1  | Basic Co | oncepts Of Expressions                                                                                                        | . 4-76 |

|   |        | 4.9.1.1  |                                                                                                                               |        |

|   |        | 4.9.1.2  | Using Physical Segment Addresses                                                                                              | . 4-78 |

|   |        | 4.9.1.3  | Unresolved Expressions During Assembly                                                                                        | . 4-79 |

|   | 4.9.2  | Operator | rs                                                                                                                            | . 4-80 |

|   |        | 4.9.2.1  | Arithmetic Operators                                                                                                          | . 4-80 |

|   |        | 4.9.2.2  | Logical Operators                                                                                                             | . 4-81 |

|   |        | 4.9.2.3  | Bitwise Logical Operators                                                                                                     |        |

|   |        | 4.9.2.4  | Relational Operators                                                                                                          |        |

|   |        | 4.9.2.5  | Dot Operator                                                                                                                  |        |

|   |        | 4.9.2.6  | Special Operators                                                                                                             |        |

|   | 4.9.3  | Expressi | ion Types                                                                                                                     |        |

|   |        | 4.9.3.1  | Constant Expressions                                                                                                          |        |

|   |        | 4.9.3.2  | Simple Expressions                                                                                                            |        |

|   |        | 4.9.3.3  | General Expressions                                                                                                           |        |

|   |        | 4.9.3.4  | Restrictions On Coding Expressions                                                                                            |        |

|   |        | 119.511  | (1) Restrictions On ORG Directive Operands                                                                                    |        |

|   |        |          | (2) Restrictions On Operands Of Directive Spectrules                                                                          |        |

|   |        |          | That Define Local Symbols                                                                                                     | 4-95   |

|   |        |          | (3) Restrictions On Operands Of Other Directives                                                                              |        |

|   |        |          | (4) Restrictions On Microcontroller Instruction Operands                                                                      |        |

|   | 4.9.4  | Express  | ion Evaluation                                                                                                                |        |

|   | т.).т  | 4.9.4.1  | Operator Precedence                                                                                                           |        |

|   |        | 4.9.4.2  | Evaluation Of Expression Values                                                                                               |        |

|   |        | 4.9.4.3  | Evaluation Of Expression Values                                                                                               |        |

|   |        | 4.9.4.3  | (1) Attributes of Parentheses ( )                                                                                             |        |

|   |        |          | <ul><li>(1) Attributes of Latentheses (1)</li><li>(2) Attribute Evaluation of Operators + and</li></ul>                       |        |

|   |        |          | (2) Attribute Evaluation of Operators + and                                                                                   |        |

|   |        |          | (4) Attribute Evaluation of Logical Operators                                                                                 |        |

|   |        |          | <ul><li>(4) Attribute Evaluation of Edgical Operators</li><li>(5) Attribute Evaluation of Bitwise Logical Operators</li></ul> |        |

|   |        |          | (6) Attribute Evaluation of Relational Operators                                                                              |        |

|   |        |          | (7) Attribute Evaluation of Dot Operator                                                                                      |        |

|   |        |          | <ul><li>(7) Attribute Evaluation of Dot Operator</li></ul>                                                                    |        |

| • | Chook  | Function | (8) Autobute Evaluation of Special Operators                                                                                  |        |

|   |        |          | l Value Checks                                                                                                                |        |

|   |        |          | 1 Counter Value Checks                                                                                                        |        |

|   |        |          | ype Checks                                                                                                                    |        |

|   |        | -        | Segment Address Checks                                                                                                        |        |

|   | 4.10.4 |          | Checks                                                                                                                        |        |

|   |        |          |                                                                                                                               |        |

|   |        |          | Checks                                                                                                                        |        |

|   | 4 10 5 |          | Checks                                                                                                                        |        |

|   |        |          | oundary Checks                                                                                                                |        |

|   |        | -        | Function Register Access Checks                                                                                               |        |

|   |        |          | Page Checks                                                                                                                   |        |

|   |        | -        | Memory Space Write Checks                                                                                                     |        |

|   | 4.10.9 |          | ribute Checks                                                                                                                 |        |

|   |        |          | Attribute Checks of Instructions Affected By Flags                                                                            |        |

|   |        | -        | Attribute Checks of Branch Instructions                                                                                       |        |

|   |        |          | odes                                                                                                                          | 4-118  |

|         | 4.11.1.1  | Immediate Addressing                                                                                                             | 4-121  |

|---------|-----------|----------------------------------------------------------------------------------------------------------------------------------|--------|

|         | 4.11.1.2  | Rotate/Shift Addressing                                                                                                          | 4-121  |

| 4.11.2  | RAM Ac    | ldressing                                                                                                                        | 4-122  |

|         | 4.11.2.1  | Register Addressing                                                                                                              | 4-122  |

|         |           | (1) Accumulator Addressing                                                                                                       | 4-122  |

|         |           | (2) Control Register Addressing                                                                                                  | 4-122  |

|         |           | (3) Pointing Register Addressing                                                                                                 | 4-123  |

|         |           | (4) Local Register Addressing                                                                                                    |        |

|         |           | (5) Register Sets                                                                                                                |        |

|         | 4.11.2.2  | Page Addressing                                                                                                                  |        |

|         |           | (1) SFR Page Addressing                                                                                                          |        |

|         |           | (2) Fixed Page Addressing                                                                                                        |        |

|         |           | (3) Current Page Addressing                                                                                                      |        |

|         |           | (4) Fixed Page SBA Area Addressing                                                                                               |        |

|         |           | (5) Current Page SBA Area Addressing                                                                                             |        |

|         | 4.11.2.3  | Direct Addressing                                                                                                                |        |

|         |           | (1) Direct Data Addressing                                                                                                       |        |

|         | 4.11.2.4  | Pointing Register Indirect Addressing                                                                                            |        |

|         |           | (1) DP/X1 Indirect Addressing                                                                                                    |        |

|         |           | (2) Indirect Addressing With Post-Increment                                                                                      |        |

|         |           | <ul><li>(2) Indirect Addressing With Post-Decrement</li></ul>                                                                    |        |

|         |           | (4) DP/USP Indirect Addressing With 7-Bit Displacement                                                                           |        |

|         |           | <ul> <li>(1) D1/OST Indirect Addressing With 7 Displacement.</li> <li>(5) X1/X2 Indirect Addressing With 16-Bit Base.</li> </ul> |        |

|         |           | (6) X1 Indirect Addressing With 8-Bit Register Displacement                                                                      |        |

| 4 11 3  | Table Da  | ata Addressing                                                                                                                   |        |

| 4.11.5  |           | Direct Addressing                                                                                                                |        |

|         | 7.11.3.1  | (1) Direct Table Addressing                                                                                                      |        |

|         | 11132     | Indirect Addressing                                                                                                              |        |

|         | 7.11.3.2  | (1) RAM Addressing Indirect Table Addressing                                                                                     |        |

|         |           | <ul><li>(1) RAM Addressing Indirect Fabre Addressing</li></ul>                                                                   |        |

| A 11 A  | Drogram   | Code Addressing                                                                                                                  |        |

| 7.11.7  |           | Direct Addressing                                                                                                                |        |

|         | 7.11.7.1  | (1) Near Code Addressing                                                                                                         |        |

|         |           | (2) Far Code Addressing                                                                                                          |        |

|         | 11112     | Relative Addressing                                                                                                              |        |

|         | 4.11.4.2  | (1) Relative Code Addressing                                                                                                     |        |

|         | 11113     | Special Code Addressing For Particular Instructions                                                                              |        |

|         |           | (1) ACAL Code Addressing                                                                                                         |        |

|         |           |                                                                                                                                  |        |

|         | 1 1 1 1 1 | (2) VCAL Code Addressing                                                                                                         |        |

|         | 4.11.4.4  | Indirect Addressing                                                                                                              |        |

| 4 1 1 5 | DOMW      | (1) RAM Addressing Indirect Code Addressing                                                                                      |        |

| 4.11.5  | KOM W     | indow Addressing                                                                                                                 | 4-144  |

| 4.11.0  |           | ng For nX-8/100 to nX-8/400                                                                                                      |        |

|         |           | Zero Page Addressing                                                                                                             |        |

| 4 1 1 7 |           | USP Indirect Addressing With Pre-Increment                                                                                       |        |

| 4.11.7  |           | ation Of Addressing                                                                                                              | 4-14/  |

|         | 4.11.7.1  | Optimization Of RAM Address Specifications                                                                                       | 4 1 47 |

|         | 4 1 1 7 2 | Without Addressing Specifiers                                                                                                    | 4-147  |

|         | 4.11.7.2  | Optimization Of RAM Address Specifications                                                                                       | 4 1 40 |

|         |           | With The Addressing Specifier \                                                                                                  | 4-149  |

| 4.12 | Directiv | ves                                                         | 4-150 |

|------|----------|-------------------------------------------------------------|-------|

|      | 4.12.1   | DCL File Specification (TYPE)                               | 4-150 |

|      | 4.12.2   | Memory Model Specification (MODEL)                          | 4-151 |

|      | 4.12.3   | COMMON Area Specification (COMMON)                          | 4-153 |

|      | 4.12.4   | ROM Window Area Specification (WINDOW)                      | 4-154 |

|      | 4.12.5   | Local Symbol Definition (EQU, SET)                          | 4-155 |

|      | 4.12.6   | Definition of Local Symbols That Represent Addresses        |       |

|      |          | (CODE, CBIT, DATA, BIT, EDATA, EBIT)                        | 4-157 |

|      | 4.12.7   | Absolute Segment Definition                                 |       |

|      |          | (CSEG, DSEG, BSEG, ESEG, EBSEG)                             | 4-163 |

|      | 4.12.8   | Using Relocatable Symbols                                   | 4-168 |

|      |          | 4.12.8.1 Segment Symbol Definition (SEGMENT)                | 4-168 |

|      |          | 4.12.8.2 Stack Segment Definition (STACKSEG)                | 4-173 |

|      |          | 4.12.8.3 Relocatable Segment Definition (RSEG)              | 4-174 |

|      | 4.12.9   | Segment Group Definition (GROUP)                            | 4-176 |

|      | 4.12.10  | Location Counter Setting (ORG)                              | 4-178 |

|      | 4.12.11  | Memory Allocation (DS, DBIT)                                | 4-180 |

|      | 4.12.12  | Program Memory Initialization (DB, DW)                      | 4-181 |

|      | 4.12.13  | Creating Programs From Multiple Source Files                | 4-183 |

|      |          | 4.12.13.1 Public Symbol Declaration (PUBLIC)                | 4-184 |

|      |          | 4.12.13.2 External Symbol Declaration (EXTRN)               | 4-185 |

|      |          | 4.12.13.3 Communal Symbol Declaration (COMM)                | 4-187 |

|      |          | 4.12.13.4 Using Public, External, And Communal Symbols      | 4-188 |

|      |          | (1) Referring Public Symbols With External Symbols          | 4-189 |

|      |          | (2) Using Communal Symbols In Multiple Source Files         |       |

|      |          | (3) Referring Communal Symbols With External Symbols        |       |

|      |          | 4.12.13.5 Using Partial Segments                            | 4-192 |

|      | 4.12.14  | Assumption And Checks Of Program State (USING)              | 4-194 |

|      |          | 4.12.14.1 Assumption Of Physical Segment Address            |       |

|      |          | In Data Memory Space (USING DSREG)                          | 4-195 |

|      |          | 4.12.14.2 Assumption Of Physical Segment Address            |       |

|      |          | In Program Memory Space (USING TSREG)                       |       |

|      |          | 4.12.14.3 Assumption Of Current Page (USING PAGE)           |       |

|      |          | 4.12.14.4 Assumption Of Data Descriptor (USING DATA)        |       |

|      |          | 4.12.14.5 Assumption Of Stack Flag (USING OPRT)             |       |

|      |          | 4.12.14.6 Flag Attribute Checks Of Branch Instruction (CHK) | 4-206 |

|      |          | 4.12.14.7 Assumption Of Pointing Register Set Bank Number   |       |

|      |          | (USING PREG)                                                | 4-208 |

|      |          | 4.12.14.8 Assumption Of Local Register Set Bank Number      |       |

|      |          | (USING LREG)                                                |       |

|      | 4.12.15  |                                                             |       |

|      | 4.12.16  |                                                             |       |

|      | 4.12.17  |                                                             |       |

|      | 4.12.18  | Register Bank Declarations                                  | 4-214 |

|      |          | 4.12.18.1 Pointing Register Bank Declaration                |       |

|      |          | (PRBANK, NOPRBANK)                                          | 4-214 |

|      |          | 4.12.18.2 Local Register Bank Declaration                   |       |

|      |          | (LRBANK, NOLRBANK)                                          |       |

|      | 4.12.19  |                                                             |       |

|      |          | 4.12.19.1 Conditional Assembly On Expression Value (IF)     | 4-217 |

|      |         | 4.12.19.2  | Conditional Assembly On Symbol Definition            |       |

|------|---------|------------|------------------------------------------------------|-------|

|      |         |            | Or Non-Definition (IFDEF, IFNDEF)                    | 4-218 |

|      | 4.12.20 | Macro De   | finition (DEFINE)                                    | 4-219 |

|      | 4.12.21 | C Source I | Level Debug Information (CFILE, CFUNCTION, CLINE)    | 4-220 |

|      | 4.12.22 |            | ion Of Branch Instructions                           | 4-221 |

|      |         | 4.12.22.1  | Optimization Of Jump Instructions (GJMP)             | 4-221 |

|      |         | 4.12.22.2  | Optimization Of Call Instructions (GCAL)             | 4-222 |

|      | 4.12.23 | Print File | Control                                              | 4-223 |

|      |         | 4.12.23.1  | Print File Output Control (PRN, NOPRN)               | 4-223 |

|      |         | 4.12.23.2  | Force Page Break (PAGE without operand)              | 4-224 |

|      |         | 4.12.23.3  | Lines Per Page and Characters Per Line Specification |       |

|      |         |            | (PAGE with operands)                                 | 4-225 |

|      |         | 4.12.23.4  | Title Specification (TITLE)                          | 4-226 |

|      |         | 4.12.23.5  | Date Specification (DATE)                            |       |

|      |         | 4.12.23.6  | Assembly List Output Control (LIST, NOLIST)          |       |

|      |         | 4.12.23.7  | Symbol List Output Control (SYM, NOSYM)              |       |

|      |         | 4.12.23.8  | Cross-Reference List Output Control (REF, NOREF)     |       |

|      |         | 4.12.23.9  | Tab Code Replacement (TAB)                           |       |

|      | 4.12.24 | Object Fil | e Control                                            |       |

|      |         | 4.12.24.1  | Object File Output Control (OBJ, NOOBJ)              | 4-231 |

|      |         | 4.12.24.2  | Assembly Level Debugging Information Output Control  |       |

|      |         |            | (DEBUG, NODEBUG)                                     |       |

|      |         |            | sage Output Control (ERR, NOERR)                     |       |

| 4.13 |         |            |                                                      |       |

|      | 4.13.1  |            | ead Assembly Lists                                   |       |

|      | 4.13.2  |            | ead Cross-Reference Lists                            |       |

|      | 4.13.3  |            | ead Symbol Lists                                     |       |

|      |         | 4.13.3.1   | Symbol Information                                   |       |

|      |         | 4.13.3.2   | Segment Information                                  |       |

|      |         | 4.13.3.3   | Segment Group Information                            | 4-241 |

|      | 4.13.4  |            | ead Termination Messages                             |       |

| 4.14 |         |            | on Files                                             |       |

|      | 4.14.1  |            | f EXTRN Declaration Files                            |       |

|      | 4.14.2  |            | TRN Declaration Files                                |       |

| 4.15 |         | 0          |                                                      |       |

|      | 4.15.1  |            | Error Messages                                       |       |

|      | 4.15.2  |            | ror Messages                                         |       |

|      |         | 4.15.2.1   | Fatal Error Messages                                 |       |

|      |         | 4.15.2.2   | Assembler Error Messages                             |       |

|      |         | 4.15.2.3   | Warning Messages                                     |       |

|      |         | 4.15.2.4   | Internal Processing Error Messages                   | 4-260 |

# Chapter 5. RL66K

| 5.1 | Introduction |                      |     |  |  |

|-----|--------------|----------------------|-----|--|--|

| 5.2 | Memo         | bry Space Management | 5-2 |  |  |

|     |              | Program Memory Space |     |  |  |

|     |              | Data Memory Space    |     |  |  |

|     |              | EEPROM Space         |     |  |  |

|     |              | Dual Port RAM Space  |     |  |  |

| 5.3 | Using  | RL66K           |                                                                 | 5-4  |

|-----|--------|-----------------|-----------------------------------------------------------------|------|

|     | 5.3.1  | Comman          | nd Line Format                                                  | 5-4  |

|     |        | 5.3.1.1         | object_files Field                                              | 5-5  |

|     |        | 5.3.1.2         | absolute_file Field                                             | 5-6  |

|     |        | 5.3.1.3         | map_file Field                                                  | 5-6  |

|     |        | 5.3.1.4         | libraries Field                                                 | 5-7  |

|     |        | 5.3.1.5         | Command Examples                                                | 5-7  |

|     | 5.3.2  | Executio        | n                                                               | 5-8  |

|     |        | 5.3.2.1         | Prompt-Based Input                                              | 5-8  |

|     |        | 5.3.2.2         | Specifying Response File Input                                  | 5-9  |

|     | 5.3.3  | Terminat        | tion Code                                                       | 5-11 |

| 5.4 | RL66F  | <b>COptions</b> | S                                                               | 5-12 |

|     | 5.4.1  | Option S        | pecifications                                                   | 5-12 |

|     |        | 5.4.1.1         | Syntax                                                          | 5-12 |

|     |        | 5.4.1.2         | Usage                                                           | 5-12 |

|     |        | 5.4.1.3         | Name Arguments                                                  | 5-12 |

|     |        | 5.4.1.4         | Value Arguments                                                 | 5-13 |

|     | 5.4.2  | List Of C       | Dptions                                                         | 5-14 |

|     | 5.4.3  | Option U        | Jse                                                             | 5-15 |

|     |        | 5.4.3.1         | Assembly Level Debugging Information Output Control (/D, /ND)   | 5-15 |

|     |        | 5.4.3.2         | Map File Data Output Control (/S, /NS)                          | 5-15 |

|     |        | 5.4.3.3         | CODE Segment Allocation Control (/CODE)                         | 5-16 |

|     |        | 5.4.3.4         | DATA Segment Allocation Control (/DATA)                         | 5-19 |

|     |        | 5.4.3.5         | BIT Segment Allocation Control (/BIT)                           |      |

|     |        | 5.4.3.6         | EDATA Segment Allocation Control (/EDATA)                       | 5-21 |

|     |        | 5.4.3.7         | EBIT Allocation Control (/EBIT)                                 | 5-22 |

|     |        | 5.4.3.8         | Segment Allocation Order Control (/ORDER)                       | 5-23 |

|     |        | 5.4.3.9         | Program Memory Space Maximum Address Setting (/CM)              | 5-24 |

|     |        | 5.4.3.10        | Data Memory Space Maximum Address Setting (/DM)                 | 5-24 |

|     |        | 5.4.3.11        | Emulation Library Automatic Search (/CC)                        | 5-25 |

|     |        | 5.4.3.12        | C Source Level Debugging Information Output Control (/SD, /NSD) | 5-25 |

|     |        | 5.4.3.13        | Stack Segment Size Change (/STACK)                              | 5-25 |

|     |        | 5.4.3.14        | ABL File Generation Control (/A, /NA)                           | 5-26 |

| 5.5 | Link P | rocessing       | g                                                               | 5-27 |

|     | 5.5.1  | Global S        | ymbol Matching                                                  | 5-27 |

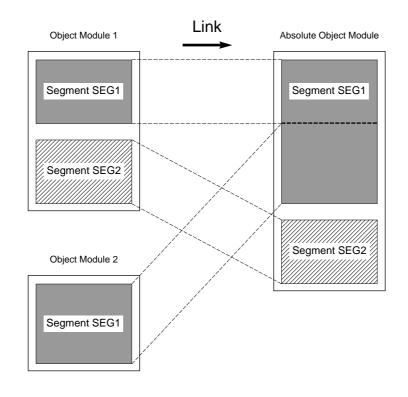

|     | 5.5.2  | Segment         | Linking                                                         | 5-27 |

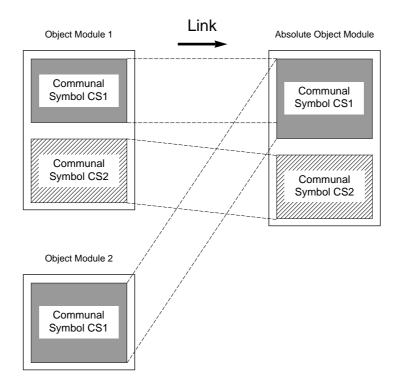

|     | 5.5.3  | Commun          | nal Symbol Linking                                              | 5-30 |

|     | 5.5.4  | Segment         | Allocation                                                      | 5-31 |

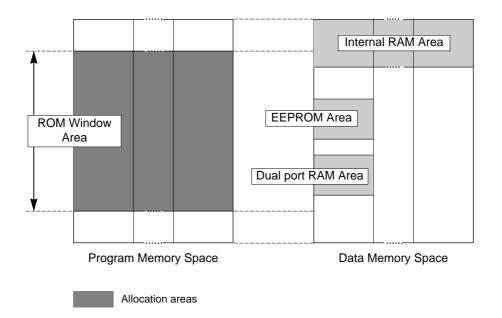

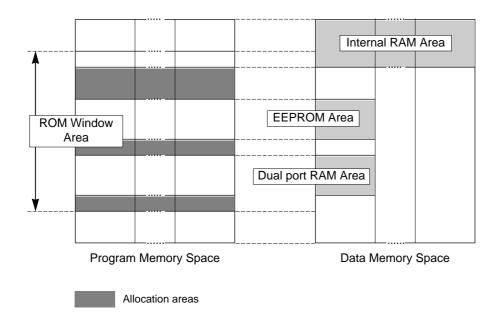

|     |        | 5.5.4.1         | Allocation Spaces And Areas                                     | 5-32 |

|     |        | 5.5.4.2         | Quasi-Segments                                                  | 5-35 |

|     |        | 5.5.4.3         | Allocation Precedence                                           | 5-36 |

|     | 5.5.5  | Segment         | Groups                                                          | 5-40 |

|     | 5.5.6  | Reservin        | g The Stack Area                                                | 5-40 |

|     |        | 5.5.6.1         | Stack Segment (\$STACK)                                         | 5-40 |

|     |        | 5.5.6.2         | Stack Symbol (_\$\$SSP)                                         | 5-40 |

|     | 5.5.7  | Fix-Up F        | Processing                                                      | 5-41 |

| 5.6 | Map F  | 'ile            | -                                                               | 5-42 |

| 5.7 | RL66F  |                 | es                                                              |      |

|     | 5.7.1  |                 | s Indicating Processing Status                                  |      |

|     | 5.7.2  |                 | essage Format                                                   |      |

|     | 5.7.3  | Error Me        | essage Redirection                                              | 5-51 |

|     |        |                 |                                                                 |      |

| 5.7.4 | List Of Error Messages 5-5         |                             |  |

|-------|------------------------------------|-----------------------------|--|

|       |                                    | Command Line Error Messages |  |

|       |                                    | Fatal Error Messages        |  |

|       |                                    | Error Messages              |  |

|       |                                    | Warning Messages            |  |

| 5.7.5 | Internal Processing Error Messages |                             |  |

# Chapter 6. LIB66K

| 6.1        | Intro | luction                                         | 6-1  |

|------------|-------|-------------------------------------------------|------|

|            | 6.1.1 | LIB66K Functions                                | 6-1  |

|            | 6.1.2 | Advantages Of Using LIB66K                      | 6-2  |

|            | 6.1.3 | Differences Between File Names And Module Names | 6-2  |

| 6.2        | Execu | ting LIB66K                                     | 6-3  |

|            | 6.2.1 | Command Line Execution                          | 6-3  |

|            |       | (1) <i>library_file</i> Field                   | 6-4  |

|            |       | (2) operations Field                            | 6-5  |

|            |       | (3) <i>list_file</i> Field                      | 6-6  |

|            |       | (4) <i>output_library_file</i> Field            |      |

|            |       | (5) Options                                     |      |

|            | 6.2.2 | Prompt-Based Execution                          |      |

|            | 6.2.3 | Using Command Line And Prompts Together         |      |

|            | 6.2.4 | Redirection                                     |      |

|            | 6.2.5 | Redirecting Output Messages                     |      |

|            | 6.2.6 | Termination Code                                |      |

| 6.3        |       | 5K Operations                                   |      |

|            | 6.3.1 | Creating New Libraries                          |      |

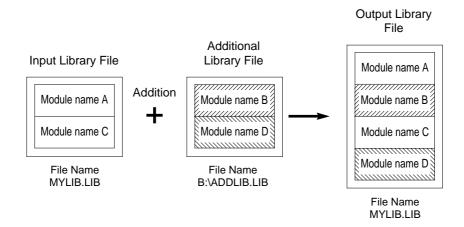

|            | 6.3.2 | Adding Modules                                  |      |

|            | 6.3.3 | Adding Library Files                            |      |

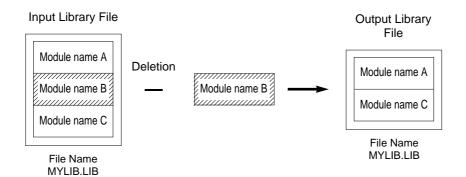

|            | 6.3.4 | Deleting Modules                                |      |

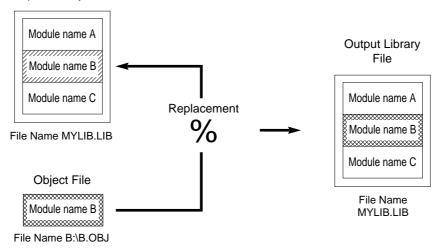

|            | 6.3.5 | Replacing Modules                               |      |

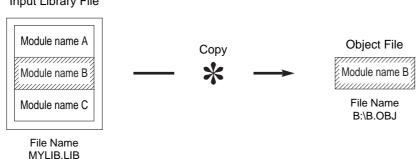

|            | 6.3.6 | Copying Modules                                 |      |

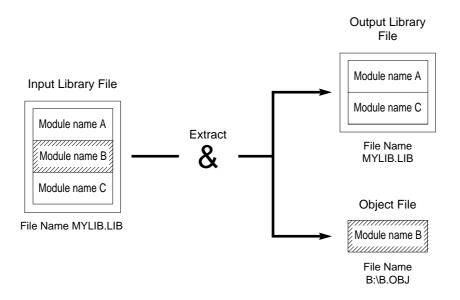

|            | 6.3.7 | Extracting Modules                              |      |

|            | 6.3.8 | Operation Precedence                            |      |

|            | 6.3.9 | Cautions During Execution                       |      |

|            |       | (1) Disk Capacity                               |      |

| <i>.</i> . |       | (2) Temporary Files                             |      |

| 6.4        |       | ile Format                                      |      |

| 6.5        |       | Messages                                        |      |

|            | 6.5.1 | Error Message Format                            |      |

|            | 6.5.2 | Fatal Error Messages                            |      |

|            | 6.5.3 | Error Messages                                  |      |

|            | 6.5.4 | Warning Messages                                | 6-29 |

# Chapter 7. OH66K

| 7.1 | Introduction                  | 1 |

|-----|-------------------------------|---|

| 7.2 | Using OH66K                   | ; |

|     | 7.2.1 Command Line Conversion |   |

|     |         | (1) <i>object_file</i> Field   | 7-3  |

|-----|---------|--------------------------------|------|

|     |         |                                |      |

|     |         | (2) <i>hex_file</i> Field      |      |

|     |         | (3) Options                    | 7-5  |

|     | 7.2.2   | Prompt-Based Conversion        | 7-6  |

|     | 7.2.3   | Redirecting Output Messages    | 7-7  |

|     | 7.2.4   | Termination Code               | 7-7  |

| 7.3 | Files U | Jsed With OH66K                |      |

|     | 7.3.1   | Input Files                    | 7-8  |

|     | 7.3.2   | Output Files                   |      |

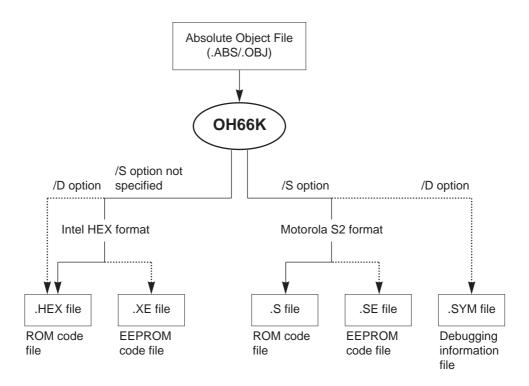

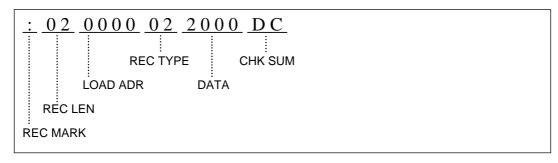

|     |         | (1) Intel HEX Files            | 7-9  |

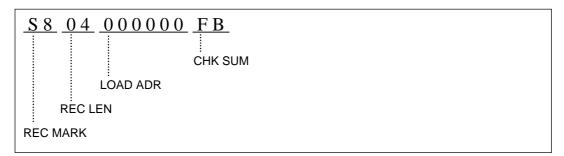

|     |         | (2) S2 Format Files            | 7-11 |

|     |         | (3) Debugging Information      | 7-13 |

|     | 7.3.3   | Input And Output File Examples |      |

|     | 7.3.4   | Temporary Files                | 7-18 |

| 7.4 | Error   | Messages                       | 7-19 |

|     | 7.4.1   | Error Message Format           | 7-19 |

|     | 7.4.2   | Fatal Error Messages           |      |

# **Chapter 8.** Absolute Print File Generation

| 8.1 | Introduction                                       | 8-1 |

|-----|----------------------------------------------------|-----|

| 8.2 | Absolute Print File Generation Procedure           | 8-1 |

| 8.3 | Link Processing For Absolute Print File Generation | 8-3 |

| 8.4 | Re-Assembly For Absolute Print File Generation     | 8-4 |

| 8.5 | Re-Assembly Errors                                 | 8-6 |

| 8.6 | If Fatal Error 11 Occurs                           | 8-7 |

# Appendices

| Appendix A. | List Of Directives     | A-1 |

|-------------|------------------------|-----|

| Appendix B. | List Of Reserved Words | A-5 |

# Chapter 1

# Introduction

The MAC66K Assembler Package is software for developing OLMS-66K Series assembly language programs.

This manual describes the following software in the MAC66K Assembler Package:

| Relocatable Assembler | RAS66K |

|-----------------------|--------|

| Linker                | RL66K  |

| Librarian             | LIB66K |

| Object Converter      | OH66K  |

This chapter explains various information needed to read the rest of the manual. Read this chapter first before moving on to other chapters.

### 1.1 About The MAC66K Assembler Package

Thank you for your purchase of the MAC66K Assembler Package. This package contains software needed to create assembly language programs for the one-chip microcontroller OLMS-66K Series.

#### • Package Contents

- 1 Floppy Disk

- 1 MAC66K Assembler Package User's Manual (this manual)

- 1 Macroprocessor MP User's Manual

The floppy disk contains the following software.

#### • Software

#### **Relocatable Assembler RAS66K**

RAS66K generates an object file from a source file coded in assembly language. The object file will contain object code corresponding to the source file, as well as information needed for linking and debugging. RAS66K also generates a print file and error file.

#### Linker RL66K

RL66K links one or more object modules and generates a single absolute object file. It also generates a map file, which shows public symbols and segment allocation.

#### Librarian LIB66K

LIB66K is software for creating and managing library files. A library file is a single grouping of multiple object files which are used by RL66K.

#### **Object Converter OH66K**

OH66K converts an absolute object file generated by RL66K or RAS66K into a HEX file.

#### Macroprocessor MP

MP is software that parses macros coded in a source file and expands them to corresponding text.

# **1.2 System Requirements**

The MAC66K Assembler Package software requires the following environment to operate.

| Operating system | : | MS-DOS (version 3.1 or higher)   |

|------------------|---|----------------------------------|

| Host computer    | : | Personal computer running MS-DOS |

| Free memory      | : | At least 180 Kbytes              |

In the explanations to follow, MS-DOS is referred to simply as DOS.

### 1.3 About This Manual

This manual describes the software in the MAC66K Assembler Package. However, for MP refer to the Macroprocessor MP User's Manual.

This manual assumes that the reader is familiar with assembly language and DOS, and that he can create and edit assembly language source files. This manual is not an introductory text.

An overview of each chapter is given below.

#### **Chapter 1. Introduction**

Chapter 1 is this chapter.

#### Chapter 2. Installation And Usage

Chapter 2 explains how to install the MAC66K Assembler Package and provides an overview of program development.

#### Chapter 3. Basic Programming Knowledge

Chapter 3 discusses basic knowledge needed to develop programs with the MAC66K Assembler Package.

#### Chapter 4. RAS66K

Chapter 4 explains how to use the relocatable assembler RAS66K and describes RAS66K assembly language.

#### Chapter 5. RL66K

Chapter 5 explains how to use the linker RL66K.

#### Chapter 6. LIB66K

Chapter 6 explains how to use the librarian LIB66K.

#### Chapter 7. OH66K

Chapter 7 explains how to use the object converter OH66K.

#### Chapter 8. Absolute Print File Generation

Chapter 7 explains how to generate absolute print files.

#### Appendices

The appendices provide charts of directives, and reserved words.

### **1.4 Related Documents**

In addition to this manual, the MAC66K Assembler Package provides the following separate documents. Refer to them as needed.

• Macroprocessor MP User's Manual

Manual for the macroprocessor MP.

• MAC66K.DOC

Text file containing recent information not included in this manual.

• DCL66K.DOC

Text file containing an explanation of DCL files used by RAS66K.

MAC66K.DOC and DCL66K.DOC are text-format files on the provided floppy disk. They can be referred with the DOS TYPE command or with your own editor.

In addition to the above documents, the MAC66K Assembler Package also contains some related documents. These related documents may be a microcontroller hardware manual, an instruction manual, an emulator or simulator manual for use in debugging, etc. The MAC66K.DOC file describes which related documents are included, so please refer to it.

Points in this manual where you should refer to these related documents will be indicated by "Please refer to related documents."

### 1.5 CPU Core

OLMS-66K one-chip microcontrollers are constructed from common CPUs with different I/O peripherals and different memory capacities.

The common CPU is called the CPU core, or simply the core. Multiple CPU cores exist in the OLMS-66K Series. Refer to MAC66K.DOC for the most recent information about devices and their CPU cores.

#### • Examples in this manual

The explanations of this manual include numerous program examples. These examples use OLMS-66K Series microcontroller instructions. Note that these may not be usable with your target microcontroller. You can confirm which instructions are usable with which CPU core by checking Appendix B, "List Of Reserved Words."

# 1.6 Symbol Usage In This Manual

To make explanations easier to understand, this manual makes use of several types of symbols. The symbols and their meanings are listed below.

| Symbol                                | Explanation                                                                                                                                                                                                 |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SAMPLE                                | These characters indicate messages displayed to the screen, command line input examples, or examples of generated list files.                                                                               |

| CAPITALS                              | Upper-case letters indicate that the characters should be input as shown.                                                                                                                                   |

| italics                               | Italics indicate that the characters should not be input as shown, but instead that they should be substituted with needed information.                                                                     |

| [ ]                                   | The contents of brackets are input as needed. They may be omitted.                                                                                                                                          |

|                                       | The contents immediately preceding the ellipses may be repeated as necessary.                                                                                                                               |

| {choice1 choice2}                     | The braces contain choices separated by vertical bars, one of which should<br>be input. Unless the choices are enclosed by brackets [], one of them must<br>be input.                                       |

| value1 to value2<br>Ctrl+C<br>PROGRAM | The value will be equal to or between <i>value 1</i> and <i>value 2</i> .<br>Press the "Ctrl" key and "C" key simultaneously.<br>A vertical line of dots indicates a partial omission of a program example. |

| ·<br>·                                |                                                                                                                                                                                                             |

| PROGRAM                               |                                                                                                                                                                                                             |

When an "H" is appended to the end of a number in this manual, that value will be hexadecimal. For example, 1234H will indicate the hexadecimal 1234.

### 1.7 Changes From Previous MAC66K Assembler Package Ver. 2.XX

This manual explains the use of MAC66K Assembler Package Ver.4.XX. The MAC66K Assembler Package Ver. 4.XX is software that supports all devices in the OLMS-66K Series, or in other words, supports all CPU cores nX-8/100, 200, 300, 400, and 500. It is an upgrade from the MAC66K Assembler Package Ver. 2.XX, which supported the nX-8/200, 300, and 400 cores.

This section describes the changes and additions to the previous version (Ver. 2.XX) for its users. New users who are starting with the latest version (Ver. 4.XX) may skip this section.

The major changes and additions to the previous version (Ver. 2.XX) are as follows.

#### • nX-8/100 and 500 core support

Ver. 4.XX adds new support for the CPU cores nX-8/100 and 500. Assembly language specifications that woud not clearly support the complex architecture of the nX-8/500 core have been clarified. Therefore the check functions of RAS66K and RL66K have been strengthened.

#### • Object file format changes

The format of object files has changed. Accordingly, object files generated by the previous version of RAS66K cannot be linked with the new version of RL66K or converted to HEX files with the new version of OH66K. Creation and management of libraries using LIB66K is still the same.

The following sections explain the changes and additions to the previous versions of each software in the package (RAS66K, RL66K, OH66K, LIB66K). The old version of the software is expressed as "old *xxx*" and the new version as "new *xxx*."

#### 1.7.1 RAS66K

#### ■ Starting RAS66K

The new RAS66K supports only the following format of starting command line.

RAS66K source\_file [options]

The following input will display RAS66K usage and terminate.

RAS66K

#### Options

The format of old RAS66K options was the same as for directives, but new RAS66K options are specified as a slash (/) followed by a one or two-character specification. For example, to generate a cross-reference list and symbol list, input the following.

RAS66K foo /S /R

In addition, the following options have been added.

| /W [type]       | Perform warning checks of the specified type.                                                                                                 |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| /NW [type]      | Disable warning checks of the specified type.                                                                                                 |

| /CD             | Recognize upper-case and lower-case distinctions.                                                                                             |

| /NCD            | Ignore upper-case and lower-case distinctions.                                                                                                |

| /CC             | Read C source level debugging information file.                                                                                               |

| /Iinclude_path  | Specifies include file path.                                                                                                                  |

| /V[buffer_size] | When source file is read, save it in a memory buffer of <i>buffer_size</i> bytes. This speeds up assembly during floppy disk-based operation. |

| /X              | Generate an EXTRN declaration file.                                                                                                           |

For details, refer to Section 4.3.2, "Option Specifications."

#### **DCL file search order and search locations**

The old RAS66K searched for DCL files in the following order.

- 1. Current directory

- 2. Directory specified by PATH environment variable

However, the new RAS66K searches in the order below.

- 1. Current directory

- 2. Directory containing RAS66K.EXE

- 3. Directory specified by DCL environment variable

#### Print file format

Print file format has changed. Refer to Section 4.13, "Print Files," for the new RAS66K print file format.

#### **EXTRN declaration files**

The new RAS66K can generate an EXTRN declaration file if the /X option is specified. The EXTRN declaration file codes EXTRN declarations corresponding to the public symbols in the source program. The usage types of public symbols and external symbols must completely match with the new RL66K, so EXTRN declaration files could be used to prevent link errors from coding mistakes and type mismatches. For details, refer to Section 4.14, "EXTRN Declaration Files."

#### ■ Upper-case and lower-case distinctions

Upper-case and lower-case distinctions of letters in symbols defined in the source program can be specified with the new RAS66K.

If /CD is specified, then upper-case and lower-case distinctions are recognized.

If /NCD is specified, then upper-case and lower-case distinctions are ignored.

If neither option is specified, then upper-case and lower-case distinctions are ignored.

#### Address constants

The new RAS66K allows coding of addresses that include physical segment addresses. For example, an address with physical segment address 3 and offset address 1000H would be coded as follows.

#### 3:1000H

Refer to Section 3.2.1, "Overview Of Memory Space," regarding physical segment addresses. Refer to Section 4.8.2.2, "Address Constants," regarding address constants.

#### ■ New operators

The new RAS66K adds the following operators.

| SEG expression      | Returns the physical segment address of an address expression |

|---------------------|---------------------------------------------------------------|

| OFFSET expression   | Returns the offset address of an address expression.          |

| PAGE expression     | Returns the page number of an address expression.             |

| BPOS expression     | Returns the bit offset (0-7) of a bit address expression.     |

| SIZE segment_symbol | Returns the segment size.                                     |

For details, refer to Section 4.9.2.6, "Special Operators."

#### **Expression attributes**

The new RAS66K strictly manages the inheritance of attributes in expressions. As a result, calculation error checking is considerably more severe than in the old RAS66K. Calculations that are contradictory will cause warnings. For details, refer to Section 4.9.1.1, "Meaning Of Attributes Of Expressions."

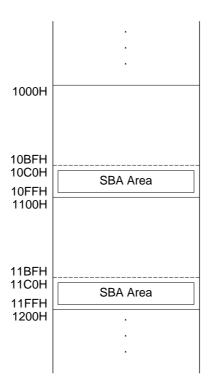

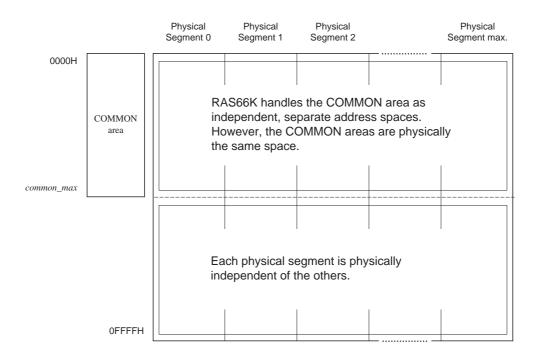

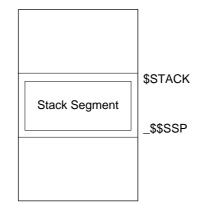

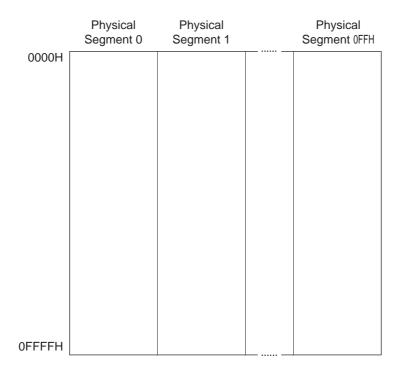

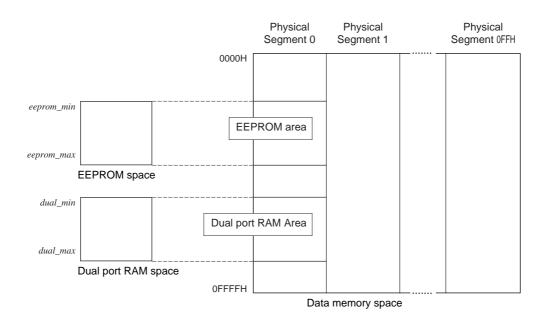

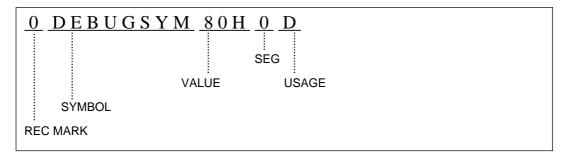

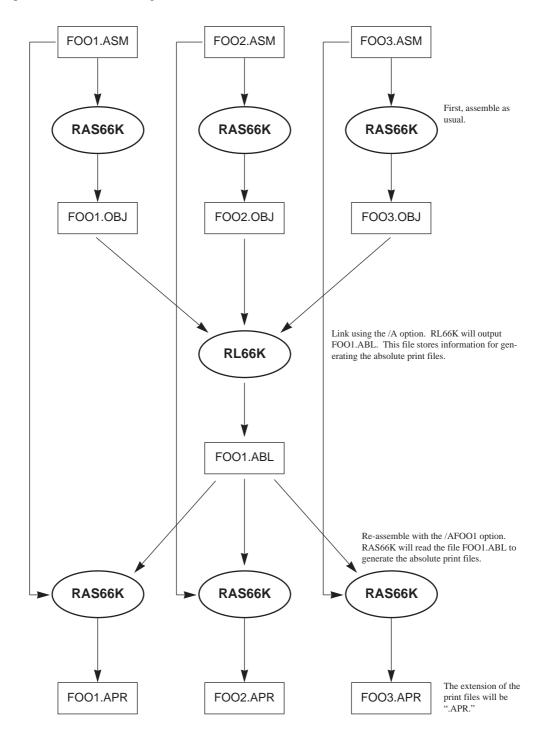

#### ■ Stack segment