## **Phase-Locked Oscillator**

Commercial: 0° to 70°C 10 MHz to 44.736 MHz

## **FEATURES**

- · Cost-effective PLL solution which includes a VCXO, filter and phase detector in a single component

- Simplicity of design requires only dividers to complete the loop

- · Output frequency may be chosen at convenient frequency to create edges for desired timing waveforms

- · Start up time less than 10 ms

- · Guaranteed start-up with ramping DC Supply

- Inputs are TTL/HCMOS compatible

#### **APPLICATIONS**

- · Regenerating and cleaning up noisy signals

- Low-jitter frequency multiplication

## SPECIAL APPLICATION NOTE

Both the reference frequency and the output frequency, or submultiple, are input to the device. The two similar frequencies are compared, and an error signal is obtained which is applied to the VCXO. The VCXO frequency is then corrected and "locked" to the average value of the reference frequency.

The output frequency, usually chosen at a convenient frequency higher than the reference frequency, may then be used to generate desired timing waveforms.

# CONNECTIONS

|                                | M2010 & M2015      | M2011 & M2016      |  |  |

|--------------------------------|--------------------|--------------------|--|--|

| Pin 1.                         | Not used           | Not used           |  |  |

| Pin 2.                         | Frequency Input #1 | Frequency Input #1 |  |  |

| Pin 5.                         | Frequency Input #2 | Frequency Input #2 |  |  |

| Pin 7.                         | Ground             | Ground and case    |  |  |

| Pin 8.                         | Output Frequency   | Output Frequency   |  |  |

| Pin 9.                         | +5V                | +5V                |  |  |

| Pin 14.                        | +5V                | +5V                |  |  |

| All other pins are not present |                    |                    |  |  |

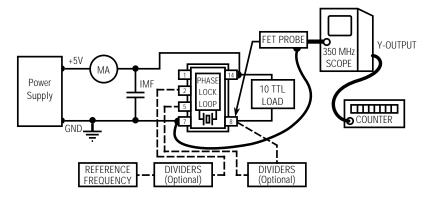

**TEST CIRCUIT**

## Description

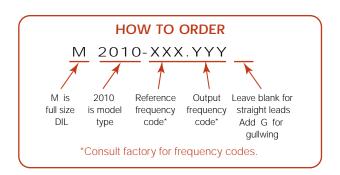

These PLL sub-systems incorporate all the components required for phase locked loop functionality except the external frequency divider. The phase locked loop unit includes VCXO, phase comparator, and control voltage filter. It will lock the locally generated VCXO output to an incoming reference signal of the same or digitally-related frequency. An external divider between VCXO output and phase-detector input establishes the output/reference frequency ratio. Offered in a 5V DIL (M) package, the PLL modules are built around a VCXO with customer's choice of reference and output frequencies.

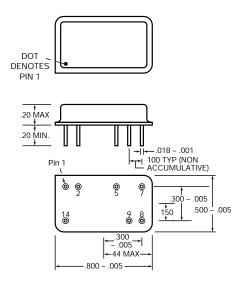

"M-1" Package

SUNST**AK微度来龟EhGOM叭ROЫ走劢**t/ TEL:0755-83396822 FAX:0755-83376182 E-MAIL: szss20@163.com<mark>FULL SIZE D.I.L</mark>. M package **CRYSTAL OSCILLATORS** M2010, M2011 M2015, M2016

## **Phase-Locked Oscillator**

Commercial: 0° to 70°C 10 MHz to 44.736 MHz

## **ELECTRICAL SPECIFICATIONS**

Frequency Range 10 MHz to 44.736 MHz

Frequency Stability Includes calibration at 25°C, operating temperature, change of input voltage, change of load, shock and

HCMOS 5V

vibration.

|                                                                                        | MIN               | TYP        | MAX      | UNITS          |

|----------------------------------------------------------------------------------------|-------------------|------------|----------|----------------|

| Input Voltage                                                                          | 4.5               | 5.0        | 5.50     | volts          |

| Input Current<br>(max. @ 5.5 VDC)                                                      |                   | 42         | 50       | mA             |

| Output Levels "0" Level, sinking 16 mA "1" Level, sourcing 8 mA                        | V <sub>DD</sub> 4 | 0.4        | 0.5      | volts<br>volts |

| Rise and Fall Times<br>from 0.8 to 2.4V, 10 TTL                                        |                   | 2.5        | 4        | ns             |

| Symmetry<br>10 TTL, @ 1.4V                                                             |                   | 45/55      | 40/60    | percent        |

| <b>Aging</b> First year After first year                                               |                   | 3<br>1     |          | ppm<br>ppm/yr  |

| Input Requirements for Pins Input Frequency, square w Sinking at 0.4V Sourcing at 2.4V | 0.6<br>100        | 1.6<br>400 | mA<br>mA |                |

| Reference Frequency Stability Requirements |          |  |  |  |

|--------------------------------------------|----------|--|--|--|

| M2010, M2011                               | ±125 ppm |  |  |  |

| M2015, M2016                               | ±150 ppm |  |  |  |

## **ENVIRONMENTAL SPECIFICATIONS**

Temperature

Operating 0° to 70°C Storage -55° to +125°C

Temperature Cycle – Not to exceed ±5 ppm change when exposed to 2 hours maximum at each temperature from 0 to 120°C, with 25°C reference

Shock - 1000 Gs, 0.35 ms, 1/2 sine wave, 3 shocks in each plane Vibration - 10-2000 Hz of .06" d.a. or 20 Gs, whichever is less

Humidity - Resistant to 85° R.H. at 85°C

## MECHANICAL SPECIFICATIONS

Gross Leak - Each unit checked in 125°C fluorocarbon

Fine Leak – Mass spectrometer leak rate less than 2 X 10<sup>-8</sup> atmos, cc/sec of helium

Pins - Kovar, 7 microinch gold over nickel

Bend Test - Will withstand two bends of 90° from reference

Header - Steel, 7 microinch gold over nickel

Case - Stainless steel, type 304

Marking - Permanent black epoxy ink or laser marked

Resistance to Solvents - MIL STD 202, Method 215

Unless customer-specific terms and conditions are signed by an officer of MF Electronics, the sale of this and all MF Electronics products are subject to terms and conditions set forth at www.mfelectronics.com/terms