PLL Frequency Synthesizer Evaluation Kit

PE3293-EK

User's Manual

6175 NANCY RIDGE DRIVE, SAN DIEGO, CA 92121 (858) 455-0660, FAX (858) 455-0770 http://www.peregrine-semi.com

Peregrine Semiconductor Corporation 1

Doc. 79/0003~03A

## **Table of Contents**

| FCC Labeling Requirement                             |

|------------------------------------------------------|

| Introduction4                                        |

| Introduction                                         |

| Getting Help                                         |

| Internet6                                            |

| Customer Support                                     |

| Hardware Section7                                    |

| Evaluation Kit Contents                              |

| Equipment Needed                                     |

| Setting Up Hardware                                  |

| Connecting the Power Supply 11                       |

| Parallel Port to 3-Wire Serial Interface Cable 11    |

| Software Section                                     |

| Software Introduction                                |

| Description                                          |

| Screen Shots13                                       |

| Installation                                         |

| Operation14                                          |

| Overiew                                              |

| Basic Operation14                                    |

| 1. Programming with the Frequency Input Loop Screens |

| 2. Programming with the Loop Block Diagrm Screens17  |

| 3. Programming with the Register Map Diagrm Screens  |

| 4. Control Bits Window                               |

| 5. Configuration Files                               |

| 6. Printer Port Screen                               |

| Measuring lock time                                  |

| Test Results                                         |

© Copyright 1999 Peregrine Semiconductor Corp. All rights reserved. Printed in the United States of America. No part of this publication may be reproduced, photocopied, stored in a retrieval system, or transmitted by electronic, mechanical or any other means without prior written permission of Peregrine Semiconductor Corp.

Peregrine Semiconductor Corp., the Peregrine logotype, and UTSi are registered trademarks of Peregrine Semiconductor Corp. PE3293 is a trademark of Peregrine Semiconductor Corp.

Peregrine Semiconductor Corp. reserves the right to make improvments to the hardware, firmware or software described in this manual at any time and without notice. While the accompanying material has been carefully reviewed to insure the most accurate information possible, the data are not warranted for absolute accuracy or completeness and are subject to change without notification.

#### Peregrine Semiconductor Corp. Life Support Policy

Peregrine Semiconductor Corp. products are not intended for use in life-critical situations, or as critical components in life-support devices or systems.

Life-support devices or systems are defined as devices or systems that are intended for surgical implant into the body, or that support or sustain life, and whose failure to perform when used in accordance with the instructions provided by the manufacturer, might result in injury to the user.

This device is intended for use only in a research and development environment. It has not been tested for compliance with FCC regulations regarding interference with radio frequency energy. It might cause harmful interference with radio communications. The user assumes responsibility for any interference caused by this device.

## FCC Labeling Requirement

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) this device may cause harmful interference, and (2) this device must accept any interference received including interference that may cause undesired operation.

## Introduction

## Introduction

The PE3293-EK is a self contained dual PLL synthesizer on a 3.25" x 3.25" surface mount circuit board. Externally it requires only power supplies, a reference frequency source and a three-wire serial data programmer to make an operating dual frequency synthesizer. The board is intended to illustrate the features of Peregrine's fractional-N architecture and the benefits of the UTSi process. The fractional-N PLL provides improved phase noise and low spurious output levels. The UTSi process, with its insulating substrate, provides improved isolation to limit crosstalk between the two PLL sections on the chip.The PE3293 minimizes current consumption by allowing the user to choose the preferred trade off between speed and power.

The PE3293 has internal fractional spurious compensation. This compensation along with a standard second order loop filter should limit the fractional spurs to -70 dBc or less. The compensation requires no external components, tuning, or software commands. No special circuit or layout features are needed on the demonstration board to fully utilize the fractional spur compensation. The fractional spur compensation may cause stability problems if loop bandwidths of more than 10% of the step size are used. The loop filter is a standard second order passive filter, keeping in mind that N is calculated using the output frequency divided by the comparison frequency, not the output frequency divided by the step size. Example: for  $f_{out} = 950$  MHz,  $f_{compare} = 800$  KHz, and  $f_{step} = 25$  KHz, we have N = 950 / 0.8 = 1187.5. Pads are provided on the board for installing additional components to make a 3<sup>rd</sup> order loop filter if desired.

Special layout features are employed in the PE3293 demonstration board to maximize the isolation between sections allowed by the fully insulating substrate of the PE3293. The power supplies for the two VCOs are isolated and brought out to separate pins on the board. This provides additional isolation and allows use of VCOs with power supply other than 3V.

The PE3293 board brings VDD1, the external bias for the PLL1 prescaler, and VDD2, the external bias for the PLL2 prescaler out to separate jacks. This allows the user to set the speeds and power usages of PLL1 and PLL2 independently. To minimize the number of power supply needed for the evaluation board, the PLL1 and PLL2 external biases have been hard-wired to the PLL main power supply (3V) through a voltage drop resistor (330 ohms for Vdd1 and 3.3 kohms for Vdd2). Note that only the PLL1 (RF) is populated, not the PLL2 (IF).

The outputs of the VCOs and the reference frequency input are via SMA jacks. The power inputs and  $f_{o}LD$  output are configured for standard .100" center header pins. A test point is set for the foLD output which can be connected to a SMA jack through a jumper.

5

## **Getting Help**

This *User's Manual* covers all of the functions of the PE3293-EK program. The program uses well-established Windows user-interface conventions and is often self-explanatory. Still, we recommend that you read through this manual before using the program.

#### Internet

Software upgrades, frequently asked questions, and applications information can be found on Peregrine's website at http://www.peregrine-semi.com.

#### **Customer Support**

Our Applications Engineering staff will be happy to answer any questions you might have about using the PE3293 or other Peregrine Semiconductor Corp. products. Contact us at (858) 455-0660.

You may also contact us by fax or e-mail:

Fax: (858) 455-0770 E-Mail:help@peregrine-semi.com

# Hardware Section

### Peregrine Semiconductor Corporation

## **Evaluation Kit Contents**

The Evaluation Kit includes all of the specific software and hardware required to evaluate the PE3293. Included in the Evaluation Kit are:

1 PE3293 Evaluation Board

- 1 PE3293 1.8GHz/550MHz Dual Fractional-N PLL

- 1 CD with Application Software included

- 1 3-Wire Interface Cable with GND

- 2 Power Supply Cables

- 1 Set of Evaluation Kit Data Plots

## **Equipment Needed**

| Computer                     | <ul> <li>Intel CPU or equivalent (386 or later)</li> <li>640 kB RAM</li> </ul> |  |  |  |

|------------------------------|--------------------------------------------------------------------------------|--|--|--|

|                              | <ul> <li>Microsoft Windows 95/98</li> </ul>                                    |  |  |  |

|                              | • Microsoft windows 95/98                                                      |  |  |  |

|                              | • Parallel port (LPT1)                                                         |  |  |  |

|                              | • Mouse (Microsoft or compatible)                                              |  |  |  |

| Power Supply                 | • 3 VDC at 4 mA for PLL                                                        |  |  |  |

|                              | • 4.1 VDC at 9 mA for VCO1 (Although VCO1 needs                                |  |  |  |

|                              | only 3.3V, 4.1V is required to compensate the voltage drop                     |  |  |  |

|                              | through a 100-ohm resistor).                                                   |  |  |  |

| Test Equipment               |                                                                                |  |  |  |

| spurious output measurement) |                                                                                |  |  |  |

CAUTION: The PE3293-EK circuit contains components that might be damaged by exposure to voltages in excess of the specified supply voltage including voltages produced by electrostatic discharges. Handle the board in accordance with procedures for handling static-sensitive components. Avoid applying excessive voltages to the power supply terminals or signal inputs or outputs.

## **Setting Up Hardware**

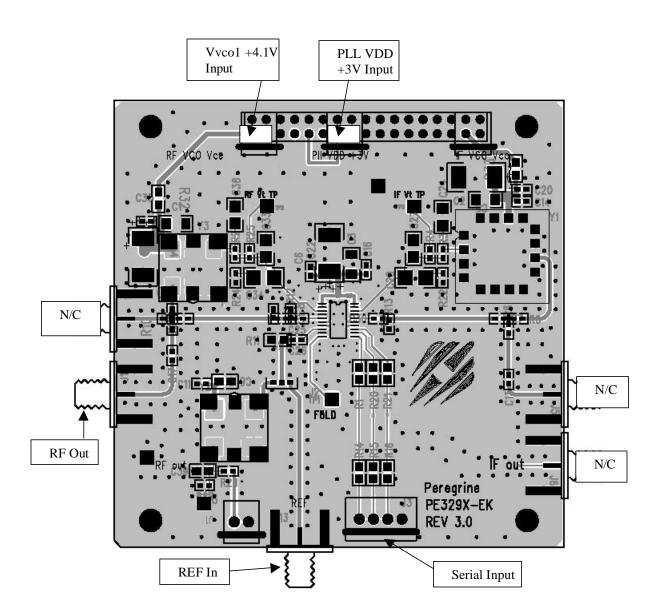

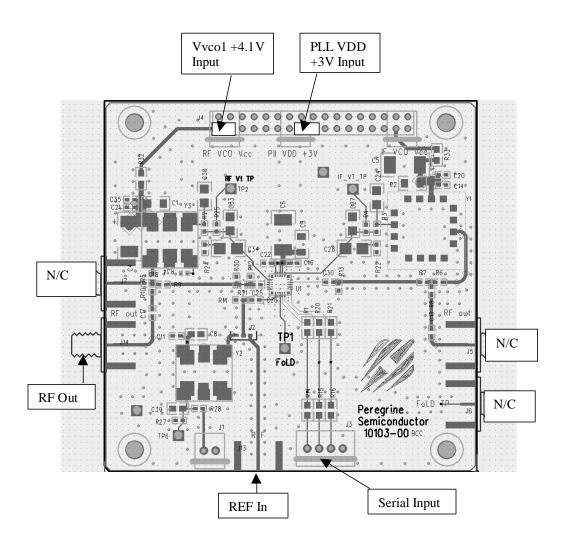

The primary test setup uses a spectrum analyzer to measure center frequency, output power, spurious outputs, crosstalk and phase noise. The configuration used to test the PE3293-EK at our facility is shown in *Figures 1 and 2* for the evaluation kit with the PE3293 in TSSOP and BCC package, respectively.

*Figure 1: PE3293 Evaluation Board Configuration for PE3293 in TSSOP Package.*

*Figure 2: PE3293 Evaluation Board Configuration for PE3293 in BCC Package.*

### **Connecting the Power Supply**

Connect the PE3293-EK to suitable power supplies as shown in *Fig. 1 or 2*. The VDD to the PE3293 is +3 volts. Although VCO1 needs only 3.3V, 4.1V is needed at  $V_{VCO1}$  terminal to compensate the voltage drop through a 100-ohm resistor. Because the PLL2 (IF) is not populated, no power supply is required for the  $V_{VCO2}$  terminal. Connection can be made using dedicated wires soldered into the supply holes or polarized pin plugs supplied with the evaluation kit.

PE3293 has to use the FlexiPower feature for VDD1 and VDD2. Vdd1 gets the required voltage through a voltage drop resistor (330 ohms for Vdd1) connected to the PLL main power, 3V.

When using a 5 volt VCO, note that the maximum tuning voltage from the PE3293 will be 2.5 volts, and the tuning range of the VCO will be restricted on the high frequency end of the specified frequency range of the VCO.

### **Parallel Port to 3-Wire Serial Interface Cable**

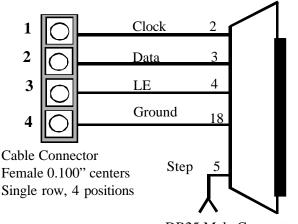

Figure 3 shows the serial interface cable configuration. The PE3293 demonstration software outputs a standard three-wire serial bus command from pins 2, 3, and 4 of the printer port of the computer. The "Step" function carried on pin 5 of the printer port goes high with the LOAD ENABLE pulse of the PLL1 main programming word. The software normally transmits all four programming words, with the PLL1 main divider control word being the third word sent.

DB25 Male Connector

Figure 3. Serial Interface

# Software

# Section

## **Software Introduction**

### Description

The PE3293-EK software runs under Microsoft Windows 95/98. We use PE3292 software to run PE3293, as well. The window screen or label may indicate PE3292, but procedure applies to PE3293. It provides a convenient means of initializing and controlling the PE3293-EK board. The user can enter frequencies directly, enter division values directly as decimal, hexadecimal, or binary numbers, and set individual control register bits directly in a registermap window. The program calculates register values from user-specified frequencies and performs range-checking on all values. The program communicates with the PE3293-EK through a standard PC parallel port (LPT1, 2, or 3). The user can save the PE3293-EK control settings as files for easy recall at any time.

## **Screen Shots**

All screen images used in this manual are from Windows 95. The appearance of the windows on your system might differ somewhat from the images in this manual, depending on the version of Windows and type of display you are using.

## Installation

1. Start Microsoft Windows. Insert the Peregrine CD into CDROM drive and open CD directory. Click Sales, Products, and then PE3293 - 1.8GHz/550MHz in the Phase Locked Loop list. Click Evaluation Board Software in the Evaluation Kit Documentation list. Choose Save this program to disk or Run this program from its current location options. Either way, follow the instructions on the screen.

2. Unzip the PE3293.exe file into an empty folder or directory.

3. Click the **setup.exe** file to start software installation procedure. Follow the instructions on the screen.

## Operation

#### Overview

This section describes how to use all of the features of the PE3293-EK software to control the PE3293-EK board. Since the PE3293-EK software uses a standard three-wire interface, it can also be used to control customer-designed breadboards or modified PE3293-EK boards. The PE3293-EK program performs range checking on values entered by the user or calculated by the program, and warns the user if certain limits are exceeded. The error messages are advisory; the program will permit the user to enter values outside the normal operating range of the PE3293. For example, an error message "fin exceeds operating limit" appears in the screen of "Frequency Input Loop 1" if the fin is higher than 1100 MHz. This message can be ignored.

#### **Basic Operation**

The PE3293 is a dual PLL synthesizer IC. The 1.8 GHz PLL (PLL 1 or RF PLL) and the 550 MHz PLL (PLL 2 or IF PLL) are programmed separately. Each PLL requires two programming words. The programming words can be generated in one of three ways. Three types of screen can be used to set the frequency of the PLLs. These are the **Frequency Input Loop** screens, which accepts frequency values, the **Loop Block Diagram** screens, which accept numbers to directly program the count registers, and the **Register Map** screen, which allows the binary control words to be set directly into the programming word registers.

If the **Frequency Input Loop** screens or the **Loop Block Diagram** screens are used to program the PLL then a third screen, the **Control <u>Bits</u>** screen must be used to set the output state of the PLL and the function of the  $f_0$ LD pin. For the PE3292 the control bits screen also sets the FlexiPower function of the prescalers.

If the **Register Map** screen is used to set the PLLs the control bits can be set directly in the **Register Map** screen.

The different screens can be accessed with the  $\underline{View}$  menu from any window. The control bits screen can be accessed from the options menu.

#### 1. Programming with the Frequency Input Loop Screens

The reference frequency, output frequency, step size, step number and comparison frequency can be specified on the Frequency Input Loop screens. Figure 4 shows one screen of the "Frequency Input Loop 1". This screen can be activated by clicking the <u>View</u> on the main menu and select **Frequency Input Loop 1**.

| puts                                                                                                                                    | Calculated Values                                                                             |  |

|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--|

| tr (MHz): 10.0<br>Starting freq (MHz): 1750.2125<br>Step Size (kHz): 12.5<br>Step Number: 0<br>Max fractionality: 32<br>fc (kHz): 400.0 | fin Spec. (MHz): 1750.2125<br>fin Cale. (MHz): 1750.2125<br>R: 25<br>M: 136<br>A: 23<br>F: 17 |  |

| exceeds operating limit).                                                                                                               | N: <mark>4375 + 17/32</mark>                                                                  |  |

|                                                                                                                                         |                                                                                               |  |

Figure 4. Frequency Input Loop 1 Screen.

Note: When programming the PE3293 to a frequency higher than 1.1 GHz, an error message will appear stating "fin exceeds operating limit." This error is derived from a known software issue and should be ignored.

Note that the **Frequency Input Loop 1** and the **Frequency Input Loop 2** screens are identical in appearance and function except that the prescaler for Loop 1 is a divide by 32 or 33, and the prescaler for Loop 2 is a divide by 16 or 17.

The **Frequency Input** screens are the basic method for programming the PLLs. These screens allow you to enter the reference frequency (fr), *starting frequency*, *step size*, *step number*, *maximum fractionality*, and comparison frequency (fc) or reference divider ratio (R) value. From these entered values, the software will calculate the values for the boxes in green. When fc is changed, the software will recalculate the value of R, and vice versa.

When both **Frequency Input Loop** screens have been programmed to the desired *fin. Calc.*, the settings from both screens can be sent to the output port by clicking on **Send** at the bottom of either **Frequency Input Loop** screen or by typing **Alt S**.

There are a number of conditions for correct operation of the PE3293.

- 1. fr must be an integer multiple of fc. (i.e. R must be an integer)

- 2. fr must be an integer multiple of Step Size

- 3. *Step Size* must be equal to *fc* divided by 1, 2, 4, 8, 16, or 32.

- *4. Step Number* must produce a calculated value for *F* which is compatible with *Max. fractionality.*

- F = 0 for any Max. fractionality.

- F = any value for Max. fractionality of 32.

- F = even values for Max. fractionality of 16.

- F = multiples of 4 for Max. fractionality of 8.

- F = multiples of 8 for Max. fractionality of 4.

- F = multiples of 16 for Max. fractionality of 2.

- F = 0 for Max. fractionality of 1.

- 5. The desired output frequency must be achievable.

- A. The desired output frequency (*fin. Spec.*) will be calculated as:

- 1) (Starting freq.) + (Step Size X Step Number).

- B. The closest achievable frequency (fin. Calc.) will be calcu-

lated as: 1)  $(32 \times M1 \times fc1) + (A1 \times fc1) + (F1/32 \times fc1)$  for the Loop 1 screen

2)

$$(16 \times M2 \times fc2) + (A2 \times fc2) + (F2/32 \times fc2)$$

for the Loop 2 screen

*C. fin. Spec.* and *fin. Calc.* must match or an error message will be displayed.

Failure to meet any of these conditions will result in an error message in the dialog box under the **Inputs** window.

Input the numbers in the clear boxes by clicking on the box and typing the values in. Enter the values by moving to another box, clicking outside the box, clicking **Send** or hitting the enter key. For the *Step Number*, you may type the value into the box or use the up and down buttons to increment or decrement the value by 1. The *Max Fractionality* is input by clicking on the box to show its pull down list and then clicking on the desired *Max Fractionality* on the list.

The user must provide fr. This is the reference frequency available from your reference source. The external reference is supplied to the input of both reference counters in the PE3293. The user must then specify either fc or R. The program will calculate the remaining term. If you change fc or R, the program will recalculate the other term to fit. If you specify a value for fc that cannot be generated by dividing fr by an integer between 3 and 511, there will be an error message, "fr is not an integer multiple of fc."

The *Starting freq*, *Step Size*, and *Step Number* are provided by the user. The program will calculate *fin Spec*. = *Starting freq* + (*Step Size X Step Number*). The program will then generate *fin Calc*. as the closest value that can be achieved using integer values for M, A, and F. If *fin Spec*. cannot be achieved using integer values of M, A, and F, there will be an error message, "Cannot achieve specified fin."

Note: When programming the PE3293 to a frequency above 1.1 GHz, an error message will appear stating "fin exceeds operating limit." This error is derived from a known software issue and should be ignored.

In general, the step size should be chosen as fc/Max fractionality and the Starting frequency should be an integer multiple of the Step Size. Failure to do so will usually lead to numerous non-

*Max fractionality* is set by choosing 1, 2, 4, 8, 16, or 32 from the pull down list for *Max Fractionality* on the **Frequency Input Loop** screen. If the calculated value for *F* is not zero or a multiple of 32/*Max fractionality*, the error message "Max fractionality exceeded" will appear.

The values of M, A, and F cannot be entered directly in the **Frequency Input Loop 1** screen. If you wish to enter these values directly, see the "Programming With the Loop Block Diagram Screen" below.

#### 2. Programming with the Loop Block Diagram Screens

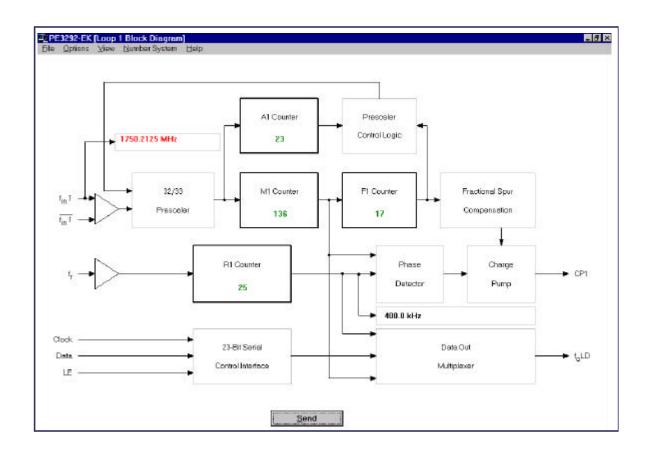

The count numbers for the *A*, *F*, *M*, and *R* counters can be input into the **Block Diagram** screen as shown in Figure 5 as **Loop 1 Block Diagram**.

Note that the **Loop 1 Block Diagram** and the **Loop 2 Block Diagram** screens are identical in appearance and function except that the prescaler block for Loop 1 shows a divide by 32 or 33, and the prescaler block shown for Loop 2 is a divide by 16 or 17.

The **Loop Block Diagram** screens allow the user to input the values for A, F, M, and R (the numbers shown in green) directly to the registers. The values for *fin. Calc.* and *fc* (shown in black) can be changed only by changing A, F, M, or R, or by going to the **Frequency Input** screen. If the resulting values of *fin. Calc.* or *fc* result in an error condition, the number will display in red in the **Loop Block Diagram** screen. If the resulting value of *fin. Calc.* does not agree with the *fin. Spec.* from the **Frequency Input** screen, the number will appear in red in the

When a **Loop Block Diagram** screen is open, the **Number System** window is active on the main menu bar. This allows input and viewing of A, F, M, and R in decimal, hex, or binary by clicking on **Number System** to pull down the menu and choosing the desired numbering system. The default setting will be in decimal.

Figure 5. PE3293 Loop 1 Block Diagram.

The **Loop Block Diagram** screen is useful when you have already calculated the register values or when you wish to view the register values calculated by the program in a more intuitive

To program Loop 1, go to <u>View</u> on the main menu and select Loop 1 Block Diagram (Fig. 5). In this screen you can specify the count value of the *A*, *F*, *M*, and *R* counter registers for Loop 1. The *A*, *F*, *M*, and *R* values can be entered and displayed in decimal, hexadecimal, or binary format.

The value of fr must be specified in the **Frequency Input Loop 1** screen. The values of *A*, *F*, *M*, and *R* from the **Loop 1 Block Diagram** will be transfered to the **Frequency Input Loop 1** screen and used to calculte *fin Calc*. If the choices of *A*, *F*, *M*, or *R* entered in the **Loop 1 Block Diagram** cause an error message in the the **Frequency Input Loop 1** screen, the value for  $f_{in}$  1 displayed in the **Loop 1 Block Diagram** will appear in red.

Note: If *R1* is changed in the **Loop 1 Block Diagram**, the comparison frequency (output of the R1counter) in the **Loop 1 Block Diagram** screen will change to the new calculated value.

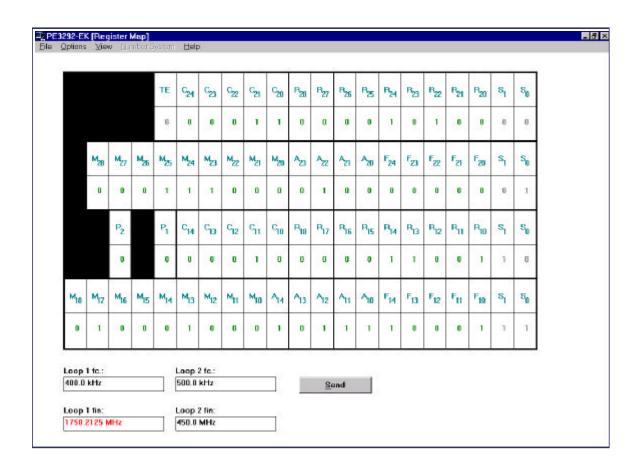

#### 3. Programming with the Register Map Screens

The **Register Map** screen as shown in Figure 6 allows you to set the state of any accessible bit in the registers of the PE3293. Bits that you can set are green. Fixed or reserved bits are gray. To access the **Register Map** screen, go to <u>View</u> on the main menu and select **Register Map**.

Figure 6. PE3293 Register Map Screen.

To program in the **Register Map** screen, place the cursor on the bit that you want to change and press the 0 or 1 keys to change the value. In this view, the program recognizes changes immediately. It is not necessary to move the cursor to enter the new value. The control bits for the PE3293 can be entered directly in the **Register Map** view to turn the individual PLLs on or off, control the f\_LD output and set the charge pump **Output Options**.

Once the desired bits are entered click on <u>Send</u> to program the PE3293. You can use this feature with the Send <u>Continuous</u> mode to change individual bits while automatically updating the PE3293.

#### 4. Control Bits Window

Except in the Register Map mode, when the PLL frequency is set using either the **Frequency Input Loop** screens or the **Loop Block Diagram** screens, the settings for the **Loop Output Options**, the **Prescaler FlexiPower Setting** and **foLD Control** must be set using the **Control** <u>**Bits**</u> window as shown in Figure 7.

To access the **Control Bits** window, go to **Options** in the main menu and click on **Control Bits** to display

the **Control Bits** window. Click on any  $f_oLD$  **Control** button to choose that output function for the  $f_oLD$  pin. The **Loop Output Options** are toggled by clicking on the function buttons. The **On** button toggles the entire PLL on or off. The **Invert** button sets the charge pump of that loop to invert the current sink and source relationship. The **Hi-Z** button turns the charge pump for that loop off, creating a high impedance at the charge pump output.

If using the PE3293, click on one of the **Prescaler FlexiPower Setting** buttons to control the prescaler function.

After the  $f_0$ LD Control, both Loop Output Options, and the Prescaler FlexiPower Setting (if using the PE3293) are set to the desired states, click on Ok to transfer the new states to the control word registers and close the window.

| ntrol Bits      |          |                                   |          |

|-----------------|----------|-----------------------------------|----------|

| foLD Control    |          | Prescaler FlexiPower Setting      |          |

| O LD1           | ⊖ fp1    | PLL1, PLL2 External               |          |

| O LD2           | O fp2    | O PLL1. PLL2 Low Power            | X Cancel |

| O LD1/LD2       | O Data   |                                   |          |

| O fc1           | Oisabled | O PLL1 High Speed, PLL2 Low Power |          |

| O fc2           |          | O PLL1, PLL2 High Speed           |          |

| Loop 1 Output ( | )ptions  | Loop 2 Output Options             |          |

| 🗵 On            |          | □ On                              |          |

| 🗆 Invert        |          | □ Invert                          |          |

| 🗆 Hi-Z          |          | T Hi-Z                            |          |

Figure 7. Control Bits Window. Note that none of the Loop 2 Output Options was selected because the Loop 2 was not populated.

20

#### **5.** Configuration Files

All of the register values and control states can be saved as files. Later, you can reload a saved configuration to restore the PE3293-EK to a particular state without having to re-enter all of the values.

#### **Saving Configurations**

From the **File** menu, choose **Save Settings As**. In the **Save As** dialog box, select a directory and enter a file name, then click **OK**.

#### **Loading Configurations**

From the **File** menu, choose **Load Setings**. In the **Open** dialog box, select a directory and a file, then click **OK**.

#### 6. Printer Port Screen

The default output of the PE3293-EK software is through the LPT1 printer port as shown in Figure 8. If you wish to use a different port to control the PE3293, go to **Options**, click on **Parallel Port** and click on the button for the port you wish to use. Click on **OK** to set the output to the selected port. The data will now be sent out through the new selected port when you click on **Send**.

| Printer Port | Address (Hex) | 🖌 Ok    |

|--------------|---------------|---------|

| IPT1         | 378           |         |

| O LPT2       | 278           | X Cance |

| O LPT3       | 3BC           |         |

Figure 8. Printer Port Screen.

## Measuring lock time

The PE3293 software has two modes for use in measuring the lock time of PLL1.

The **Toggle** mode allows switching repeatedly back and forth between two chosen frequencies. This is well suited to checking the coarse frequency acquisition by monitoring the tuning voltage of a synthesizer using an oscilloscope, or when using a mixer and oscilloscope to measure the phase difference between a PLL already locked on frequency, and the experimental PLL. The standard programming mode is more useful when measuring the lock up time as a one-shot event using a Modulation Domain Analyzer or similar instrument.

To use **Toggle Mode** click on **Options** to pull down the menu and then click on **Toggle Mode**. Click on **Options** again. You will now see that the **Repetition Rate** and **Toggle Setting** options are available.

Click on **<u>Repetition Rate</u>**. The **Repetition Rate** window will ask you to set a number for the delay time. The actual time period represented by this number will be machine dependent. You will have to experiment to determine the delay number needed to give the desired time between stepping events for your computer.

Click on **Toggle Setting**. The **Toggle Setting** window will ask you to chose the number of step sizes you wish to jump at each toggle event. The output frequency will toggle between the specified frequency (**fin Spec.**) in the **Frequency Input Loop 1** screen and a frequency that is the set number of steps above or below the starting frequency. A step is defined by the **Step Size** entry of the **Inputs** box of the **Frequency Input Loop 1** view. As an example if we set the **Staring Frequency** to 1730.4 MHz, the **Step Size** to 12.5 KHz and the **Step Number** to 1 we will get an **fin Spec.** of 1730.4125 MHz. A **Toggle Setting** of 5 steps will then cause the frequency to toggle between 1730.4125 MHz and 1730.475 MHz. A **Toggle Setting** of -5 steps will cause the frequency to toggle between 1730.4125 MHz.

When the **Toggle Mode** is used, the software sends only the programming word for the PLL1 main divider. The rising edge of the Load Enable pulse can be used as a start signal for measuring lock up time. The Load Enable pulse is present on pin 4

of the DB25 connector, pin 3 of J3, and pin 13 of the IC. When done as a one-shot event there is no way to distinguish between jumping to the toggle frequency and jumping back to the specified frequency.

To use the standard programming mode to measure lock time as a single event with a Modulation Domain Analyzer, an output for use as the trigger has been provided on pin 5 of the DB25 connector. When the standard programming mode is used the software always sends all four programming words. The word for the PLL1 main divider is the third word in the series. This makes it difficult to use the Load Enable pulse as the trigger for measuring lock time. The output provided on pin 5 of the DB25 connector gives a pulse which is synchronous with the PLL1 main divider Load Enable pulse. This output is labeled "Step" (see Fig. 3, Page 11). This signal is not available on the PE3293 board. It must be taken from the DB25 connector.

## **Test Results**

Three test plots are normally enclosed. Two of them are the phase noise plots with a 10 MHz square wave or a 19.2 MHz sine wave as the reference. The third plot is a linear plot to show the step size spur.

The test data are measured with the following parameters for PLL1 Frequency Input Loop 1:

| fr (Reference freq.) (MHz):     | 10        | 19.2    |

|---------------------------------|-----------|---------|

| Starting frequency (MHz):       | 1750.2125 | 1750.09 |

| Step size (KHz):                | 12.5      | 10      |

| Step number:                    | 0         | 0       |

| Max fractionality:              | 16        | 16      |

| fc (comparison frequency) (KHz) | 160       | 160     |

SUNSTAR 商斯达实业集团是集研发、生产、工程、销售、代理经销、技术咨询、信息服务等为一体的高科技企业,是专业高科技电子产品生产厂家,是具有10多年历史的专业电子元器件供应商,是中国最早和最大的仓储式连锁规模经营大型综合电子零部件代理分销商之一,是一家专业代理和分銷世界各大品牌IC芯片和電子元器件的连锁经营综合性国际公司,专业经营进口、国产名厂名牌电子元件,型号、种类齐全。在香港、北京、深圳、上海、西安、成都等全国主要电子市场设有直属分公司和产品展示展销窗口门市部专卖店及代理分销商,已在全国范围内建成强大统一的供货和代理分销网络。我们专业代理经销、开发生产电子元器件、集成电路、传感器、微波光电元器件、工控机/DOC/DOM电子盘、专用电路、单片机开发、MCU/DSP/ARM/FPGA软件硬件、二极管、三极管、模块等,是您可靠的一站式现货配套供应商、方案提供商、部件功能模块开发配套商。商斯达实业公司拥有庞大的资料库,有数位毕业于著名高校——有中国电子工业摇篮之称的西安电子科技大学(西军电)并长期从事国防尖端科技研究的高级工程师为您精挑细选、量身订做各种高科技电子元器件,并解决各种技术问题。

微波光电部专业代理经销高频、微波、光纤、光电元器件、组件、部件、模块、整机;电 磁兼容元器件、材料、设备;微波 CAD、EDA 软件、开发测试仿真工具;微波、光纤仪器仪表。 欢迎国外高科技微波、光纤厂商将优秀产品介绍到中国、共同开拓市场。长期大量现货专业批发 高频、微波、卫星、光纤、电视、CATV 器件: 晶振、VCO、连接器、PIN 开关、变容二极管、开 关二极管、低噪晶体管、功率电阻及电容、放大器、功率管、MMIC、混频器、耦合器、功分器、 振荡器、合成器、衰减器、滤波器、隔离器、环行器、移相器、调制解调器;光电子元器件和组 件:红外发射管、红外接收管、光电开关、光敏管、发光二极管和发光二极管组件、半导体激光 二极管和激光器组件、光电探测器和光接收组件、光发射接收模块、光纤激光器和光放大器、光 调制器、光开关、DWDM 用光发射和接收器件、用户接入系统光光收发器件与模块、光纤连接器、 光纤跳线/尾纤、光衰减器、光纤适 配器、光隔离器、光耦合器、光环行器、光复用器/转换器; 无线收发芯片和模组、蓝牙芯片和模组。

更多产品请看本公司产品专用销售网站:

商斯达微波光电产品网:HTTP://www.rfoe.net/

商斯达中国传感器科技信息网: http://www.sensor-ic.com/

商斯达工控安防网: http://www.pc-ps.net/

商斯达电子元器件网: http://www.sunstare.com/

商斯达消费电子产品网://www.icasic.com/

商斯达实业科技产品网://www.sunstars.cn/ 射频微波光电元器件销售热线:

地址:深圳市福田区福华路福庆街鸿图大厦1602室

电话: 0755-83396822 83397033 83398585 82884100

传真: 0755-83376182 (0) 13823648918 MSN: SUNS88888@hotmail.com

邮编: 518033 E-mail:szss20@163.com QQ: 195847376

深圳赛格展销部: 深圳华强北路赛格电子市场 2583 号 电话: 0755-83665529 25059422 技术支持: 0755-83394033 13501568376

欢迎索取免费详细资料、设计指南和光盘;产品凡多,未能尽录,欢迎来电查询。

北京分公司:北京海淀区知春路 132 号中发电子大厦 3097 号

TEL: 010-81159046 82615020 13501189838 FAX: 010-62543996 上海分公司:上海市北京东路 668 号上海賽格电子市场 D125 号

TEL: 021-28311762 56703037 13701955389 FAX: 021-56703037

西安分公司: 西安高新开发区 20 所(中国电子科技集团导航技术研究所) 西安劳动南路 88 号电子商城二楼 D23 号

TEL: 029-81022619 13072977981 FAX:029-88789382