# **Digital Signal Processor for TV**

### **■**Package

## General Description

The NJU26102 is a digital signal processor that provides Delay, eala, ViVA2+, PEQ, and AGC.

The NJU26102 is suitable for audio products such as TV, CD radio- cassette, speakers system, and others.

NJU26102

### ■ Feature

- ●3D Sound: eala, BBE ViVA, BBE ViVA+, BBE ViVA2+.

- Sound enhancement: BBE, Mach3Bass.

- ●5band PEQ, Tone Control.

- AGC to control sound-volume difference between channels or programs.

# ■ Digital Signal Processor Specification

24bit fixed-point Digital Signal Processor

Maximum Clock Frequency : 38MHz

Power Supply : DSP Core 2.5V, I/O Interface 2.5V (+3.3V tolerant)

Package : QFP-32

The detail hardware specification of the NJU26102 is described in the "NJU26100 Series Hardware Data Sheet". In respect to software commands, request NJR.

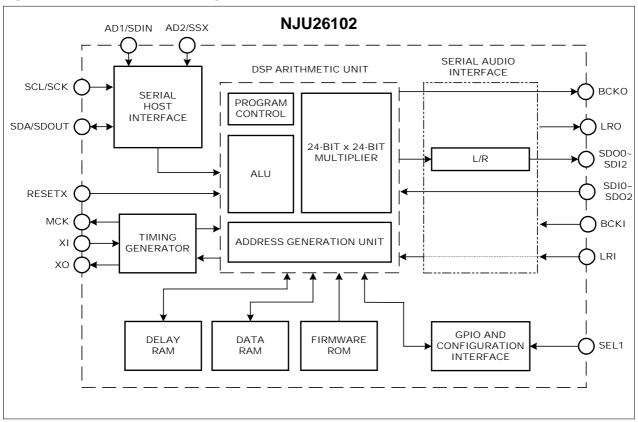

# ■ DSP Block Diagram

## Fig.1 NJU26102 DSP Block Diagram

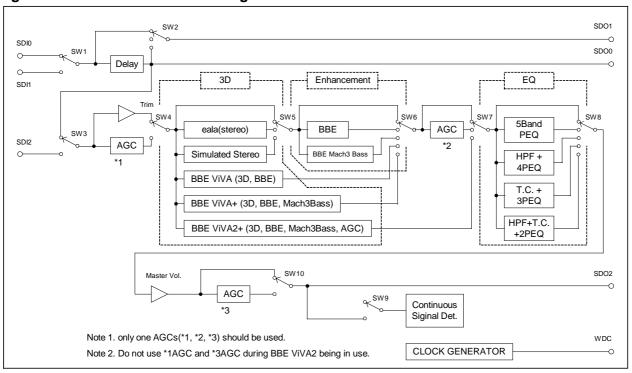

# **■** Function Block Diagram

## Fig.2 NJU26102 Function Block Diagram

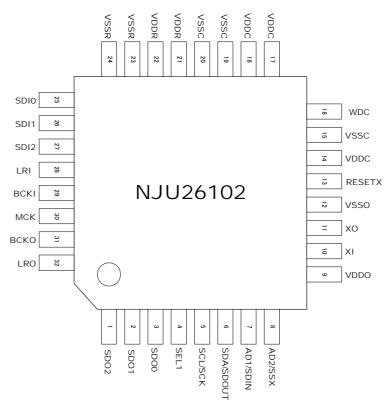

# **■** Pin Configuration

Fig.3 NJU26102 Pin Configuration

# **■** Pin Description

**Table 1 Pin Description**

| Iabic | iable i Fili Description |     |                                        |     |          |     |                             |  |

|-------|--------------------------|-----|----------------------------------------|-----|----------|-----|-----------------------------|--|

| No.   | Pin Name                 | I/O | Pin Description                        | No. | Pin Name | I/O | Pin Description             |  |

| 1     | SDO2                     | 0   | Audio Data Output 2                    | 17  | VDDC     | Р   | DSP Core Power Supply +2.5V |  |

| 2     | SDO1                     | 0   | Audio Data Output 1                    | 18  | VDDC     | Р   | DSP Core Power Supply +2.5V |  |

| 3     | SDO0                     | 0   | Audio Data Output 0                    | 19  | VSSC     | G   | DSP Core Power Supply GND   |  |

| 4     | SEL1                     | I   | Select I <sup>2</sup> C or Serial bus  | 20  | VSSC     | G   | DSP Core Power Supply GND   |  |

| 5     | SCL/SCK                  | I   | I <sup>2</sup> C clock / Serial clock  | 21  | VDDR     | Р   | I/O Power Supply +2.5V      |  |

| 6     | SDA/SDOUT                | Ю   | I <sup>2</sup> C I/O / Serial Out      | 22  | VDDR     | Р   | I/O Power Supply +2.5V      |  |

| 7     | AD1/SDIN                 | I   | I <sup>2</sup> C Address / Serial In   | 23  | VSSR     | G   | I/O Power Supply GND        |  |

| 8     | AD2/SSX                  | I   | I <sup>2</sup> C Address/Serial enable | 24  | VSSR     | G   | I/O Power Supply GND        |  |

| 9     | VDDO                     | Р   | OSC Power Supply +2.5V                 | 25  | SDI0     | I   | Audio Data Input 0          |  |

| 10    | XI                       | I   | OSC Clock Input                        | 26  | SDI1     | I   | Audio Data Input 1          |  |

| 11    | XO                       | 0   | OSC Clock Output                       | 27  | SDI2     | I   | Audio Data Input 2          |  |

| 12    | VSSO                     | G   | OSC Power Supply GND                   | 28  | LRI      | I   | LR Clock Input              |  |

| 13    | RESETX                   | I   | Reset                                  | 29  | BCKI     | I   | Bit Clock Input             |  |

| 14    | VDDC                     | Р   | DSP Core Power Supply +2.5V            | 30  | MCK      | 0   | A/D, D/A Clock Output       |  |

| 15    | VSSC                     | G   | DSP Core Power Supply GND              | 31  | BCKO     | 0   | Bit Clock Output            |  |

| 16    | WDC                      | 0   | Clock for Watch Dog Timer              | 32  | LRO      | 0   | LR Clock Output             |  |

<sup>\*</sup> I : Input, O : Output, IO : Bi-directional, P : +Power, G : GND \* Package is shown in fig. 3.

#### Audio Interface

The NJU26102 audio interface provides industry serial data formats of I<sup>2</sup>S, MSB-first left-justified or MSB-first Right-justified. The NJU26102 audio interface provides three data inputs, SDI0, SDI1, and SDI2, and three data outputs, SDO0, SDO1, and SDO3, as shown in table 2 and 3. The input serial data is selected by the firmware command.

**Table 2 Serial Audio Input Pins**

| Symbol | Pin No. | Description            |  |  |  |  |

|--------|---------|------------------------|--|--|--|--|

| SDI0   | 25      | Audio Data Input 0 L/R |  |  |  |  |

| SDI1   | 26      | Audio Data Input 1 L/R |  |  |  |  |

| SDI2   | 27      | Audio Data Input 2 L/R |  |  |  |  |

**Table 3 Serial Audio Input Pins**

| Symbol | Pin No. | Description             |

|--------|---------|-------------------------|

| SDO0   | 3       | Audio Data Output 0 L/R |

| SDO1   | 2       | Audio Data Output 1 L/R |

| SDO2   | 1       | Audio Data Output 2 L/R |

#### ■ Host Interface

The NJU26102 can be controlled via Serial Host Interface (SHI) using either of two serial bus formats: 4-Wire serial bus or  ${\bf I^2C}$  bus. Data transfers are in 8 bits packets (1 byte) when using either format. The SHI operates only in a SLAVE fashion. A host controller connected to the interface always drives the clock (SCL / SCK) line and initiates data transfers, regardless of the chosen communication protocol.

The detail 4-Wire Serial bus and I<sup>2</sup>C bus information are described in the "NJU26100 Series Hardware Data Sheet".

#### 4-Wire Serial Interface

The serial host interface can be configured for 4-Wire Serial bus communication by setting SEL1="H" during the reset initialization sequence. SHI bus communication is full-duplex; a write byte is shifted into the SDIN pin at the same time that a read byte is shifted out of the SDOUT pin. Data transfers are MSB first and are enabled by setting the Slave Select pin LOW (SSX = 0). Data is clocked into SDIN on rising transitions of SCK. Data is latched at SDOUT on falling transitions of SCK except for the first byte (MSB) which is latched on the falling transitions of SSX. SDOUT is Hi-Z in case of SSX = "H". SDOUT is CMOS output in case of SSX = "L". SDOUT needs a pull-up resistor when SDOUT is Hi-Z.

# ■ I<sup>2</sup>C address

AD1 and AD2 pins are used to configure the seven-bit SLAVE address of the serial host interface. These pins offer additional flexibility to SLAVE address. 4 addresses could be chosen by AD1 and AD2-pin. The AD1 and AD2-pin addresses are decided by the connections of AD1 and AD2-pin. The AD1 and AD2 addresses should be the same level as AD1 and AD2-pin connections.

Table 4 I<sup>2</sup>C Bus SLAVE Address

| bit7 | bit6 | bit5 | bit4 | bit3 | bit2             | bit1             | bit0 |

|------|------|------|------|------|------------------|------------------|------|

| 0    | 0    | 1    | 1    | 1    | AD2 <sup>*</sup> | AD1 <sup>*</sup> | R/W  |

<sup>\*</sup> AD1 or AD2 address is 0 when AD1 or AD2-pin is "L". AD1 or AD2 address is 1 when AD1 or AD2-pin is "H".

The detail I<sup>2</sup>C bus timing of the NJU26102 is described in the "NJU26100 Series Hardware Data Sheet".

## ■ Watchdog Clock

NJU26102 outputs clock pulse through WDC (Pin No. 16) during normal operation.

WDC Clock Cycle (L / H) Time 184msec (fs=48kHz)

200msec (fs=44.1kHz) 276msec (fs=32kHz)

The NJU26102 generates a clock pulse through the WDC terminal after resetting the NJU26102. The WDC clock is useful to check the status of the NJU26102 operation. For example, a microcomputer monitors the WDC clock and checks the status of the NJU26102. When the WDC clock pulse is lost or not normal clock cycle, the NJU26102 does not operate correctly. Then reset the NJU26102 and set up the NJU26102 again.

## **■** Firmware Command Table

Host processor can control the NJU26102 via 4-Wire serial bus or I<sup>2</sup>C bus interface. The following table summarizes the available user commands.

Table 5 NJU26102 Command

| ub.0 0 | 140020102 Command           |                                                                           |  |  |  |

|--------|-----------------------------|---------------------------------------------------------------------------|--|--|--|

| No.    | Command                     | Command Description                                                       |  |  |  |

| 1      | System State                | DSP Mode, Data Width, Serial Audio Mode, Audio Clock, MCK clock           |  |  |  |

| 2      | Firmware Version No.        | Firmware Version No. Request                                              |  |  |  |

|        | Request                     |                                                                           |  |  |  |

| 3      | Firmware                    | eala, BBE, Mach3Bass, ViVA, ViVA+, ViVA2, PEQ, AGC, Signal Detect, Bypass |  |  |  |

|        | Mode Select                 |                                                                           |  |  |  |

| 4      | Input Select /              | Input Select: SDI0, SDI1, SDI2, Delay Input Select                        |  |  |  |

|        | Fs Select                   | Sample Rate: 48, 44.1, 32kHz                                              |  |  |  |

| 5      | Input Trim                  | 0 to -31dB                                                                |  |  |  |

| 6      | Master Volume               | 0 to -96dB, -Inf (with Smooth Control)                                    |  |  |  |

| 7      | Channel Balance             | 0 to -30dB, -Inf, L/R Select                                              |  |  |  |

| 8      | AGC Threshold Level         | Threshold Level: -6 to -40dBFS                                            |  |  |  |

|        |                             | Noise Compressor Threshold Level: -50 to -96dBFS, -Inf                    |  |  |  |

|        |                             | Attack Time: 0.1, 0.2, 0.5, 1, 2, 5sec                                    |  |  |  |

|        |                             | Release Time: 1, 2, 5msec                                                 |  |  |  |

|        |                             | Ratio: 1.5:1, 2:1, 4:1, 8:1, 20:1, -Inf:1                                 |  |  |  |

|        |                             | Boost: 0 to +24dB                                                         |  |  |  |

|        |                             | Output Trim: 0 to -31dB                                                   |  |  |  |

|        |                             | Position: forward the 3D, EQ, backward the Master Volume                  |  |  |  |

| 9      | eala Gain                   | 0 to +12dB                                                                |  |  |  |

| 10     | BBE ViVA / ViVA+            | 0 to +6dB                                                                 |  |  |  |

|        | Surround Gain               |                                                                           |  |  |  |

| 11     | BBE                         | Level: 0 to -15dB                                                         |  |  |  |

|        |                             | HF Adjust: 0 to 15                                                        |  |  |  |

| 12     | BBE ViVA2+ AGC              | Threshold Level: -6 to -26dBFS                                            |  |  |  |

|        |                             | Attack Time: 0.1, 0.2, 0.5, 1, 2, 5sec                                    |  |  |  |

|        |                             | Release Time: 1, 2, 5msec                                                 |  |  |  |

|        |                             | Ratio: 2:1, 4:1, 8:1, -Inf:1                                              |  |  |  |

|        |                             | Boost: 0 to +24dB                                                         |  |  |  |

|        |                             | Output Trim: 0 to -31dB                                                   |  |  |  |

| 13     | BBE Mach3Bass               | f0: 40 to 150Hz                                                           |  |  |  |

|        |                             | Q: 1.8 to 8.2                                                             |  |  |  |

|        |                             | Gain: 0 to +12dB                                                          |  |  |  |

| 14     | EQ Mode                     | 5band PEQ, HPF, Tone Control                                              |  |  |  |

| 15     | PEQ f0 /HPF fc              | f0: 20 to 20kHz(1/6 octave, 20 points/decade)                             |  |  |  |

|        |                             | Q: 0.33 to 8.2                                                            |  |  |  |

| 1.5    | 5                           | Gain: -12 to +12dB                                                        |  |  |  |

| 16     | Delay Time                  | Delay: 0 to 37.5msec (at Fs = 32kHz)                                      |  |  |  |

| 17     | Continuous Signal<br>Detect | Continuous Signal Detect                                                  |  |  |  |

| 18     | NOP                         | No Operation                                                              |  |  |  |

|        | 1                           | =                                                                         |  |  |  |

In respect to detail command information, request NJR.

## ■ License Information

1. The NJU26102 is manufactured by New Japan Radio Co.,Ltd. under license from BBE Sound Inc. BBE is a registered trademark of BBE Sound Inc. A license from BBE Sound Inc. must be required before the NJU26102 can be purchased from New Japan Radio Co.,Ltd.

BBE Sound, Inc.

5831 Production Drive

Huntington Beach, CA 92649 USA

Tel: 714-897-6766 Fax: 714-896-0736 http://www.bbesound.com

2. Purchase of I<sup>2</sup>C components of New Japan Radio Co. ,Ltd or one of sublicensed Associated Companies conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard specification as defined by Philips.

Version V1.05

[CAUTION]

The specifications on this databook are only given for information, without any guarantee as regards either mistakes or omissions. The application circuits in this databook are described only to show representative usages of the product and not intended for the guarantee or permission of any right including the industrial rights.