# INTEGRATED CIRCUITS

# DATA SHEET

# **PCK2001**

14.318-150 MHz I<sup>2</sup>C 1:18 Clock Buffer

Product specification Supersedes data of 1998 Oct 27

# 14.318-150 MHz I<sup>2</sup>C 1:18 Clock Buffer

**PCK2001**

### **FEATURES**

- HIGH speed, LOW noise non-inverting 1-18 buffer

- Typically used to support four SDRAM DIMMs

- Multiple V<sub>DD</sub>, V<sub>SS</sub> pins for noise reduction

- 3.3V operation

- Separate 3-State pin for testing

- ESD protection exceeds 2000V per Standard 801.2

- Optimized for 66MHz, 100MHz and 133MHz operation

- 175 ps skew outputs

- Available in 48-pin SSOP package

- See PCK2001M for mobile (reduced pincount) 28-pin 1-10 buffer version

• Individual clock output enable/disable via I<sup>2</sup>C

### **DESCRIPTION**

The PCK2001 is a 1–18 fanout buffer used for 133/100 MHz CPU, 66/33 MHz PCI, 14.318 MHz REF, or 133/100/66 MHz SDRAM clock distribution. 18 outputs are typically used to support up to 4 SDRAM DIMMS commonly found in desktop, workstation or server applications.

All clock outputs meet Intel's drive, rise/fall time, accuracy, and skew requirements. An I<sup>2</sup>C interface is included to allow each output to be enabled/disabled individually. An output disabled via the I<sup>2</sup>C interface will be held in the LOW state. In addition, there is an OE input which 3-States all outputs.

### **QUICK REFERENCE DATA**

| SYMBOL                               | PARAMETER                                           | CONDITIONS                        | TYPICAL    | UNIT |

|--------------------------------------|-----------------------------------------------------|-----------------------------------|------------|------|

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>BUF_IN to BUF_OUT <sub>n</sub> | V <sub>CC</sub> = 3.3V, CL = 30pF | 2.5<br>2.5 | ns   |

| t <sub>r</sub>                       | Rise time                                           | V <sub>CC</sub> = 3.3V, CL = 30pF | 1.0        | ns   |

| t <sub>f</sub>                       | Fall time                                           | V <sub>CC</sub> = 3.3V, CL = 20pF | 700        | ps   |

| I <sub>CC</sub>                      | Total supply current                                | V <sub>CC</sub> = 3.465V          | 50         | μА   |

# ORDERING INFORMATION

| PACKAGES                         | TEMPERATURE RANGE | ORDER CODE | DRAWING NUMBER |  |

|----------------------------------|-------------------|------------|----------------|--|

| 48-Pin Plastic SSOP 0°C to +70°C |                   | PCK2001 DL | SOT370-1       |  |

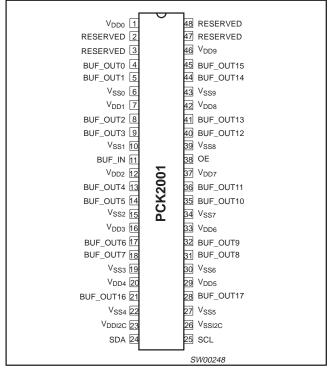

### PIN CONFIGURATION

I<sup>2</sup>C is a trademark of Philips Semiconductors Corporation.

# **PIN DESCRIPTION**

| PIN<br>NUMBER                                  | I/O<br>TYPE | SYMBOL                | FUNCTION                           |

|------------------------------------------------|-------------|-----------------------|------------------------------------|

| 4, 5, 8, 9                                     | Output      | BUF_OUT (0-3)         | Buffered clock outputs             |

| 13, 14, 17,<br>18                              | Output      | BUF_OUT (4-7)         | Buffered clock outputs             |

| 31, 32, 35,<br>36                              | Output      | BUF_OUT<br>(8–11)     | Buffered clock outputs             |

| 40, 41, 44,<br>45                              | Output      | BUF_OUT<br>(12–15)    | Buffered clock outputs             |

| 21, 28                                         | Output      | BUF_OUT<br>(16–17)    | Buffered clock outputs             |

| 11                                             | Input       | BUF_IN                | Buffered clock input               |

| 38                                             | Input       | OE                    | Active high output enable          |

| 24                                             | I/O         | SDA                   | I <sup>2</sup> C serial data       |

| 25                                             | Input       | SCL                   | I <sup>2</sup> C serial clock      |

| 3, 7, 12, 16,<br>20, 29, 33,<br>37, 42, 46     | Input       | V <sub>DD (0-9)</sub> | 3.3V Power supply                  |

| 6, 10, 15,<br>19, 22,<br>27, 30, 34,<br>39, 43 | Input       | V <sub>SS (0-9)</sub> | Ground                             |

| 23                                             | Input       | V <sub>DDI2C</sub>    | 3.3V I <sup>2</sup> C Power supply |

| 26                                             | Input       | V <sub>SSI2C</sub>    | I <sup>2</sup> C Ground            |

# 14.318-150 MHz I<sup>2</sup>C 1:18 Clock Buffer

PCK2001

# **FUNCTION TABLE**

| OE | BUF_IN | I <sup>2</sup> CEN | BUF_OUTn |

|----|--------|--------------------|----------|

| L  | X      | Х                  | Z        |

| Н  | L      | X                  | L        |

| Н  | Н      | Н                  | Н        |

| Н  | Н      | L                  | L        |

# ABSOLUTE MAXIMUM RATINGS<sup>1, 2</sup>

In accordance with the Absolute Maximum Rating System (IEC 134) Voltages are referenced to  $V_{SS}$  ( $V_{SS} = 0V$ )

| CVMDOL           | DADAMETED                                                     | CONDITION                                                                   |      | LIMITS                |      |  |

|------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------|------|-----------------------|------|--|

| SYMBOL PARAMET   | PARAMETER                                                     |                                                                             |      | MAX                   | UNIT |  |

| $V_{DD}$         | DC 3.3V supply voltage                                        |                                                                             | -0.5 | +4.6                  | V    |  |

| I <sub>IK</sub>  | DC input diode current                                        | V <sub>I</sub> < 0                                                          |      | -50                   | mA   |  |

| V <sub>I</sub>   | DC input voltage                                              | Note 2                                                                      | -0.5 | 5.5                   | V    |  |

| I <sub>OK</sub>  | DC output diode current                                       | $V_O > V_{DD}$ or $V_O < 0$                                                 |      | ±50                   | mA   |  |

| V <sub>O</sub>   | DC output voltage                                             | Note 2                                                                      | -0.5 | V <sub>CC</sub> + 0.5 | V    |  |

| I <sub>O</sub>   | DC output source or sink current                              | $V_O >= 0$ to $V_{DD}$                                                      |      | ±50                   | mA   |  |

| T <sub>STG</sub> | Storage temperature range                                     |                                                                             | -65  | +150                  | °C   |  |

| P <sub>TOT</sub> | Power dissipation per package plastic medium-shrink SO (SSOP) | For temperature range: 0 to +70°C above +55°C derate linearly with 11.3mW/K |      | 850                   | mW   |  |

## NOTES:

# **RECOMMENDED OPERATING CONDITIONS**

| SYMBOL           | PARAMETER                                       | CONDITIONS | LIM   | UNIT     |      |

|------------------|-------------------------------------------------|------------|-------|----------|------|

| STWIBOL          | PARAMETER                                       | CONDITIONS | MIN   | MAX      | UNIT |

| $V_{DD}$         | DC 3.3V supply voltage                          |            | 3.135 | 3.465    | V    |

| C <sub>L</sub>   | Capacitive load                                 |            | 20    | 30       | pF   |

| VI               | DC input voltage range                          |            | 0     | $V_{DD}$ | V    |

| Vo               | DC output voltage range                         |            | 0     | $V_{DD}$ | V    |

| T <sub>amb</sub> | Operating ambient temperature range in free air |            | 0     | +70      | °C   |

<sup>1.</sup> Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

2. The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

# 14.318-150 MHz I<sup>2</sup>C 1:18 Clock Buffer

PCK2001

# **DC CHARACTERISTICS**

|                  | SYMBOL PARAMETER                                          |                     | TEST CONDITIONS                           |                    |                       | LIMITS                          |    |

|------------------|-----------------------------------------------------------|---------------------|-------------------------------------------|--------------------|-----------------------|---------------------------------|----|

| SYMBOL           |                                                           |                     |                                           |                    |                       | T <sub>amb</sub> = 0°C to +70°C |    |

|                  |                                                           | V <sub>DD</sub> (V) | OTHER                                     |                    | MIN                   | MAX                             | 1  |

| V <sub>IH</sub>  | HIGH level input voltage                                  | 3.135 to 3.465      |                                           |                    | 2.0                   | V <sub>DD</sub> + 0.3           | V  |

| V <sub>IL</sub>  | LOW level input voltage                                   | 3.135 to 3.465      |                                           |                    | V <sub>SS</sub> - 0.3 | 0.8                             | V  |

| V <sub>OH</sub>  | 3.3V output HIGH voltage                                  | 3.135 to 3.465      | $I_{OH} = -1mA$                           |                    | 2.4                   | -                               | V  |

| V <sub>OL</sub>  | 3.3V output LOW voltage                                   | 3.135 to 3.465      | I <sub>OL</sub> = 1mA                     |                    | -                     | 0.4                             | V  |

|                  | I <sub>OH</sub> Output HIGH current                       | 3.135 to 3.465      | V <sub>OUT</sub> = 2.0V                   |                    | -54                   | -                               | mA |

| IOH              |                                                           | 3.135 to 3.465      | V <sub>OUT</sub> = 3.135V                 |                    | -                     | -46                             |    |

| ,                | Output LOW ourrent                                        | 3.135 to 3.465      | V <sub>OUT</sub> = 1.0V                   |                    | 54                    | _                               | A  |

| l <sub>OL</sub>  | Output LOW current                                        | 3.135 to 3.465      | $V_{OUT} = 0.4V$                          |                    | -                     | 53                              | mA |

| ±l <sub>l</sub>  | Input leakage current                                     | 3.465               |                                           |                    | -                     | 5                               | μΑ |

| ±l <sub>OZ</sub> | 3-State output OFF-State current                          | 3.465               | V <sub>OUT</sub> = V <sub>DD</sub> or GND | I <sub>O</sub> = 0 | _                     | 10                              | μΑ |

| I <sub>CC</sub>  | Quiescent supply current                                  | 3.465               | $V_I = V_{DD}$ or GND                     | I <sub>O</sub> = 0 | -                     | 100                             | μΑ |

| Δl <sub>CC</sub> | Additional quiescent supply current given per control pin | 3.135 to 3.465      | $V_1 = V_{DD} - 0.6V$                     | I <sub>O</sub> = 0 | -                     | 500                             | μΑ |

PCK2001

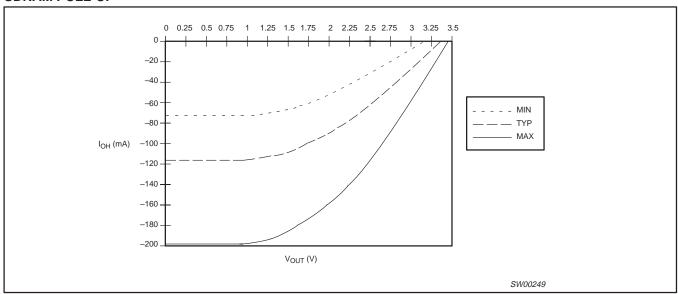

# SDRAM CLOCK OUTPUT BUFFER PULL-UP CHARACTERISTICS

|         | PULL-UP         |             |             |  |  |

|---------|-----------------|-------------|-------------|--|--|

| VOLTAGE | l<br>(mA)       |             |             |  |  |

| (V)     | MIN             | TYP         | MAX         |  |  |

| 0       | <del>-</del> 72 | -116        | -198        |  |  |

| 1       | <del>-</del> 72 | -116        | -198        |  |  |

| 1.40    | -68             | -110        | -188        |  |  |

| 1.50    | -67             | -107        | -184        |  |  |

| 1.65    | -64             | -103        | -177        |  |  |

| 1.80    | -60             | -98         | -170        |  |  |

| 2.00    | -54             | -90         | <b>–157</b> |  |  |

| 2.40    | -39             | <b>–</b> 69 | -126        |  |  |

| 2.60    | -30             | -56         | -107        |  |  |

| 3.135   | 0               | <b>–15</b>  | -46         |  |  |

| 3.30    |                 | 0           | -23         |  |  |

| 3.465   |                 |             | 0           |  |  |

# **SDRAM PULL-UP**

PCK2001

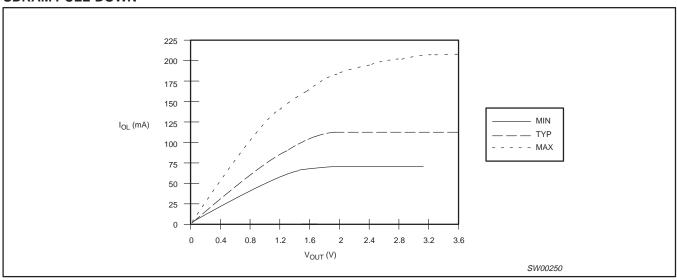

# SDRAM CLOCK OUTPUT BUFFER PULL-DOWN CHARACTERISTICS

|         | PUI       | LL-UP |     |  |  |

|---------|-----------|-------|-----|--|--|

| VOLTAGE | I<br>(mA) |       |     |  |  |

| (V)     | MIN       | TYP   | MAX |  |  |

| 0       | 0         | 0     | 0   |  |  |

| 0.4     | 23        | 34    | 53  |  |  |

| 0.65    | 35        | 52    | 83  |  |  |

| 0.85    | 43        | 65    | 104 |  |  |

| 1.00    | 49        | 74    | 118 |  |  |

| 1.4     | 61        | 93    | 152 |  |  |

| 1.5     | 64        | 98    | 159 |  |  |

| 1.65    | 67        | 103   | 168 |  |  |

| 1.8     | 70        | 108   | 177 |  |  |

| 1.95    | 72        | 112   | 184 |  |  |

| 3.135   | 72        | 112   | 204 |  |  |

| 3.6     |           | 112   | 204 |  |  |

# **SDRAM PULL-DOWN**

# 14.318-150 MHz I<sup>2</sup>C 1:18 Clock Buffer

PCK2001

### **AC CHARACTERISTICS**

| SYMBOL                              | PARAMETER                         | TEST CONDITI     | TEST CONDITIONS |      | LIMITS<br>T <sub>amb</sub> = 0°C to +70°C |      |      |

|-------------------------------------|-----------------------------------|------------------|-----------------|------|-------------------------------------------|------|------|

|                                     |                                   |                  | NOTES           | MIN  | TYP <sup>9</sup>                          | MAX  | 1    |

| T <sub>SDKP</sub>                   | SDRAM CLK period                  |                  | 1, 6            | 15.0 | 15.2                                      | 15.5 |      |

| T <sub>SDKH</sub>                   | SDRAM CLK HIGH time               | 66MHz            | 2, 6, 8         | 5.6  | 7.8                                       | 8.4  | ns   |

| T <sub>SDKL</sub>                   | SDRAM CLK LOW time                |                  | 3, 6, 8         | 5.3  | 7.4                                       | 8.0  |      |

| T <sub>SDKP</sub>                   | SDRAM CLK period                  |                  | 1, 6            | 10.0 | 10.01                                     | 10.5 |      |

| T <sub>SDKH</sub>                   | SDRAM CLK HIGH time               | 100MHz           | 2, 6, 8         | 3.3  | 5.1                                       | 5.7  | ns   |

| T <sub>SDKL</sub>                   | SDRAM CLK LOW time                | ]                | 3, 6, 8         | 3.1  | 4.9                                       | 5.5  | 1    |

| T <sub>SDKP</sub>                   | SDRAM clock period                |                  | 1, 6            | 7.4  | 7.5                                       | 7.7  |      |

| T <sub>SDKH</sub>                   | SDRAM CLK HIGH time               | 133MHz           | 2, 6, 8         | 2.6  | 3.2                                       | 3.8  | ns   |

| T <sub>SDKL</sub>                   | SDRAM CLK LOW time                | 1                | 3, 6, 8         | 2.1  | 2.8                                       | 3.5  | 1    |

| T <sub>SDRISE</sub>                 | SDRAM rise time                   |                  | 4, 6, 10        | 1.5  | 2.0                                       | 4.0  | V/ns |

| T <sub>SDFALL</sub>                 | SDRAM fall time                   |                  | 4, 6, 11        | 1.5  | 2.9                                       | 4.0  | V/ns |

| T <sub>PLH</sub>                    | SDRAM buffer LH propagation delay |                  | 6, 7            | 1.0  | 2.5                                       | 3.5  | ns   |

| T <sub>PHL</sub>                    | SDRAM buffer HL propagation delay |                  | 6, 7            | 1.0  | 2.5                                       | 3.5  | ns   |

| T <sub>PZL</sub> , T <sub>PZH</sub> | SDRAM buffer enable time          |                  | 6, 7            | 1.0  | 2.6                                       | 5.0  | ns   |

| T <sub>PLZ</sub> , T <sub>PHZ</sub> | SDRAM buffer disable time         |                  | 6, 7            | 1.0  | 2.7                                       | 5.0  | ns   |

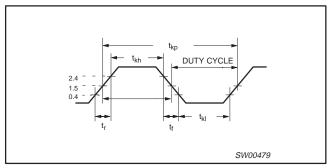

| DUTY CYCLE                          | Output Duty Cycle                 | Measured at 1.5V | 5, 6, 7         | 45   | 52                                        | 55   | %    |

| T <sub>SDSKW</sub>                  | SDRAM Bus CLK skew                |                  | 1, 6            |      | 150                                       | 250  | ps   |

| T <sub>DDSKW</sub>                  | Device to device skew             |                  |                 |      |                                           | 250  | ps   |

- 1. Clock period and skew are measured on the rising edge at 1.5V.

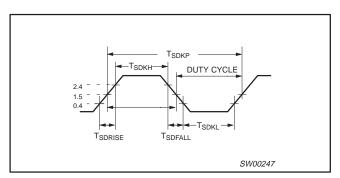

- T<sub>SDKH</sub> is measured at 2.4V as shown in Figure 4.

T<sub>SDKL</sub> is measured at 0.4V as shown in Figure 4.

- T<sub>SDRL</sub> is integrated at 0.44 as shown in Figure 4.

T<sub>SDRISE</sub> and T<sub>SDFALL</sub> are measured as a transition through the threshold region V<sub>OL</sub> = 0.4V and V<sub>OH</sub> = 2.4V (1mA) JEDEC specification.

Duty cycle should be tested with a 50/50% input.

Over MIN (20pF) to MAX (30pF) discrete load, process, voltage, and temperature.

- 7. Input edge rate for these tests must be faster than 1 V/ns.

- Calculated at minimum edge rate (1.5ns) to guarantee 45/55% duty cycle at 1.5V. Pulsewidth is required to be wider at the faster edge to ensure duty cycle specification is met.

- 9. All typical values are at  $V_{CC} = 3.3V$  and  $T_{amb} = 25^{\circ}C$ . 10. Typical is measured with MAX (30pf) discrete load.

- 11. Typical is measured with MIN (20pf) discrete load.

PCK2001

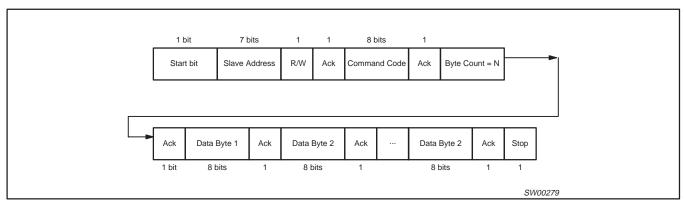

### I<sup>2</sup>C CONSIDERATIONS

I<sup>2</sup>C has been chosen as the serial bus interface to control the PCK2001. I<sup>2</sup>C was chosen to support the JEDEC proposal JC-42.5 168 Pin Unbuffered SDRAM DIMM. All vendors are required to determine the legal issues associated with the manufacture of I<sup>2</sup>C devices.

1) Address assignment: The clock driver in this specification uses the single, 7-bit address shown below. All devices can use the address if only one master clock driver is used in a design. The address can be re-used for the CKBF device if no other conflicting I<sup>2</sup>C clock driver is used in the system.

The following address was confirmed by Philips on 09/04/96.

| A6 | A5 | A4 | А3 | A2 | A1 | A0 | R/W# |

|----|----|----|----|----|----|----|------|

| 1  | 1  | 0  | 1  | 0  | 0  | 1  | 0    |

**NOTE:** The R/W# bit is used by the I<sup>2</sup>C controller as a data direction bit. A 'zero' indicates a transmission (WRITE) to the clock device. A 'one' indicates a request for data (READ) from the clock driver. Since the definition of the clock buffer only allows the controller to WRITE data; the R/W# bit of the address will always be seen as 'zero'. Optimal address decoding of this bit is left to the vendor.

- 2) Options: It is our understanding that metal mask options and other pinouts of this type of clock driver will be allowed to use the same address as the original CKBF device. I<sup>2</sup>C addresses are defined in terms of function (master clock driver) rather than form (pinout, and option).

- 3) Slave/Receiver: The clock driver is assumed to require only slave/receiver functionality. Slave/transmitter functionality is optional.

- 4) Data Transfer Rate: 100 kbits/s (standard mode) is the base functionality required. Fast mode (400 kbits/s) functionality is optional.

- 5) Logic Levels: I<sup>2</sup>C logic levels are based on a percentage of V<sub>DD</sub> for the controller and other devices on the bus. Assume all devices are based on a 3.3 Volt supply.

- 6) Data Byte Format: Byte format is 8 Bits as described in the following appendices.

- 7) Data Protocol: To simplify the clock I<sup>2</sup>C interface, the clock driver serial protocol was specified to use only block writes from the controller. The bytes must be accessed in sequential order from lowest to highest byte with the ability to stop after any complete byte has been transferred. Indexed bytes are not allowed. However, the SMBus controller has a more specific format than the generic I<sup>2</sup>C protocol.

The clock driver must meet this protocol which is more rigorous than previously stated I<sup>2</sup>C protocol. Treat the description from the viewpoint of controller. The controller "writes" to the clock driver and if possible would "read" from the clock driver (the clock driver is a slave/receiver only and is incapable of this transaction.)

"The block write begins with a slave address and a write condition. After the command code the host (controller) issues a byte count which describes how many more bytes will follow in the message. If the host had 20 bytes to send, the first byte would be the number 20 (14h), followed by the 20 bytes of data. The byte count may not be 0. A block write command is allowed to transfer a maximum of 32 data bytes."

NOTE: The acknowledgement bit is returned by the slave/receiver (the clock driver).

# 14.318-150 MHz I<sup>2</sup>C 1:18 Clock Buffer

PCK2001

Consider the command code and the byte count bytes required as the first two bytes of any transfer. The command code is software programmable via the controller, but will be specified as 0000 0000 in the clock specification. The byte count byte is the number of additional bytes required to transfer, not counting the command code and byte count bytes. Additionally, the byte count byte is required to be a minimum of 1 byte and a maximum of 32 bytes to satisfy the above requirement.

### For example:

| Byte count byte Notes: |      | Notes:                                                                       |

|------------------------|------|------------------------------------------------------------------------------|

| MSB                    | LSB  |                                                                              |

| 0000                   | 0000 | Not allowed. Must have at least one byte.                                    |

| 0000                   | 0001 | Data for functional and frequency select register (currently byte 0 in spec) |

| 0000                   | 0010 | Reads first two bytes of data. (byte 0 then byte 1)                          |

| 0000                   | 0011 | Reads first three bytes (byte 0, 1, 2 in order)                              |

| 0000                   | 0100 | Reads first four bytes (byte 0, 1, 2, 3 in order)                            |

| 0000                   | 0101 | Reads first five bytes (byte 0, 1, 2, 3, 4 in order)                         |

| 0000                   | 0110 | Reads first six bytes (byte 0, 1, 2, 3, 4, 5 in order)                       |

| 0000                   | 0111 | Reads first seven bytes (byte 0, 1, 2, 3, 4, 5, 6 in order)                  |

| 0010                   | 0000 | Max byte count supported = 32                                                |

A transfer is considered valid after the acknowledge bit corresponding to the byte count is read by the controller. The serial controller interface can be simplified by discarding the information in both the command code and the byte count bytes and simply reading all the bytes that are sent to the clock driver after being addressed by the controller. It is expected that the controller will not provide more bytes than the clock driver can handle. A clock vendor may choose to discard any number of bytes that exceed the defined byte count.

- 8) Clock stretching: The clock device must not hold/stretch the SCLOCK or SDATA lines low for more than 10 mS. Clock stretching is discouraged and should only be used as a last resort. Stretching the clock/data lines for longer than this time puts the device in an error/time-out mode and may not be supported in all platforms. It is assumed that all data transfers can be completed as specified without the use of clock/data stretching.

- 9) General Call: It is assumed that the clock driver will not have to respond to the "general call."

- 10) Electrical Characteristics: All electrical characteristics must meet the standard mode specifications found in section 15 of the I<sup>2</sup>C specification.

- a) Pull-Up Resistors: Any internal resistors pull-ups on the SDATA and SCLOCK inputs must be stated in the individual datasheet. The use of internal pull-ups on these pins of below 100K is discouraged. Assume that the board designer will use a single external pull-up resistor for each line and that these values are in the 5 6K Ohm range. Assume one I<sup>2</sup>C device per DIMM (serial presence detect), one I<sup>2</sup>C controller, one clock driver plus one/two more I<sup>2</sup>C devices on the platform for capacitive loading purposes.

- (b) Input Glitch Filters: Only fast mode I<sup>2</sup>C devices require input glitch filters to suppress bus noise. The clock driver is specified as a standard mode device and is not required to support this feature.

- 11) PWR DWN#: If a clock driver is placed in PWR DWN# mode, the SDATA and SCLK inputs must be Tri-Stated and the device must retain all programming information. I<sub>dd</sub> current due to the I<sup>2</sup>C circuitry must be characterized and in the data sheet.

For specific I<sup>2</sup>C information consult the Philips I<sup>2</sup>C Peripherals Data Handbook IC12 (1997)

# 14.318-150 MHz I<sup>2</sup>C 1:18 Clock Buffer

PCK2001

### SERIAL CONFIGURATION MAP

The serial bits will be read by the clock buffer in the following order:

Byte 0 - Bits 7, 6, 5, 4, 3, 2, 1, 0

Byte 1 - Bits 7, 6, 5, 4, 3, 2, 1, 0

Byte 2 - Bits 7, 6, 5, 4, 3, 2, 1, 0

All unused register bits (Reserved and N/A) should be desined as "Dont Care". It is expected that the controller will force all of these bits to a "0" level.

All register bits labeled "Initialize to 0" must be written to zero during intialization. Failure to do so may result in a higher than normal operating current. The controller will read back the last written value.

Byte 0: Output active/inactive register

1 = enable; 0 = disable

| BIT | PIN# | NAME     | DESCRIPTION     |  |  |  |  |  |  |

|-----|------|----------|-----------------|--|--|--|--|--|--|

| 7   | 18   | BUF_OUT7 | Active/Inactive |  |  |  |  |  |  |

| 6   | 17   | BUF_OUT6 | Active/Inactive |  |  |  |  |  |  |

| 5   | 14   | BUF_OUT5 | Active/Inactive |  |  |  |  |  |  |

| 4   | 13   | BUF_OUT4 | Active/Inactive |  |  |  |  |  |  |

| 3   | 9    | BUF_OUT3 | Active/Inactive |  |  |  |  |  |  |

| 2   | 8    | BUF_OUT2 | Active/Inactive |  |  |  |  |  |  |

| 1   | 5    | BUF_OUT1 | Active/Inactive |  |  |  |  |  |  |

| 0   | 4    | BUF_OUT0 | Active/Inactive |  |  |  |  |  |  |

### NOTE:

# Byte 1: Output active/inactive register

1 = enable; 0 = disable

| BIT | PIN# | NAME      | DESCRIPTION     |

|-----|------|-----------|-----------------|

| 7   | 45   | BUF_OUT15 | Active/Inactive |

| 6   | 44   | BUF_OUT14 | Active/Inactive |

| 5   | 41   | BUF_OUT13 | Active/Inactive |

| 4   | 40   | BUF_OUT12 | Active/Inactive |

| 3   | 36   | BUF_OUT11 | Active/Inactive |

| 2   | 35   | BUF_OUT10 | Active/Inactive |

| 1   | 32   | BUF_OUT9  | Active/Inactive |

| 0   | 31   | BUF_OUT8  | Active/Inactive |

### NOTE:

# Byte 2: Optional register for possible future requirments

|     |      | ·          | · · · · · · · · · · · · · · · · · · · |

|-----|------|------------|---------------------------------------|

| BIT | PIN# | NAME       | DESCRIPTION                           |

| 7   | 28   | BUF_OUT17  | Active/Inactive                       |

| 6   | 21   | BUF_OUT16  | Active/Inactive                       |

| 5   | _    | (reserved) | (reserved)                            |

| 4   | _    | (reserved) | (reserved)                            |

| 3   | _    | (reserved) | (reserved)                            |

| 2   | _    | (reserved) | (reserved)                            |

| 1   | _    | (reserved) | (reserved)                            |

| 0   | _    | (reserved) | (reserved)                            |

# NOTE:

Inactive means outputs are held LOW and are disabled from switching. These outputs are designed to be configured at power-on and are not expected to be configured during the normal modes of operation.

Inactive means outputs are held LOW and are disabled from switching. These outputs are designed to be configured at power-on and are not expected to be configured during the normal modes of operation.

<sup>1.</sup> Inactive means outputs are held LOW and are disabled from switching. These outputs are designed to be configured at power-on and are not expected to be configured during the normal modes of operation.

# 14.318-150 MHz I<sup>2</sup>C 1:18 Clock Buffer

PCK2001

# **AC WAVEFORMS**

$\begin{array}{l} V_M=1.5V \\ V_X=V_{OL}+0.3V \\ V_Y=V_{OH}-0.3V \\ V_{OL} \ and \ V_{OH} \ are \ the \ typical \ output \ voltage \ drop \ that \ occur \ with \ the \ output \ load. \end{array}$

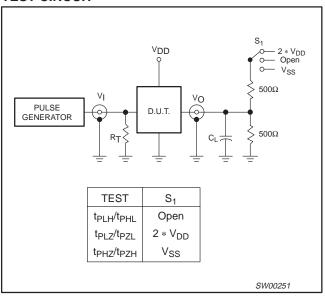

Figure 1. Load circuitry for switching times.

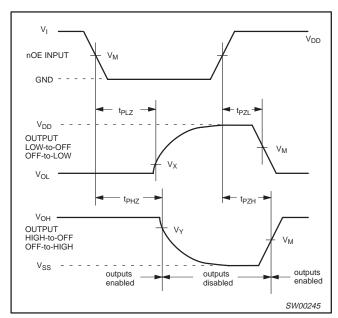

Figure 2. 3-State enable and disable times

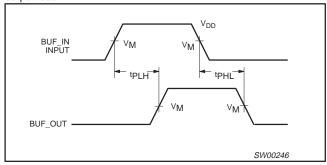

Figure 3. Buffer Output clock

Figure 4. SDRAM Output clock

# **TEST CIRCUIT**

Figure 5. Load circuitry for switching times

PCK2001

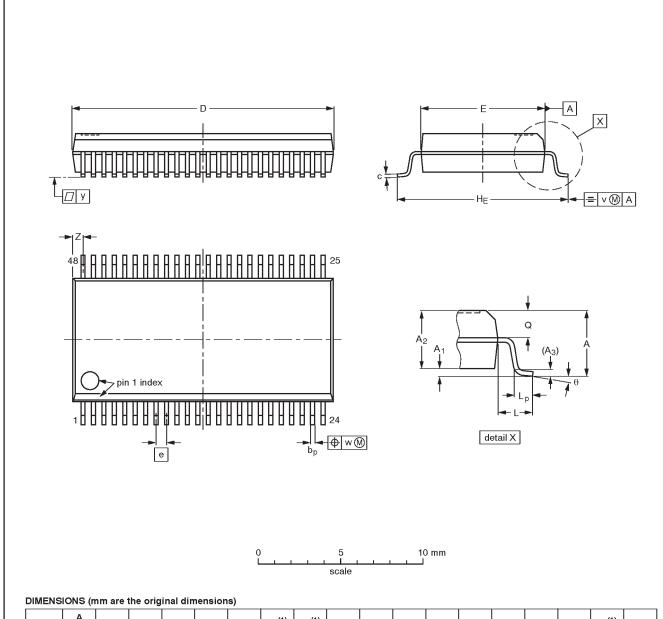

# SSOP48: plastic shrink small outline package; 48 leads; body width 7.5 mm

SOT370-1

| UNIT | A<br>max. | Α1         | A <sub>2</sub> | <b>A</b> <sub>3</sub> | bp         | С            | D <sup>(1)</sup> | E <sup>(1)</sup> | е     | HE           | L   | Lp         | Q          | v    | w    | у   | Z <sup>(1)</sup> | θ        |

|------|-----------|------------|----------------|-----------------------|------------|--------------|------------------|------------------|-------|--------------|-----|------------|------------|------|------|-----|------------------|----------|

| mm   | 2.8       | 0.4<br>0.2 | 2.35<br>2.20   | 0.25                  | 0.3<br>0.2 | 0.22<br>0.13 | 16.00<br>15.75   | 7.6<br>7.4       | 0.635 | 10.4<br>10.1 | 1.4 | 1.0<br>0.6 | 1.2<br>1.0 | 0.25 | 0.18 | 0.1 | 0.85<br>0.40     | 8°<br>0° |

### Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  |     | REFER          | EUROPEAN | ISSUE DATE |  |                                 |  |

|----------|-----|----------------|----------|------------|--|---------------------------------|--|

| VERSION  | IEC | IEC JEDEC EIAJ |          |            |  | ISSUEDATE                       |  |

| SOT370-1 |     | MO-118AA       |          |            |  | <del>93-11-02</del><br>95-02-04 |  |

1999 Jul 06 12

# 14.318-150 MHz I<sup>2</sup>C 1:18 Clock Buffer

PCK2001

### Data sheet status

| Data sheet status         | Product status | Definition [1]                                                                                                                                                                                                                                             |

|---------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective specification   | Development    | This data sheet contains the design target or goal specifications for product development. Specification may change in any manner without notice.                                                                                                          |

| Preliminary specification | Qualification  | This data sheet contains preliminary data, and supplementary data will be published at a later date. Philips Semiconductors reserves the right to make changes at any time without notice in order to improve design and supply the best possible product. |

| Product specification     | Production     | This data sheet contains final specifications. Philips Semiconductors reserves the right to make changes at any time without notice in order to improve design and supply the best possible product.                                                       |

<sup>[1]</sup> Please consult the most recently issued datasheet before initiating or completing a design.

### **Definitions**

**Short-form specification** — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

**Application information** — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

### **Disclaimers**

**Life support** — These products are not designed for use in life support appliances, devices or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

Philips Semiconductors 811 East Arques Avenue P.O. Box 3409 Sunnyvale, California 94088–3409 Telephone 800-234-7381 © Copyright Philips Electronics North America Corporation 1999 All rights reserved. Printed in U.S.A.

Date of release: 07-99

Document order number: 9397-750-06208

Let's make things better.

Philips Semiconductors

SUNSTAR 商斯达实业集团是集研发、生产、工程、销售、代理经销 、技术咨询、信息服务等为一体的高科技企业,是专业高科技电子产品生产厂家,是具有 10 多年历史的专业电子元器件供应商,是中国最早和最大的仓储式连锁规模经营大型综合电子零部件代理分销商之一,是一家专业代理和分銷世界各大品牌 IC 芯片和電子元器件的连锁经营綜合性国际公司,专业经营进口、国产名厂名牌电子元件,型号、种类齐全。在香港、北京、深圳、上海、西安、成都等全国主要电子市场设有直属分公司和产品展示展销窗口门市部专卖店及代理分销商,已在全国范围内建成强大统一的供货和代理分销网络。 我们专业代理经销、开发生产电子元器件、集成电路、传感器、微波光电元器件、工控机/DOC/DOM 电子盘、专用电路、单片机开发、MCU/DSP/ARM/FPGA 软件硬件、二极管、三极管、模块等,是您可靠的一站式现货配套供应商、方案提供商、部件功能模块开发配套商。商斯达实业公司拥有庞大的资料库,有数位毕业于著名高校——有中国电子工业摇篮之称的西安电子科技大学(西军电)并长期从事国防尖端科技研究的高级工程师为您精挑细选、量身订做各种高科技电子元器件,并解决各种技术问题。

微波光电部专业代理经销高频、微波、光纤、光电元器件、组件、部件、模块、整机;电磁兼容元器件、材料、设备;微波 CAD、EDA 软件、开发测试仿真工具;微波、光纤仪器仪表。欢迎国外高科技微波、光纤厂商将优秀产品介绍到中国、共同开拓市场。长期大量现货专业批发高频、微波、卫星、光纤、电视、CATV 器件: 晶振、VCO、连接器、PIN 开关、变容二极管、开关二极管、低噪晶体管、功率电阻及电容、放大器、功率管、MMIC、混频器、耦合器、功分器、振荡器、合成器、衰减器、滤波器、隔离器、环行器、移相器、调制解调器;光电子元器件和组件:红外发射管、红外接收管、光电开关、光敏管、发光二极管和发光二极管组件、半导体激光二极管和激光器组件、光电探测器和光接收组件、光发射接收模块、光纤激光器和光放大器、光调制器、光开关、DWDM 用光发射和接收器件、用户接入系统光光收发器件与模块、光纤连接器、光纤跳线/尾纤、光衰减器、光纤适 配器、光隔离器、光耦合器、光环行器、光复用器/转换器;无线收发芯片和模组、蓝牙芯片和模组。

更多产品请看本公司产品专用销售网站:

商斯达中国传感器科技信息网: http://www.sensor-ic.com/

商斯达工控安防网: http://www.pc-ps.net/

商斯达电子元器件网: http://www.sunstare.com/

商斯达微波光电产品网:HTTP://www.rfoe.net/

商斯达消费电子产品网://www.icasic.com/

商斯达实业科技产品网://www.sunstars.cn/ 微波元器件销售热线:

地址:深圳市福田区福华路福庆街鸿图大厦 1602 室

电话: 0755-82884100 83397033 83396822 83398585

传真: 0755-83376182 (0) 13823648918 MSN: SUNS8888@hotmail.com

邮编: 518033 E-mail:szss20@163.com QQ: 195847376

深圳赛格展销部: 深圳华强北路赛格电子市场 2583 号 电话: 0755-83665529 25059422

技术支持: 0755-83394033 13501568376

欢迎索取免费详细资料、设计指南和光盘 : 产品凡多,未能尽录,欢迎来电查询。

北京分公司:北京海淀区知春路 132 号中发电子大厦 3097 号

TEL: 010-81159046 82615020 13501189838 FAX: 010-62543996

上海分公司: 上海市北京东路 668 号上海賽格电子市场 D125 号

TEL: 021-28311762 56703037 13701955389 FAX: 021-56703037

西安分公司: 西安高新开发区 20 所(中国电子科技集团导航技术研究所)

西安劳动南路 88 号电子商城二楼 D23 号

TEL: 029-81022619 13072977981 FAX:029-88789382