INTEGRATED CIRCUITS

Product specification Supersedes data of 1999 May 17 File under Integrated Circuits, IC18 1999 Jun 04

#### CONTENTS

| 1     | FEATURES                      |

|-------|-------------------------------|

| 2     | GENERAL DESCRIPTION           |

| 3     | QUICK REFERENCE DATA          |

| 4     | ORDERING INFORMATION          |

| 5     | BLOCK DIAGRAM                 |

| 6     | PINNING                       |

| 7     | FUNCTIONAL DESCRIPTION        |

| 7.1   | Overview                      |

| 7.2   | The 80C51XA processor         |

| 7.3   | The GPS correlators           |

| 7.4   | Memory organization           |

| 7.4.1 | Data memory space             |

| 7.4.2 | Code memory space             |

| 7.5   | CPU peripheral features       |

| 7.5.1 | Timers/counters               |

| 7.5.2 | Watchdog timer                |

| 7.5.3 | UARTs                         |

| 7.5.4 | RF IC programming port        |

| 7.5.5 | General purpose I/O           |

| 7.6   | The real-time clock           |

| 7.7   | The external bus              |

| 7.7.1 | Program memory chip select    |

| 7.7.2 | Data memory chip select       |

| 7.7.3 | Read strobe                   |

| 7.7.4 | Write LOW byte strobe         |

| 7.7.5 | Write HIGH byte strobe        |

| 7.8   | Backup supplies and reset     |

| 7.8.1 | Supply domains                |

| 7.8.2 | Power-down design strategy    |

| 7.8.3 | System reset control          |

| 7.8.4 | Power saving modes            |

| 7.9   | Clock signals and oscillators |

| 7.9.1 | System clock (XTAL1)          |

| 7.9.2 | RTC clock (XTAL3)             |

| 7.9.3 | Reference clock (RCLK)        |

| LIMITING VALUES         |

|-------------------------|

| LIVITING VALUES         |

|                         |

| THERMAL CHARACTERISTICS |

|                         |

|                         |

| DC CHARACTERISTICS      |

- DC CHARACTERISTICS

AC CHARACTERISTICS

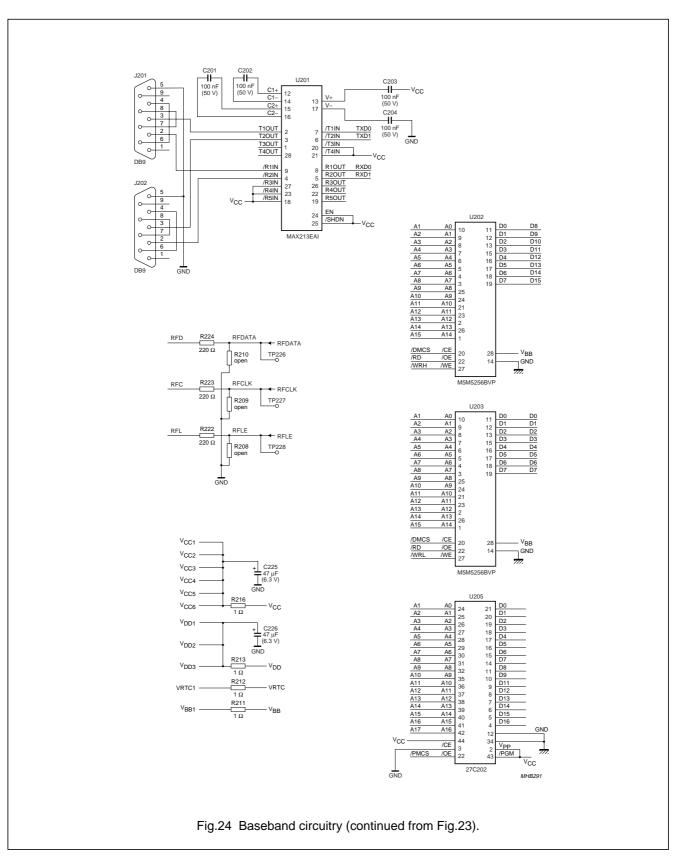

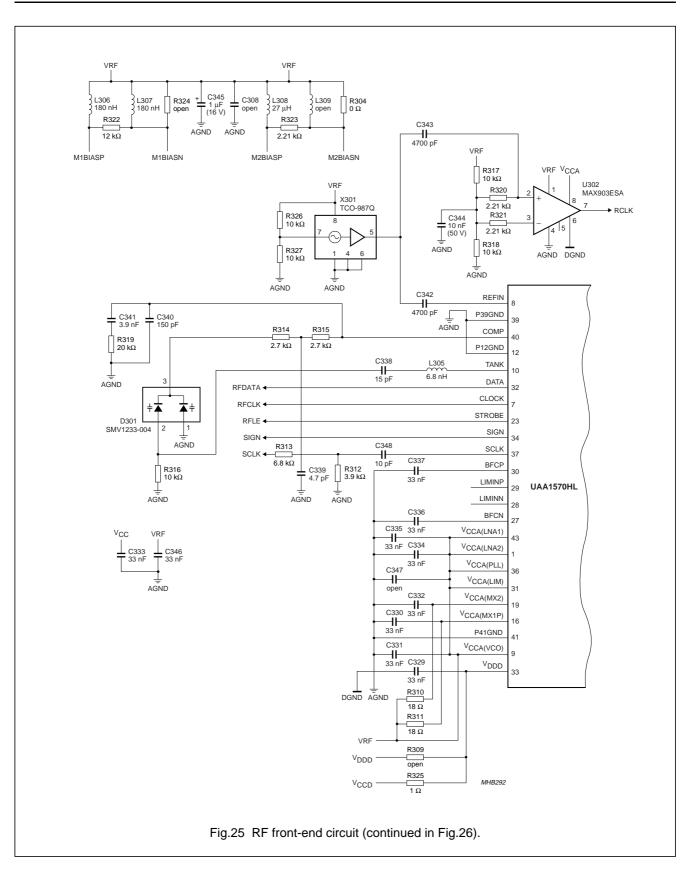

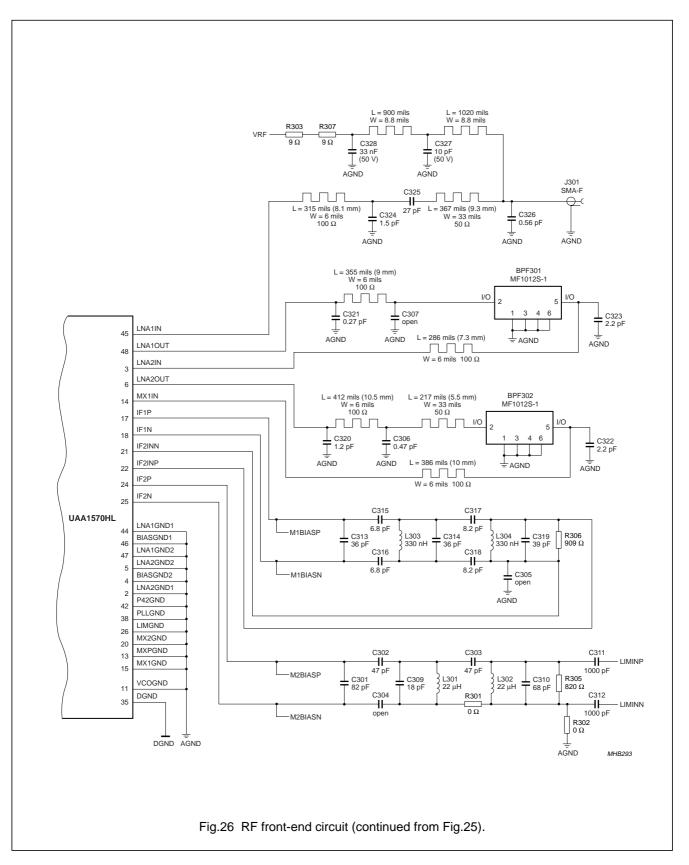

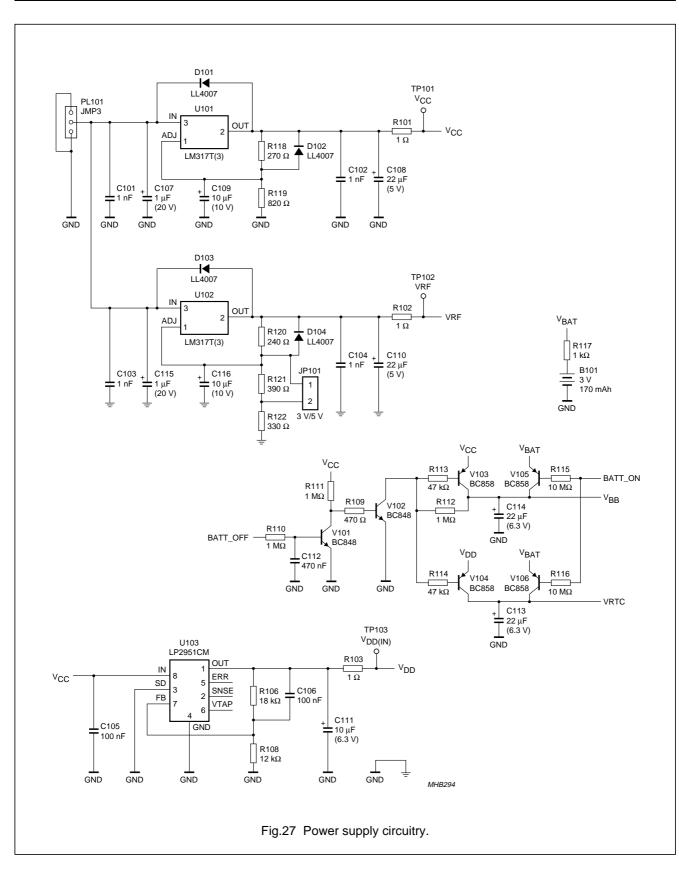

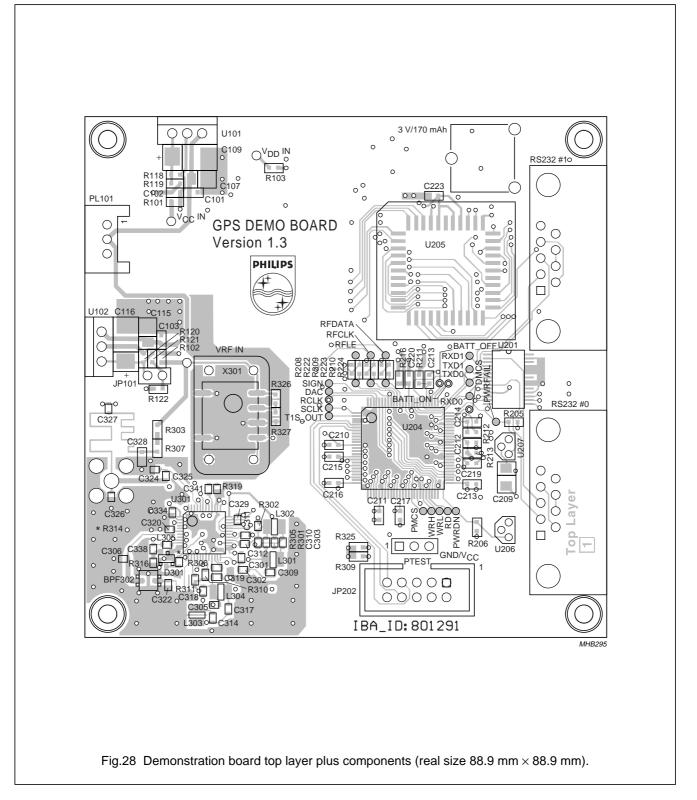

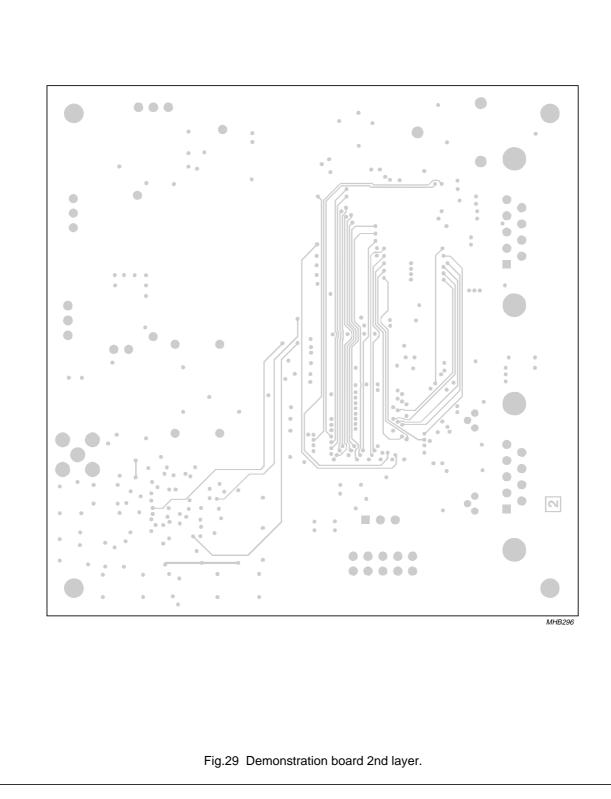

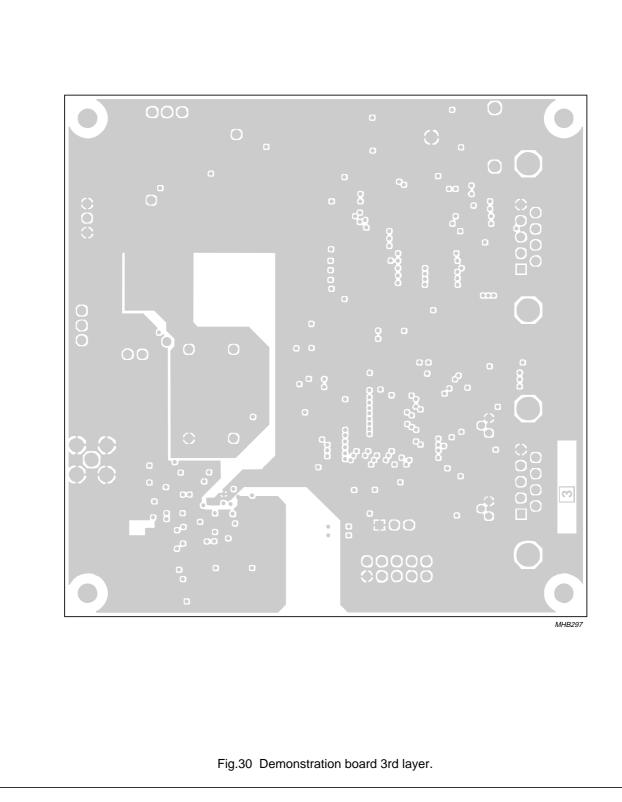

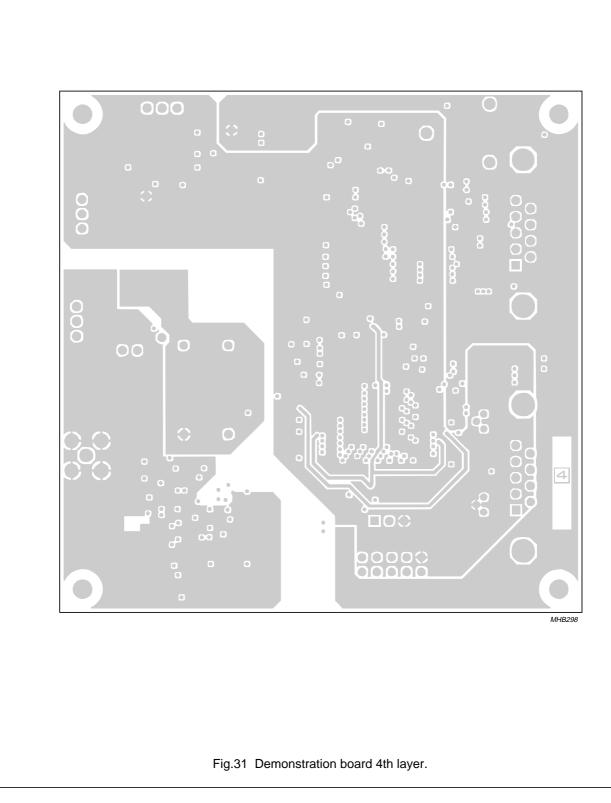

DEFAULT APPLICATION AND DEMONSTRATION BOARD

- 13 PACKAGE OUTLINE

14 SOLDERING

8

9

- 14.1 Introduction to soldering surface mount packages

- 14.2 Reflow soldering

- 14.3 Wave soldering

- 14.4 Manual soldering

- 14.5 Suitability of surface mount IC packages for wave and reflow soldering methods

- 15 DEFINITIONS

- 16 LIFE SUPPORT APPLICATIONS

#### Product specification

SAA1575HL

### Global Positioning System (GPS) baseband processor

#### **1 FEATURES**

- Single-chip GPS baseband solution with built-in 16-bit microcontroller

- All digital, 0.5 micron CMOS technology

- · Single power supply with full 3 V operation

- Separate I/O power supply pins for operation with 3 or 5 V external devices

- Up to 30 MHz system clock from on-chip crystal oscillator or external clock input

- · 2 kbytes words internal data memory for fast execution

- External bus for up to 512 kbytes words data memory and 512 kbytes words program memory

- Programmable external bus timing to match external memory speed

- · Chip selection outputs to reduce glue logic requirements

- Reset controller for power-down detection and servicing

- 8 GPS channel correlators driven by firmware for flexible GPS correlation algorithms

- 1 second pulse output of GPS time

- 2-bit digital IF GPS signal input synchronized to external sample clock

- 2 fully duplex UARTs for communication with host system processor and other devices

- Real-time clock with 32.768 kHz crystal and supply for low power timekeeping

- Watchdog timer

- Power-down modes under firmware control

- 100-pin LQFP package

- 50 mA supply current (typ.) when 8 GPS channels in track (approximate).

#### 2 GENERAL DESCRIPTION

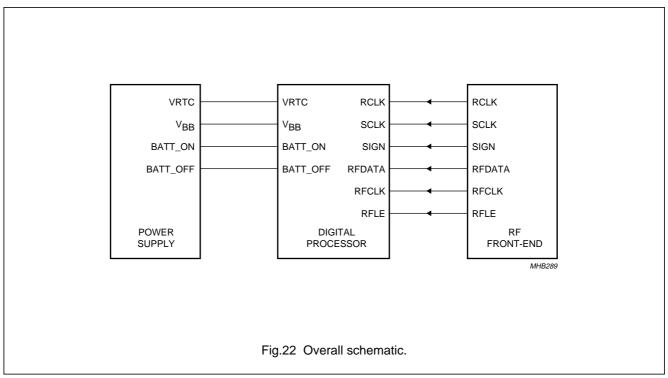

The SAA1575HL is an integrated circuit which implements a complete baseband function for Global Positioning System (GPS) receivers. It combines a 16-bit Philips 80C51XA microcontroller, 8 GPS channel correlators and related peripherals in a single IC. Users can implement a complete GPS receiver using only the SAA1575HL, the UAA1570HL front-end Philips IC (or similar), external memory and a few discrete components.

The IC is aimed at low cost applications. A low power solution was also used where possible, although this was of secondary importance to cost. The core of the SAA1575HL operates at 3 V.

However, for compatibility with current automotive applications, the periphery is supplied from separate pins and can be operated between 3 and 5 V, as required.

The function of the SAA1575HL is to read the 1 or 2-bit sampled IF bitstream from a front-end IC and, under control of firmware on an external ROM, calculate the full GPS solution. The results are communicated to a host in National Maritime Electronics Association (NMEA) format via a standard serial port. A second serial port can be used to provide differential GPS information to the processor for more advance applications. In addition, various other functions are integrated onto the IC such as a real-time GPS clock, a power-down/reset controller, timer/counters and a watchdog timer.

To summarise, the SAA1575HL has the following functional units:

- 16-bit 80C51XA microcontroller core

- 2 kbytes words on-chip SRAM (16-bit words)

- 8 GPS channel correlators

- 2 UARTs

- 8 general purpose I/O lines

- 3 timer/counters

- 1 real-time clock

- 1 watchdog timer

- 1 power-down/reset controller.

The structure is based on a 16-bit microcontroller core operating on all other units as memory mapped peripherals and registers. A 16-bit data bus and a 19-bit address bus are extended to external pins so that external data and program memory can be accessed. On-chip decoder circuits eliminate the need for external glue logic for external memory access.

Each of the 8 GPS channel correlators includes a carrier Numerically Controlled Oscillator (NCO), PN code generator, phase rotator and low-pass filter. They correlate the local PN sequence with the digitized input GPS signal and generate the filtered correlation result for the microcontroller. The firmware provided then generates a navigation solution and provides standard GPS data outputs to the user.

SAA1575HL

The GPS firmware is located in off-chip program memory. It processes the GPS signals from up to 8 satellites and generates GPS information that can be output to the host processor through one of the two serial ports. Much of hardware configuration of the SAA1575HL can be controlled by the firmware and so details such as the external bus timing may change between firmware revisions. For the purpose of this document, the standard Philips firmware has been assumed (release HD00).

#### **3 QUICK REFERENCE DATA**

| SYMBOL                | PARAMETER                           | CONDITIONS                     | MIN. | TYP. | MAX. | UNIT |

|-----------------------|-------------------------------------|--------------------------------|------|------|------|------|

| V <sub>CC(core)</sub> | core supply voltage                 |                                | 2.7  | 3.3  | 3.6  | V    |

| V <sub>CC(P)</sub>    | peripheral supply voltage           |                                | 2.7  | 5.0  | 5.5  | V    |

| V <sub>CC(R)</sub>    | real-time clock core supply voltage |                                | 2.4  | 3.3  | 3.6  | V    |

| V <sub>CC(B)</sub>    | backup peripheral supply voltage    |                                | 2.7  | 5.0  | 5.5  | V    |

| I <sub>CC(core)</sub> | core supply current                 | normal mode                    | -    | 35   | -    | mA   |

|                       |                                     | sleep mode                     | -    | 15   | -    | mA   |

| I <sub>CC(R)</sub>    | real-time clock core supply current | f <sub>RTC</sub> = 32.768 kHz  | -    | 10   | 30   | μA   |

| I <sub>CC(B)</sub>    | backup peripheral supply current    | normal mode; dependent on load | -    | 5    | -    | mA   |

|                       |                                     | sleep mode                     | -    | 1    | -    | μA   |

| I <sub>CC(P)</sub>    | peripheral supply current           | normal mode                    | _    | 20   | -    | mA   |

|                       |                                     | sleep mode                     | -    | -    | 1    | mA   |

| f <sub>osc</sub>      | oscillator frequency                |                                | 26   | 30   | 32   | MHz  |

| T <sub>amb</sub>      | ambient temperature                 |                                | -40  | +25  | +85  | °C   |

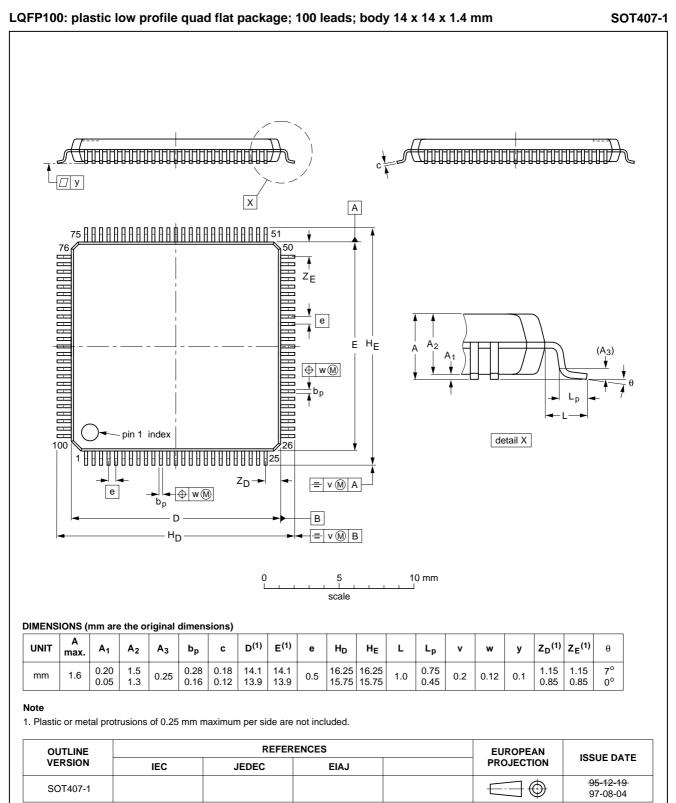

#### 4 ORDERING INFORMATION

| TYPE      | PACKAGE |                                                                                       |          |  |  |  |

|-----------|---------|---------------------------------------------------------------------------------------|----------|--|--|--|

| NUMBER    | NAME    | NAME DESCRIPTION VERSION                                                              |          |  |  |  |

| SAA1575HL | LQFP100 | plastic low profile quad flat package; 100 leads; body 14 $\times$ 14 $\times$ 1.4 mm | SOT407-1 |  |  |  |

#### 5 BLOCK DIAGRAM

#### Product specification

# Global Positioning System (GPS) baseband processor

#### 6 PINNING

| SYMBOL                | PIN | I/O | DESCRIPTION                                                                                                                                                                                                            |

|-----------------------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCLK                  | 1   | 0   | <b>Sample clock</b> : sample clock generated internally by dividing down the RCLK (reference clock) input. This output is provided for use by the front-end IC.                                                        |

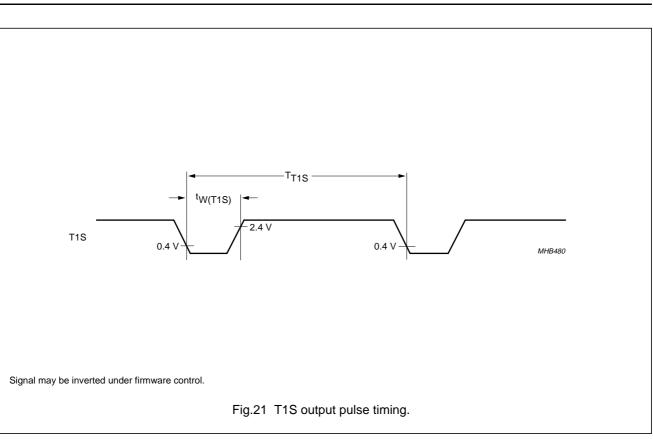

| T1S                   | 2   | 0   | <b>GPS time pulse</b> : a 1 pulse per second output whose rising or falling edge (firmware controlled) is synchronized to GPS time when the receiver is tracking a GPS signal. The pulse length is approximately 1 ms. |

| TP3                   | 3   | I   | Test pin: tie HIGH                                                                                                                                                                                                     |

| TP4                   | 4   | I   | Test pin: tie HIGH                                                                                                                                                                                                     |

| GPIO5                 | 5   | I/O | <b>GPIO bit 5</b> : standard general purpose I/O mapped into the segment 15 of the address space. The top 4 bits can be used as the XA external timer control access pins (T0, T1, T2 and T2EX).                       |

| GPIO6                 | 6   | I/O | <b>GPIO bit 6</b> : standard general purpose I/O mapped into the segment 15 of the address space. The top 4 bits can be used as the XA external timer control access pins (T0, T1, T2 and T2EX).                       |

| GPIO7                 | 7   | I/O | <b>GPIO bit 7</b> : standard general purpose I/O mapped into the segment 15 of the address space. The top 4 bits can be used as the XA external timer control access pins (T0, T1, T2 and T2EX).                       |

| n.c.                  | 8   | 0   | Not connected: do not connect                                                                                                                                                                                          |

| n.c.                  | 9   | 0   | Not connected: do not connect                                                                                                                                                                                          |

| A19                   | 10  | 0   | External memory address bus bit 19: 19-bit address bus; used to address external RAM and program memory                                                                                                                |

| A18                   | 11  | 0   | External memory address bus bit 18: 19-bit address bus; used to address external RAM and program memory                                                                                                                |

| V <sub>CC(core)</sub> | 12  | -   | <b>Main core power supply</b> : 2.7 to 3.6 V only; main supply for the core in normal operation                                                                                                                        |

| V <sub>SS</sub>       | 13  | _   | Ground: 0 V reference                                                                                                                                                                                                  |

| XTAL1                 | 14  | I   | <b>Crystal 1</b> : input to the inverting amplifier; used in the system oscillator circuit and input to the internal clock generator circuits                                                                          |

| XTAL2                 | 15  | 0   | Crystal 2: output from the system oscillator amplifier                                                                                                                                                                 |

| V <sub>CC(P)</sub>    | 16  | -   | <b>Main I/O power supply</b> : 2.7 to 5.5 V operating range; main supply for the periphery in normal operation                                                                                                         |

| V <sub>SS</sub>       | 17  | -   | Ground: 0 V reference                                                                                                                                                                                                  |

| A17                   | 18  | 0   | External memory address bus bit 17: 19-bit address bus; used to address external RAM and program memory                                                                                                                |

| A16                   | 19  | 0   | External memory address bus bit 16: 19-bit address bus; used to address external RAM and program memory                                                                                                                |

| A15                   | 20  | 0   | External memory address bus bit 15: 19-bit address bus; used to address external RAM and program memory                                                                                                                |

| A14                   | 21  | 0   | <b>External memory address bus bit 14</b> : 19-bit address bus; used to address external RAM and program memory                                                                                                        |

| A13                   | 22  | 0   | External memory address bus bit 13: 19-bit address bus; used to address external RAM and program memory                                                                                                                |

| A12                   | 23  | 0   | <b>External memory address bus bit 12</b> : 19-bit address bus; used to address external RAM and program memory                                                                                                        |

1999 Jun 04

| SYMBOL                | PIN | I/O | DESCRIPTION                                                                                                                                                                                                                                                                  |  |

|-----------------------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| A11                   | 24  | 0   | <b>External memory address bus bit 11</b> : 19-bit address bus; used to address external RAM and program memory                                                                                                                                                              |  |

| V <sub>CC(P)</sub>    | 25  | -   | <b>Main I/O power supply</b> : 2.7 to 5.5 V operating range; main supply for the periphery in normal operation                                                                                                                                                               |  |

| V <sub>SS</sub>       | 26  | _   | Ground: 0 V reference                                                                                                                                                                                                                                                        |  |

| A10                   | 27  | 0   | <b>External memory address bus bit 10</b> : 19-bit address bus; used to address external RAM and program memory                                                                                                                                                              |  |

| A9                    | 28  | 0   | <b>External memory address bus bit 9</b> : 19-bit address bus; used to address external RAM and program memory                                                                                                                                                               |  |

| A8                    | 29  | 0   | <b>External memory address bus bit 8</b> : 19-bit address bus; used to address external RAM and program memory                                                                                                                                                               |  |

| V <sub>CC(core)</sub> | 30  | -   | <b>Main core power supply</b> : 2.7 to 3.6 V only; main supply for the core in normal operation                                                                                                                                                                              |  |

| V <sub>SS</sub>       | 31  | -   | Ground: 0 V reference                                                                                                                                                                                                                                                        |  |

| A7                    | 32  | 0   | <b>External memory address bus bit 7</b> : 19-bit address bus; used to address external RAM and program memory                                                                                                                                                               |  |

| A6                    | 33  | 0   | <b>External memory address bus bit 6</b> : 19-bit address bus; used to address external RAM and program memory                                                                                                                                                               |  |

| A5                    | 34  | 0   | <b>External memory address bus bit 5</b> : 19-bit address bus; used to address external RAM and program memory                                                                                                                                                               |  |

| A4                    | 35  | 0   | <b>External memory address bus bit 4</b> : 19-bit address bus; used to address external RAM and program memory                                                                                                                                                               |  |

| A3                    | 36  | 0   | <b>External memory address bus bit 3</b> : 19-bit address bus; used to address external RAM and program memory                                                                                                                                                               |  |

| V <sub>CC(P)</sub>    | 37  | -   | <b>Main I/O power supply</b> : 2.7 to 5.5 V operating range; main supply for the periphery in normal operation                                                                                                                                                               |  |

| V <sub>SS</sub>       | 38  | _   | Ground: 0 V reference                                                                                                                                                                                                                                                        |  |

| A2                    | 39  | 0   | <b>External memory address bus bit 2</b> : 19-bit address bus; used to address external RAM and program memory                                                                                                                                                               |  |

| A1                    | 40  | 0   | <b>External memory address bus bit 1</b> : 19-bit address bus; used to address external RAM and program memory                                                                                                                                                               |  |

| PMCS                  | 41  | 0   | External program memory select: external program memory read strobe                                                                                                                                                                                                          |  |

| TP2                   | 42  | I   | Test pin: tie LOW                                                                                                                                                                                                                                                            |  |

| RSTIME                | 43  | Ι   | <b>Reset timer control</b> : this controls the on-chip reset timer. If this is HIGH, reset will be de-asserted approximately 10 ms after both PWRDN and PWRFAIL go HIGH. If this is LOW, reset will be de-asserted approximately 10 µs after both PWRDN and PWRFAIL go HIGH. |  |

| TP1                   | 44  |     | Test pin: tie LOW                                                                                                                                                                                                                                                            |  |

| WRH                   | 45  | I/O | Write MSB: write strobe for external data memory; asserted for both MSB and word write operations; input mode only used for test purposes                                                                                                                                    |  |

| WRL                   | 46  | I/O | Write LSB: write strobe for external data memory; asserted for both LSB and word write operations; input mode only used for test purposes                                                                                                                                    |  |

| RD                    | 47  | I/O | <b>External data read</b> : read strobe for external data memory; input mode only used for test purposes                                                                                                                                                                     |  |

| SYMBOL                | PIN | I/O | DESCRIPTION                                                                                                                                                                                                                                              |  |

|-----------------------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| D15                   | 48  | I/O | <b>External memory data bus</b> : 16-bit data bus; used to connect to external RAM and program memory                                                                                                                                                    |  |

| D14                   | 49  | I/O | <b>External memory data bus bit 14</b> : 16-bit data bus; used to connect to external RAM and program memory                                                                                                                                             |  |

| V <sub>SS</sub>       | 50  | _   | Ground: 0 V reference                                                                                                                                                                                                                                    |  |

| V <sub>CC(P)</sub>    | 51  | -   | <b>fain I/O power supply</b> : 2.7 to 5.5 V operating range; main supply for the peripher<br>n normal operation                                                                                                                                          |  |

| PWRDN                 | 52  | I   | <b>Power-down indicator</b> : a LOW on this pin asserts an XA interrupt intended for use as a power fail interrupt. Once reset is asserted, either by <b>PWRFAIL</b> or the firmware, it will remain asserted until a set time after this pin goes HIGH. |  |

| D13                   | 53  | I/O | <b>External memory data bus bit 13</b> : 16-bit data bus; used to connect to external RAM and program memory                                                                                                                                             |  |

| D12                   | 54  | I/O | <b>External memory data bus bit 12</b> : 16-bit data bus; used to connect to external RAM and program memory                                                                                                                                             |  |

| D11                   | 55  | I/O | <b>External memory data bus bit 11</b> : 16-bit data bus; used to connect to external RAM and program memory                                                                                                                                             |  |

| D10                   | 56  | I/O | <b>External memory data bus bit 10</b> : 16-bit data bus; used to connect to external RAM and program memory                                                                                                                                             |  |

| D9                    | 57  | I/O | <b>External memory data bus bit 9</b> : 16-bit data bus; used to connect to external RAM and program memory                                                                                                                                              |  |

| D8                    | 58  | I/O | <b>External memory data bus bit 8</b> : 16-bit data bus; used to connect to external RAM and program memory                                                                                                                                              |  |

| D7                    | 59  | I/O | <b>External memory data bus bit 7</b> : 16-bit data bus; used to connect to external RAM and program memory                                                                                                                                              |  |

| V <sub>SS</sub>       | 60  | _   | Ground: 0 V reference                                                                                                                                                                                                                                    |  |

| V <sub>CC(P)</sub>    | 61  | -   | <b>Main I/O power supply</b> : 2.7 to 5.5 V operating range; main supply for the periphery in normal operation                                                                                                                                           |  |

| D6                    | 62  | I/O | <b>External memory data bus bit 6</b> : 16-bit data bus; used to connect to external RAM and program memory                                                                                                                                              |  |

| D5                    | 63  | I/O | <b>External memory data bus bit 5</b> : 16-bit data bus; used to connect to external RAM and program memory                                                                                                                                              |  |

| D4                    | 64  | I/O | <b>External memory data bus bit 4</b> : 16-bit data bus; used to connect to external RAM and program memory                                                                                                                                              |  |

| V <sub>SS</sub>       | 65  | _   | Ground: 0 V reference                                                                                                                                                                                                                                    |  |

| V <sub>CC(core)</sub> | 66  | -   | Main core power supply: 2.7 to 3.6 V only; main supply for the core in normal operation                                                                                                                                                                  |  |

| D3                    | 67  | I/O | <b>External memory data bus bit 3</b> : 16-bit data bus; used to connect to external RAM and program memory                                                                                                                                              |  |

| D2                    | 68  | I/O | <b>External memory data bus bit 2</b> : 16-bit data bus; used to connect to external RAM and program memory                                                                                                                                              |  |

| D1                    | 69  | I/O | <b>External memory data bus bit 1</b> : 16-bit data bus; used to connect to external RAM and program memory                                                                                                                                              |  |

| D0                    | 70  | I/O | <b>External memory data bus bit 0</b> : 16-bit data bus; used to connect to external RAM and program memory                                                                                                                                              |  |

| V <sub>SS</sub>       | 71  | _   | Ground: 0 V reference                                                                                                                                                                                                                                    |  |

|                       | I   |     |                                                                                                                                                                                                                                                          |  |

| SYMBOL             | PIN | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                         |  |

|--------------------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| V <sub>CC(R)</sub> | 72  | -   | <b>Backup core power supply</b> : 2.4 to 3.6 V only. Separate from the core supply to allow a low capacity battery to be used to maintain the Real-Time Clock (RTC) function. This should be powered from the main supply during normal operation and switched to battery backup when the main supply fails.                        |  |

| DMCS               | 73  | 0   | <b>External data memory select</b> : external RAM select pin, active LOW when the external data memory space is addressed. This output is driven from $V_{CC(R)}$ and $V_{CC(B)}$ supplies to ensure that the external RAM is not enabled during power-down.                                                                        |  |

| PWRFAIL            | 74  | I   | <b>Power fail indicator</b> : a LOW on this pin forces the embedded microcontroller into reset. Reset will not be de-asserted until a set time after both PWRDN and PWRFAIL go HIGH. For correct start-up, this pin should be LOW on power-up.                                                                                      |  |

| XTAL4              | 75  | 0   | Crystal 4: output from the RTC oscillator amplifier; this pin is only 3 V tolerant                                                                                                                                                                                                                                                  |  |

| XTAL3              | 76  | I   | <b>Crystal 3</b> : input to inverting amplifier used in the RTC oscillator circuits (32.768 kHz); this pin is only 3 V tolerant                                                                                                                                                                                                     |  |

| PWRB               | 77  | 0   | <b>Backup supply select</b> : this output is intended to drive an external FET used to switch the battery backup supply(s). It is active LOW and is controlled directly by the PWRFAIL.                                                                                                                                             |  |

| PWRM               | 78  | 0   | <b>Main supply select</b> : this output is intended to drive an external FET used to switch the main supply(s). It is active LOW and is controlled directly by PWRFAIL.                                                                                                                                                             |  |

| V <sub>SS</sub>    | 79  | _   | Ground: 0 V reference                                                                                                                                                                                                                                                                                                               |  |

| V <sub>CC(B)</sub> | 80  | -   | <b>Backup I/O power supply</b> : 2.4 to 5.5 V only. Supply for the RAM select, power fail and power switching I/O pads only allowing these functions to be powered when the main power supply fails. This should be powered from the main supply during normal operation and switched to battery backup when the main supply fails. |  |

| TXD1               | 81  | 0   | <b>Transmitter output 1</b> : transmit channel for serial port 1 (UART1) of the embedded processor                                                                                                                                                                                                                                  |  |

| RXD1               | 82  | I   | <b>Receiver input 1</b> : receive channel for serial port 1 (UART1) of the embedded processor. It is intended that this serial port is dedicated to differential GPS information (dependent on firmware).                                                                                                                           |  |

| TXD0               | 83  | 0   | <b>Transmitter output 0</b> : transmit channel for serial port 0 (UART0) of the embedded processor.                                                                                                                                                                                                                                 |  |

| RXD0               | 84  | I   | <b>Receiver input 0</b> : receive channel for serial port 0 (UART0) of the embedded processor. It is intended that this serial port is dedicated to the NMEA data stream (dependent on firmware).                                                                                                                                   |  |

| V <sub>SS</sub>    | 85  | _   | Ground: 0 V reference                                                                                                                                                                                                                                                                                                               |  |

| V <sub>CC(P)</sub> | 86  | -   | <b>Main I/O power supply</b> : 2.7 to 5.5 V operating range; main supply for the periphery in normal operation                                                                                                                                                                                                                      |  |

| GPIO4              | 87  | I/O | <b>GPIO bit 4</b> : standard general purpose I/O mapped into the segment 15 of the address space. The top 4 bits can be used as the XA external timer control access pins (T0, T1, T2 and T2EX).                                                                                                                                    |  |

| GPIO3              | 88  | I/O | <b>GPIO bit 3</b> : standard general purpose I/O mapped into the segment 15 of the address space. The top 4 bits can be used as the XA external timer control access pins (T0, T1, T2 and T2EX).                                                                                                                                    |  |

| RFDAT              | 89  | 0   | RFIC set-up data: serial data output used to set up the UAA1570HL front-end IC.                                                                                                                                                                                                                                                     |  |

| RFCLK              | 90  | 0   | <b>RFIC set-up data</b> : clock output for the serial data output used to set up the UAA1570HL front-end IC. The state of the RFDAT and RFLE lines is latched into the front-end IC on the rising edge.                                                                                                                             |  |

| SYMBOL | PIN | I/O | DESCRIPTION                                                                                                                                                                                      |  |

|--------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RFLE   | 91  | 0   | <b>RFIC setup latch</b> : output used to latch the RFIC set-up into the active UAA1570HL control registers                                                                                       |  |

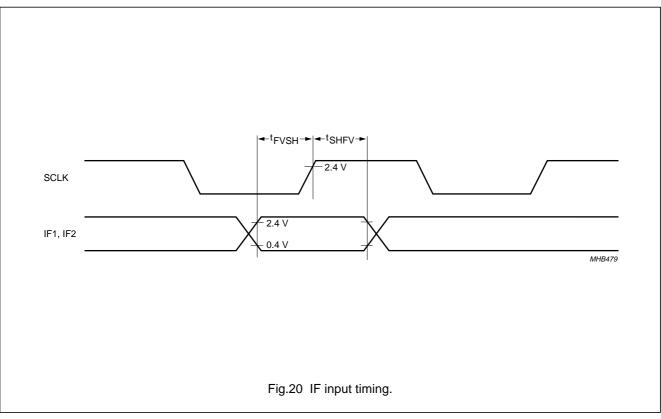

| IF2    | 92  | 1   | <b>MSB IF input</b> : MSB of the 2-bit GPS digital IF signal input. Clocked in on the rising edge of SCLK. If only a 1-bit IF input is available this input should be held HIGH.                 |  |

| IF1    | 93  | 1   | <b>LSB IF input</b> : LSB of the 2-bit GPS digital IF signal input. Clocked in on the rising edge of SCLK.                                                                                       |  |

| GPIO2  | 94  | I/O | <b>GPIO bit 2</b> : standard general purpose I/O mapped into the segment 15 of the address space. The top 4 bits can be used as the XA external timer control access pins (T0, T1, T2 and T2EX). |  |

| GPIO1  | 95  | I/O | <b>GPIO bit 1</b> : standard general purpose I/O mapped into the segment 15 of the address pace. The top 4 bits can be used as the XA external timer control access pins T0, T1, T2 and T2EX).   |  |

| GPIO0  | 96  | I/O | <b>GPIO bit 0</b> : standard general purpose I/O mapped into the segment 15 of the address space. The top 4 bits can be used as the XA external timer control access pins (T0, T1, T2 and T2EX). |  |

| n.c.   | 97  | 0   | Not connected: do not connect                                                                                                                                                                    |  |

| RCLK   | 98  | I   | <b>Reference clock</b> : input from the TXCO reference. Not used internally. This is divided under firmware control to produce the sample clock, SCLK, used to gate the IF inputs.               |  |

| TEST1  | 99  | 1   | Test pin: connect to pin 100                                                                                                                                                                     |  |

| TEST2  | 100 | 0   | Test pin: connect to pin 99                                                                                                                                                                      |  |

#### Global Positioning System (GPS) SAA1575HL baseband processor 91 RFLE 90 RFCLK 89 RFDAT 88 GPI03 87 GPI04 86 VCC(P) 85 VSS 84 RXD0 83 TXD0 82 RXD1 81 TXD1 80 VCC(B) 79 VSS 78 PWRM 99 TEST1 98 RCLK 97 n.c. 96 GPI00 95 GPI01 94 GPI02 93 JF1 92 JF2 TEST2 PWRB XTAL3 8 1 20 SCLK 1 75 XTAL4 74 PWRFAIL T1S 2 73 DMCS TP3 3 TP4 4 72 V<sub>CC(R)</sub> GPIO7 5 71 V<sub>SS</sub> GPIO6 6 70 D0 GPIO5 7 69 D1 68 D2 n.c. 8 n.c. 9 67 D3 A19 10 66 V<sub>CC(core)</sub> 65 V<sub>SS</sub> A18 11 V<sub>CC(core)</sub> 12 64 D4 SAA1575HL V<sub>SS</sub> [13 63 D5 XTAL1 14 62 D6 XTAL2 15 61 V<sub>CC(P)</sub> V<sub>CC(P)</sub> 16 60 V<sub>SS</sub> VSS 17 59 D7 A17 18 58 D8 A16 19 57 D9 A15 20 56 D10 A14 21 55 D11 A13 22 54 D12 A12 23 53 D13 A11 24 52 PWRDN 51 V<sub>CC(P)</sub> VCC(P) 25 RSTIME 45 TP1 44 WRH 45 WRL 46 RD 47 D15 48 D14 49 VSS 50 Vcc(P) 3 Vss 38 A2 39 A1 40 26 27 28 29 34 42 32 R 35 36 4 31 VCC(core) [ VSS [ A7 [ A7 [ A6 [ A5 ] A5 [ A3 ] A3 [] PMCS TP2 A9 A8 /SS A10 MHB461 Fig.2 Pin configuration.

### SAA1575HL

#### 7 FUNCTIONAL DESCRIPTION

#### 7.1 Overview

The function of the SAA1575HL is to accept any IF data (1 or 2-bit) from a front-end RF IC (such as the UAA1570HL) and provide a serial NMEA compatible GPS position and time output. The IF input is sampled synchronously with the front-end reference clock, SCLK. Data is decoded from the IF input stream by one of eight parallel correlators which allow up to eight satellites to be tracked at one time. The acquisition, allocation and tracking of the satellites is performed under firmware control by the on-chip processor.

In addition to the SAA1575HL and an appropriate front-end IC (such as the UAA1570HL), the only external components required to complete a functional GPS receiver are some RAM, the firmware ROM and some discrete devices to control the power supplies. The need for external glue logic is eliminated by various chip-select functions implemented on the SAA1575HL. The SAA1575HL also contains an optional independent Real-Time Clock (RTC) which requires a separate 32.768 kHz crystal. This can be set to GPS time by the processor and enables fast re-acquisition (a warm start) of satellites after power has been switched off. A separate supply pin is provided to allow the RTC to be powered while the rest of the IC is turned off.

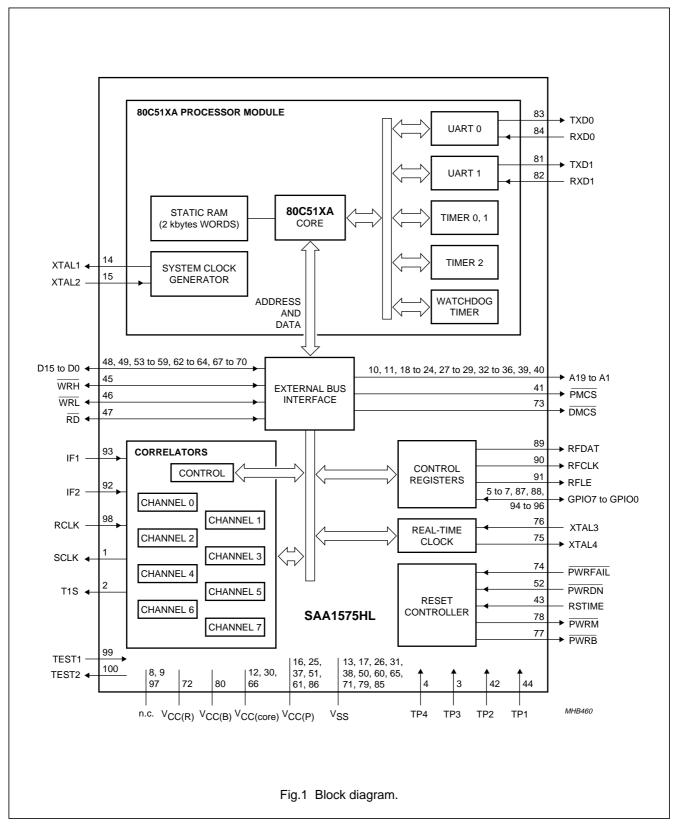

The block diagram of the SAA1575HL is shown in Fig.1. The IC consists of a processor core, its associated peripherals, some internal memory and a series of GPS correlators.

The processor core is based on an embedded Philips 80C51XA (known as the XA). The XA peripherals (UARTs, timers, watchdog and general purpose I/Os) are termed special function registers and are memory mapped in parallel with an area of the data memory. They are connected to the core by dedicated data and address buses. The internal data memory is also connected to the core by a dedicated bus.

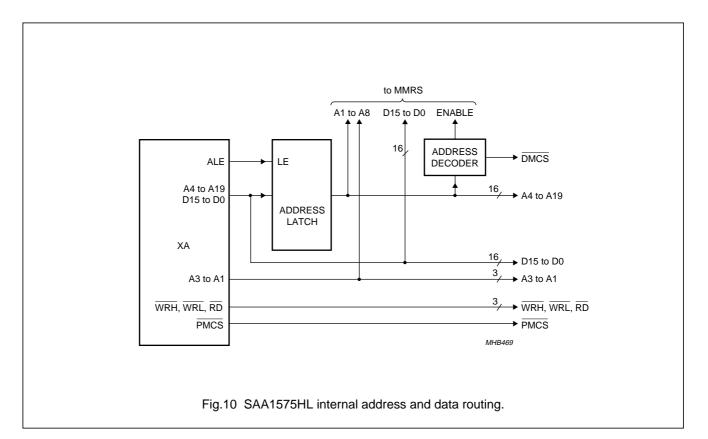

The rest of the IC (the correlators, RTC and system control) is mapped into the external data memory space. The multiplexed data and address buses provided by the XA core are separated by an on-chip latch to provide the distinct 16-bit data bus and 19-bit address bus. These are made available externally for connection to external memory via the external bus interface.

The correlators, RTC and system control blocks are memory mapped into the highest page of the 16 pages in the XA data structure. Both the RTC and the correlators are asynchronous to the system clock, with synchronization being achieved by firmware and interrupts.

#### 7.2 The 80C51XA processor

The microcontroller core in the SAA1575HL is a Philips design called the XA (eXtended Architecture) which is an extended 80C51-like 16-bit microcontroller. This is largely compatible with the 8051 but with various improvements. The main features of the XA compared to the 8051 can be summarized as follows:

- 16-bit versus 8-bit data processing

- 20-bit versus 16-bit address bus

- 3 clock instruction cycle versus 12 clock instruction cycle

- 10 Mips versus 1 Mips

- 20 CPU registers versus 1 accumulator

- All 20 CPU registers in the XA can be used as the accumulator register in the 8051

- + 16  $\times$  16 multiplication in 12 clocks,  $^{32}\!/_{16}$  division in 22 clocks

- New type of instructions such as normalization, sign extension and trap

- Multi-tasking support versus no multi-tasking support.

#### 7.3 The GPS correlators

The correlator block forms the GPS specific hardware for correlating with the direct sequence spread spectrum GPS signals. The 8 identical correlators share the 2-bit IF input and the sample clock of the Analog-to-Digital Converter (ADC) of the front-end. The input signal is the 50 bits/s GPS data spread by the 1.023 Mbits/s PN code and modulated by the residual carrier. The residual carrier frequency is composed of the Doppler frequency and the receiver local oscillator frequency offset.

To recover the GPS data and find the accurate timing of the received data for GPS navigation from the low-level (as low as –130 dBm) GPS signal, the residual carrier frequency and phase have to be found by a Phase-Locked Loop (PLL) with minimum tracking phase error. The starting position of the PN code in the received signal is found by correlation within a Delay-Locked Loop (DLL). The channel correlator includes a local numerically controlled oscillator and a programmable local PN code generator with the phase rotation and correlation circuit.

#### 7.4 Memory organization

The memory space in the SAA1575HL is configured in a Harvard architecture which means that the code and data memory are organized in separate address spaces. This section describes the SAA1575HL memory requirements.

#### 7.4.1 DATA MEMORY SPACE

The SAA1575HL contains 2 kbytes words of internal data memory. For correct firmware operation, a further 32 kbytes words of external data memory is needed with a maximum access time of 100 ns.

The specifications of this external memory are firmware dependent. The figures given in this document are for the standard Philips firmware. With other revisions of firmware the timings could differ by integer numbers of XTAL1 clock cycles.

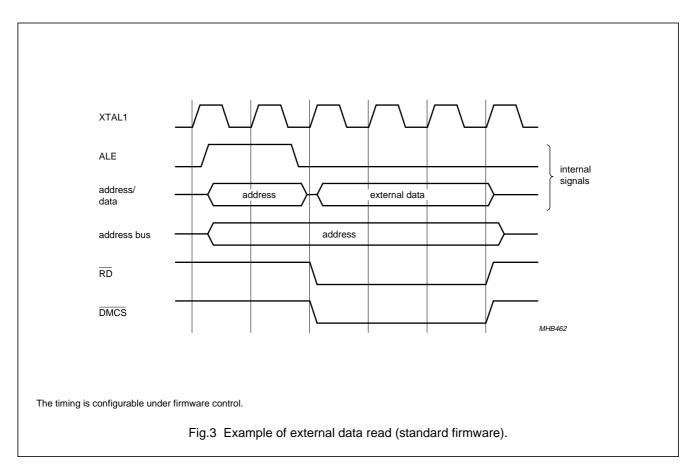

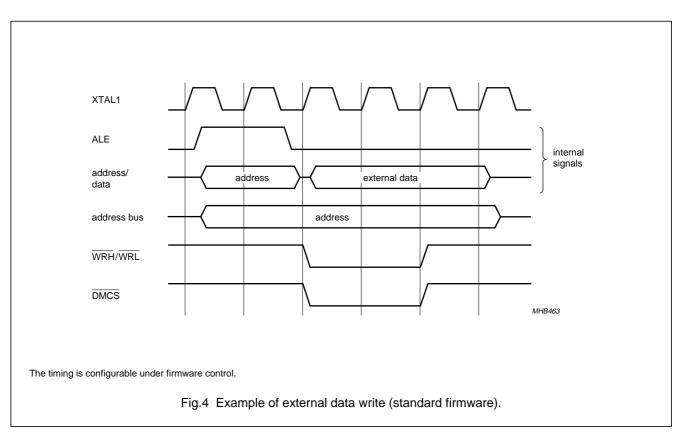

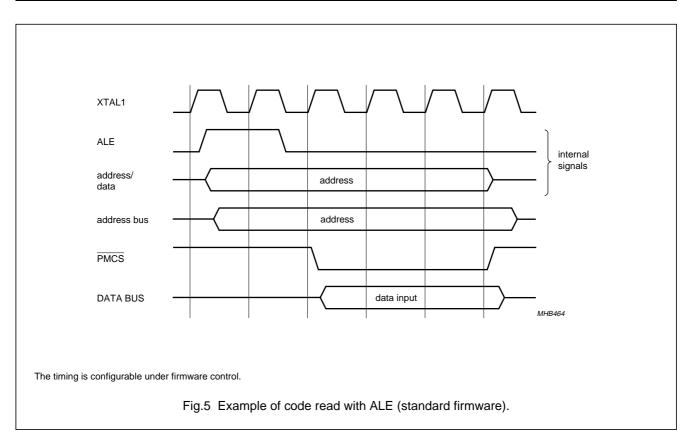

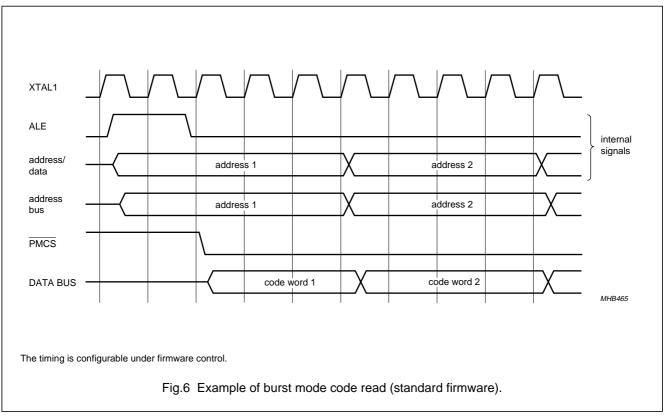

In the SAA1575HL, all of the data read and write cycles are preceded by an internal Arithmetic and Logic Elements (ALEs) cycle (as in any standard 80C51 system). The multiplexed address/data bus and the ALE signal are not available externally. However, for clarity, these are illustrated in Figs 3 to 6.

### SAA1575HL

#### 7.4.2 CODE MEMORY SPACE

The SAA1575HL has no internal code memory. The GPS solution firmware resides in external memory. With the standard Philips firmware, a ROM with a maximum access time of 100 ns is required.

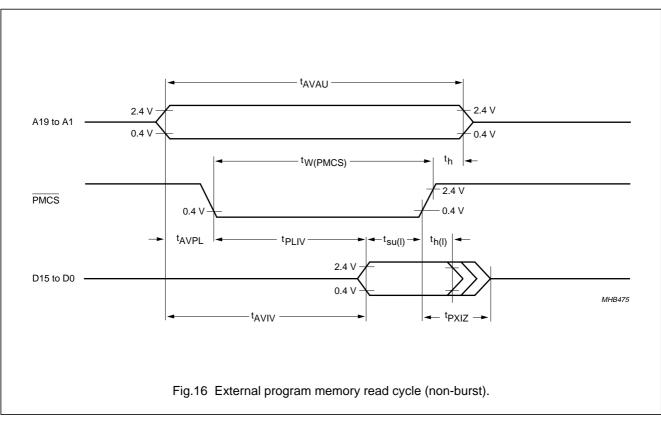

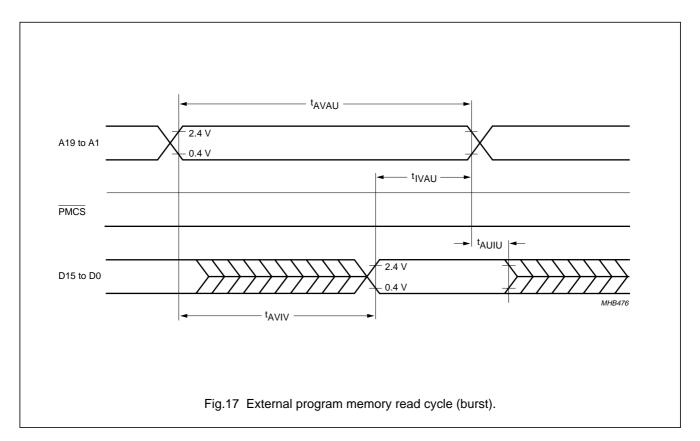

The classic operation of a multiplexed address/data bus involves an address being set-up for every bus cycle. The internal ALE signal is used to latch the address prior to the cycle on which the data is set-up. An example of the resulting timing is illustrated in Fig.5.

The SAA1575HL does not require an internal ALE cycle for each code fetch. The lowest 3 address lines are not multiplexed with the data lines and so these can be used to incrementally read code locations. The XA core can therefore issue up to 8 word reads through sequential code memory for each ALE cycle. This is termed a burst code read. An example of the resulting timing is illustrated in Fig.6.

Any type of branch or jump in the program may require a code fetch in a non-sequential manner and a new ALE cycle will be needed. This may occur at any stage in a code read. Thus the length of the read strobe in a burst read is not necessarily an integer multiple of the individual code read length.

#### 7.5 CPU peripheral features

The SAA1575HL contains the hardware for 3 timers, 2 UARTs, a watchdog timer, a 3-bit RF IC programming link and an 8-bit general purpose I/O port.

#### 7.5.1 TIMERS/COUNTERS

The SAA1575HL has 2 standard 16-bit timer/counters and a third 16-bit up/down timer/counter. These timer/event counters can perform the following functions:

- · Measure time intervals and pulse duration

- · Count external interrupts

- Generate interrupt requests

- Generate Pulse Width Modulation (PWM) or timed output waveforms.

The timers are used by the standard Philips firmware to generate the baud rates for the UART serial ports. The additional features are not used in the standard Philips firmware but are available for use in custom firmware revisions.

All of the timers are configured in the 16-bit auto-reload mode of operation. Timer 1 is used to generate the baud rate for UART0 and Timer 2 is used to generate the baud rate for UART1. In the standard Philips firmware, Timer 0 is not used.

#### 7.5.2 WATCHDOG TIMER

The watchdog timer protects the system from incorrect code execution by causing a processor reset if the watchdog timer underflows as a result of a failure of the firmware to feed the timer prior to it reaching its terminal count.

In the standard Philips firmware, the watchdog is enabled with a time-out period of 130 ms (at a clock frequency of 30 MHz).

#### 7.5.3 UARTs

The SAA1575HL contains 2 UART ports, compatible with the enhanced UART modes 1 to 3 on the 8xC51FB (mode 0 operations not supported). With the exception of the removal of the mode 0 operation, the UARTs in the SAA1575HL are identical to those in the XA-G3 product. Each UART rate is determined by either a fixed division of the oscillator (in UART mode 2) or by one of the timer overflow rates (in UART modes 1 and 3). With the standard Philips firmware, both UARTs are configured to be in Mode 1: variable rate 8-bit operation. Ten bits are transmitted (via TXDn) or received (via RXDn): a START bit, 8 data bits (LSB first), and a STOP bit.

In general, the UART clocks (which are 16 times the baud rate) are determined by the Timer 1 or Timer 2 overflow rate. With the standard Philips firmware, Timer 1 is used to generate the baud rate for UART0 and Timer 2 is used to generate the baud rate for UART1. The baud rate is set to be 4800 bits/s for both UARTs.

#### 7.5.4 RF IC PROGRAMMING PORT

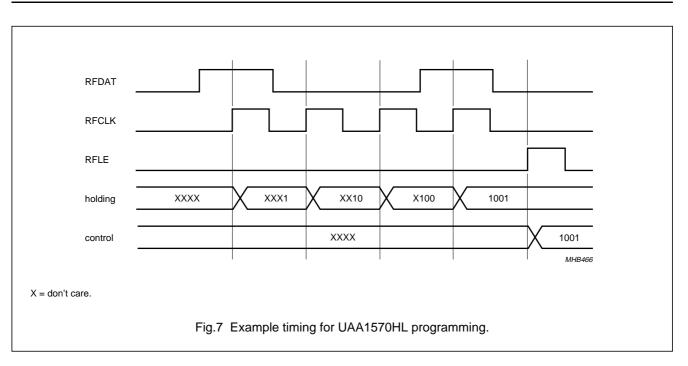

The SAA1575HL is capable of programming the UAA1570HL via a standard 3-wire serial link. This consists of a clock line (SCLK), data line (D15 to D0) and a latch enable (RFLE). Data is clocked into a holding register in the UAA1570HL serially on each rising edge of the output RFCLK. Once the complete serial packet has been clocked into the RF IC, the latch enable output, RFLE, is asserted which copies the new word from the holding register in the RF IC into the control registers.

Proper timing of the clock, data and latch outputs is ensured by firmware. An example sequence is illustrated in Fig.7. The signals shown would result in the value 1001 being loaded into the last 4 bits of the RF IC serial register. Each loading operation of the RF IC reloads the complete RF control register.

With the standard Philips firmware, a 20-bit long word 0X5E320 is transmitted in this manner on start-up or re-initialization. This gives full compatibility with the Philips UAA1570HL front-end IC. See the *"UAA1570HL"* for more details about the configuration options of the front-end IC.

### SAA1575HL

#### 7.5.5 GENERAL PURPOSE I/O

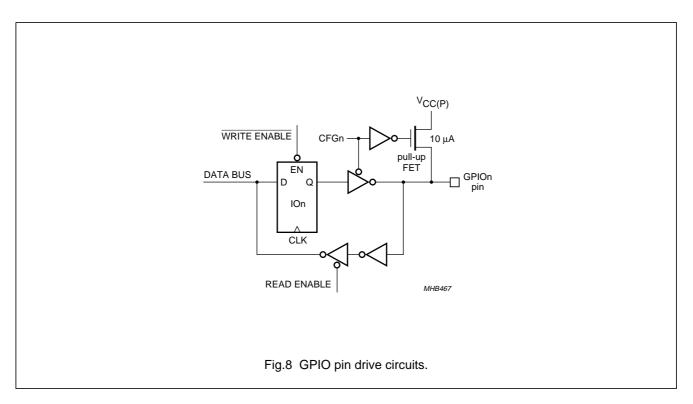

The SAA1575HL possesses an 8-bit general purpose I/O register and 8 associated I/Os (see Fig.8). With the standard Philips firmware, all 8 of these pins are configured as outputs.

With the standard Philips firmware, only pin GPIO0 is used. This is switched on at the end of the firmware initialization sequence and remains on subsequently.

#### 7.6 The real-time clock

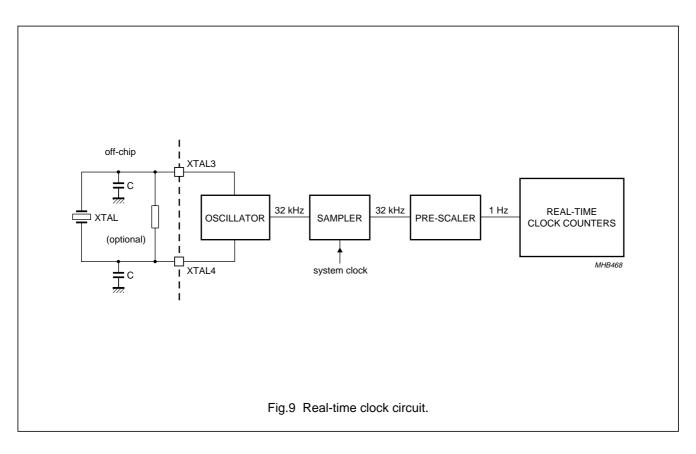

The Real-Time Clock (RTC) is a functional unit used to generate time information. Its purpose is to supply approximate GPS time to the system firmware for the initial acquisition of satellites (a warm start). The power supply for the RTC is separate from the rest of the IC, allowing a low capacity battery to be used to maintain the low power RTC function.

The timebase for the RTC should be provided by a dedicated 32.768 kHz crystal which can be omitted if the RTC is not required. This is divided down by a fixed divider to provide the 1 Hz timebase used for the rest of the RTC block. A digital sampling circuit is also included to prevent digital noise due to the on-chip processor causing incorrect timekeeping.

### SAA1575HL

Product specification

The SAA1575HL uses a digital under-sampling system to ensure that ground bounce does not cause RTC timekeeping errors. This places a restriction on the ratio of XTAL1 and XTAL3 frequencies for which the RTC will operate correctly. This has been optimistic for the case  $f_{XTAL1} = 30$  MHz,  $f_{XTAL3} = 32$  kHz and, assuming that the RTC crystal frequency will always be 32 kHz, will operate correctly for the entire specified range of system frequencies.

#### 7.7 The external bus

The off-chip memories and the on-chip registers are on the same address and data bus. The routing of the data and address signals between the on-chip registers and the off-chip memories is controlled by a block known as the external bus interface. In addition, certain chip enable signals are decoded within the block to reduce the amount of external glue logic required in the complete system.

The address latch, normally required on 80C51 systems, is implemented within the SAA1575HL. Therefore, no ALE signal is seen outside the IC and address and data lines are brought out on separate pins.

However, since internally there is still the need to latch the address from a common address/data bus, signals on the data bus will be seen to change during the address set-up cycles.

The lower 3 external address lines are driven directly by the XA core and are not latched. This allows 'burst' code reads to be performed in which adjacent code locations are accessed without the need for an address latch cycle.

Signals similar to those used by a standard 80C51 or XA system are used to control the external bus activity.

#### 7.7.1 PROGRAM MEMORY CHIP SELECT

This signal (PMCS) is an active LOW strobe used to enable the output of the external code memory. It remains HIGH when a read code is not in progress.

#### 7.7.2 DATA MEMORY CHIP SELECT

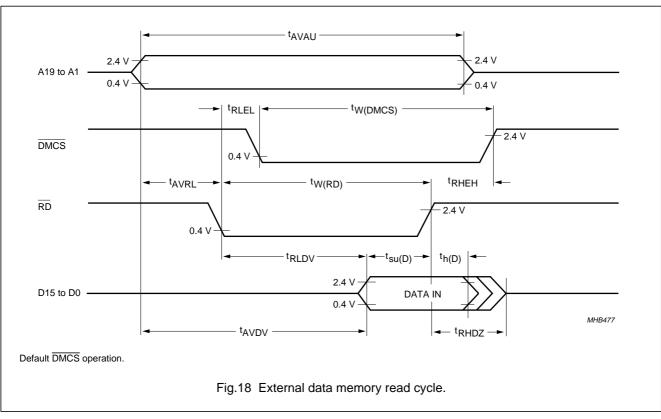

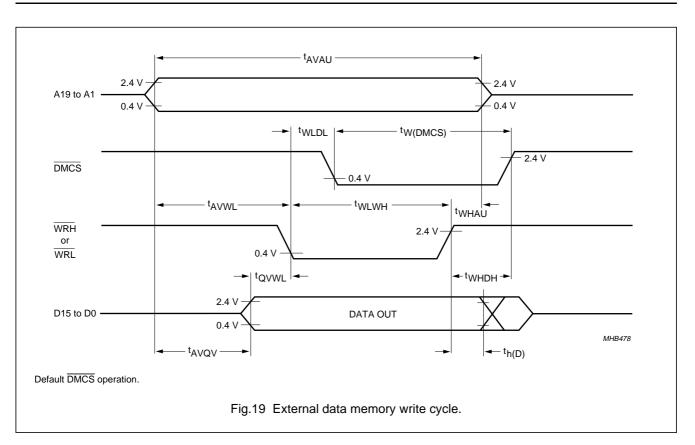

This signal (DMCS) is an active LOW strobe used to enable the external data memory. The SAA1575HL hardware supports two distinct modes of operation of this signal (selected in firmware) designed for optimum power or optimum speed. The standard Philips firmware is configured for optimum power.

DMCS is taken LOW during an external data read or write operation to segments 0 to 14 of the memory map. To prevent the corruption of external data memory, the DMCS pin is driven on the backup supply voltage and will be held HIGH once the PWRFAIL signal has been asserted LOW.

With the standard Philips firmware, the DMCS signal is gated by the external access read and write strobes. This should significantly reduce the power consumption of the external RAM but may require the use of a slightly faster external memory (depending on clock speed and details of the external memory used).

#### 7.7.3 READ STROBE

This signal  $(\overline{RD})$  is an active LOW strobe used to indicate that the XA is expecting data from the external bus.

#### 7.7.4 WRITE LOW BYTE STROBE

This signal (WRL) is an active LOW strobe used to indicate that the XA is performing an external write. This strobe only applies to the lower data byte of the 16-bit data word, allowing byte writes to be performed from the 16-bit data. This strobe will also be taken LOW for word write operations.

#### 7.7.5 WRITE HIGH BYTE STROBE

This signal ( $\overline{\text{WRH}}$ ) is an active LOW strobe used to indicate that the XA is performing an external write. This strobe only applies to the higher data byte of the 16-bit data word, allowing byte writes to be performed from the 16-bit data. This strobe will also be taken LOW for word write operations.

#### 7.8 Backup supplies and reset

The SAA1575HL is designed to operate correctly in situations when the main power supply fails. In addition to the main core and peripheral power supplies, separate pins are provided for backup core and peripheral supplies which enable critical (and low-power) functions to be maintained during the loss of main power. There is also an on-chip reset timer which will aid the design of a full power-down strategy.

#### 7.8.1 SUPPLY DOMAINS

To allow for the use of inexpensive 5 V external components, the periphery of the SAA1575HL can be powered with a higher voltage than the core. Therefore there is a distinction between the core and peripheral power supplies. In addition, there is the need to maintain certain functionality on a low-power supply in the event of main power failure. Therefore there are 2 additional supplies required for so-called backup operation. Thus there are four distinct power supply domains, two for the core supplies and two for the peripheral supplies.

| Table 1 | Supply | domains |

|---------|--------|---------|

|---------|--------|---------|

| SUPPLY                | DESCRIPTION                                    | PURPOSE                                                                                                                                                 |

|-----------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC(core)</sub> | main core<br>supply (3 V)                      | provides power for all core<br>circuits, excluding those<br>mentioned below                                                                             |

| V <sub>CC(P)</sub>    | main peripheral<br>supply<br>(3 to 5 V)        | provides power for all pins,<br>excluding those mentioned<br>below                                                                                      |

| V <sub>CC(R)</sub>    | RTC core<br>supply<br>(2.4 to 3 V)             | powers the real-time clock,<br>the 32 kHz oscillator and<br>the 32 kHz de-bounce<br>circuit; it also produces the<br>signals for DMCS, PWRM<br>and PWRB |

| V <sub>CC(B)</sub>    | backup<br>peripheral<br>supply<br>(2.4 to 5 V) | provides power for the<br>following pins: DMCS,<br>PWRM, PWRB and<br>PWRFAIL                                                                            |

In normal operation, the backup core and pad supplies should be provided from the main power supply rather than a low-capacity battery since the power drawn on the backup supplies while the processor is operating may be significant. Two output pins, PWRM and PWRB are provided to control this switching.

The power consumption of the SAA1575HL in the power-down mode is minimal since no outputs are changing. The only active circuit in power-down is the real-time clock.

Isolation between the power domains is controlled by the PWRFAIL input pin. This must be driven LOW in a power-failure situation to ensure that the backup domains are isolated from the main supply domains. If this is not done, it is possible that the registers contained in the backup supply domain will be corrupted as the main supply is cycled. It is also possible that under these circumstances a high backup supply current will be drawn (depending on details of the external supply circuitry).

#### 7.8.2 POWER-DOWN DESIGN STRATEGY

In power-down operation the main supplies are assumed to have failed. The backup core and pad supplies should be switched to backup power. The detection of the power failure and the power supply switching is the responsibility of the user. However, the SAA1575HL does provide several functions to aid this task. The power-down and power-fail operations of the SAA1575HL are controlled by two inputs, PWRDN and PWRFAIL, which are assumed to be connected to external voltage comparators. The use of external comparators allows the voltage thresholds to be set by the system designer. It also allows a certain amount of flexibility as to which supplies are monitored for power failure.

#### 7.8.2.1 Power-down control signals

The power-down control signal pins (see Table 2) are either inputs or outputs associated with the SAA1575HL power control. The descriptions are for the intended use of the control signals in a normal application.

For a correct reset to occur, it is important that **PWRFAIL** should be held LOW as long as minimum voltages have been established on all four of the power supply domains. If this is not done various serious consequences may occur, including main oscillator failure, a high supply current state, a processor crash or RTC register corruption.

| SIGNAL  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PWRDN   | <b>Power-down indicator</b> : this should be driven LOW by an external comparator to indicate impending power failure. Internally it sends an interrupt to the processor used to initiate a power-fail routine. At the end of this routine the standard firmware forces the processor into reset. This also inhibits the external RAM chip select. Reset is only de-asserted a set time after both PWRDN and PWRFAIL go HIGH, controlled by the RSTIME input.        |

| PWRFAIL | <b>Power fail indicator</b> : this should be driven LOW by an external comparator to indicate immediate power failure. Internally it forces immediate reset of the processor, isolation of the RTC and inhibition of the external RAM chip select. It also controls the power switch outputs PWRB and PWRM. Reset is only de-asserted a set time after both go HIGH, controlled by the RSTIME input.                                                                 |

| RSTIME  | <b>Reset timer control</b> : this sets the time delay between de-assertion of both $\overline{PWRDN}$ and $\overline{PWRFAIL}$ and the de-assertion of the processor reset. If HIGH, the delay is approximately 10 ms. If LOW the delay is approximately 10 $\mu$ s.                                                                                                                                                                                                 |

| DMCS    | <b>External RAM chip select</b> : this is driven via the backup supplied core and pads. In power-down this is isolated from the rest of the IC and the output held HIGH to prevent corruption of the external RAM.                                                                                                                                                                                                                                                   |

| PWRM    | <b>Main power supply control</b> : in normal operation this is held LOW. This can be used to switch the main supplies to all of the supply input pins. In normal operation the backup pad supply pin should be driven by the main supply and the backup core supply pins should be driven by the main core supply. When the IC goes into power-down mode this output goes HIGH. In power-down the backup supply pins should be driven by their appropriate supplies. |

| PWRB    | Backup power supply control: this is the inverse of PWRM                                                                                                                                                                                                                                                                                                                                                                                                             |

#### **Table 2**Power-down control signals

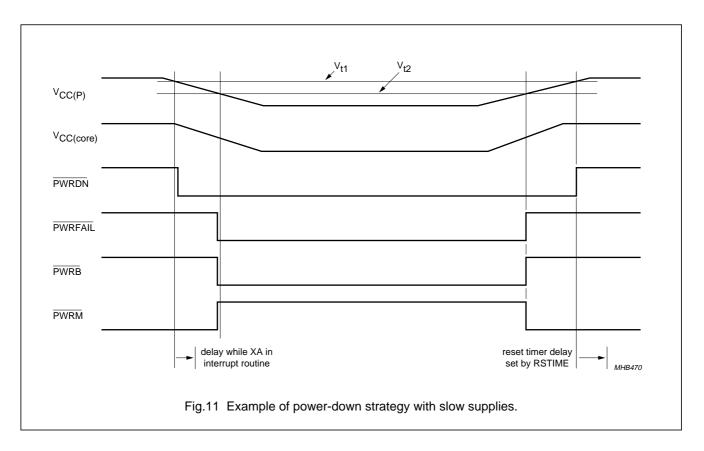

#### 7.8.2.2 Example of strategy for slow supplies

The ultimate use of the power control signals is up to the user. However, two possibilities are presented as design examples. The first example will operate correctly in circuits where the rise times of the power supplies is slow compared to any delay between the supplies to the peripheral and core power domains.

In this example, both the  $\overline{PWRDN}$  and  $\overline{PWRFAIL}$  logic inputs to the SAA1575HL are derived by comparing the  $V_{CC(P)}$  supply voltage against known references. In general, since it is a lower voltage, the  $V_{CC(core)}$  supply may hold and reach it's nominal voltage quicker than the  $V_{CC(P)}$  supply.

As  $V_{CC(P)}$  falls, the first threshold is reached and  $\overline{PWRDN}$  is taken LOW. This triggers an interrupt in the firmware which is used to perform any required housekeeping. It is assumed that there is time for this to be completed before complete supply failure.

#### Product specification

### SAA1575HL

At the end of the interrupt routine, the firmware places the SAA1575HL into reset. As  $V_{CC(P)}$  continues to fall, the second threshold is reached and is taken LOW. This toggles the power controls, both PWRM and PWRB, and will force a reset if it has not already occurred.

On power-up, the power controls both PWRM and PWRB will be switched once the second threshold voltage is reached. As the supply voltage rises further, the first voltage threshold will be reached at which time both PWRDN and PWRFAIL will be HIGH. This starts the reset counter and the SAA1575HL will remain in reset until a set time after this, depending on the state of the input pin RSTIME.

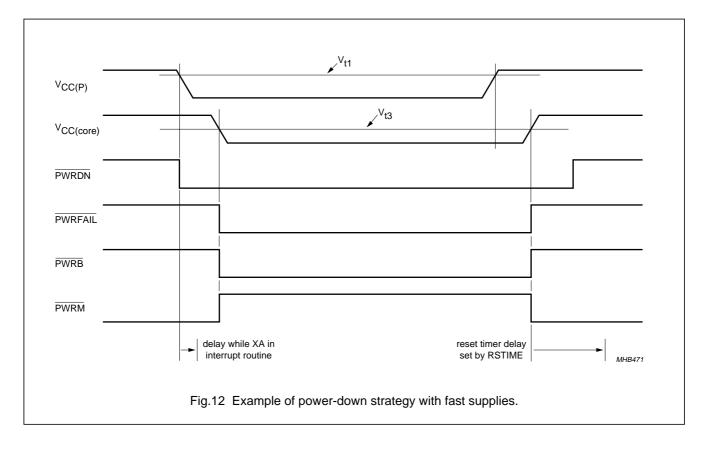

#### 7.8.2.3 Example of strategy for fast supplies

The second example will operate correctly in circuits where the delay between the supplies to the peripheral and core power domains is significant compared to the rise times of the power supplies. This may occur in cases where the core supply is a regulated (delayed) version of the peripheral supply. If the previous strategy were used in this situation, it would be possible for the SAA1575HL to miss the PWRFAIL LOW state at power-up, resulting in the IC not being given a correct reset.

In this example, the  $\overline{\text{PWRDN}}$  logic input is derived as before by comparing the  $V_{CC(P)}$  supply voltage against a known reference voltage. But in this instance the  $\overline{\text{PWRFAIL}}$  logic input is derived by comparing the  $V_{CC(core)}$  core supply against a threshold voltage.

As  $V_{CC(P)}$  falls, the first threshold level is reached and  $\overline{PWRDN}$  is taken LOW. This triggers an interrupt in the firmware which is used to perform any required housekeeping. At the end of the interrupt routine, the firmware places the SAA1575HL into reset.

#### Product specification

### SAA1575HL

However, if the fall times on the supplies is fast, it is likely that the PWRFAIL input will go LOW before the interrupt routine has been completed. This would force the SAA1575HL into immediate reset. At this time both PWRM and PWRB toggle to switch backup supply sources.

On power-up, the V<sub>CC(P)</sub> supply rises quickly. However, since this only controls an interrupt flag and the SAA1575HL is still held in reset by PWRFAIL, this has no effect. Only once the V<sub>CC(core)</sub> supply rises will PWRFAIL be de-asserted. This can only occur once the V<sub>CC(core)</sub> voltage has reached the set threshold, and so there is no risk of the IC 'missing' the reset pulse. The SAA1575HL will come out of reset a set time after this, depending on the state of the input pin RSTIME.

#### 7.8.3 SYSTEM RESET CONTROL

The SAA1575HL contains an internal timer and control logic to perform various system reset tasks. Control of this logic is by three external pins, PWRDN, PWRFAIL, and RSTIME. This allows the system designer to set the voltage thresholds at which the system goes into and comes out of reset.

#### 7.8.3.1 The reset timer

The heart of the reset system is a 20-bit counter with asynchronous reset, clocked from the XTAL1 system clock. The reset counter is asynchronously reset if the PWRFAIL pin is LOW. Once reset, the counter will only be enabled once both PWRFAIL and PWRDN go HIGH. This prevents the SAA1575HL from leaving the reset state until both power detect inputs have flagged the power system as healthy.

The internal reset signal is generated by decoding the reset counter. The decode value, and hence the time delay, is controlled by the reset time control pin, RSTIME.

#### Table 3 Reset time control

| RSTIME<br>INPUT | NUMBER OF<br>CYCLES BEFORE<br>RESET<br>DE-ASSERTED | TIME DELAY<br>(f <sub>XTAL1</sub> = 30 MHz) |

|-----------------|----------------------------------------------------|---------------------------------------------|

| 1               | 294 912                                            | 9.8 ms                                      |

| 0               | 288                                                | 9.6 µs                                      |

The internal reset is de-asserted a given number of XTAL1 clock cycles after PWRFAIL and PWRDOWN go HIGH. It is suggested that for most applications RSTIME should be held HIGH, giving a reset time of approximately 10 ms. This would be needed to allow the on-chip oscillator to stabilize after power-up. The shorter reset time can be used for applications using an external XTAL1 clock signal which does not need a long stabilization period.

It is important that **PWRFAIL** should be LOW during power-up of the IC to give the correct reset.

#### 7.8.3.2 Overall reset operation

The assertion of the reset signal (by means already described) will cause the following to occur:

- Internal XA processor reset

- Internal registers reset

- Data bus pins set to be inputs

- Read and write strobes de-asserted

- · GPIO pins set to be inputs

- On-chip XTAL1 oscillator enabled.

#### 7.8.3.3 CPU reset operation

Assuming that the correct external PWRFAIL sequence is generated on power-up, the internal XA will receive the correct reset signal from the on-chip reset block. If the proper PWRFAIL is not performed, the operation of the on-chip reset block cannot be guaranteed and the XA may fail wholly or in part.

The embedded XA requires a minimum length of reset to complete the various tasks. This minimum length is guaranteed by the on-chip reset block. The only restriction on the length of the pulse is that is should be long enough to be asynchronously detected by the SAA1575HL (typically 10 ns).

The embedded CPU can also be reset by the watchdog timer (this may be disabled on some custom firmware revisions).

#### 7.8.4 POWER SAVING MODES

The SAA1575HL supports two power saving modes; Idle mode and sleep mode. Both modes are selected by firmware (or message over the serial link if included in the firmware). In addition, the input to any of the correlators can be inhibited individually (by firmware) which will reduce the power consumed by the block to only the clock tree dissipation.

#### 7.8.4.1 Sleep mode

The sleep mode is intended to overlay the function of the standard 80C51XA Idle mode. Sleep is initiated by a firmware or external serial link command. This initiates a firmware routine which performs the following:

- 1. Send serial command to power-down RF IC (UAA1570HL)

- 2. Inhibit RCLK, IF2 and IF1 inputs to SAA1575HL

- 3. Enter standard 80C51XA Idle state.

In sleep mode the RCLK and IF inputs are prevented from entering the IC. This capability is included to cover the situation in which the SAA1575HL is used with a front-end which does not respond to the power-down command in a similar way to the UAA1570HL. Sleep mode can be exited by any active hardware interrupt, for example a UART interrupt. The sleep mode has no effect on the operation of the RTC.

#### 7.8.4.2 Idle mode

The Idle mode is initiated by a firmware or external serial link command. This is a direct use of the standard 80C51XA Idle mode. The interrupt signals from the active peripherals such as UARTs, timers, host interface and external interrupts will cause the CPU to resume execution from the point at which it was halted. In the Idle mode, all of the output pins retain their logic states from their 'pre-idle' position. No other action is taken on entering Idle mode. In particular, the correlators will remain active since RCLK, IF1 and IF2 will not be prevented from entering the IC.

#### 7.9 Clock signals and oscillators

The SAA1575HL requires 3 clock signals for full operation:

- XTAL1: Processor (system) clock

- XTAL3: Real-time clock crystal frequency (optional)

- RCLK: GPS reference clock.

Two of these clocks, XTAL1 and XTAL3, can be generated by on-chip oscillator circuits. The third, RCLK, must be supplied from an external source; in most applications a temperature compensated oscillator module.

#### 7.9.1 SYSTEM CLOCK (XTAL1)

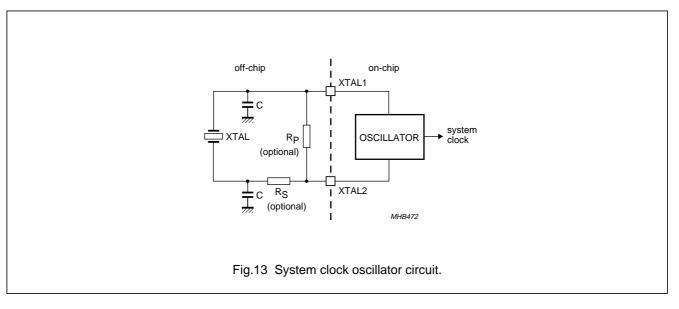

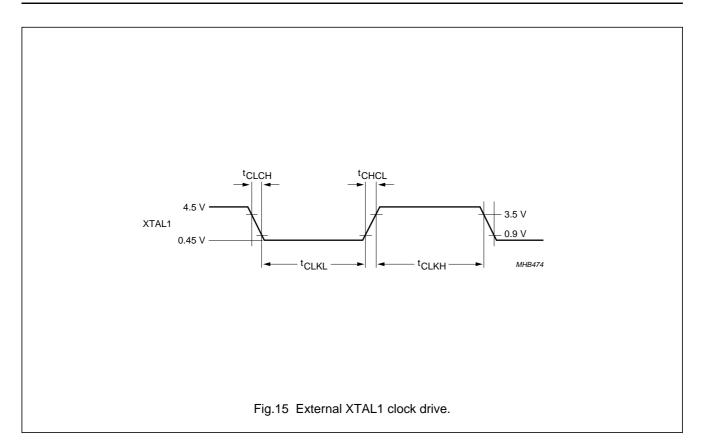

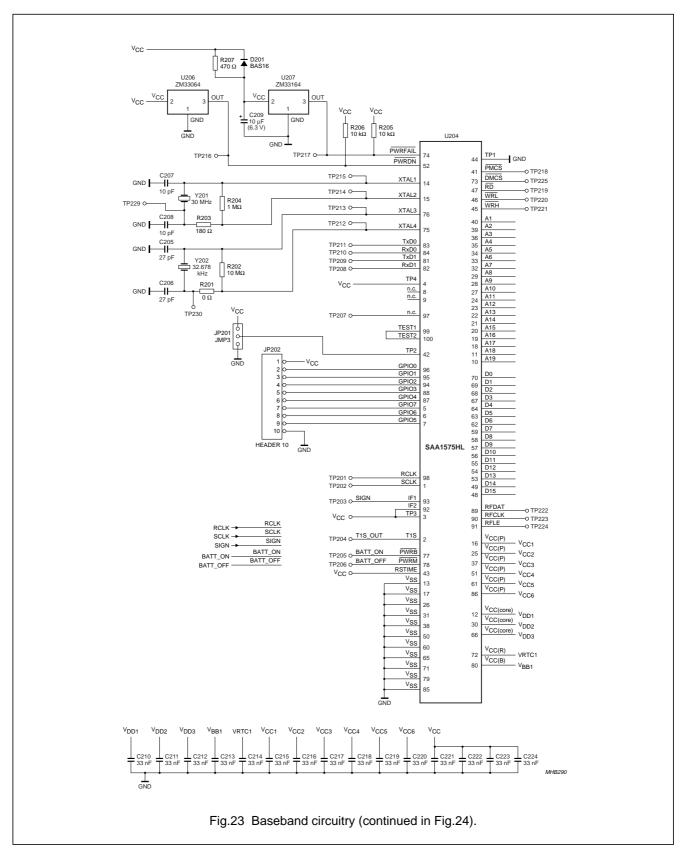

The SAA1575HL requires a system clock for the on-chip processor and related peripheral blocks. This can be provided from an external clock source via the XTAL1 input pin or by using the on-chip oscillator circuit with an external resonating element connected between the XTAL1 and XTAL2 pins. In most circumstances this would be an external crystal accompanied by two capacitors connected to ground, a series resistor (to optimize power consumption) and a shunt resistor to ensure start-up under all conditions.

Optimum values of C, R<sub>P</sub> and R<sub>S</sub> will depend on the crystal used. However, typical values would be C = 20 pF, R<sub>P</sub> = 1 M $\Omega$  and R<sub>S</sub> = 200  $\Omega$ . The hardware places a restriction on the range of frequencies for which correct operation will occur; 26 MHz < f<sub>XTAL1</sub> < 32 MHz.

However, the restriction on operating frequency imposed by the firmware is tighter than this. The standard Philips firmware has been written on the assumption of a 30 MHz system clock frequency.

#### Product specification

### SAA1575HL

#### 7.9.2 RTC CLOCK (XTAL3)

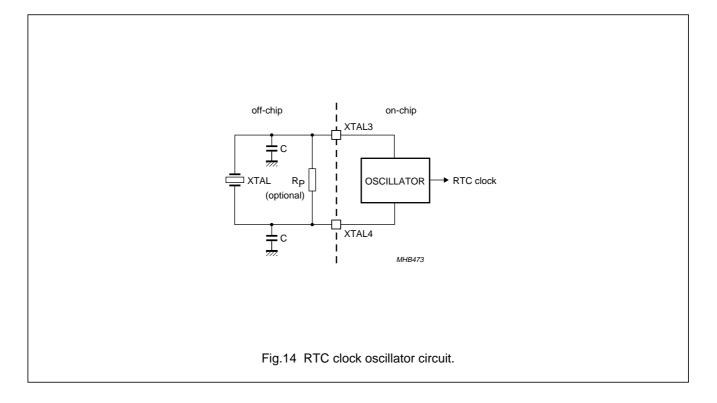

If the on-chip real-time clock is required (as with the standard Philips firmware), a low frequency clock signal is required to run the clock. The SAA1575HL is designed so that a standard 32.768 kHz watch crystal can be used for this purpose. Since this is much slower than the system clock, a much lower power is required to run just the real-time clock, allowing it to be powered from a low-capacity battery when the main power supply fails.

As with the system clock, there is an on-chip oscillator so that only a few passive external components are required. These would be an external crystal accompanied by two capacitors connected to ground, a series resistor (optional) and a shunt resistor to ensure start-up under all conditions.

Optimum values of C and R<sub>P</sub> will depend on the crystal used. However, typical values would be C = 22 pF and R<sub>P</sub> = 1 M $\Omega$ .

#### 7.9.3 REFERENCE CLOCK (RCLK)

The reference clock input, RCLK, is used as the source for the sampling of the IF input signal. A divided-down version of RCLK is output on the sample clock pin, SCLK, for use by the front-end IC.

The division ratio of RCLK/SCLK is programmable in firmware. In the standard Philips firmware this ratio is set to 3.

### SAA1575HL

#### 8 LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134).