### INTEGRATED CIRCUITS

# DATA SHEET

## XA-H4 Single-chip 16-bit microcontroller

Preliminary specification IC28 Data Handbook

### Single-chip 16-bit microcontroller

XA-H4

#### **DESCRIPTION**

The powerful 16-bit XA CPU core and rich feature set make the XA-H3 and XA-H4 devices ideal for high-performance real-time applications such as industrial control and networking. By supporting of up to 32 MB of external memory, these devices provide a low-cost solution to embedded applications of any complexity. Features like DMA, memory controller and four advanced USARTs help solve I/O intensive tasks with a minimum of CPU load.

The XA-H3 feature set is a subset of the XA-H4 (see Table 1). The XA-H3/H4 devices are members of the Philips XA (eXtended Architecture) family of high performance 16-bit microcontrollers.

The XA-H3 and XA-H4 are designed to significantly minimize the need for external components.

#### **FEATURES**

- Large Memory Support

- De-multiplexed Address/Data Bus

- Six Programmable Chip Selects

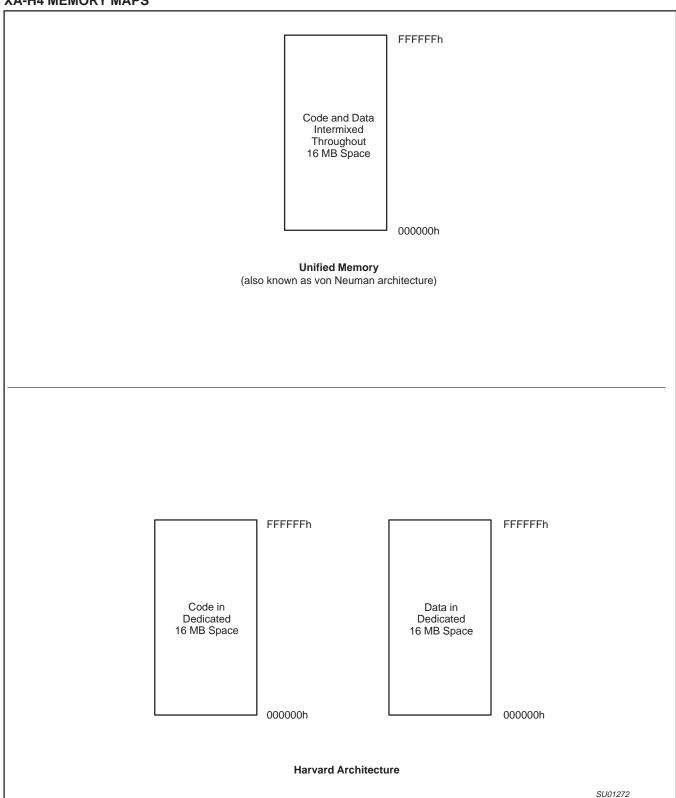

- Support for Unified Memory allows easy user modification of all code

- External ISP Flash support for easy code download

- Dynamic Bus Sizing each of 6 Chip Selects can be programmed for 8-bit or 16-bit bus.

- Dynamic Bus Timing each of 6 chip selects has individual programmable bus timing.

- 32 Programmable General Purpose I/O Pins

- Four USARTs with 230.4 kbps capability

- Eight DMA Channels

#### ADDITIONAL XA-H4 FEATURES (NOT AVAILABLE ON XA-H3)

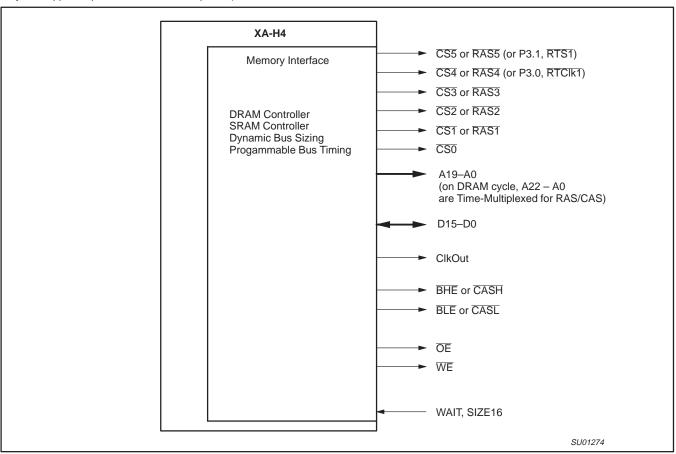

- Complete DRAM controller supports up to four banks of 8 MB each

- Memory controller supports 16 MB in Unified Mode

- Memory controller supports 32 MB in Harvard Mode

- Serial ports are USARTs

- Synchronous capability up to 1 Mbps, and include HDLC/SDLC support

- Four Match Characters are supported on each USART in Async Mode

- Hardware Autobaud on all four USARTs in Async Mode

- USARTs are improved 85C30 style

## Single-chip 16-bit microcontroller

XA-H4

Table 1. XA-H3 and XA-H4 features comparison

| Feature                                                           | XA-H3                          | XA-H4                                  |

|-------------------------------------------------------------------|--------------------------------|----------------------------------------|

| Maximum External Memory<br>(Harvard Memory Mode)                  | 6 MB                           | 32 MB<br>(16 MB Code, 16 MB Data)      |

| Maximum External Memory<br>(Unified Memory Mode)                  | 6 MB                           | 16 MB                                  |

| Memory Controller supports both Harvard and Unified architectures | Yes                            | Yes                                    |

| De-multiplexed Address/Data Bus                                   | Yes                            | Yes                                    |

| DRAM Controller                                                   | No                             | Yes                                    |

| DMA Channels                                                      | 8                              | 8                                      |

| Dynamic Bus Sizing                                                | Yes                            | Yes                                    |

| Dynamic Bus Timing                                                | Yes                            | Yes                                    |

| Programmable Chip Selects                                         | 6                              | 6                                      |

| General Purpose IO Pins                                           | 33                             | 33                                     |

| Potential Interrupt Pins                                          | 16                             | 16                                     |

| Interrupts (programmable priority)                                | 7 Standard SW                  | 7 Standard SW                          |

|                                                                   | 4 High Priority SW             | 4 High Priority SW                     |

|                                                                   | 9 Hardware Event               | 9 Hardware Event                       |

| Two Counter/Timers plus Watchdog                                  | Yes                            | Yes                                    |

| Baud Rate Generators <sup>1</sup>                                 | 4                              | 4                                      |

| Serial Ports                                                      | 4 UARTs                        | 4 USARTs                               |

| Maximum Serial Data Rates                                         | asynch to 230.4 kbps (no sync) | asynch to 230.4 kbps<br>sync to 1 Mbps |

| Match Characters                                                  | No                             | 4 async chars per USART                |

| Hardware Autobaud                                                 | No                             | up to 230.4 kbps                       |

#### NOTE:

#### **ORDERING INFORMATION**

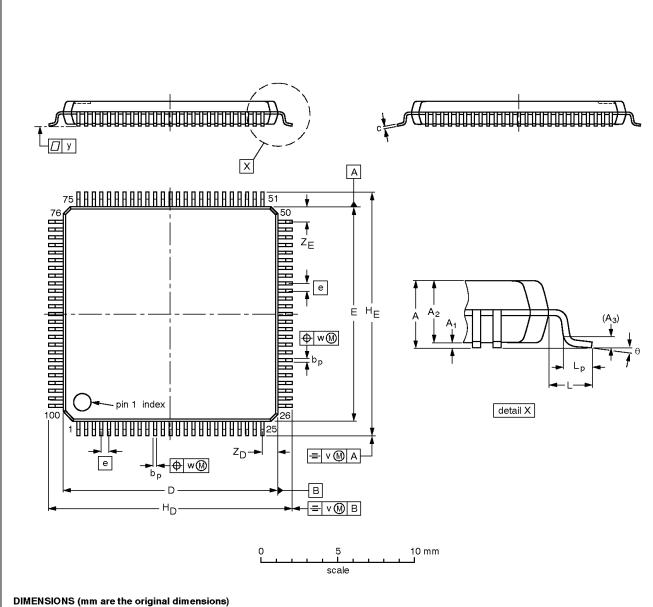

| ROMIess Only    | Temperature range °C and Package                           | Freq (MHz) | Package Drawing Number |

|-----------------|------------------------------------------------------------|------------|------------------------|

| H4 = PXAH40KFBE | −40 to +85°C, 100-Pin Low Profile Quad Flat Package (LQFP) | 30         | SOT407-1               |

#### NOTE

K=30 MHz, F = (-40 to +85), BE = LQFP

<sup>1.</sup> Can be used as additional counters if not needed as BRGs.

### Single-chip 16-bit microcontroller

XA-H4

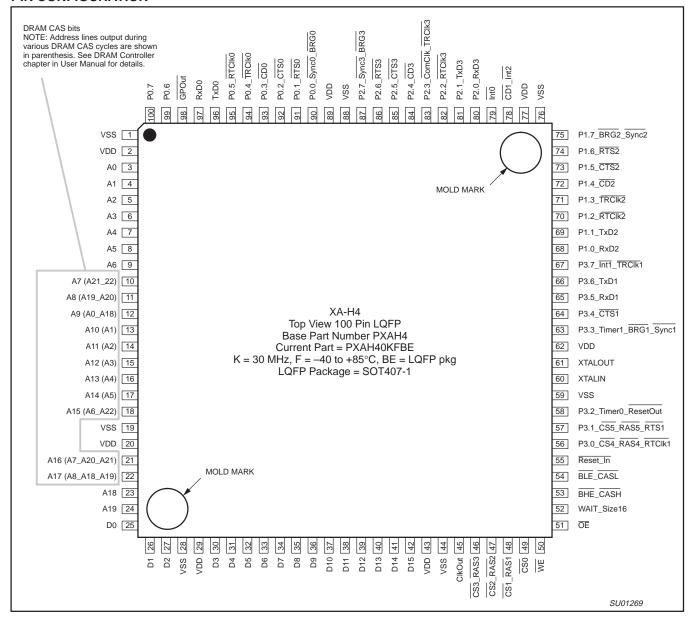

#### PIN CONFIGURATION

#### XA-H4

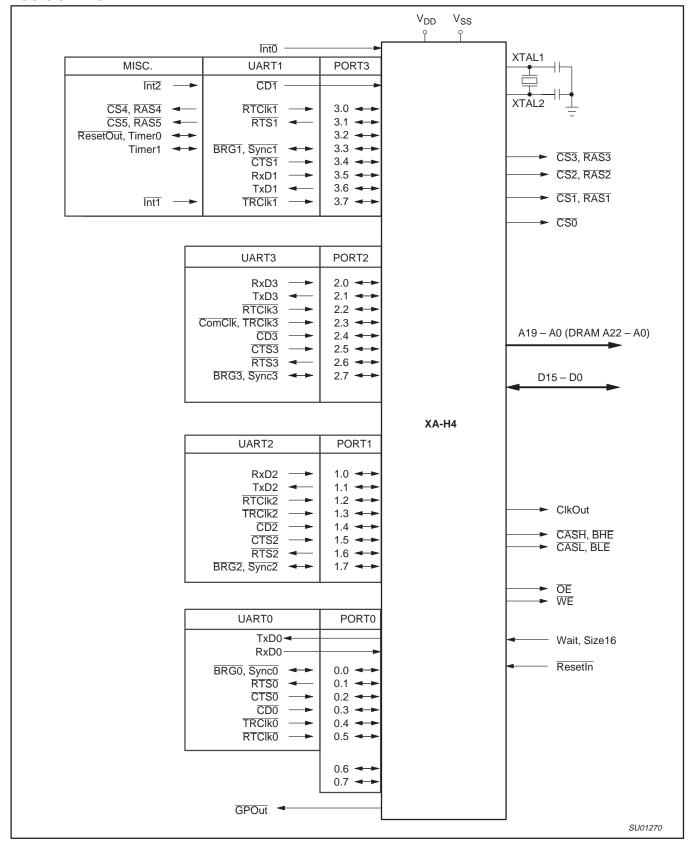

#### **LOGIC SYMBOL XA-H4**

XA-H4

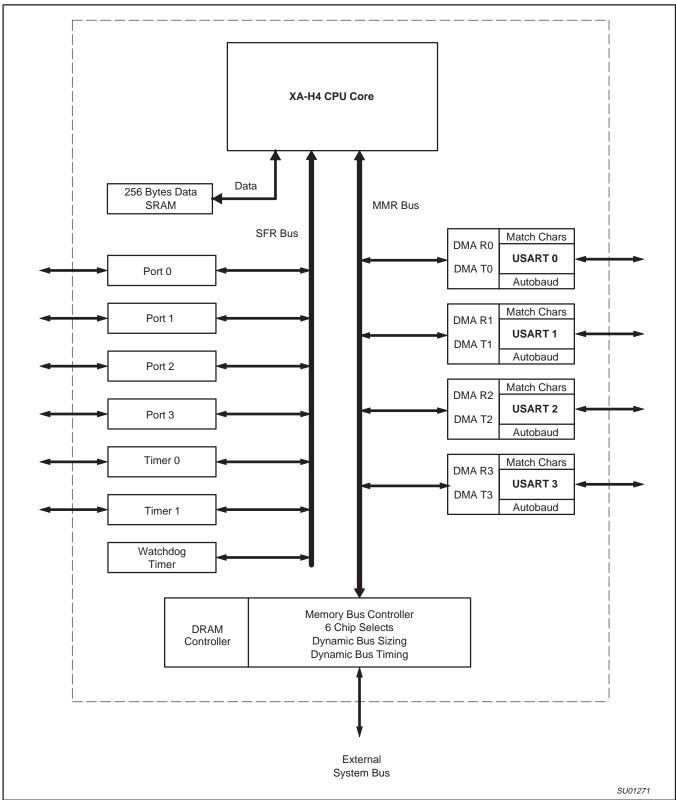

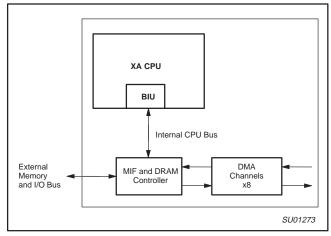

#### **XA-H4 BLOCK DIAGRAM**

XA-H4

#### **XA-H4 MEMORY MAPS**

XA-H4

### **PIN DESCRIPTIONS**

| Mnemonic        | Lqfp<br>Pin No.                 | Туре       | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                     |          |  |  |  |  |  |  |  |

|-----------------|---------------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|--|--|--|

| V <sub>SS</sub> | 1, 19, 28,<br>44, 59,<br>76, 88 | I          | Ground: 0 V reference.                                                                                                                                                                                                                                                                                                                                                                                                                |          |  |  |  |  |  |  |  |

| $V_{DD}$        | 2, 20, 29,<br>43, 62,<br>77, 89 | ı          | Power Supply: This is the power supply voltage for normal, idle, and power down operation.                                                                                                                                                                                                                                                                                                                                            |          |  |  |  |  |  |  |  |

| ResetIn         | 55                              | I          | <b>Reset:</b> A low on this pin resets the microcontroller, causing I/O ports and peripherals to take on their default states, and the processor to begin execution at the address contained in the reset vector.                                                                                                                                                                                                                     |          |  |  |  |  |  |  |  |

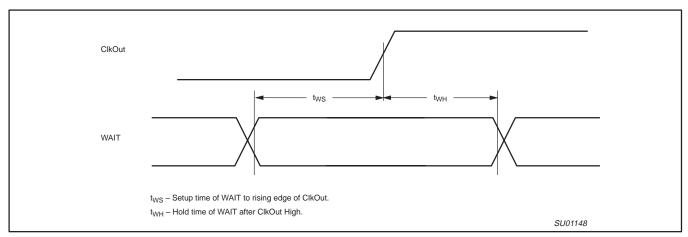

| WAIT/<br>Size16 | 52                              | I          | <b>Wait/Size16:</b> During Reset, this input determines bus size for boot device ("1" = 16-bit boot device; "0" = 8-bit.) During normal operation this is the Wait input ("1" = Wait; "0" = Proceed.)                                                                                                                                                                                                                                 |          |  |  |  |  |  |  |  |

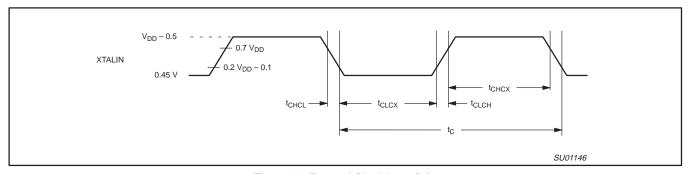

| XTALIn          | 60                              | I          | Crystal 1: Input to the inverting amplifier used in the oscillator circuit and input to the internal clock generator circuits.                                                                                                                                                                                                                                                                                                        |          |  |  |  |  |  |  |  |

| XTALOut         | 61                              | ı          | Crystal 2: Output from the oscillator amplifier.                                                                                                                                                                                                                                                                                                                                                                                      |          |  |  |  |  |  |  |  |

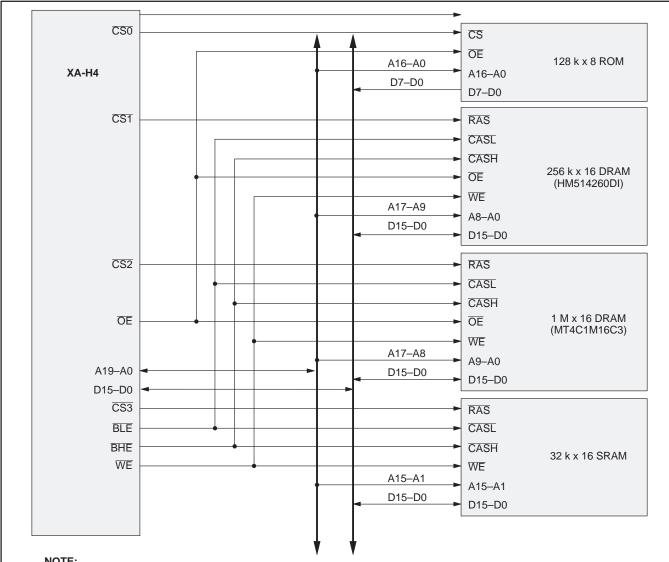

| <del>CS0</del>  | 49                              | 0          | Chip Select 0: This output provides the active low chip select to the boot device (usually ROM or Flash.) It cannot be connected to DRAM. From reset, it is enabled and mapped to an address range based at 000000h. It can be remapped by software to a higher base in the address map (see the "Memory Interface" chapter in the XA-H4 User Manual.)                                                                                |          |  |  |  |  |  |  |  |

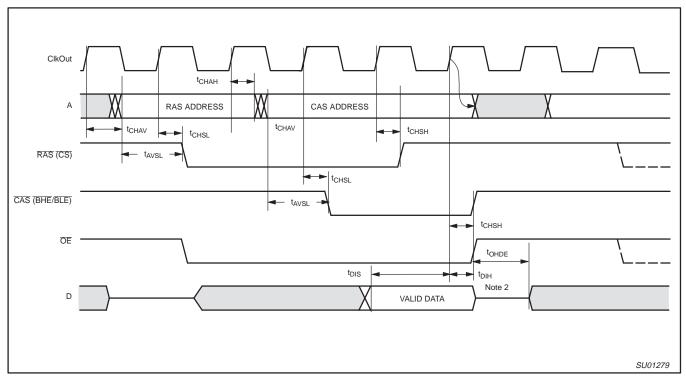

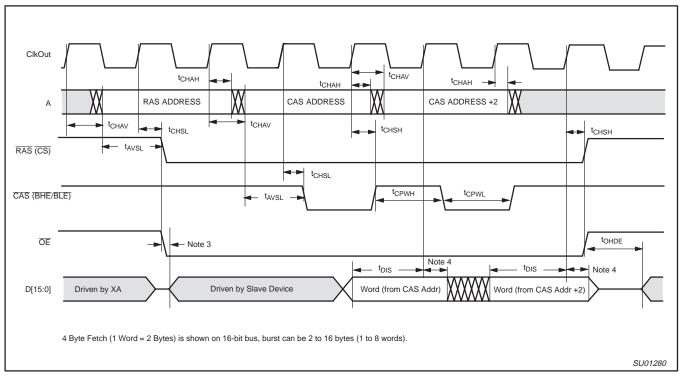

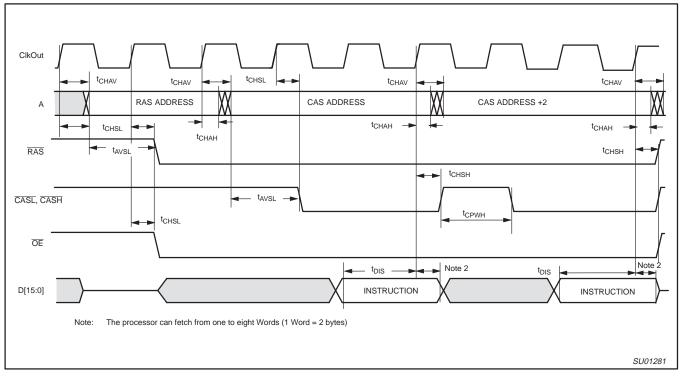

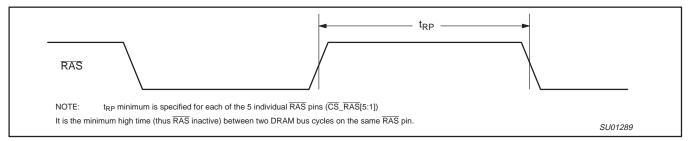

| CS1_RAS1        | 48                              | 0          | Chip Select 1 or RAS1: Chip Selects and RAS 1 through 5 come out of reset disabled. They can be programmed to function as normal chip selects, or as RAS strobes to DRAM. CS1 can be "swapped" with CS0 (see the SWAP operation and control bit in the "Memory Controller" chapter of the XA-H4 User Manual.) CS1 is usually mapped to be based at 000000h after the swap, but is capable of being based anywhere in the 16 MB space. |          |  |  |  |  |  |  |  |

| CS2_RAS2        | 47                              | 0          | Chip Select 2 or RAS2: Active low Chip Selects CS1 through CS5 come out of reset disabled. They can be programmed to function as normal chip selects, or as RAS strobes to DRAM. CS2 through CS5 are not used with the "SWAP" operation (see the "Memory Controller" chapter in the XA-H4 User Manual.) They are mappable to any region of the 16 MB address space.                                                                   |          |  |  |  |  |  |  |  |

| CS3_RAS3        | 46                              | 0          | CS3 or RAS3: See Chip Select 2 for description.                                                                                                                                                                                                                                                                                                                                                                                       |          |  |  |  |  |  |  |  |

| See Pins 56,    | 57 for 2 ad                     | ditional C | Chip Selects                                                                                                                                                                                                                                                                                                                                                                                                                          |          |  |  |  |  |  |  |  |

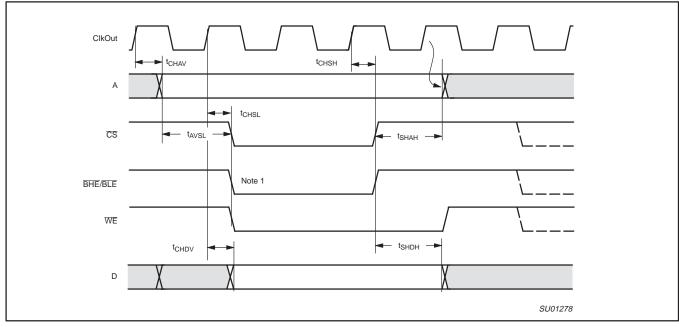

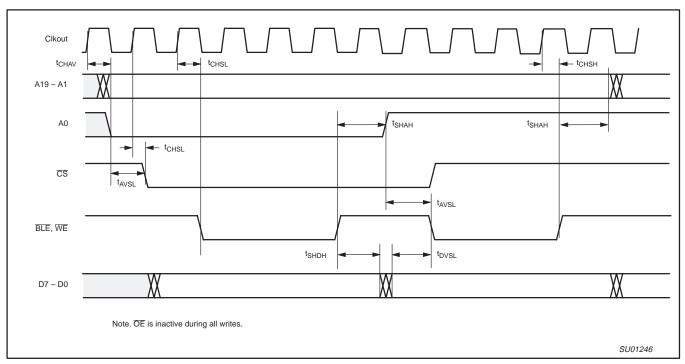

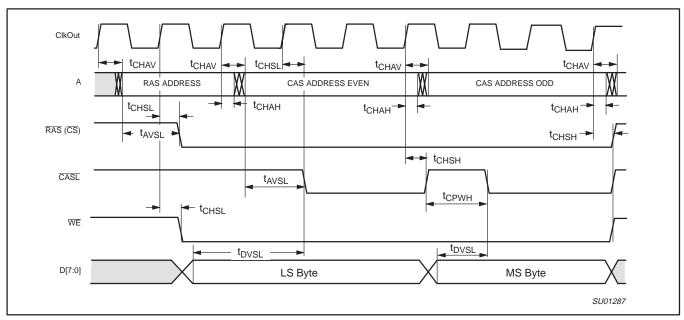

| WE              | 50                              | 0          | Write Enable: Goes active low during all bus write cycles only.                                                                                                                                                                                                                                                                                                                                                                       |          |  |  |  |  |  |  |  |

| ŌĒ              | 51                              | 0          | Output Enable: Goes active low during all bus read cycles only.                                                                                                                                                                                                                                                                                                                                                                       |          |  |  |  |  |  |  |  |

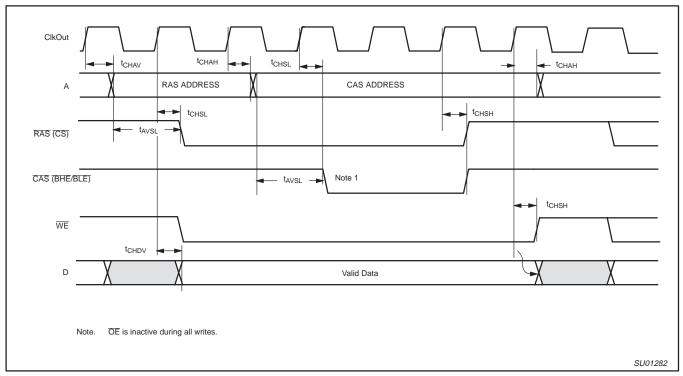

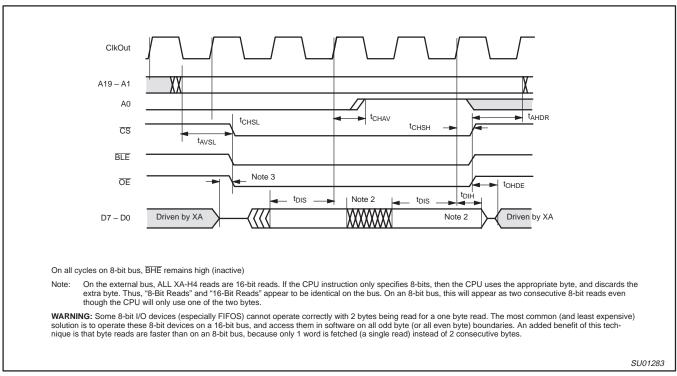

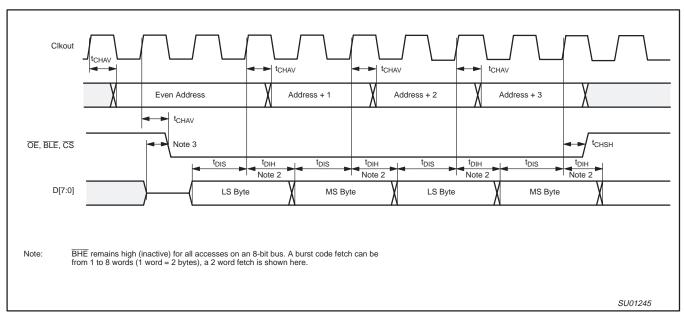

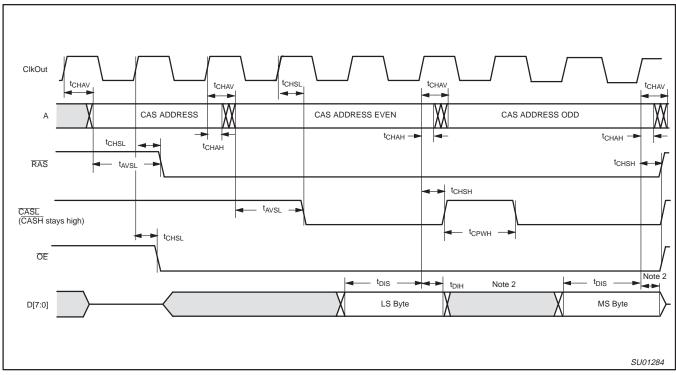

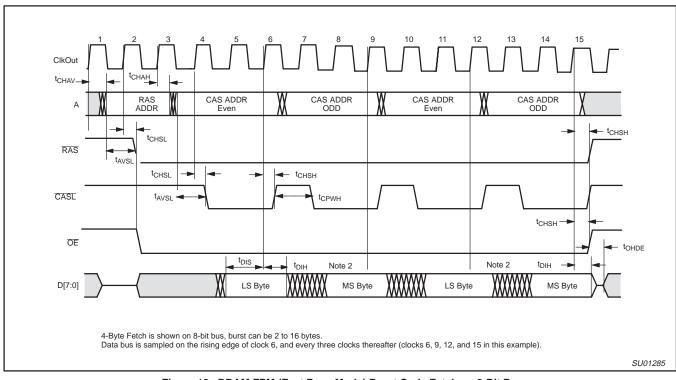

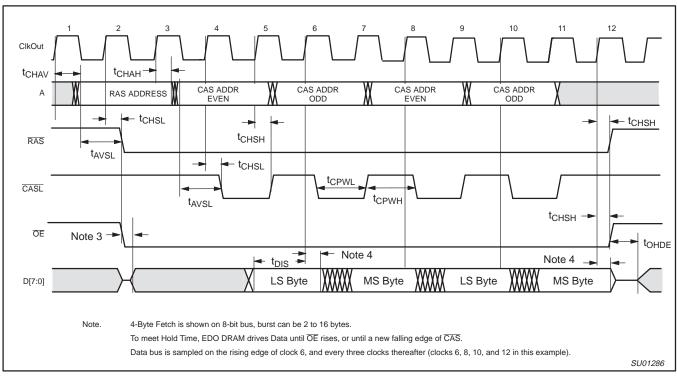

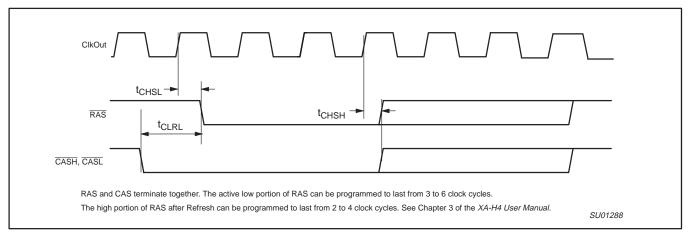

| BLE_CASL        | 54                              | 0          | Byte Low Enable or CAS_Low_Byte: Goes active low during all bus cycles that access D7 – D0, read or write, Generic or DRAM. Functions as CAS during DRAM cycles.                                                                                                                                                                                                                                                                      |          |  |  |  |  |  |  |  |

| BHE_CASH        | 53                              | 0          | Byte High Enable or CAS_High_Byte: Goes active low during all bus cycles that access data bus lines D15 – D8, read or write, Generic or DRAM. Functions as CAS during DRAM cycles.                                                                                                                                                                                                                                                    |          |  |  |  |  |  |  |  |

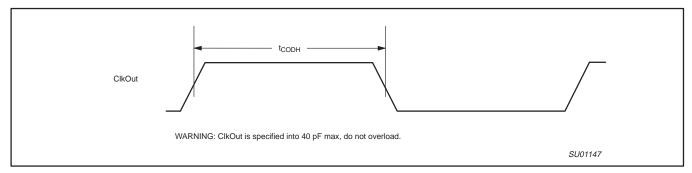

| ClkOut          | 45                              | 0          | Clock Output: This pin outputs a buffered version of the internal CPU clock. The clock output may be used in conjunction with the external bus to synchronize WAIT state generators, etc. The clock output may be disabled by software.  WARNING: The capacitive loading on this output must not exceed 40 pf.                                                                                                                        |          |  |  |  |  |  |  |  |

| A19 – A0        | 24 – 21,<br>18 – 3              | 0          | Address[19:0]: These address lines output A19 – A0 during (SRAM, etc.) bus cycles.  DRAMS (H4 only) are connected only to pins 22, 21, 18 – 10 (pins A17 to A7; see user manual "MIF Chapter" for connecting various DRAM sizes); the appropriate address values are multiplexed onto these 11 pins for RAS and CAS during DRAM bus cycles.                                                                                           |          |  |  |  |  |  |  |  |

| D15 – D0        | 42 – 30,<br>27 – 25             | I/O        | Data[15:0]: Bi-directional data bus, D15 – D0.                                                                                                                                                                                                                                                                                                                                                                                        |          |  |  |  |  |  |  |  |

| P0.0            | 90                              | I/O        | P0.0_Sync0_BRG0: Port 0 Bit 0, or USART0 Sync input or output, or USART0 BRG output, or USART0 TxClk output.                                                                                                                                                                                                                                                                                                                          | 1        |  |  |  |  |  |  |  |

| P0.1            | 91                              | I/O        | P0.1_RTS0: Port 0 Bit 1, or USART0 RTS (Request To Send) output.                                                                                                                                                                                                                                                                                                                                                                      | 1        |  |  |  |  |  |  |  |

| P0.2            | 92                              | I/O        | P0.2_CTS0: Port 0 Bit 2, or USART0 CTS (Clear To Send) input.                                                                                                                                                                                                                                                                                                                                                                         | 1        |  |  |  |  |  |  |  |

| P0.3            | 93                              | I/O        | P0.3_CD0: Port 0 Bit 3, or USART0 Carrier Detect input.                                                                                                                                                                                                                                                                                                                                                                               | 1        |  |  |  |  |  |  |  |

| P0.4            | 94                              | I/O        | P0.4_TRCIk0: Port 0 Bit 4, or USART0 TR clock input.                                                                                                                                                                                                                                                                                                                                                                                  | 1, 2     |  |  |  |  |  |  |  |

| P0.5            | 95                              | I/O        | P0.5_RTClk0: Port 0 Bit 5, or USART0 RT clock input.                                                                                                                                                                                                                                                                                                                                                                                  | 1, 2     |  |  |  |  |  |  |  |

| P0.6            | 99                              | I/O        | <b>P0.6:</b> Port 0 Bit 6                                                                                                                                                                                                                                                                                                                                                                                                             | 1        |  |  |  |  |  |  |  |

|                 |                                 |            |                                                                                                                                                                                                                                                                                                                                                                                                                                       | <u> </u> |  |  |  |  |  |  |  |

XA-H4

| Mnemonic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Lqfp<br>Pin No. | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | See<br>Note |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| TxD0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 96              | 0    | TxD0: Transmit data for USART0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             |

| RxD0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 97              | ı    | RxD0: Receive data for USART0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |             |

| GPOut                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 98              | 0    | GPOut – General Purpose Output Bar: Similar to GPIO, but Push/Pull and inverted output only. WARNING: This output is inverted. The polarity of the pin is the opposite of the bit that drives it (GPOut[7])                                                                                                                                                                                                                                                                                                                                                         |             |

| P1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 68              | I/O  | P1.0_RxD2: Port 1 Bit 0, or USART2 RxD input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |

| P1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 69              | I/O  | P1.1_TxD2: Port 1 Bit 1, or USART2 TxD output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |

| P1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 70              | I/O  | P1.2_RTCIk2: Port 1 Bit 2, or USART2 RT Clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2           |

| P1.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 71              | I/O  | P1.3_TRCIk2: Port 1 Bit 3, or USART2 TR Clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2           |

| P1.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 72              | I/O  | P1.4_CD2: Port 1 Bit 4, or USART2 Carrier Detect input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |

| P1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 73              | I/O  | P1.5_CTS2: Port 1 Bit 5, or USART2 Clear To Send input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |

| P1.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 74              | I/O  | P1.6_RTS2: Port 1 Bit 6, or USART2 Request To Send output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |

| P1.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 75              | I/O  | P1.7_BRG2_Sync2: Port 1 Bit 7, or USART2 Sync input or output, or BRG output, or TxClk output (see USART clk diagrams in the user manual.)                                                                                                                                                                                                                                                                                                                                                                                                                          |             |

| P2.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 80              | I/O  | P2.0_RxD3: Port 2 Bit 0, or USART3 Rx Data input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |

| P2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 81              | I/O  | P2.1_TxD3: Port 2 Bit 1, or USART3 Tx Data output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |

| P2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 82              | I/O  | P2.2_RTClk3: Port 2 Bit 2, or USART3 RT Clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2           |

| P2.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 83              | I/O  | P2.3_ComClk_TRClk3: Port 2 Bit 3, or USART3 TR Clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2           |

| P2.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 84              | I/O  | P2.4_CD3: Port 2 Bit 4, or USART3 Carrier Detect input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |

| P2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 85              | I/O  | P2.5_CTS3: Port 2 Bit 5, or USART3 Clear To Send input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |

| P2.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 86              | I/O  | P2.6_RTS3: Port 2 Bit 6, or USART3 Request To Send output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |

| P2.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 87              | I/O  | P2.7_Sync3_BRG3: Port 2 Bit 7, or USART3 Sync input or output, or BRG output, or TxClk output (see USART clock diagrams in the user manual.)                                                                                                                                                                                                                                                                                                                                                                                                                        |             |

| P3.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 56              | I/O  | P3.0_CS4_RAS4_RTClk1: Port 3 Bit 0, or CS4 or RAS 4 output, or USART1 RT Clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 |      | Active low chip selects CS1 through CS5 come out of reset disabled. They can be programmed to function as normal chip selects, or as RAS strobes to DRAM. CS2 through CS5 are not used with the "SWAP" operation (see the "Memory Controller" chapter in the <i>XA-H4 User Manual</i> .) They are mappable to any region of the 16 MB address space.                                                                                                                                                                                                                |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 |      | P3.1_CS5_RTS1: Port 3 Bit 1, or CS5 output, or USART1 Request To Send output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |

| P3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 57              | I/O  | Active low chip selects CS1 through CS5 come out of reset disabled. They can be programmed to function as normal chip selects, or as RAS strobes to DRAM. CS2 through CS5 are not used with the "SWAP" operation (see the "Memory Controller" chapter in the <i>XA-H4 User Manual</i> .) They are mappable to any region of the 16 MB address space.                                                                                                                                                                                                                |             |

| P3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 58              | I/O  | P3.2_Timer0_ResetOut: Port 3 Bit 2, or Timer0 input or output, or ResetOut output. ResetOut: If the ResetOut function is selected, this pin outputs a low whenever the XA-H4 processor is reset by an internal source (Watchdog Reset or the RESET instruction.) WARNING: Unlike the other 31 GPIO pins, during power up reset, this pin can output a strongly driven low pulse. The duration of this low pulse ranges from 0 ns to 258 system clocks, starting at the time that V <sub>CC</sub> is valid. The state of the ResetIn pin does not affect this pulse. |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 |      | When used as GPIO, this pin can be driven low by software without resetting the XA-H4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |

| P3.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 63              | I/O  | P3.3_Timer1_BRG1_Sync1: Port 3 Bit 3, or Timer1 input or output, or USART1 BRG output, or USART1 Sync input or output.                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |

| P3.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 64              | I/O  | P3.4_CTS1: Port 3 Bit 4, or USART1 Clear To Send input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |

| P3.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 65              | I/O  | P3.5_RxD1: Port 3 Bit 5, or USART1 Receive Data input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |