**PHILIPS**

Let's make things better.

#### Why consumer oriented DSP is different

Without the advent of digital signal processing many of the latest advances in personal communications and multimedia entertainment would not have been possible. Digitising analog signals and processing them in the digital domain not only eliminates the temperature drift and ageing problems associated with analog circuitry, it also means that adaptation to changing standards and the inclusion of advanced new performance features can be accomplished with software changes rather than changes to the hardware. Digital signal processing has also had an impact on the digital world, dramatically increasing the storage density of hard/optical disk drives and the speed with which data can be transmitted.

The latest generation of consumer product DSP applications (for example, baseband signal processing in digital mobile/cordless telephones and multi-channel audio decoding in digital TV transmissions) requires considerable processing power — comparable in terms of MOPS (Million Operations Per Second) to that of a desktop PC. In addition, most of these applications are 'real-time', putting severe constraints on the time available to calculate the required DSP algorithms.

With the ready availability of both DSP and RISC processors that can be clocked at several hundred MHz, it is tempting to solve these real-time processing problems simply by increasing the clock speed. However, the penalty you pay for doing so is greater power consumption, which increases linearly with clock frequency. In applications such as mobile and cordless telephones, where extended standby and talk times are key selling features, it is simply unacceptable to adopt a solution that increases the drain on the battery. Because consumer applications are also very price sensitive, the challenge for designers is to find a solution that combines high functional performance (as opposed to raw MIPS performance), low power operation and low cost in a single implementation solution.

Many consumer applications also call for a highly integrated implementation, in which the DSP processor is part of a complete system-on-silicon solution. If circuit miniaturisation is important, such single-chip systems-on-silicon have obvious advantages, and if the volume is high enough they will also be the lowest cost option. Because of the absence of glue logic and peripheral components, single-chip solutions often also achieve the lowest power consumption.

However, in addition to the technical advantages of adopting a system-on-silicon approach, there is also a strong business advantage in doing so. In a world that is more and more dominated by standards (such as GSM and DECT for wireless telephony and MPEG for digital video/audio) the only way for equipment manufacturers to differentiate themselves from their competitors is by designing performance improvements or extra features into their products. The expertise within a company that allows it to achieve this — often referred to as a company's 'intellectual property' (IP) — needs careful guarding so that it cannot easily be copied. In this respect, system-on-silicon solutions have the IP protection advantage of being almost impossible to reverse engineer.

The value of intellectual property in the arena of DSP is particularly significant for several other reasons as well. The algorithms involved require in-depth knowledge of complex arithmetic operations that are highly sensitive to bit inaccuracies. In addition, real-time DSP applications involve a very wide design space in which hardware and software codesign is the only way to arrive at optimal solutions. As a result, DSP expertise is in short supply and therefore expensive to acquire.

### Possible approaches to providing the necessary DSP performance.

Because power consumption considerations preclude the possibility of simply increasing the clock frequency in order to meet the required MOPS performance, most consumer product applications utilise DSP processors that feature a high degree of parallelism. This parallelism can be achieved in a variety of ways, each having its own advantages and disadvantages.

Deep Pipelining. Although not strictly a form of parallelism, deeper pipelining means that more instructions can be executed in the current processing sequence, thereby increasing the instruction throughput rate. However, deep pipelines can suffer from a high level of latency under program jump, branch and task switching conditions because the pipeline needs to be purged and refilled with a new section of program code. Mechanisms to overcome this latency (such as branch prediction, speculative calculation, and pipeline bypassing) have been employed in some advanced RISC processors, but they all come at a price in terms of additional silicon area and higher power consumption. Because they disturb the temporal predictability of program execution, these techniques would in any case prove complicated in real-time DSP processors.

Instruction-Level Parallelism. This is a true parallel processing technique that adds additional execution units (such as an additional multiplier/accumulator) to the DSP so that two or more data paths can be driven in parallel by a single instruction sequencer. Bearing in mind the inherent parallelism that exists in most DSP algorithms, instruction-level parallelism is an ideal technique for increasing the speed of algorithm execution. For example, the addition of a second multiplier/accumulator can speed up algorithms such as block-based FIR filters and FFTs by a factor of more than two compared to single multiplier/accumulator architectures, without any need to increase the clock frequency.

**Data-Level Parallelism.** Many of the multiply/accumulate algorithms found in typical DSP applications involve the multiplication of a large number of data values by a set of fixed coefficients. Where this high degree of regularity in the data structure exists, advantage can be gained by packing two or more data values into a single data word that can be fetched from memory in a single cycle. This technique can be used to best advantage when it is combined with instruction level parallelism so that all data path elements are kept busy during each instruction cycle.

Task-Level Parallelism. Where no single DSP processor is capable of executing the algorithms fast enough, the task can be shared between two similar processors (if necessary, on the same chip as in Philips Semiconductors DUET AC3/MPEG multi-channel audio decoder). Such architectures, in which both processors are essentially similar, are referred to as homogeneous. A multi-processor approach can also be used to advantage where different algorithms, or different parts of the same algorithm, require fundamentally different DSP architectures in order to execute efficiently. In this case the architecture is referred to as heterogeneous.

#### The R.E.A.L. DSP Architecture

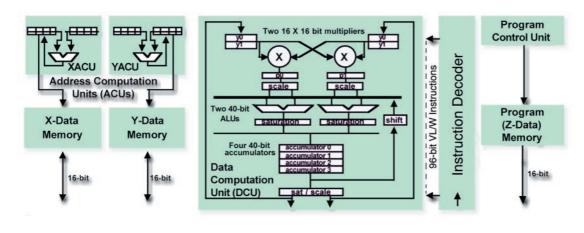

Philips Semiconductors' R.E.A.L. DSP is based largely on techniques for instruction-level parallelism that were first proven in the design of its previous KISS and EPICS families of DSP cores, but R.E.A.L. also includes elements of both data-level and task-level parallelism. R.E.A.L. DSP features an advanced dual Harvard architecture with two 16-bit data bus pathways to its Data Computation Unit (DCU) — see Figure 1. The DCU comprises two 16x16-bit signed multipliers and two 40-bit Arithmetic Logic Units (ALUs) each providing 32 data bits and 8 overflow bits. The data values generated by these ALUs are stored in four 40-bit accumulators.

This dual multiplier/accumulator architecture, first developed by Philips Semiconductors some five years ago, is an example of how the company's extensive applications knowledge — its 'intellectual property' in DSP — has resulted in a core that is optimised for the calculation of sum-of-products based algorithms such as those used extensively for the filtering of baseband signals in wireless telephony. Provided that both multiplier/accumulators can be kept fully occupied, this architecture can halve the time taken to execute these algorithms, without having to increase the clock speed.

To overcome the potential problem of having to fetch two data samples and two coefficients from memory during each instruction cycle (one data sample and one coefficient for each multiplier/accumulator), advantage can be gained from the fact that

practical FIR filter algorithms process the digitised signal samples in blocks. For this finite block size processing, R.E.A.L. DSP's dual multiplier/accumulator architecture can calculate two output samples simultaneously — both calculations using the same coefficient data. As a result a single fetched coefficient can be used simultaneously by both multiplier/accumulators. In addition, because each input sample is used in the calculation of both output samples, separated in time by a single clock cycle, it can be fetched from memory once and stored for one clock cycle in one of the input registers shown in Figure 1.

Optimum use of the data path through R.E.A.L. DSP's dual multiplier/ accumulator architecture is achieved by two independent Address Computation Units (ACUs), both of which can be active within the same instruction cycle. Each ACU features eight address pointers (organised in four banks of two) with automatic context switching of pointers during interrupts and capabilities for modulo protected pointer updates and bit reversed addressing.

The R.E.A.L. DSP dual multiplier/accumulator architecture accelerates the calculation of the vast majority of block processing multiply/accumulate type algorithms without the penalties (in terms of silicon area and memory complexity) of having to use 32-bit wide data buses. For example, a 64-tap FIR filter with a block size of N takes  $8 + 37 \times N$  cycles to execute, compared to a minimum of  $64 \times N$  cycles for a single multiplier/accumulator architecture.

# R.E.A.L. DSP's dual Harvard architecture and dual multiplier/accumulator more than double the execution speed of block-based FIR and FFT type algorithms

X-Data bus Y-Data bus Z-Data bus X-Data bus

Figure 1: R.E.A.L. DSP's dual Harvard architecture and dual multiplier/acculator more than double the execution speed of block-based FIR and FFT type algorithms.

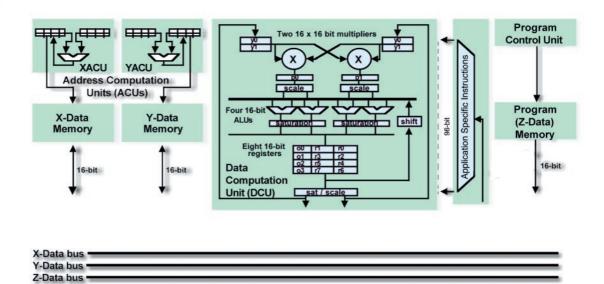

#### **Application Specific Instructions Drive Massive Parallelism**

However, not all DSP algorithms are as regular as FIR filters. Other applications, such as MPEG decoding for set-top boxes, or speech coding in GSM phones, utilise algorithms that contain complex sequences of arithmetic operations. To cope with this type of algorithm, R.E.A.L. DSP's multiplier/accumulator structure can be operated as two multipliers, four independent 16-bit ALUs and eight independent 16-bit registers, together with several shifters and saturation units — see Figure 2. Each one of these elements can be individually controlled from within user-defined 96-bit Application Specific Instructions (ASIs), giving programmers maximum use of a massive amount of parallel processing. ASIs can also be used to control the address computation units (ACUs) and data transfers within the DSP core.

In order to call these instructions from R.E.A.L. DSP's 16-bit program memory, selected ASIs are stored in a look-up table and pointed to by a special class of 16-bit opcode. They are typically only needed to speed up the execution of the tight program loops that make up speed critical parts of algorithm processing, but because these are typically also the loops that execute 90% of the time, the ability of ASIs to customise the R.E.A.L. DSP's instruction set to the target application leads to dramatic improvements in performance. As many as 256 different ASIs can be selected, which has already proved more than enough for complete target applications in mobile telephony and audio processing.

Because ASIs are fully accounted for in R.E.A.L. DSP's assembler, linker and instruction set simulator, the effect of different ASIs on the execution speed of algorithms can be evaluated from within the programming environment. If silicon implementation of the look-up table takes the form of RAM, different sets of ASIs can also be down-loaded to the chip to evaluate their performance, or even to customise the DSP core on-the-fly in order to process radically different algorithms.

Driven by user-defined 96-bit Application Specific Instructions, the R.E.A.L. DSP core adapts to the execution of irregular DSP algorithms

Figure 2: Driven by user-defined 96-bit Application Specific Instructions, The R.E.A.L. DSP core adapts to the execution of irregular DSP algoritms.

#### **Hardware Acceleration Solves Speed-Critical Computations**

Even if a suitable set of ASIs cannot be found to increase algorithm processing to the necessary speed, Philips Semiconductors' R.E.A.L. DSP has yet another means to achieve the required performance. The VHDL synthesis model of the R.E.A.L. DSP core allows designers to add Application Specific Execution Units (AXUs) at specified points in the data path or in the address computation units. By executing parts of the algorithm or address computation in dedicated hardware, these AXUs represent the fastest possible processing solution for a given clock frequency. Philips Semiconductors already has a library of AXUs, such as dedicated shifters, but designers can also design their own AXUs and fit them in to the R.E.A.L. DSP architecture.

Because R.E.A.L. DSP is fully described at VHDL register-transfer level, it is strongly process independent. The existing RD160xx R.E.A.L. DSP cores are implemented in 0.35 micron to 0.25 micron CMOS — operating at clock speeds up to 85 MHz under worst-case operating conditions (2.2 V supply and +85 degree C) and achieving a sustained processing performance well in excess of 850 MOPS. Under typical conditions they can achieve clock speeds of up to 125 MHz, increasing their MOPS rating to 1,250.

The dual multiplier-accumulator version is the RD16020, but there is also a cut-down single multiplier/accumulator version designated the RD16010 core for lower cost/performance applications. New generations are already under development for implementation in sub 0.25 micron CMOS, with increased processing performance and extension of the data pathways from 16 bits to 24 bits to handle the resolution required in complex, high-end audio applications.

#### **Design Tools**

With the current state of embedded DSP technology, hand-crafted assembly language programming is still needed to create the time-critical inner loops that make up DSP algorithms, not only to create code that will execute fast enough but also to generate code that is compact enough to fit within realistically sized embedded memories. Programs written in assembler, however, suffer the disadvantages of being time consuming to generate, difficult to maintain and, above all, difficult to reuse. In addition, assembler programs are often poorly documented and only the original programmer can read them efficiently and understand how they work.

In consumer product applications where the re-use of intellectual property (IP) and short time-to-market are critical factors in business success, assembly language programming is not a realistic way forward. The solution is to provide users with efficient high-level language compilers that can handle the complexities of DSP architectures. Because of its widespread use and standardisation, ANSI-C is the obvious choice of high-level language to use.

However, C was not written with DSP processors in mind. It was written for standard Von Neuman architectures (common data/program memory) with a single contiguous memory space and no fixed register structures. DSP processors, on the other hand, typically have Harvard architectures (separate data and program memory) with multiple address spaces, dedicated register sets and a high degree of parallelism, all of which affect program compilation. In addition, ANSI-C doesn't support the fixed point arithmetic employed by most DSPs.

As well as supporting R.E.A.L. with an assembler and linker to meet current programming expectations, Philips Semiconductors is also working on C compilers for R.E.A.L. DSP. Using the CoSy compiler development platform from ACE Associated Compiler Experts b.v. (Amsterdam,The Netherlands), one of the world's leading compiler technology companies, Philips Semiconductors has already produced a fully validated ANSI-C compiler that is capable of handling the control code that surrounds DSP algorithms. Work is now underway, in collaboration with ACE, to add DSP specific extensions to the compiler so that it can also generate the cycle-count optimised DSP code which, although it only makes up 10% of the program, runs 90% of the time.

The flexible framework of CoSy, with its rigorously defined intermediate representation, opens up the possibility of making powerful optimisation strategies available to programmers.

The existing development platform is being complemented by a state-of-the-art Code Development Framework (CDF), which in addition to providing programmers with an integrated development environment and a common graphical user interface, will also include (among other features) configuration management and Real-Time Operating System (RTOS) support.

Whichever way code is generated, the R.E.A.L. DSP development platform includes powerful tools for software and hardware simulation and debugging. An instruction set simulator allows designers to experiment with different sets of ASIs or even to modify R.E.A.L. DSP's hardware architecture by adding AXUs as a result of the simulation results. Emulation chips, capable of executing up to 50 million instructions per second, are available for real-time evaluation of program performance, and the program can also be simulated on aVHDL model of the final core for interconnect verification. Simulated and verified designs are supplied in the form of compiled VHDL, a synthesised netlist or placed and routed blocks, allowing R.E.A.L. DSP cores to be integrated seamlessly into ASIC design flows to create complete systems-on-silicon.

Creating these systems-on-silicon requires IP contributions not only in the area of DSP, but also in areas such as embedded microcontrollers, peripheral devices, memory, A/D and D/A conversion, I/O interfacing and mixed signal circuitry. More importantly, it requires IP input in the areas of system level simulation tools, multi-processor architectures and high bandwidth on-chip bus structures. Philips Semiconductors possesses a high level of IP in all these areas, which together with its in depth knowledge of real applications, puts it in a strong position to create the low-cost, low-power systems-on-silicon that will power the next generation of high-technology consumer products.

## Philips Semiconductors – a worldwide company

Argentina: see South America

Australia: 34 Waterloo Road, NORTH RYDE, NSW 2113

Tel. +61 2 9805 4455, Fax. +61 2 9805 4466

Austria: Computerstr 6 A-1101 WIEN P.O. Box 213 Tel +43 160 1010

Fax. +43 160 101 1210

**Belarus:** Hotel Minsk Business Center, Bld. 3, r. 1211, Volodarski Str. 6, 220050 MINSK, Tel. +375 172 200 733, Fax. +375 172 200 773

Belgium: see The Netherlands

Bulgaria: Philips Bulgaria Ltd., Energoproject, 15th floor,

51 James Bourchier Blvd., 1407 SOFIA Tel. +359 2 689 211, Fax. +359 2 689 102

Canada: PHILIPS SEMICONDUCTORS/COMPONENTS,

Tel. +1 800 234 7381

China/Hong Kong: 501 Hong Kong Industrial Technology Centre,

72 Tat Chee Avenue, Kowloon Tong, HONG KONG, Tel. +852 2319 7888, Fax. +852 2319 7700

Colombia: see South America

Czech Republic: see Austria

Denmark: Prags Boulevard 80, PB 1919, DK-2300 COPENHAGEN S,

Tel. +45 32 88 2636, Fax. +45 31 57 0044 Finland: Sinikalliontie 3, FIN-02630 ESPOO, Tel. +358 9 615800, Fax. +358 9 61580920

France: 51 Rue Carnot, BP317, 92156 SURESNES Cedex,

Tel. +33 1 40 99 6161, Fax. +33 1 40 99 6427

Germany: Hammerbrookstraße 69, D-20097 HAMBURG,

Tel. +49 40 23 53 60, Fax. +49 40 23 536 300

Greece: No. 15, 25th March Street, GR 17778 TAVROS/ATHENS,

Tel. +30 1 4894 339/239, Fax. +30 1 4814 240

India: Philips INDIA Ltd. Band Box Building, 2nd floor 254-D, Dr. Annie Besant Road, Worli, MUMBAI 400 025, Tel. +91 22 493 8541, Fax. +91 22 493 0966

Indonesia: PT Philips Development Corporation, Semiconductors Division,

Gedung Philips, Jl. Buncit Raya Kav.99-100, JAKARTA 12510, Tel. +62 21 794 0040 ext. 2501, Fax. +62 21 794 0080

Ireland: Newstead, Clonskeagh, DUBLIN 14

Tel. +353 1 7640 000. Fax. +353 1 7640 200

Israel: RAPAC Electronics, 7 Kehilat Saloniki St. PO Box 18053. TEL AVIV 61180, Tel. +972 3 645 0444, Fax. +972 3 649 1007

Italy: PHILIPS SEMICONDUCTORS, Piazza IV Novembre 3

20124 MILANO, Tel. +39 2 6752 2531, Fax. +39 2 6752 2557

Japan: Philips Bldg 13-37, Kohnan 2-chome, Minato-ku TOKYO 108-8507, Tel. +81 3 3740 5130, Fax. +81 3 3740 5077

Korea: Philips House, 260-199 Itaewon-dong, Yongsan-ku, SEOUL,

Tel. +82 2 709 1412, Fax. +82 2 709 1415

Malaysia: No. 76 Jalan Universiti, 46200 PETALING JAYA, SELANGOR,

Tel. +60 3 750 5214, Fax. +60 3 757 4880

Mexico: 5900 Gateway East, Suite 200, EL PASO, TEXAS 79905,

Tel. +9-5 800 234 7381

Middle East: see Italy

Netherlands: Postbus 90050, 5600 PB FINDHOVEN, Bldg, VB

Tel. +31 40 27 82785, Fax. +31 40 27 88399

New Zealand: 2 Wagener Place, C.P.O. Box 1041, AUCKLAND

Tel. +64 9 849 4160, Fax. +64 9 849 7811 Norway: Box 1, Manglerud 0612, OSLO. Tel. +47 22 74 8000, Fax. +47 22 74 8341

Pakistan: see Singapore

Philippines: Philips Semiconductors Philippines Inc., 106 Valero St. Salcedo Village, P.O. Box 2108 MCC, MAKATI, Metro MANILA, Tel. +63 2 816 6380, Fax. +63 2 817 3474

Poland: UI. Lukiska 10, PL 04-123 WARSZAWA, Tel. +48 22 612 2831. Fax. +48 22 612 2327

Portugal: see Spain

Romania: see Italy

Russia: Philips Russia, UI. Usatcheva 35A, 119048 MOSCOW,

Tel. +7 095 755 6918, Fax. +7 095 755 6919

**Singapore:** Lorong 1, Toa Payoh, SINGAPORE 319762, Tel. +65 350 2538, Fax. +65 251 6500

Slovakia: see Austria Slovenia: see Italy

South Africa: S.A. PHILIPS Ptv Ltd., 195-215 Main Road Martindale.

2092 JOHANNESBURG, P.O. Box 7430 Johannesburg 2000,

Tel. +27 11 470 5911, Fax. +27 11 470 5494

South America: Al. Vicente Pinzon, 173, 6th floor, 04547-130 SÃO PAULO, SP, Brazil

Tel. +55 11 821 2333, Fax. +55 11 821 2382

Spain: Balmes 22, 08007 BARCELONA

Tel. +34 93 301 6312, Fax. +34 93 301 4107

Sweden: Kottbygatan 7, Akalla, S-16485 STOCKHOLM,

Tel. +46 8 5985 2000, Fax. +46 8 5985 2745

Switzerland: Allmendstrasse 140, CH-8027 ZÜRICH,

Tel. +41 1 488 2741 Fax. +41 1 488 3263

Taiwan: Philips Semiconductors, 6F, No. 96, Chien Kuo N. Rd., Sec. 1, TAIPEI, Taiwan Tel. +886 2 2134 2865, Fax. +886 2 2134 2874

Thailand: PHILIPS ELECTRONICS (THAILAND) Ltd.

209/2 Sanpavuth-Bangna Road Prakanong, BANGKOK 10260, Tel. +66 2 745 4090, Fax. +66 2 398 0793

Turkey: Talatpasa Cad. No. 5, 80640 GÜLTEPE/ISTANBUL, Tel. +90 212 279 2770, Fax. +90 212 282 6707

Ukraine: PHILIPS UKRAINE, 4 Patrice Lumumba str., Building B, Floor 7,

252042 KIEV, Tel. +380 44 264 2776, Fax. +380 44 268 0461

United Kingdom: Philips Semiconductors Ltd., 276 Bath Road, Hayes MIDDLESEX UB3 5BX, Tel. +44 181 730 5000, Fax, +44 181 754 8421

United States: 811 East Arques Avenue, SUNNYVALE, CA 94088-3409,

Tel. +1 800 234 7381 Uruguay: see South America

Vietnam: see Singapore

Yugoslavia: PHILIPS, Trg N. Pasica 5/v, 11000 BEOGRAD, Tel. +381 11 625 344, Fax.+381 11 635 777

For all other countries apply to: Philips Semiconductors, International Marketing & Sales Communications, Building BE-p, P.O. Box 218, 5600 MD EINDHOVEN, The Netherlands, Fax. +31 40 27 24825

Internet: http://www.semiconductors.philips.com

© Philips Electronics N.V. 1998

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights.

Printed in The Netherlands Date of release: September 1998 Document order number: 9397 750 04278

**PHILIPS**

SCB60

Let's make things better

SUNSTAR 商斯达实业集团是集研发、生产、工程、销售、代理经销、技术咨询、信息服务等为一体的高科技企业,是专业高科技电子产品生产厂家,是具有 10 多年历史的专业电子元器件供应商,是中国最早和最大的仓储式连锁规模经营大型综合电子零部件代理分销商之一,是一家专业代理和分銷世界各大品牌 IC 芯片和電子元器件的连锁经营綜合性国际公司,专业经营进口、国产名厂名牌电子元件,型号、种类齐全。在香港、北京、深圳、上海、西安、成都等全国主要电子市场设有直属分公司和产品展示展销窗口门市部专卖店及代理分销商,已在全国范围内建成强大统一的供货和代理分销网络。 我们专业代理经销、开发生产电子元器件、集成电路、传感器、微波光电元器件、工控机/DOC/DOM 电子盘、专用电路、单片机开发、MCU/DSP/ARM/FPGA 软件硬件、二极管、三极管、模块等,是您可靠的一站式现货配套供应商、方案提供商、部件功能模块开发配套商。商斯达实业公司拥有庞大的资料库,有数位毕业于著名高校——有中国电子工业摇篮之称的西安电子科技大学(西军电)并长期从事国防尖端科技研究的高级工程师为您精挑细选、量身订做各种高科技电子元器件,并解决各种技术问题。

微波光电部专业代理经销高频、微波、光纤、光电元器件、组件、部件、模块、整机;电磁兼容元器件、材料、设备;微波 CAD、EDA 软件、开发测试仿真工具;微波、光纤仪器仪表。欢迎国外高科技微波、光纤厂商将优秀产品介绍到中国、共同开拓市场。长期大量现货专业批发高频、微波、卫星、光纤、电视、CATV 器件: 晶振、VCO、连接器、PIN 开关、变容二极管、开关二极管、低噪晶体管、功率电阻及电容、放大器、功率管、MMIC、混频器、耦合器、功分器、振荡器、合成器、衰减器、滤波器、隔离器、环行器、移相器、调制解调器;光电子元器件和组件:红外发射管、红外接收管、光电开关、光敏管、发光二极管和发光二极管组件、半导体激光二极管和激光器组件、光电探测器和光接收组件、光发射接收模块、光纤激光器和光放大器、光调制器、光开关、DWDM 用光发射和接收器件、用户接入系统光光收发器件与模块、光纤连接器、光纤跳线/尾纤、光衰减器、光纤适 配器、光隔离器、光耦合器、光环行器、光复用器/转换器;无线收发芯片和模组、蓝牙芯片和模组。

更多产品请看本公司产品专用销售网站:

商斯达中国传感器科技信息网: http://www.sensor-ic.com/

商斯达工控安防网: http://www.pc-ps.net/

商斯达电子元器件网: http://www.sunstare.com/

商斯达微波光电产品网:HTTP://www.rfoe.net/

商斯达消费电子产品网://www.icasic.com/

商斯达实业科技产品网://www.sunstars.cn/ 微波元器件销售热线:

地址:深圳市福田区福华路福庆街鸿图大厦 1602 室

电话: 0755-82884100 83397033 83396822 83398585

传真: 0755-83376182 (0) 13823648918 MSN: SUNS8888@hotmail.com

邮编: 518033 E-mail:szss20@163.com QQ: 195847376

深圳赛格展销部: 深圳华强北路赛格电子市场 2583 号 电话: 0755-83665529 25059422

技术支持: 0755-83394033 13501568376

欢迎索取免费详细资料、设计指南和光盘 : 产品凡多,未能尽录,欢迎来电查询。

北京分公司:北京海淀区知春路 132 号中发电子大厦 3097 号

TEL: 010-81159046 82615020 13501189838 FAX: 010-62543996

上海分公司: 上海市北京东路 668 号上海賽格电子市场 D125 号

TEL: 021-28311762 56703037 13701955389 FAX: 021-56703037

西安分公司: 西安高新开发区 20 所(中国电子科技集团导航技术研究所)

西安劳动南路 88 号电子商城二楼 D23 号

TEL: 029-81022619 13072977981 FAX:029-88789382