### **IDEAS FOR DESIGN**

Page

| Power/battery switching using VD-MOS FETs                      | 2  |

|----------------------------------------------------------------|----|

| Drivers for brushless DC motors                                | 4  |

| Using the PHN708 and PHN405 in hard disk drives                | 6  |

| Siren driver circuit for car alarms                            | 9  |

| Printed circuit board heatsink area for surface-mount packages | 10 |

#### **POWER/BATTERY SWITCHING USING VD-MOS FETS**

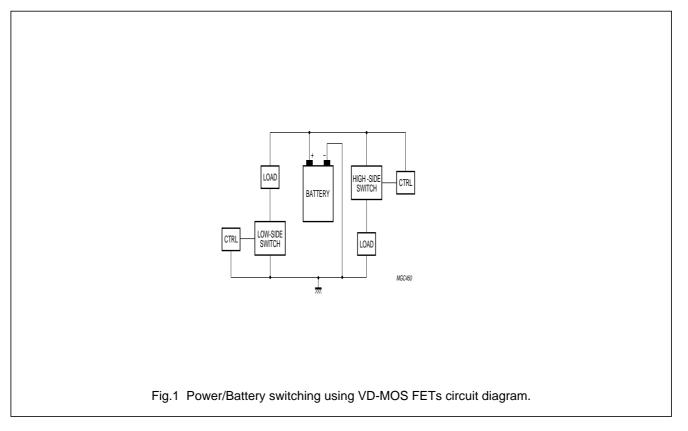

A Power switch can be used to disconnect a load during a period of non use. The load may be anything from a light bulb, an electronic valve, a stepper or brush motor to electronic components in a lap top computer that is not in use all the time. There is a choice between a low-side switch (LSS) located between the load and the power supply return input, and a high-side switch (HSS), between the load and the power supply return is referenced to ground, whilst with an HSS the control is referenced to V<sub>DD</sub> (see Fig.1). This makes the control for an HSS more complicated than for an LSS, and the design is more expensive and has a higher risk.

For power switching purposes MOSFETs have some important advantages over bipolar transistors. Firstly they are voltage controlled instead of current controlled, and secondly they have no thermal runaway or secondary breakdown. This is due to the fact that a MOSFET has a negative temperature coefficient of drain current, while a bipolar transistor has a positive temperature coefficient of collector current. Also the on-resistance of the FET can be reduced simply by connecting two or more in parallel.

Although more expensive, an HSS may perform better during fault conditions. The most probable fault that will

Ideas for design

occur is a short from the output of the switch to ground. Since most environments are connected to ground, damage to the output wire of the switch may be sufficient for an output short to ground to cause the load to remain active. In the case of an HSS the short will be across the load, thus preventing its activation.

It is often required to control power switches from the output of digital logic. The most common logic families use levels of +2.4 V (TTL) or +5 V (CMOS). Figures 2 to 5 illustrate how to switch loads from these logic levels. In Fig.2 the 2.4 volt gate drive will fully turn on a MOSFET with a gate-source threshold voltage (VGS<sub>th</sub>) of less than 1.5 V. However, when using a FET with VGS<sub>th</sub> of less than 3 V (see Fig.3), a gate pull-up resistor connected to +5 V is necessary to generate a full 5 volt swing from the TTL output. Using CMOS levels makes life easier. Since these levels equal the V+ and V- values, a MOSFET is simply chosen with a VGS<sub>th</sub> somewhere between V+ and V-. If the load is returned to ground, a P-channel FET is recommended (see Fig.4), or N-channel (see Fig.5) otherwise.

If the load is inductive, the use of a series gate resistor is recommended, as the drain-gate capacitance of the FET could couple inductive transients of the load back to the delicate logic circuitry.

#### DRIVERS FOR BRUSHLESS DC MOTORS

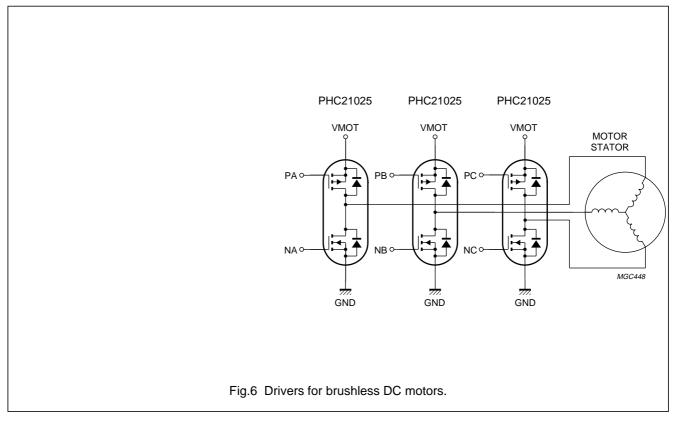

Brushless DC motors normally have a permanent magnet rotor and a wire-wound stator. They are very efficient and provide rapid acceleration, high speed, and smooth, quiet operation. The current to the stator coils is switched electronically as shown in Fig.6 and the switches are arranged in three half-bridge configurations to allow current flow in both directions.

In this example, the complementary P and N channel VD-MOS FETs are shown, but it is also possible to use only N channel switches, depending on the control circuitry. The PHILIPS Integrated Circuit TDA5142T has been chosen as the controller, and three of the PHC21025 MOSFETs (one 100 m $\Omega$  N-channel and one 250 m $\Omega$  P-channel type in a SO8 package) as motor drivers. These FETs can drive motors that require currents of up to 4 A (when soldering point temperature of drain pins does not exceed 80 °C) with gate drive coming directly from the IC.

A characteristic of inductive loads (such as stator windings) is the flyback energy that occurs when the drive current through a winding is switched off. This energy needs to be absorbed by the intrinsic source-drain diode of the FET. The flyback current is equal to the motor current, which is at a maximum during acceleration and (active) braking. The flyback power is the product of both this current and the forward voltage drop over the diode, and of the duty cycle which in turn depends on the inductance of the windings. This dissipation is a substantial part of the total dissipation.

We can take a practical example and calculate the power dissipation of the intrinsic diodes during flyback, and the FETs when in the 'on' state.

Assume that we have a motor with 6000 rpm (100 rps) and 6 pole-pairs (600 'electrical' rps). The period time for one 'electrical revolution' is 1.667 ms. In each 'electrical revolution' all of the six FETs are switched, giving a switching frequency of 3600 Hz. A FET is therefore switching once every 278  $\mu$ s, which is also the maximum time that the diode can be conducting. The FETs themselves are conducting at two periods, 278  $\mu$ s and 556  $\mu$ s, which is at a duty factor of 33%. The dissipation per half bridge (per SO8) is: {0.33 × (I<sub>MOTOR</sub>)<sup>2</sup> × R<sub>DSonP</sub>} + {0.33 × (I<sub>MOTOR</sub>)<sup>2</sup> × R<sub>DSonN</sub>} + flyback<sub>N</sub>.

To calculate the dissipation during flyback for this example, values of 2  $\Omega$  for the ohmic resistance of the windings, and 540  $\mu$ H for the inductance have been assumed. With a 12 V, 1 A motor, SPICE simulations show that the dissipation in the diode during flyback starts at 1.6 W at time zero, decreasing to 0 W after 60  $\mu$ s. This is repeated every 1.667 ms and gives an average dissipation of 29 mW. The dissipation in the N-channel FET is 33 mW and in the P-channel FET 83 mW. This gives a total dissipation of 174 mW, of which 58 mW (33%) is in the diodes and cannot be neglected.

### Ideas for design

During acceleration and (active) braking, the motor current is much higher than during normal operation, and a current limiter may be necessary. The circuit design must be based on this higher current, because acceleration may last for up to a few seconds, long enough to heat up the FETs. During flyback, not only is the current much higher but it also lasts longer. In the simulation example, if the motor current is increased to 3 A, the flyback will last for 120  $\mu$ s. The diode forward voltage will also be higher at this current level, and for one SO8 package the total dissipation increased to 1.5 W.

## USING THE PHN708 AND PHN405 IN HARD DISK DRIVES

Philips Semiconductors has introduced two low-ohmic VD-MOS FET arrays, which are primarily designed for use in hard disk drives. Together with the demand for ever increasing storage capacity and decreasing access times of hard disk drives, also the problems for the design engineers are increasing.

The table below shows what solution we offer for these problems.

For high- and mid-end drives, market developments show a clear trend of moving the power stages from inclusion onto the controller ICs to external discrete field effect transistors.

With the introduction of the two new VD-MOS FET arrays, Philips Semiconductors now offers a cost effective and highly integrated solution to the requirements for external power stages, using up to 35% less printed circuit board area compared with a solution using five or six SO8 packages.

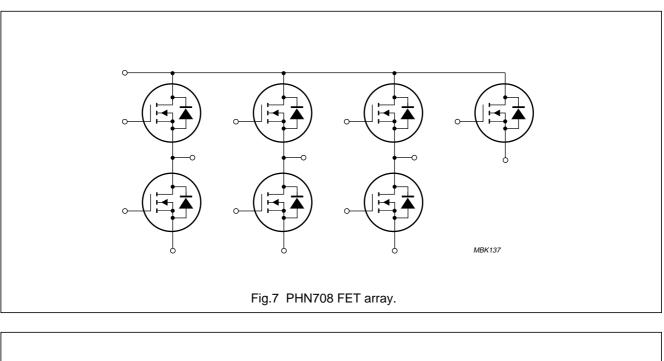

The key feature in the design of these new arrays is that they contain seven (PHN708) or four (PHN405) separate pieces of silicon in one package.

#### PHN708 – power stage for spindle drive

The PHN708 is an array with seven N-channel FETs, with a maximum on-resistance of 80 m $\Omega$  for each FET, and is intended to drive a spindle motor. The maximum drain-source voltage is 30 V, so both 5 and 12 V motors can be used.

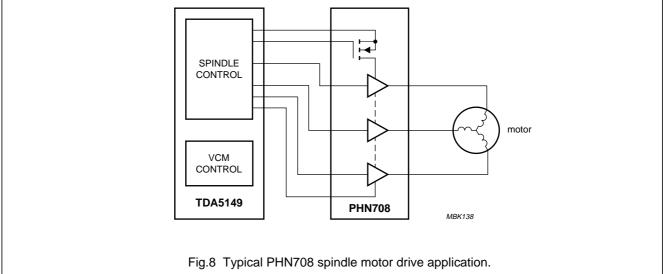

The FETs are configured as shown in Fig.7. Six of them form three half-bridges, needed to drive a three-phase brushless DC motor. The seventh is a so called 'isolation transistor', supplying the power to the half-bridges. This transistor can also be used for the break-function. This of course depends on the controller IC that is used. Together with Philips Semiconductors' TDA5149 combined spindle and voice coil motor controller, a complete solution for spindle-motor drives is provided. (See Fig.8.)

The PHN708 comes in a surface-mount SSOP24 package.

| REQUIREMENT                                               | IMPLEMENTATION                                 | PROBLEM                                               | SOLUTION                     |

|-----------------------------------------------------------|------------------------------------------------|-------------------------------------------------------|------------------------------|

| decreased seek time<br>regarding actuator arm<br>movement | more power in voice coil<br>motor driver stage | controller chip runs too hot                          | external VD-MOS FET<br>array |

| decreased seek time<br>regarding rpm                      | more power in spindle<br>driver stage          | controller chip runs too hot                          | external VD-MOS FET<br>array |

| faster acceleration and deceleration                      | more power in spindle<br>driver stage          | controller chip runs too hot                          | external VD-MOS FET<br>array |

| increased form-factor                                     | more power in spindle<br>driver stage          | controller chip runs too hot                          | external VD-MOS FET<br>array |

| increased number of platters                              | more power in spindle<br>driver stage          | controller chip runs too hot                          | external VD-MOS FET<br>array |

| controlled temperature                                    | less resistance in the circuit                 | larger MOSFETs required                               | external VD-MOS FET<br>array |

| minimal board space                                       | smaller or fewer packages                      | replacement required for single or dual external FETs | external VD-MOS FET<br>array |

Table 1

Hard disk system design considerations

### Ideas for design

#### PHN405 – power stage for voice coil motor control

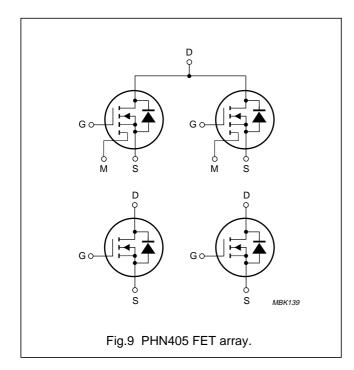

The PHN405 consists of four 50 m $\Omega$  max N-channel FETs, two of which have current-sense capability. It is designed for driving voice coil motors. The maximum drain-source voltage is 30 V.

The FETs are configured as shown in Fig.9. The top two FETs have shared drain terminals, while the bottom two FETs have all terminals available to the outside world. To obtain the required accuracy to position the read/write heads of the drive, it is necessary to monitor the current flowing through the motor for each stage. Conventional solutions require series resistors, which are controversial as they need to have a very low resistance value for reasons of power dissipation. Yet they can't be too small because this would produce a too small reference signal for feedback. These contradicting design requirements were solved by using the top two FETs as 'senseFETs', in fact current mirrors, that represent the current through the voice coil motor in a ratio of 1:36.

The PHN405 comes in a surface-mount SSOP16 package.

#### Current monitoring using senseFETs

Current sensing is often done by means of an external resistor, which is rather expensive due to its required 1-2% accuracy. Also, sensing of the voltage drop would require two extra IC pins and causes performance loss due to the added power dissipation in the resistor. SenseFETs are a better alternative, effectively eliminating all of these problems at the expense of less than 3% more silicon.

A senseFET is a MOSFET that splits the load current into a power and a sense component. In the PHN405, the current ratio is 36 to 1. It is important to know that this ratio is only valid for the condition where the source (S) and monitor (M) terminals are at the same voltage level. If this is not the case, the accuracy of the ratio will decrease, as is explained below.

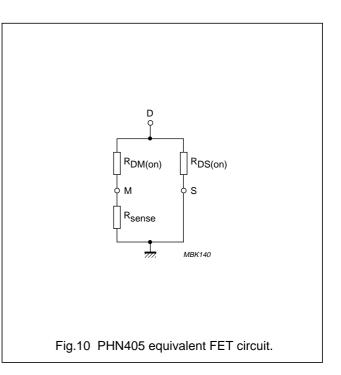

Think of the FET as a voltage-controlled resistor between drain (D) and source (S) respectively monitor (M) terminals. The equivalent resistance model is shown in Fig.10.

The voltage drop across the sense resistor is:

$$V_{\text{sense}} = R_{\text{sense}} \times \frac{I_{\text{D}} \times R_{\text{DS}(\text{on})}}{R_{\text{DM}(\text{on})} + R_{\text{sense}}}$$

If  $R_{sense} \mathrel{\scriptstyle > } R_{DM\,(on)}$  then  $V_{sense} = I_D \times R_{DS\,(on)}$  .

This is the maximum sense voltage that can be obtained.

Applying these formulas to the PHN405:

$$V_{\text{sense max}} = 5 \times 0.05 = 0.25$$

V, and

$$R_{\text{sense max}} = \frac{V_{\text{sense max}}}{I_{\text{sense}}} = \frac{0.25}{5 \div 36} = 1.8 \ \Omega$$

This is the same value as  $R_{DM(on)}$ .

Due to the addition of R<sub>sense</sub>, the current ratio will be:

$$n' = \frac{R_{DM(on)} + R_{sense}}{R_{DS(on)}} \text{ instead of } n = \frac{R_{DM(on)}}{R_{DS(on)}}$$

The values of both  $R_{DM(on)}$  and  $R_{DS(on)}$  are temperature dependent, and because the currents are different, also the temperatures will be different.

The total accuracy of the system depends on the value of  $R_{sense}$ . If  $R_{sense}$  is kept smaller than  $R_{DM(on)}$ , then an overall accuracy of 5% is achieved. However, if direct current sensing is used, meaning that no sense resistor is used, while keeping the M and S pins at the same voltage level, an overall accuracy of 2% is achieved. This can easily be implemented with today's controller ICs using an op-amp to detect the voltage difference. The voltage difference is compensated with a voltage or current source.

#### SIREN DRIVER CIRCUIT FOR CAR ALARMS

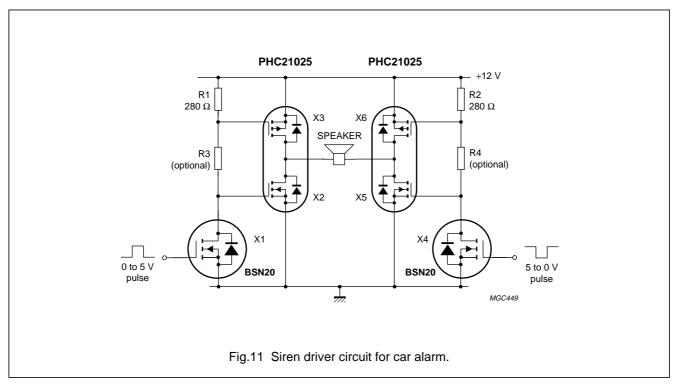

Figure 11 shows a siren driver circuit created with VD-MOS FETs. Power is supplied by a 12 V battery, and the driver inputs are complementary pulse waveforms from a microprocessor.

Chosen for our example are two BSN20 VD-MOS FETs in small SOT23 packages and two PHC21025, each comprising two FETs in one SO8 package. In its minimum configuration the circuit requires six components (excluding the speaker) and its maximum configuration is eight components. All components can be surface mounted.

The two push-pull stages X2/X3 and X5/X6 drive the speaker directly. Either X2 and X6 are conducting or X5 and X3, reversing the current through the speaker. Driver stages X1 and X4 convert the 5 V input swing from the microprocessor to the 12 V switching level.

During microprocessor reset and with no alarm, both driver input pins must have the same potential. (0 or 5 V; 0 V is preferred). With the FETs X1 and X4 not conducting, the gates of FETs X2, X3, X5 and X6 will be high, and X2 and X5 will be conducting, resulting in no current through the speaker. When driver inputs are pulsed (complementary), almost the full 12 V is switched over the speaker (a little less due to the on-resistance of the push-pull FETs 100 m $\Omega$  N-channel and 250 m $\Omega$  P-channel).

### Ideas for design

When designing this siren driver circuit, take the following into account. The BSN20 (X1 and X4) have an input threshold between 0.4 and 1.8 V. The value of the pull-up resistors R1 + R3 and R2 + R4 must be as small as possible (but not less than 280  $\Omega$ ) to achieve the highest possible switching speed, and to guarantee a voltage level at the gates of X2 and X5 less than 0.8 V. R3 and R4 are optional, but may be necessary to reduce high through-current in the push-pull stages. When using these resistors however, the gate voltage at X3 and X6 will not fully reduce to 0.8 V, which can influence the on-resistance of these FETs and consequently the dissipation when conducting. When using R3 and R4, the values of R1 and R2 need to be adjusted to maintain the 280  $\Omega$ .

Concerning the dissipation in the push-pull stage, the on-resistance of the FETs increases by a factor of 1.7 when operating at 150 °C junction temperature. For the P-channel, which dissipates the most, this means that the on-resistance increases to 425 mΩ. If a 4  $\Omega$  speaker is used, the maximum current will be 2.6 A at 12 V. If the pulse is symmetrical and the duty cycle is 50%, the dissipation in the P-channel FET will be 1.45 W. Note that the temperature at the soldering point of the drain pins must not exceed 80 °C.

### PRINTED CIRCUIT BOARD HEATSINK AREA FOR SURFACE- MOUNT PACKAGES

When using surface mount components, it is not as easy to dissipate heat in clip-on or bolt-on heatsinks than with through-hole components. With surface mount components, the conductive tracks or pads on the printed-circuit board are often the only means to transfer heat away from the component.

The amount of heat sink area required for the BSP100 type in a SOT223 package can be calculated as follows. This type has been selected as an example for a design that uses a 100 m $\Omega$ , N-channel VD-MOS-FET with an  $I_{DS}$  of 3 A. The maximum operating junction temperature of this device is 150 °C. At this temperature, the on-resistance of the FET increases with a factor of 1.7 and the power dissipation in continuous use (duty factor 100%) is 1.53 W.

If the ambient temperature is 40 °C, then the total thermal resistance ( $R_{th}$ ) requirement for FET and PCB is: (150 – 40)/1.53 = 72 K/W. The thermal resistance of the FET itself is 10 K/W from junction to the soldering point of the drain tab. Therefore the requirement for  $R_{th}$  of the heatsink is 72 – 10 = 62 K/W.

### Ideas for design

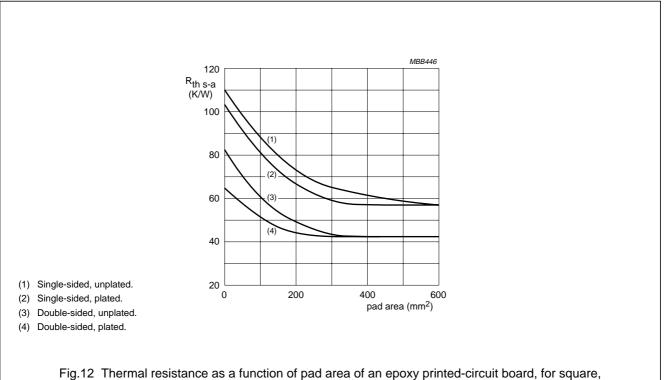

Figure 12 shows typical thermal resistance from soldering point to ambient as a function of area of an epoxy printedcircuit board. The drain tab of the SOT223 is soldered in the centre of one of the sides (as shown in Fig.13). In this example curve (1) shows a single-sided and unplated copper pad area of  $20 \times 20$  mm.

A similar calculation can be applied to the SO8 package. Using the PHN210 as an example, we have two 100 m $\Omega$ , N-channel VD-MOS FETs in one SO8 package. Taking  $I_{DS} = 2$  A per FET and duty factor = 50%, the dissipation per FET is 0.34 W and the total for both FETs is 0.68 W. If the ambient temperature is 60 °C, then the total thermal resistance (R<sub>th</sub>) requirement for FET and PCB is: (150 – 60)/0.68 = 132 K/W. For the SO8 package the R<sub>th</sub> from junction to the soldering point of the drain tab is 35 K/W, so the requirement for the heat sink thermal resistance is 132 – 35 = 97 K/W. Referring again to curve (1) in Fig.12, it can be seen that 50 mm<sup>2</sup> is required.

This example is true for both FETs dissipating equal power. A suggested PCB design is shown in Fig.14. Here the copper is divided into two  $3.5 \times 7$  mm rectangular portions which gives the required total heatsink area and keeps the drain connections separated.

horizontal PCB copper, no airflow.

| Fig.13 PCB heatsink a |  | Fig.14 PCB heat |  |

|-----------------------|--|-----------------|--|

SUNSTAR 商斯达实业集团是集研发、生产、工程、销售、代理经销、技术咨询、信息服务等为一体的高科技企业,是专业高科技电子产品生产厂家,是具有10多年历史的专业电子元器件供应商,是中国最早和最大的仓储式连锁规模经营大型综合电子零部件代理分销商之一,是一家专业代理和分銷世界各大品牌IC芯片和電子元器件的连锁经营综合性国际公司,专业经营进口、国产名厂名牌电子元件,型号、种类齐全。在香港、北京、深圳、上海、西安、成都等全国主要电子市场设有直属分公司和产品展示展销窗口门市部专卖店及代理分销商,已在全国范围内建成强大统一的供货和代理分销网络。我们专业代理经销、开发生产电子元器件、集成电路、传感器、微波光电元器件、工控机/DOC/DOM电子盘、专用电路、单片机开发、MCU/DSP/ARM/FPGA软件硬件、二极管、三极管、模块等,是您可靠的一站式现货配套供应商、方案提供商、部件功能模块开发配套商。商斯达实业公司拥有庞大的资料库,有数位毕业于著名高校——有中国电子工业摇篮之称的西安电子科技大学(西军电)并长期从事国防尖端科技研究的高级工程师为您精挑细选、量身订做各种高科技电子元器件,并解决各种技术问题。

微波光电部专业代理经销高频、微波、光纤、光电元器件、组件、部件、模块、整机;电磁兼容元器件、材料、设备;微波 CAD、EDA 软件、开发测试仿真工具;微波、光纤仪器仪表。 欢迎国外高科技微波、光纤厂商将优秀产品介绍到中国、共同开拓市场。长期大量现货专业批发 高频、微波、卫星、光纤、电视、CATV 器件: 晶振、VCO、连接器、PIN 开关、变容二极管、开 关二极管、低噪晶体管、功率电阻及电容、放大器、功率管、MIIC、混频器、耦合器、功分器、 振荡器、合成器、衰减器、滤波器、隔离器、环行器、移相器、调制解调器;光电子元器件和组 件:红外发射管、红外接收管、光电开关、光敏管、发光二极管和发光二极管组件、半导体激光 二极管和激光器组件、光电探测器和光接收组件、光发射接收模块、光纤激光器和光放大器、光 调制器、光开关、DWDM 用光发射和接收器件、用户接入系统光光收发器件与模块、光纤连接器、 光纤跳线/尾纤、光衰减器、光纤适 配器、光隔离器、光耦合器、光环行器、光复用器/转换器; 无线收发芯片和模组、蓝牙芯片和模组。

更多产品请看本公司产品专用销售网站:

商斯达中国传感器科技信息网: http://www.sensor-ic.com/

商斯达工控安防网: http://www.pc-ps.net/

商斯达电子元器件网: http://www.sunstare.com/

商斯达微波光电产品网:HTTP://www.rfoe.net/

商斯达消费电子产品网://www.icasic.com/

商斯达实业科技产品网://www.sunstars.cn/ 微波元器件销售热线:

地址: 深圳市福田区福华路福庆街鸿图大厦 1602 室

电话: 0755-82884100 83397033 83396822 83398585

传真: 0755-83376182 (0) 13823648918 MSN: SUNS8888@hotmail.com

邮编: 518033 E-mail:szss20@163.com QQ: 195847376

深圳赛格展销部: 深圳华强北路赛格电子市场 2583 号 电话: 0755-83665529 25059422 技术支持: 0755-83394033 13501568376

欢迎索取免费详细资料、设计指南和光盘;产品凡多,未能尽录,欢迎来电查询。

北京分公司:北京海淀区知春路 132 号中发电子大厦 3097 号

TEL: 010-81159046 82615020 13501189838 FAX: 010-62543996 上海分公司: 上海市北京东路 668 号上海賽格电子市场 D125 号

TEL: 021-28311762 56703037 13701955389 FAX: 021-56703037

西安分公司: 西安高新开发区 20 所(中国电子科技集团导航技术研究所) 西安劳动南路 88 号电子商城二楼 D23 号

TEL: 029-81022619 13072977981 FAX:029-88789382