# Regarding the change of names mentioned in the document, such as Mitsubishi Electric and Mitsubishi XX, to Renesas Technology Corp.

The semiconductor operations of Hitachi and Mitsubishi Electric were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Mitsubishi Electric, Mitsubishi Electric Corporation, Mitsubishi Semiconductors, and other Mitsubishi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Note : Mitsubishi Electric will continue the business operations of high frequency & optical devices and power devices.

Renesas Technology Corp. Customer Support Dept. April 1, 2003

# MITSUBISHI 32-BIT SINGLE-CHIP MICROCOMPUTER

# Software Manual

1998-07-01

#### KEEP SAFETY FIRST IN YOUR CIRCUIT DESIGNS ! -

Mitsubishi Electric Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of non-flammable materials or (iii) prevention against any malfunction or mishap.

#### NOTES REGARDING THESE MATERIALS

- These materials are intended as a reference to assist our customers in the selection of the Mitsubishi semiconductor product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Mitsubishi Electric Corporation or a third party.

- Mitsubishi Electric Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts or circuit application examples contained in these materials.

- All information contained in these materials, including product data, diagrams and charts, represent information on products at the time of publication of these materials, and are subject to change by Mitsubishi Electric Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor for the latest product information before purchasing a product listed herein.

- Mitsubishi Electric Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- The prior written approval of Mitsubishi Electric Corporation is necessary to reprint or reproduce in whole or in part these materials.

- If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination. Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

- Please contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor for further details on these materials or the products contained therein.

# **Table of contents**

# CHAPTER 1 CPU PROGRAMMING MODEL

| 1.1 CPU register                                | 1-2  |

|-------------------------------------------------|------|

| 1.2 General-purpose registers                   | 1-2  |

| 1.3 Control registers                           | 1-3  |

| 1.3.1 Processor status word register: PSW (CR0) | 1-4  |

| 1.3.2 Condition bit register: CBR (CR1)         | 1-5  |

| 1.3.3 Interrupt stack pointer: SPI (CR2)        |      |

| User stack pointer: SPU (CR3)                   | 1-5  |

| 1.3.4 Backup PC: BPC (CR6)                      |      |

| 1.4 Accumulator                                 |      |

| 1.5 Program counter                             | 1-6  |

| 1.6 Data format                                 | 1-7  |

| 1.6.1 Data types                                | 1-7  |

| 1.6.2 Data formats                              | 1-8  |

| 1.7 Addressing mode                             | 1-10 |

# **CHAPTER 2 INSTRUCTION SET**

| 2.1 Instruction set overview    |      |

|---------------------------------|------|

| 2.1.1 Load/store instructions   | 2-2  |

| 2.1.2 Transfer instructions     | 2-4  |

| 2.1.3 Operation instructions    | 2-4  |

| 2.1.4 Branch instructions       | 2-6  |

| 2.1.5 EIT-related instructions  | 2-8  |

| 2.1.6 DSP function instructions | 2-8  |

| 2.2 Instruction format          | 2-11 |

### **CHAPTER 3 INSTRUCTIONS**

| 3.1 Conventions for instruction description | 3-2   |

|---------------------------------------------|-------|

| 3.2 Instruction description                 | . 3-5 |

## APPENDICES

| Appendix A Instruction list              | A-2  |

|------------------------------------------|------|

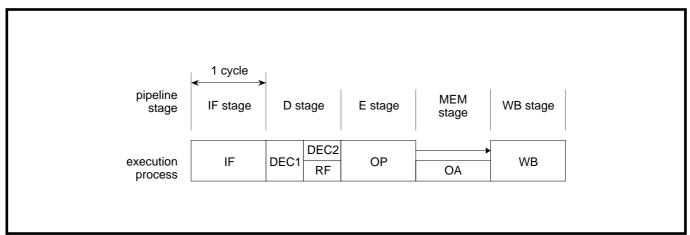

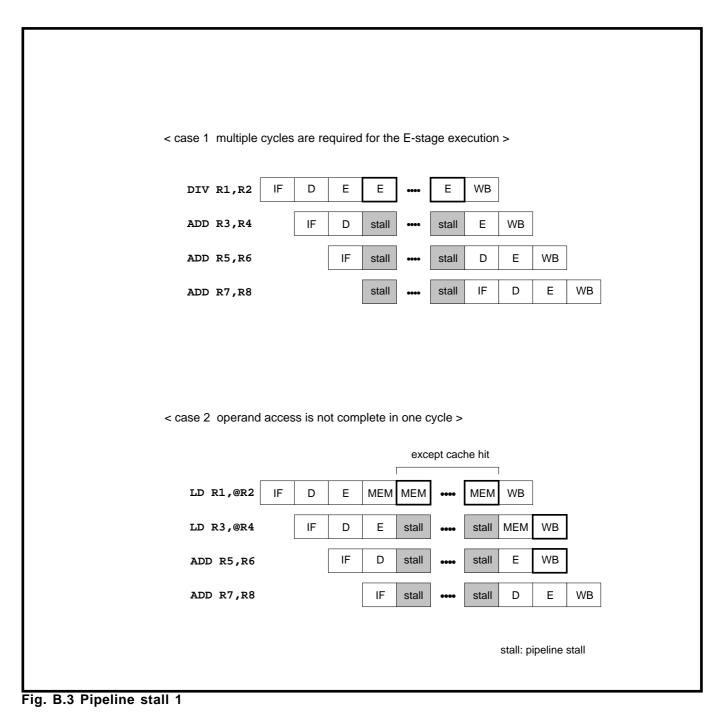

| Appendix B Pipeline stages               |      |

| B.1 Overview of pipeline processing      |      |

| B.2 Instructions and pipeline processing | A-6  |

| B.3 Pipeline processing                  | A-7  |

| Appendix C Instruction execution time    | A-10 |

# CHAPTER 1 CPU PROGRAMMING MODEL

- 1.1 CPU register

- 1.2 General-purpose registers

- 1.3 Control registers

- 1.4 Accumulator

- 1.5 Program counter

- 1.6 Data format

- 1.7 Addressing mode

# 1.1 CPU register

# 1.1 CPU register

The M32R CPU has 16 general-purpose registers, 5 control registers, an accumulator and a program counter. The accumulator is of 64-bit width. The registers and program counter are of 32-bit width.

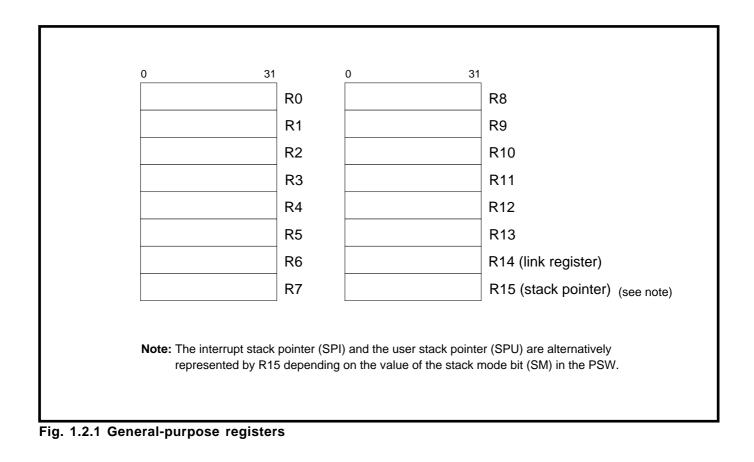

# 1.2 General-purpose registers

The 16 general-purpose registers (R0 - R15) are of 32-bit width and are used to retain data and base addresses. R14 is used as the link register and R15 as the stack pointer (SPI or SPU). The link register is used to store the return address when executing a subroutine call instruction. The interrupt stack pointer (SPI) and the user stack pointer (SPU) are alternately represented by R15 depending on the value of the stack mode bit (SM) in the processor status word register (PSW).

# **1.3 Control registers**

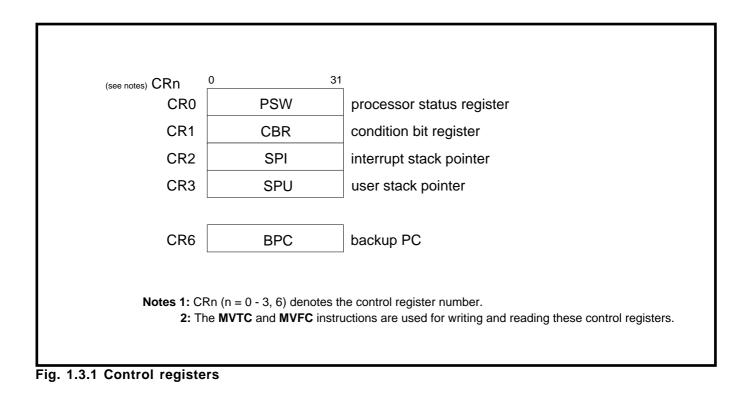

There are 5 control registers which are the processor status word register (PSW), the condition bit register (CBR), the interrupt stack pointer (SPI), the user stack pointer (SPU) and the backup PC (BPC). The **MVTC** and **MVFC** instructions are used for writing and reading these control registers.

# **1.3 Control registers**

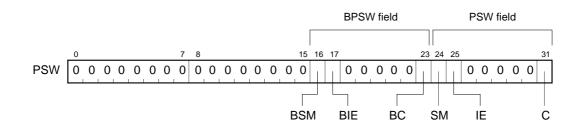

### 1.3.1 Processor status word register: PSW (CR0)

The processor status word register (PSW) shows the M32R CPU status. It consists of the current PSW field, and the BPSW field where a copy of the PSW field is saved when EIT occurs.

The PSW field is made up of the stack mode bit (SM), the interrupt enable bit (IE) and the condition bit (C).

The BPSW field is made up of the backup stack mode bit (BSM), the backup interrupt enable bit (BIE) and the backup condition bit (BC) .

| D  | bit name              | function                                                                               | init.     | R | W |

|----|-----------------------|----------------------------------------------------------------------------------------|-----------|---|---|

| 16 | BSM (backup SM)       | saves value of SM bit when EIT occurs                                                  | undefined | 0 | 0 |

| 17 | BIE (backup IE)       | saves value of IE bit when EIT occurs                                                  | undefined | 0 | 0 |

| 23 | BC (backup C)         | saves value of C bit when EIT occurs                                                   | undefined | 0 | 0 |

| 24 | SM (stack mode)       | 0: uses R15 as the interrupt stack pointer<br>1: uses R15 as the user stack pointer    | 0         | 0 | 0 |

| 25 | IE (interrupt enable) | 0: does not accept interrupt<br>1: accepts interrupt                                   | 0         | 0 | 0 |

| 31 | C (condition bit)     | indicates carry, borrow and overflow resulting from operations (instruction dependent) | 0         | 0 | 0 |

Note: "init." ...initial state immediately after reset

"R"...  $\bigcirc$  : read enabled

"W"...  $\bigcirc$  : write enabled

### **1.3 Control registers**

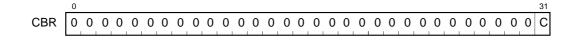

#### 1.3.2 Condition bit register: CBR (CR1)

The condition bit register (CBR) is a separate register which contains the condition bit (C) in the PSW. The value of the condition bit (C) in the PSW is reflected in this register. This register is read-only. An attempt to write to the CBR with the **MVTC** instruction is ignored.

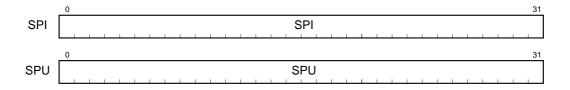

#### 1.3.3 Interrupt stack pointer: SPI (CR2) User stack pointer: SPU (CR3)

The interrupt stack pointer (SPI) and the user stack pointer (SPU) retain the current stack address. The SPI and SPU can be accessed as the general-purpose register R15. R15 switches between representing the SPI and SPU depending on the value of the stack mode bit (SM) in the PSW.

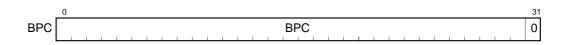

#### 1.3.4 Backup PC: BPC (CR6)

The backup PC (BPC) is the register where a copy of the PC value is saved when EIT occurs. Bit 31 is fixed at "0". When EIT occurs, the PC value immediately before EIT occurrence or that of the next instruction is set. The value of the BPC is reloaded to the PC when the **RTE** instruction is executed. However, the values of the lower 2 bits of the PC become "00" on returning (It always returns to the word boundary).

# 1.4 Accumulator

# 1.4 Accumulator

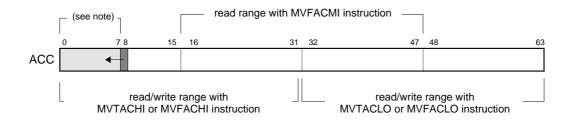

The accumulator (ACC) is a 64-bit register used for the DSP function.

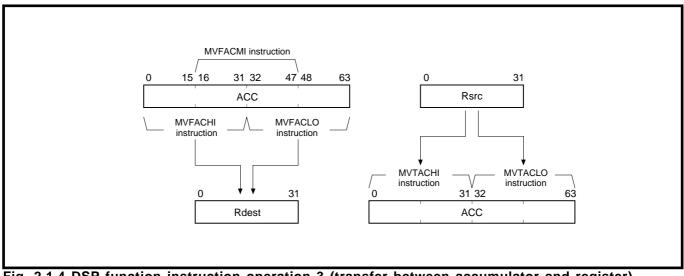

Use the **MVTACHI** and **MVTACLO** instructions for writing to the accumulator. The high-order 32 bits (bit 0 - bit 31) can be set with the **MVTACHI** instruction and the low-order 32 bits (bit 32 - bit 63) can be set with the **MVTACLO** instruction. Use the **MVFACHI**, **MVFACLO** and **MVFACMI** instructions for reading from the accumulator. The high-order 32 bits (bit 0 - bit 31) are read with the **MVFACHI** instruction, the low order 32 bits (bit 32 - bit 63) with the **MVFACLO** instruction and the middle 32 bits (bit 16 - bit 47) with the **MVFACMI** instruction.

The **MUL** instruction also uses the accumulator and the contents are destroyed when this instruction is executed.

**Note:** Bits 0 - 7 are always read as the sign-extended value of bit 8. An attempt to write to this area is ignored.

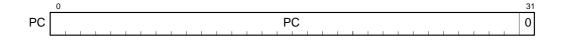

# 1.5 Program counter

The program counter (PC) is a 32-bit counter that retains the address of the instruction being executed. Since the M32R CPU instruction starts with even-numbered addresses, the LSB (bit 31) is always "0".

# **1.6 Data format**

#### 1.6.1 Data types

Signed and unsigned integers of byte (8 bits), halfword (16 bits), and word (32 bits) types are supported as data in the M32R CPU instruction set. A signed integer is represented in a 2's complement format.

| signed byte (8-bit) integer        | 0 7<br>S    |

|------------------------------------|-------------|

| unsigned byte (8-bit) integer      | 0 7         |

| signed halfword (16-bit) integer   | 0 15<br>S   |

| unsigned halfword (16-bit) integer | 0 15        |

| signed word (32-bit) integer       | 0 31<br>S   |

| unsigned word (32-bit) integer     | 0 31        |

|                                    | S: sign bit |

|                                    |             |

Fig. 1.6.1 Data types

# 1.6 Data format

### 1.6.2 Data formats

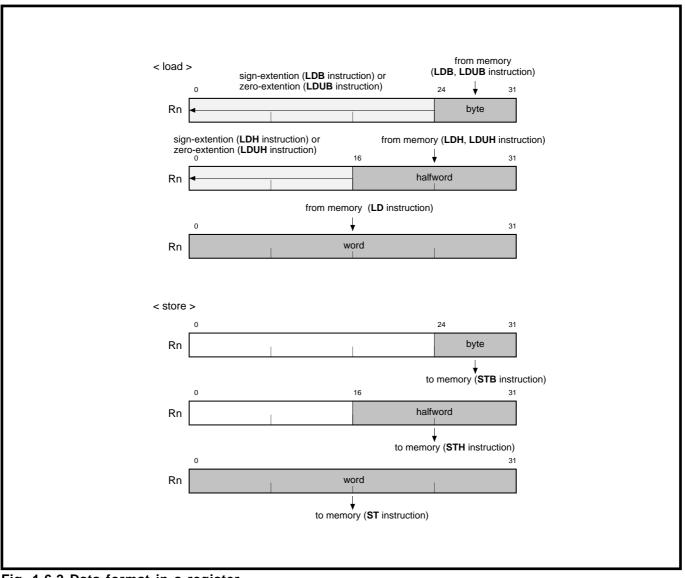

### (1) Data format in a register

Data size of a register is always a word (32 bits).

Byte (8 bits) and halfword (16 bits) data in memory are sign-extended (the LDB and LDH instructions) or zero-extended (the LDUB and LDUH instructions) to 32 bits, and loaded into the register. Word (32 bits) data in a register is stored to memory by the ST instruction. Halfword (16 bits) data in the LSB side of a register is stored to memory by the STH instruction. Byte (8 bits) data in the LSB side of a register is stored to memory by the STB instruction.

Fig. 1.6.2 Data format in a register

### 1.6 Data format

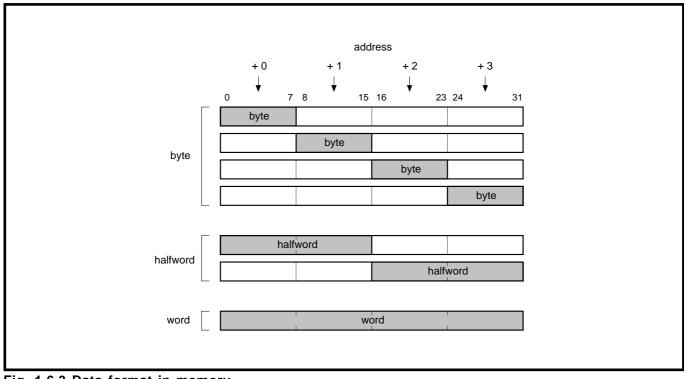

#### (2) Data format in memory

Data stored in memory can be one of these types: byte (8 bits), halfword (16 bits) or word (32 bits). Although the byte data can be located at any address, the halfword data and the word data can only be located on the halfword boundary and the word boundary, respectively. If an attempt is made to access data in memory which is not located on the correct boundary, an address exception occurs.

Fig. 1.6.3 Data format in memory

# 1.7 Addressing mode

# **1.7 Addressing mode**

M32R supports the following addressing modes.

### (1) Register direct [R or CR]

The general-purpose register or the control register to be processed is specified.

### (2) Register indirect [@R]

The contents of the register specify the address of the memory. This mode can be used by all load/store instructions.

### (3) Register relative indirect [@(disp, R)]

(The contents of the register) + (16-bit immediate value which is sign-extended to 32 bits) specify the address of the memory.

### (4) Register indirect and register update

- 4 is added to the register contents [@R+] the contents of the register before update specify address of memory (can be specified with LD instruction).

- 4 is added to the register contents [@+R] the contents of the register after update specify address of memory (can be specified with ST instruction).

- 4 is subtracted from the register contents [@-R] the contents of the register after update specify address of memory (can be specified with ST instruction).

### (5) immediate [#imm]

The 4-, 5-, 8-, 16- or 24-bit immediate value.

### (6) PC relative [pcdisp]

(The contents of PC) + (8, 16, or 24-bit displacement which is sign-extended to 32 bits and 2 bits left-shifted) specify the address of memory.

# CHAPTER 2 INSTRUCTION SET

2.1 Instruction set overview2.2 Instruction format

# 2.1 Instruction set overview

## 2.1 Instruction set overview

The M32R CPU has a RISC architecture. Memory is accessed by using the load/store instructions and other operations are executed by using register-to-register operation instructions. A total of 83 instructions are implemented.

M32R supports compound instructions such as " load & address update" and "store & address update" which are useful for high-speed data transfer.

The M32R instruction set overview is explained below.

#### 2.1.1 Load/store instructions

The load/store instructions carry out data transfers between a register and a memory.

| LD     | Load                   |

|--------|------------------------|

| LDB    | Load byte              |

| LDUB   | Load unsigned byte     |

| LDH    | Load halfword          |

| LDUH   | Load unsigned halfword |

| LOCK   | Load locked            |

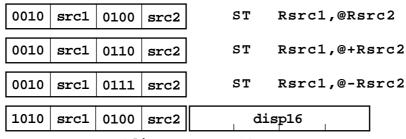

| ST     | Store                  |

| STB    | Store byte             |

| STH    | Store halfword         |

| UNLOCK | Store unlocked         |

Three types of addressing modes can be specified for load/store instructions.

#### (1) Register indirect

The contents of the register specify the address. This mode can be used by all load/store instructions.

### (2) Register relative indirect

(The contents of the register) + (32-bit sign-extended 16-bit immediate value) specifies the address. This mode can be used by all except **LOCK** and **UNLOCK** instructions.

### (3) Register indirect and register update

- 4 is added to the register value

- the value in the register before update specifies the address (can be specified only with the **LD** instruction).

- 4 is added to the register value

- the value in the register after update specifies address (can be specified only with the **ST** instruction).

- 4 is subtracted to the register value

- the value in the register after update specifies address (can be specified only with the **ST** instruction).

When accessing halfword and word size data, it is necessary to specify the address on the halfword boundary or the word boundary (Halfword size should be such that the low-order 2 bits of the address are "00" or "10", and word size should be such that the low order 2 bits of the address are "00"). If an unaligned address is specified, an address exception occurs.

When accessing byte data or halfword data with load instructions, the high-order bits are sign-extended or zero-extended to 32 bits, and loaded to a register.

# 2.1 Instruction set overview

### 2.1.2 Transfer instructions

The transfer instructions carry out data transfers between registers or a register and an immediate value.

| LD24 | Load 24-bit immediate      |

|------|----------------------------|

| LDI  | Load immediate             |

| MV   | Move register              |

| MVFC | Move from control register |

| MVTC | Move to control register   |

| SETH | Set high-order 16-bit      |

#### 2.1.3 Operation instructions

Compare, arithmetic/logic operation, multiply and divide, and shift are carried out between registers.

• compare instructions

| СМР   | Compare                    |

|-------|----------------------------|

| СМРІ  | Compare immediate          |

| CMPU  | Compare unsigned           |

| CMPUI | Compare unsigned immediate |

• arithmetic operation instructions

| ADD   | Add                                  |

|-------|--------------------------------------|

| ADD3  | Add 3-operand                        |

| ADDI  | Add immediate                        |

| ADDV  | Add with overflow checking           |

| ADDV3 | Add 3-operand with overflow checking |

| ADDX  | Add with carry                       |

| NEG   | Negate                               |

| SUB   | Subtract                             |

| SUBV  | Subtract with overflow checking      |

| SUBX  | Subtract with borrow                 |

# 2.1 Instruction set overview

• logic operation instructions

| AND  | AND                    |

|------|------------------------|

| AND3 | AND 3-operand          |

| ΝΟΤ  | Logical NOT            |

| OR   | OR                     |

| OR3  | OR 3-operand           |

| XOR  | Exclusive OR           |

| XOR3 | Exclusive OR 3-operand |

|      |                        |

• multiply/divide instructions

| Divide             |

|--------------------|

| Divide unsigned    |

| Multiply           |

| Remainder          |

| Remainder unsigned |

|                    |

shift instructions

| SLL  | Shift left logical               |

|------|----------------------------------|

| SLL3 | Shift left logical 3-operand     |

| SLLI | Shift left logical immediate     |

| SRA  | Shift right arithmetic           |

| SRA3 | Shift right arithmetic 3-operand |

| SRAI | Shift right arithmetic immediate |

| SRL  | Shift right logical              |

| SRL3 | Shift right logical 3-operand    |

| SRLI | Shift right logical immediate    |

# 2.1 Instruction set overview

### 2.1.4 Branch instructions

The branch instructions are used to change the program flow.

| BC   | Branch on C-bit                      |

|------|--------------------------------------|

| BEQ  | Branch on equal                      |

| BEQZ | Branch on equal zero                 |

| BGEZ | Branch on greater than or equal zero |

| BGTZ | Branch on greater than zero          |

| BL   | Branch and link                      |

| BLEZ | Branch on less than or equal zero    |

| BLTZ | Branch on less than zero             |

| BNC  | Branch on not C-bit                  |

| BNE  | Branch on not equal                  |

| BNEZ | Branch on not equal zero             |

| BRA  | Branch                               |

| JL   | Jump and link                        |

| JMP  | Jump                                 |

| NOP  | No operation                         |

Only a word-aligned (word boundary) address can be specified for the branch address.

### 2.1 Instruction set overview

The addressing mode of the **BRA**, **BL**, **BC** and **BNC** instructions can specify an 8-bit or 24-bit immediate value. The addressing mode of the **BEQ**, **BNE**, **BEQZ**, **BNEZ**, **BLEZ**, **BLEZ**, and **BGTZ** instructions can specify a 16-bit immediate value.

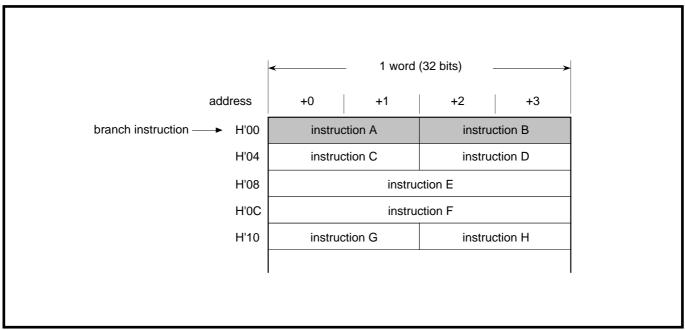

In the **JMP** and **JL** instructions, the register value becomes the branch address. However, the low-order 2-bit value of the register is ignored. In other branch instructions, (PC value of branch instruction) + (sign-extended and 2 bits left-shifted immediate value) becomes the branch address. However, the low order 2-bit value of the address becomes "00" when addition is carried out. For example, refer to Figure 2.1.1. When instruction A or B is a branch instruction, branching to instruction G, the immediate value of either instruction A or B becomes 4.

Simultaneous with execution of branching by the **JL** or **BL** instructions for subroutine calls, the PC value of the return address is stored in R14. The low-order 2-bit value of the address stored in R14 (PC value of the branch instruction + 4) is always cleared to "0". For example, refer to Figure 2.1.1. If an instruction A or B is a **JL** or **BL** instruction, the return address becomes that of the instruction C.

Fig. 2.1.1 Branch addresses of branch instruction

## 2.1 Instruction set overview

### 2.1.5 EIT-related instructions

The EIT-related instructions carry out the EIT events (Exception, Interrupt and Trap). Trap initiation and return from EIT are EIT-related instructions.

| TRAP | Trap            |

|------|-----------------|

| RTE  | Return from EIT |

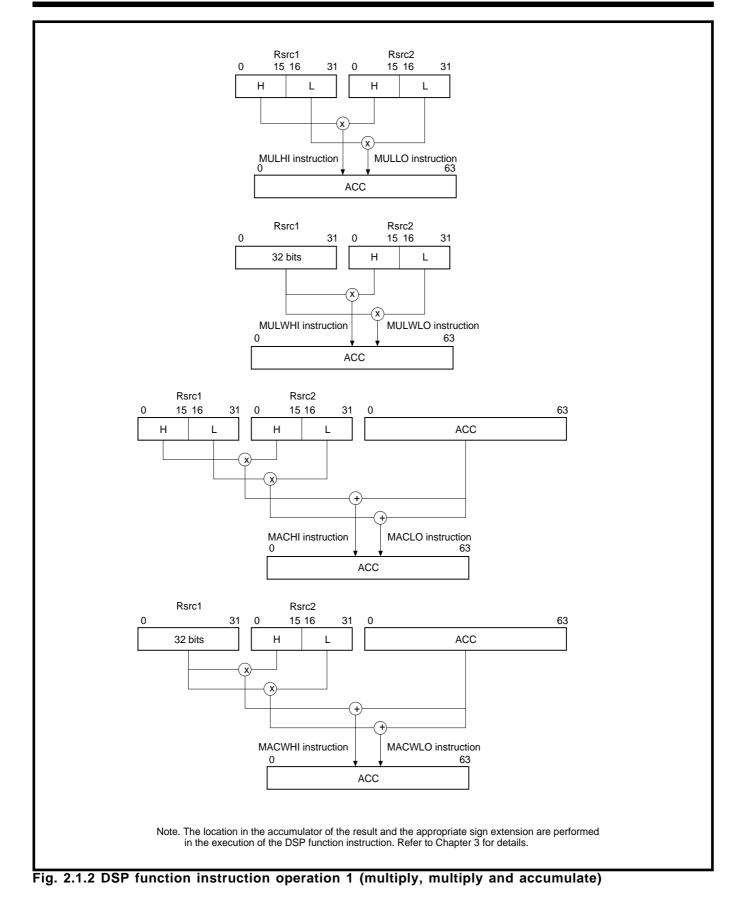

#### 2.1.6 DSP function instructions

The DSP function instructions carry out multiplication of 32 bits x 16 bits and 16 bits x 16 bits or multiply and add operation; there are also instructions to round off data in the accumulator and carry out transfer of data between the accumulator and a general-purpose register.

| MACHI   | Multiply-accumulate high-order halfwords         |

|---------|--------------------------------------------------|

| MACLO   | Multiply-accumulate low-order halfwords          |

| MACWHI  | Multiply-accumulate word and high-order halfword |

| MACWLO  | Multiply-accumulate word and low-order halfword  |

| MULHI   | Multiply high-order halfwords                    |

| MULLO   | Multiply low-order halfwords                     |

| MULWHI  | Multiply word and high-order halfword            |

| MULWLO  | Multiply word and low-order halfword             |

| MVFACHI | Move from accumulator high-order word            |

| MVFACLO | Move from accumulator low-order word             |

| MVFACMI | Move from accumulator middle-order word          |

| MVTACHI | Move to accumulator high-order word              |

| MVTACLO | Move to accumulator low-order word               |

| RAC     | Round accumulator                                |

| RACH    | Round accumulator halfword                       |

|         |                                                  |

### 2.1 Instruction set overview

# 2.1 Instruction set overview

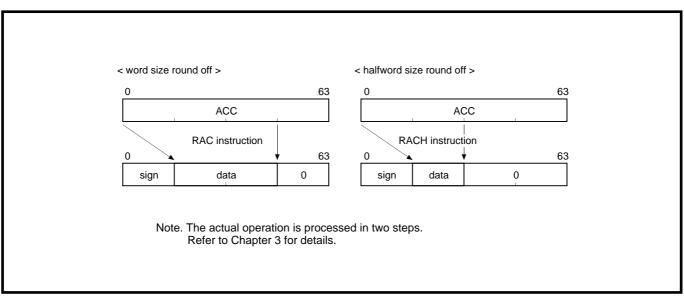

Fig. 2.1.3 DSP function instruction operation 2 (round off)

Fig. 2.1.4 DSP function instruction operation 3 (transfer between accumulator and register)

# 2.2 Instruction format

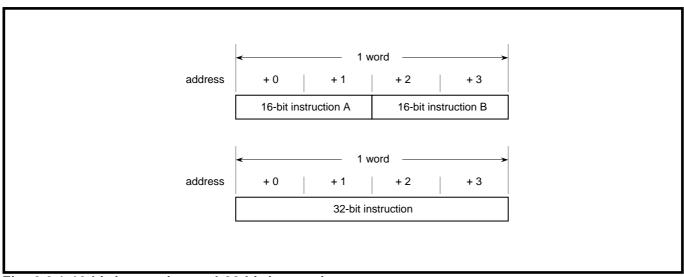

There are two major instruction formats: two 16-bit instructions packed together within a word boundary, and a single 32-bit instruction (see Fig. 2.2.1). Figure 2.2.2 shows the instruction format of M32R family.

Fig. 2.2.1 16-bit instruction and 32-bit instruction

| < 16-b                    | oit instructio | n > |          |                         |                           |

|---------------------------|----------------|-----|----------|-------------------------|---------------------------|

| 0                         | pp1 R1         | op2 | R2       | $R_1 = R_1$ op $R_2$    |                           |

| 0                         | pp1 R1         | (   | ;        | $R_1 = R_1$ op c        |                           |

| o                         | op1 cond       | 0   | ;        | Branch (Short Displacen | nent)                     |

| < 32-b                    | oit instructio | n > |          |                         |                           |

| 0                         | p1 R1          | op2 | R2       | С                       | $R_1 = R_2  \text{op}  c$ |

| o                         | pp1 R1         | op2 | R2       | С                       | Compare and Branch        |

| 0                         | p1 R1          |     |          | С                       | R1 = R1 op c              |

| 0                         | op1 cond       |     |          | c                       | Branch                    |

| Fig. 2.2.2 Instruction fo |                |     | <u> </u> |                         |                           |

# 2.2 Instruction format

The MSB (Most Significant Bit) of a 32-bit instruction is always "1".

The MSB of a 16-bit instruction in the high-order halfword is always "0" (instruction A in Figure 2.2.3), however the processing of the following 16-bit instruction depends on the MSB of the instruction. In Figure 2.2.3, if the MSB of the instruction B is "0", instructions A and B are executed sequentially; B is executed after A. If the MSB of the instruction B is "1", instructions A and B are executed in parallel. The current implementation allows only the NOP instruction as instruction B for parallel execution. The MSB of the NOP instruction used for word arraignment adjustment is changed to "1" automatically by a standard Mitsubishi assembler, then the M32R can execute this instruction without requiring any clock cycles.

| MSB                           | Ν                                  | MSB<br>↓               | < instruction execution sequence >          |

|-------------------------------|------------------------------------|------------------------|---------------------------------------------|

| 0                             | 16-bit instruction A               | 0 16-bit instruction B | [instruction A]> [instruction B] sequential |

| 0                             | 16-bit instruction A               | 1 16-bit instruction B | [instruction A] & [instruction B] parallel  |

| 1                             | 32-bit ins                         | truction               |                                             |

| 0<br>1<br>Fig. 2.2.3 Processi | 16-bit instruction A<br>32-bit ins |                        | 0111 0000 0000 0000                         |

Instructions

# CHAPTER 3 INSTRUCTIONS

3.1 Conventions for instruction description3.2 Instruction description

# 3.1 Conventions for instruction description

# 3.1 Conventions for instruction description

Conventions for instruction description are summarized below.

# [Mnemonic]

Shows the mnemonic and possible operands (operation target) using assembly language notation.

| Table 3.1.1 Ope      | rand list                             |                                                                                                                                          |

|----------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| symbol<br>(see note) | addressing mode                       | operation target                                                                                                                         |

| R                    | register direct                       | general-purpose registers (R0 - R15)                                                                                                     |

| CR                   | control register                      | control registers (CR0 = PSW, CR1 = CBR, CR2 = SPI,<br>CR3 = SPU, CR6 = BPC)                                                             |

| @R                   | register indirect                     | memory specified by register contents as address                                                                                         |

| @(disp, R)           | register relative indirect            | memory specified by (register contents) + (sign-extended value of 16-bit displacement) as address                                        |

| @R+                  | register indirect and register update | 4 is added to register contents (memory specified by register contents before update as address)                                         |

| @+R                  | register indirect and register update | 4 is added to register contents (memory specified by register contents after update as address)                                          |

| @-R                  | register indirect and register update | 4 is subtracted from register contents (memory specified by register contents after update as address)                                   |

| #imm                 | immediate                             | immediate value (refer to each instruction description)                                                                                  |

| pcdisp               | PC relative                           | memory specified by (PC contents) + (8, 16, or 24-bit displacement which is sign-extended to 32 bits and 2 bits left-shifted) as address |

Note. When expressing Rsrc or Rdest as an operand, a general-purpose register numbers (0 - 15) should be substituted for src or dest. When expressing CRsrc or CRdest, control register numbers (0 - 3, 6) should be substituted for src or dest.

## [Function]

Indicates the operation performed by one instruction. Notation is in accordance with C language notation.

| Table 3.1.2 | Operation | expression | (operator) |

|-------------|-----------|------------|------------|

|-------------|-----------|------------|------------|

| operato | r meaning                          |

|---------|------------------------------------|

| +       | addition (binomial operator)       |

| _       | subtraction (binomial operator)    |

| *       | multiplication (binomial operator) |

|         |                                    |

# 3.1 Conventions for instruction description

| operator | meaning                                                                                        |

|----------|------------------------------------------------------------------------------------------------|

| /        | division (binomial operator)                                                                   |

| %        | remainder operation (binomial operator)                                                        |

| ++       | increment (monomial operator)                                                                  |

|          | decrement (monomial operator)                                                                  |

| _        | sign invert (monomial operator)                                                                |

| =        | substitute right side into left side (substitute operator)                                     |

| +=       | adds right and left variables and substitute into left side (substitute operator)              |

| -=       | subtract right variable from left variable and substitute into left side (substitute operator) |

| >        | greater than (relational operator)                                                             |

| <        | less than (relational operator)                                                                |

| >=       | greater than or equal to (relational operator)                                                 |

| <=       | less than or equal to (relational operator)                                                    |

| ==       | equal (relational operator)                                                                    |

| !=       | not equal (relational operator)                                                                |

| &&       | AND (logical operator)                                                                         |

|          | OR (logical operator)                                                                          |

| !        | NOT (logical operator)                                                                         |

| ?:       | execute a conditional expression (conditional operator)                                        |

## Table 3.1.3 Operation expression (operator) (cont.)

#### Table 3.1.4 Operation expression (bit operator)

| operator | meaning                 |

|----------|-------------------------|

| <<       | bits are left-shifted   |

| >>       | bits are right-shifted  |

| &        | bit product (AND)       |

|          | bit sum (OR)            |

| ٨        | bit exclusive or (EXOR) |

| ~        | bit invert              |

### Table 3.1.5 Data type

| expression     | type    | sign | bit length | range                                    |

|----------------|---------|------|------------|------------------------------------------|

| char           | integer | yes  | 8          | -128 to +127                             |

| short          | integer | yes  | 16         | -32,768 to +32,767                       |

| int            | integer | yes  | 32         | -2,147,483,648 to +2,147,483,647         |

| unsigned char  | integer | no   | 8          | 0 to 255                                 |

| unsigned short | integer | no   | 16         | 0 to 655,535                             |

| unsigned int   | integer | no   | 32         | 0 to 4,294,967,295                       |

| signed64bit    | integer | yes  | 64         | signed 64-bit integer (with accumulator) |

## 3.1 Conventions for instruction description

### [Description]

Describes the operation performed by the instruction and any condition bit change.

#### [EIT occurrence]

Shows possible EIT events (Exception, Interrupt, Trap) which may occur as the result of the instruction's execution. Only address exception (AE) and trap (TRAP) may result from an instruction execution.

#### [Instruction format]

Shows the bit level instruction pattern (16 bits or 32 bits). Source and/or destination register numbers are put in the src and dest fields as appropriate. Any immediate or displacement value is put in the imm or disp field, its maximum size being determined by the width of the field provided for the particular instruction. Refer to 2.2 Instruction format for detail.

## 3.2 Instruction description

# 3.2 Instruction description

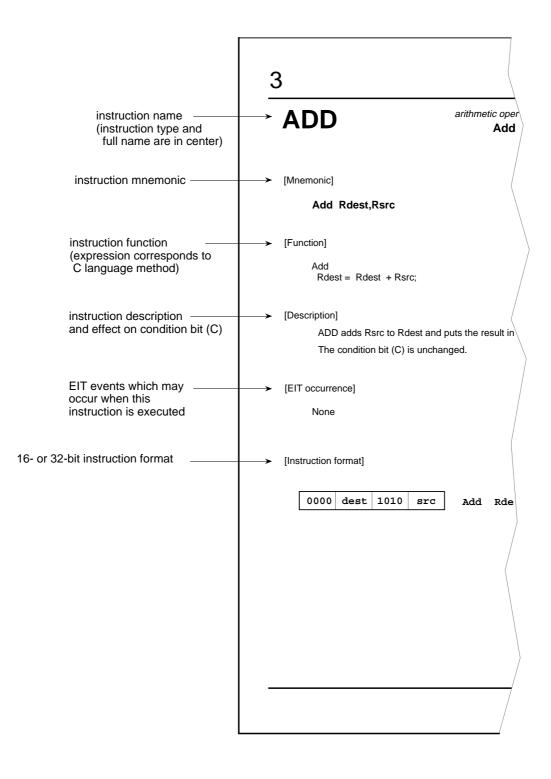

This section lists M32R family instructions in alphabetical order. Each page is laid out as shown below.

# 3.2 Instruction description

# ADD

arithmetic/logic operation Add

# ADD

### [Mnemonic]

ADD Rdest,Rsrc

### [Function]

Add

Rdest = Rdest + Rsrc;

### [Description]

ADD adds Rsrc to Rdest and puts the result in Rdest. The condition bit (C) is unchanged.

### [EIT occurrence]

None

### [Encoding]

0000 dest 1010 src

ADD Rdest,Rsrc

3.2 Instruction description

arithmetic operation instruction Add 3-operand

### [Mnemonic]

ADD3 Rdest,Rsrc,#imm16

### [Function]

Add

Rdest = Rsrc + ( signed short ) imm16;

#### [Description]

ADD3 adds the 16-bit immediate value to Rsrc and puts the result in Rdest. The immediate value is sign-extended to 32 bits before the operation. The condition bit (C) is unchanged.

#### [EIT occurrence]

None

### [Encoding]

| 1000 | dest | 1010 | src | imm16 |

|------|------|------|-----|-------|

|------|------|------|-----|-------|

ADD3 Rdest,Rsrc,#imm16

# 3.2 Instruction description

arithmetic operation instruction Add immediate

# ADDI

### [Mnemonic]

ADDI Rdest,#imm8

### [Function]

Add

Rdest = Rdest + ( signed char ) imm8;

### [Description]

ADDI adds the 8-bit immediate value to Rdest and puts the result in Rdest. The immediate value is sign-extended to 32 bits before the operation. The condition bit (C) is unchanged.

### [EIT occurrence]

None

### [Encoding]

0100 dest imm8

ADDI Rdest,#imm8

3.2 Instruction description

arithmetic operation instruction Add with overflow checking

### [Mnemonic]

ADDV

Rdest,Rsrc

### [Function]

Add

Rdest = ( signed ) Rdest + ( signed ) Rsrc; C = overflow ? 1 : 0;

#### [Description]

ADDV adds Rsrc to Rdest and puts the result in Rdest. The condition bit (C) is set when the addition results in overflow; otherwise it is cleared.

#### [EIT occurrence]

None

#### [Encoding]

0000 dest 1000 src

ADDV Rdest,Rsrc

# 3.2 Instruction description

arithmetic operation instruction ADDV3 Add 3-operand with overflow checking ADDV3

### [Mnemonic]

ADDV3 Rdest,Rsrc,#imm16

### [Function]

#### Add

```

Rdest = ( signed ) Rsrc + ( signed ) ( ( signed short ) imm16 );

C = overflow ? 1 : 0;

```

#### [Description]

ADDV3 adds the 16-bit immediate value to Rsrc and puts the result in Rdest. The immediate value is sign-extended to 32 bits before it is added to Rsrc.

The condition bit (C) is set when the addition results in overflow; otherwise it is cleared.

#### [EIT occurrence]

None

#### [Encoding]

| 1000 | dest | 1000 | src | imm16 |

|------|------|------|-----|-------|

|------|------|------|-----|-------|

ADDV3 Rdest,Rsrc,#imm16

3.2 Instruction description

arithmetic operation instruction Add with carry

### [Mnemonic]

ADDX Rdest,Rsrc

### [Function]

Add

```

Rdest = ( unsigned ) Rdest + ( unsigned ) Rsrc + C;

C = carry_out ? 1 : 0;

```

### [Description]

ADDX adds Rsrc and C to Rdest, and puts the result in Rdest. The condition bit (C) is set when the addition result cannot be represented by a 32-bit unsigned integer; otherwise it is cleared.

#### [EIT occurrence]

None

### [Encoding]

0000 dest 1001 src

ADDX Rdest,Rsrc

### 3.2 Instruction description

logic operation instruction AND

### [Mnemonic]

AND Rdest,Rsrc

### [Function]

Logical AND Rdest = Rdest & Rsrc;

### [Description]

AND computes the logical AND of the corresponding bits of Rdest and Rsrc and puts the result in Rdest.

The condition bit (C) is unchanged.

### [EIT occurrence]

None

### [Encoding]

0000 dest 1100 src

AND Rdest,Rsrc

3.2 Instruction description

logic operation instruction AND 3-operand

### [Mnemonic]

AND3 Rdest,Rsrc,#imm16

### [Function]

Logical AND Rdest = Rsrc & ( unsigned short ) imm16;

#### [Description]

AND3 computes the logical AND of the corresponding bits of Rsrc and the 16-bit immediate value, which is zero-extended to 32 bits, and puts the result in Rdest. The condition bit (C) is unchanged.

### [EIT occurrence]

None

#### [Encoding]

| 1000 dest | 1100 | src | imm16 |

|-----------|------|-----|-------|

|-----------|------|-----|-------|

AND3 Rdest,Rsrc,#imm16

### 3.2 Instruction description

## BC

*branch instruction* Branch on C-bit

## BC

### [Mnemonic]

| 1 | BC | pcdisp8  |

|---|----|----------|

| 2 | BC | pcdisp24 |

### [Function]

Branch

```

① if ( C==1 ) PC = ( PC & 0xffffffc ) + ( ( ( signed char ) pcdisp8 ) << 2 );

② if ( C==1 ) PC = ( PC & 0xfffffffc ) + ( sign_extend ( pcdisp24 ) << 2 );

where

#define sign_extend(x) ( ( ( signed ) ( (x)<< 8 ) ) >>8 )

```

### [Description]

BC causes a branch to the specified label when the condition bit (C) is 1. There are two instruction formats; which allows software, such as an assembler, to decide on the better format.

The condition bit (C) is unchanged.

### [EIT occurrence]

None

| 0111 | 1100 | pcdisp8 | вс       | pcdisp8 |    |          |

|------|------|---------|----------|---------|----|----------|

| 1111 | 1100 |         | pcdisp24 |         | BC | pcdisp24 |

3.2 Instruction description

branch instruction Branch on equal

### [Mnemonic]

BEQ Rsrc1,Rsrc2,pcdisp16

### [Function]

Branch

if (Rsrc1 == Rsrc2) PC = (PC & 0xfffffffc) + (((signed short) pcdisp16) << 2);

### [Description]

BEQ causes a branch to the specified label when Rsrc1 is equal to Rsrc2. The condition bit (C) is unchanged.

#### [EIT occurrence]

None

### [Encoding]

| 1011 | src1 | 0000 | src2 | pcdisp16 |

|------|------|------|------|----------|

|      |      |      |      |          |

BEQ Rsrc1,Rsrc2,pcdisp16

### 3.2 Instruction description

BEQZ

*branch instruction* Branch on equal zero

### [Mnemonic]

BEQZ Rsrc,pcdisp16

### [Function]

Branch

if (Rsrc == 0) PC = (PC & 0xffffffc) + (( (signed short ) pcdisp16) << 2);

### [Description]

BEQZ causes a branch to the specified label when Rsrc is equal to zero. The condition bit (C) is unchanged.

### [EIT occurrence]

None

### [Encoding]

| 1011 | 0000 | 1000 | src   | pcdisp16 |

|------|------|------|-------|----------|

|      | Dar  |      | dian1 | 6        |

BEQZ Rsrc,pcdisp16

3.2 Instruction description

**BGEZ** Branch on greater than or equal zero

### [Mnemonic]

BGEZ Rsrc,pcdisp16

### [Function]

Branch

if ( (signed) Rsrc >= 0 ) PC = ( PC & 0xffffffc ) + ( ( ( signed short ) pcdisp16 ) << 2);

### [Description]

BGEZ causes a branch to the specified label when Rsrc treated as a signed 32-bit value is greater than or equal to zero. The condition bit (C) is unchanged.

#### [EIT occurrence]

None

#### [Encoding]

| 1011 0000 1011 src | pcdisp16 |

|--------------------|----------|

|--------------------|----------|

BGEZ Rsrc,pcdisp16

### 3.2 Instruction description

branch instruction Branch on greater than zero

### [Mnemonic]

BGTZ Rsrc,pcdisp16

### [Function]

Branch

if ((signed) Rsrc > 0) PC = (PC & 0xffffffc) + ( ( (signed short) pcdisp16 ) << 2);

### [Description]

BGTZ causes a branch to the specified label when Rsrc treated as a signed 32-bit value is greater than zero. The condition bit (C) is unchanged.

### [EIT occurrence]

None

### [Encoding]

| 1011 0000 1101 src | pcdisp16 |

|--------------------|----------|

|--------------------|----------|

BGTZ Rsrc,pcdisp16

3.2 Instruction description

## BL

*branch instruction* Branch and link

### [Mnemonic]

| 1 | BL | pcdisp8  |

|---|----|----------|

| 2 | BL | pcdisp24 |

### [Function]

### [Description]

BL causes an unconditional branch to the address specified by the label and puts the return address in R14.

There are two instruction formats; this allows software, such as an assembler, to decide on the better format.

The condition bit (C) is unchanged.

### [EIT occurrence]

None

| 0111 | 1110 | pcdisp8 | BL       | pcdisp8 |    |          |

|------|------|---------|----------|---------|----|----------|

| 1111 | 1110 |         | pcdisp24 |         | BL | pcdisp24 |

### 3.2 Instruction description

**BLEZ**

branch instruction Branch on less than or equal zero

### [Mnemonic]

BLEZ Rsrc, pcdisp16

### [Function]

Branch

if ((signed) Rsrc <= 0) PC = (PC & 0xffffffc) + (((signed short) pcdisp16) << 2);

### [Description]

BLEZ causes a branch to the specified label when the contents of Rsrc treated as a signed 32bit value, is less than or equal to zero. The condition bit (C) is unchanged.

#### [EIT occurrence]

None

### [Encoding]

| 1011  | 0000 | 1100 | src   | pcdisp16 |

|-------|------|------|-------|----------|

| BT.F7 | Dar  |      | dian1 | 6        |

BLEZ Rsrc,pcdisp16

3.2 Instruction description

branch instruction Branch on less than zero

[Mnemonic]

BLTZ Rsrc,pcdisp16

### [Function]

Branch

if ((signed) Rsrc < 0) PC = (PC & 0xffffffc) + (((signed short) pcdisp16) << 2);

#### [Description]

BLTZ causes a branch to the specified label when Rsrc treated as a signed 32-bit value is less than zero.

The condition bit (C) is unchanged.

#### [EIT occurrence]

None

#### [Encoding]

| 1011 0000 1010 src p | disp16 |

|----------------------|--------|

|----------------------|--------|

BLTZ Rsrc,pcdisp16

### 3.2 Instruction description

## BNC

*branch instruction* Branch on not C-bit

### [Mnemonic]

| 1 | BNC | pcdisp8  |

|---|-----|----------|

| 2 | BNC | pcdisp24 |

### [Function]

Branch

```

① if (C==0) PC = ( PC & 0xfffffffc ) + ( ( ( signed char ) pcdisp8 ) << 2 );

② if (C==0) PC = ( PC & 0xfffffffc ) + ( sign_extend ( pcdisp24 ) << 2 );

where

#define sign_extend(x) ( ( ( signed ) ( (x)<< 8 ) ) >>8 )

```

### [Description]

BNC branches to the specified label when the condition bit (C) is 0.

There are two instruction formats; this allows software, such as an assembler, to decide on the better format.

The condition bit (C) is unchanged.

### [EIT occurrence]

None

| 0111 | 1101 | pcdisp8 | BNC      | pcdisp8 |     |          |

|------|------|---------|----------|---------|-----|----------|

| 1111 | 1101 |         | pcdisp24 | 1 1     | BNC | pcdisp24 |

3.2 Instruction description

branch instruction Branch on not equal

### [Mnemonic]

BNE Rsrc1,Rsrc2,pcdisp16

### [Function]

Branch

if (Rsrc1 != Rsrc2 ) PC = (PC & 0xffffffc ) + ((( signed short ) pcdisp16) << 2);

### [Description]

BNE causes a branch to the specified label when Rsrc1 is not equal to Rsrc2. The condition bit (C) is unchanged.

#### [EIT occurrence]

None

### [Encoding]

| 11 src1 0001 src2 | pcdisp16 |

|-------------------|----------|

|-------------------|----------|

BNE Rsrc1,Rsrc2,pcdisp16

### 3.2 Instruction description

branch instruction Branch on not equal zero

### [Mnemonic]

BNEZ Rsrc,pcdisp16

### [Function]

Branch if ( Rsrc != 0 ) PC = ( PC & 0xfffffffc ) + ( ( ( signed short ) pcdisp16 ) << 2);

### [Description]

$\mathsf{BNEZ}$  causes a branch to the specified label when Rsrc is not equal to zero. The condition bit (C) is unchanged.

### [EIT occurrence]

None

### [Encoding]

| 1011 0000 1001 src pcdisp16 |

|-----------------------------|

|-----------------------------|

BNEZ Rsrc,pcdisp16

3.2 Instruction description

## BRA

branch instruction Branch

### [Mnemonic]

| 1 | BRA | pcdisp8  |

|---|-----|----------|

| 2 | BRA | pcdisp24 |

### [Function]

Branch

DC = ( PC & 0xfffffffc ) + ( ( signed char ) pcdisp8 ) << 2 );</li>

PC = ( PC & 0xfffffffc ) + ( sign\_extend ( pcdisp24 ) << 2 ); where #define sign\_extend(x) ( ( ( signed ) ( (x)<< 8 ) ) >>8 )

### [Description]

BRA causes an unconditional branch to the address specified by the label. There are two instruction formats; this allows software, such as an assembler, to decide on the better format.

The condition bit (C) is unchanged.

### [EIT occurrence]

None

| 0111 | 1111 | pcdisp8 | BRA      | pcdisp8 |     |          |

|------|------|---------|----------|---------|-----|----------|

| 1111 | 1111 |         | pcdisp24 | 1 1     | BRA | pcdisp24 |

### 3.2 Instruction description

## CMP

*compare instruction* Compare

### [Mnemonic]

CMP Rsrc1,Rsrc2

### [Function]

Compare

C = ((signed) Rsrc1 < (signed) Rsrc2) ? 1:0;

### [Description]

The condition bit (C) is set to 1 when Rsrc1 is less than Rsrc2. The operands are treated as signed 32-bit values.

### [EIT occurrence]

None

### [Encoding]

0000 src1 0100 src2

CMP Rsrc1,Rsrc2

3.2 Instruction description

## CMPI

*compare instruction* Compare immediate

[Mnemonic]

CMPI Rsrc,#imm16

### [Function]

Compare

C = ((signed) Rsrc < (signed short) imm16) ? 1:0;

### [Description]

The condition bit (C) is set when Rsrc is less than 16-bit immediate value. The operands are treated as signed 32-bit values. The immediate value is sign-extended to 32-bit before the operation.

### [EIT occurrence]

None

### [Encoding]

| 1000 0000 0100 src | imm16 |

|--------------------|-------|

|--------------------|-------|

CMPI Rsrc,#imm16

### 3.2 Instruction description

## CMPU

*compare instruction* Compare unsigned

## CMPU

### [Mnemonic]

CMPU Rsrc1,Rsrc2

### [Function]

Compare

C = ((unsigned) Rsrc1 < (unsigned) Rsrc2) ? 1:0;

### [Description]

The condition bit (C) is set when Rsrc1 is less than Rsrc2. The operands are treated as unsigned 32-bit values.

### [EIT occurrence]

None

### [Encoding]

0000 src1 0101 src2

CMPU Rsrc1,Rsrc2

3.2 Instruction description

*compare instruction* Compare unsigned immediate

[Mnemonic]

CMPUI Rsrc,#imm16

### [Function]

Compare

C = ((unsigned) Rsrc < (unsigned) ((signed short) imm16)) ? 1:0;

### [Description]

The condition bit (C) is set when Rsrc is less than the 16-bit immediate value. The operands are treated as unsigned 32-bit values. The immediate value is sign-extended to 32-bit before the operation.

#### [EIT occurrence]

None

### [Encoding]

| 1000 | 0000 | 0101 | src | imm16 |

|------|------|------|-----|-------|

|      | _    |      |     |       |

CMPUI Rsrc,#imm16

### 3.2 Instruction description

## DIV

multiply and divide instruction Divide

## DIV

### [Mnemonic]

DIV Rdest,Rsrc

### [Function]

Signed division Rdest = ( signed ) Rdest / ( signed ) Rsrc;

### [Description]

DIV divides Rdest by Rsrc and puts the quotient in Rdest. The operands are treated as signed 32-bit values and the result is rounded toward zero. The condition bit (C) is unchanged. When Rsrc is zero, Rdest is unchanged.

### [EIT occurrence]

None

### [Encoding]

| 1001 dest 0000 src | 0000 0000 0000 0000 |

|--------------------|---------------------|

|--------------------|---------------------|

DIV Rdest,Rsrc

3.2 Instruction description

## DIVU

multiply and divide instruction Divide unsigned

### [Mnemonic]

DIVU Rdest,Rsrc

### [Function]

Unsigned division Rdest = ( unsigned ) Rdest / ( unsigned ) Rsrc;

### [Description]

DIVU divides Rdest by Rsrc and puts the quotient in Rdest. The operands are treated as unsigned 32-bit values and the result is rounded toward zero. The condition bit (C) is unchanged. When Rsrc is zero, Rdest is unchanged.

#### [EIT occurrence]

None

| 1001 | dest | 0001  | src | 0000 | 0000 | 0000 | 0000 |

|------|------|-------|-----|------|------|------|------|

| DIVU | Rde  | est,R | src |      |      |      |      |

### 3.2 Instruction description

## JL

branch instruction Jump and link JL

### [Mnemonic]

JL Rsrc

### [Function]

Subroutine call (register direct) R14 = ( PC & 0xffffffc ) + 4; PC = Rsrc & 0xffffffc;

### [Description]

JL causes an unconditional jump to the address specified by Rsrc and puts the return address in R14.

The condition bit (C) is unchanged.

### [EIT occurrence]

None

### [Encoding]

0001 1110 1100 src

JL Rsrc

3.2 Instruction description

branch instruction Jump

### [Mnemonic]

JMP Rsrc

### [Function]

Jump

PC = Rsrc & 0xfffffffc;

### [Description]

JMP causes an unconditional jump to the address specified by Rsrc. The condition bit (C) is unchanged.

### [EIT occurrence]

None

### [Encoding]

0001 1111 1100 src

JMP Rsrc

### 3.2 Instruction description

## LD

load/store instruction Load LD

### [Mnemonic]

| 1 | LD | Rdest,@Rsrc          |

|---|----|----------------------|

| 2 | LD | Rdest,@Rsrc+         |

| 3 | LD | Rdest,@(disp16,Rsrc) |

### [Function]

### Load

- ① Rdest = \*( int \*) Rsrc;

- ② Rdest = \*( int \*) Rsrc, Rsrc += 4;

- $\$  Rdest = \*( int \*) ( Rsrc + ( signed short ) disp16 );

### [Description]

- ① The contents of the memory at the address specified by Rsrc are loaded into Rdest.

- ② The contents of the memory at the address specified by Rsrc are loaded into Rdest. Rsrc is post incremented by 4.

- ③ The contents of the memory at the address specified by Rsrc combined with the 16bit displacement are loaded into Rdest.

The displacement value is sign-extended to 32 bits before the address calculation. The condition bit (C) is unchanged.

### [EIT occurrence]

Address exception (AE)

| 0010                      | dest | 1100 | src | LD | Rdest,@Rsr | C   |  |

|---------------------------|------|------|-----|----|------------|-----|--|

| 0010                      | dest | 1110 | src | LD | Rdest,@Rsr | :c+ |  |

| 1010 dest 1100 src disp16 |      |      |     |    |            |     |  |

| LD Rdest,@(disp16,Rsrc)   |      |      |     |    |            |     |  |

3.2 Instruction description

## LD24

load/store instruction Load 24-bit immediate

### [Mnemonic]

LD24 Rdest,#imm24

### [Function]

Load

Rdest = imm24 & 0x00ffffff;

### [Description]

LD24 loads the 24-bit immediate value into Rdest. The immediate value is zero-extended to 32 bits.

The condition bit (C) is unchanged.

### [EIT occurrence]

None

### [Encoding]

| 1110 | dest | imm24 |

|------|------|-------|

|      |      |       |

LD24 Rdest,#imm24

### 3.2 Instruction description

## LDB

load/store instruction Load byte

## LDB

### [Mnemonic]

LDB Rdest,@Rsrc

LDB Rdest,@(disp16,Rsrc)

### [Function]

Load

- ① Rdest = \*( signed char \*) Rsrc;

- Rdest = \*( signed char \*) ( Rsrc + ( signed short ) disp16 );

### [Description]

- ① LDB sign-extends the byte data of the memory at the address specified by Rsrc and loads it into Rdest.

- ② LDB sign-extends the byte data of the memory at the address specified by Rsrc combined with the 16-bit displacement, and loads it into Rdest.

The displacement value is sign-extended to 32 bits before the address calculation. The condition bit (C) is unchanged.

#### [EIT occurrence]

None

### [Encoding]

| 0010                     | dest | 1000 | src | LDB Rdest,@Rs | rc |  |

|--------------------------|------|------|-----|---------------|----|--|

| 1010                     | dest | 1000 | src | disp16        |    |  |

| IDD Ddogt @/digp16 Dang) |      |      |     |               |    |  |

LDB Rdest,@(disp16,Rsrc)

3.2 Instruction description

## LDH

load/store instruction Load halfword

### [Mnemonic]

LDH Rdest,@Rsrc

LDH Rdest,@(disp16,Rsrc)

### [Function]

### Load

Rdest = \*( signed short \*) Rsrc;

Rdest = \*( signed short \*) ( Rsrc + ( signed short ) disp16 );

### [Description]

- ① LDH sign-extends the halfword data of the memory at the address specified by Rsrc and loads it into Rdest.

- ② LDH sign-extends the halfword data of the memory at the address specified by Rsrc combined with the 16-bit displacement, and loads it into Rdest.

The displacement value is sign-extended to 32 bits before the address calculation. The condition bit (C) is unchanged.

### [EIT occurrence]

Address exception (AE)

### [Encoding]

| 0010 | dest | 1010 | src | LDH Rdest,@Rsrc |

|------|------|------|-----|-----------------|

| 1010 | dest | 1010 | src | disp16          |

LDH Rdest,@(disp16,Rsrc)

### 3.2 Instruction description

## LDI

*transfer instruction* Load immediate

# LDI

### [Mnemonic]

LDI Rdest,#imm8

LDI Rdest,#imm16

### [Function]

Load

- ① Rdest = ( signed char ) imm8;

- @ Rdest = ( signed short ) imm16;

### [Description]

- ① LDI loads the 8-bit immediate value into Rdest.

The immediate value is sign-extended to 32 bits.

- 2 LDI loads the 16-bit immediate value into Rdest. The immediate value is sign-extended to 32 bits. The condition bit (C) is unchanged.

### [EIT occurrence]

None

| 0110             | dest | imm8 |      | : | LDI | Rdes | st,#ir | nm 8 |

|------------------|------|------|------|---|-----|------|--------|------|

| 1001             | dest | 1111 | 0000 |   | im  | 16   |        |      |

| LDI Rdest,#imm16 |      |      |      |   |     |      |        |      |

3.2 Instruction description

## LDUB

load/store instruction Load unsigned byte

### [Mnemonic]

LDUB Rdest,@Rsrc

LDUB Rdest,@(disp16,Rsrc)

### [Function]

### Load

- ① Rdest = \*( unsigned char \*) Rsrc;

- Rdest = \*( unsigned char \*) ( Rsrc + ( signed short ) disp16 );

### [Description]

- ① LDUB zero-extends the byte data from the memory at the address specified by Rsrc and loads it into Rdest.

- ② LDUB zero-extends the byte data of the memory at the address specified by Rsrc combined with the 16-bit displacement, and loads it into Rdest.

The displacement value is sign-extended to 32 bits before address calculation. The condition bit (C) is unchanged.

#### [EIT occurrence]

None

### [Encoding]

| 0010                      | dest | 1001 | src | LDUB Rdest,@F | lsrc |  |  |

|---------------------------|------|------|-----|---------------|------|--|--|

| 1010                      | dest | 1001 | src | disp16        |      |  |  |

| I DUD Deat @(dian16 Dana) |      |      |     |               |      |  |  |

LDUB Rdest,@(disp16,Rsrc)

### 3.2 Instruction description

## LDUH

load/store instruction Load unsigned halfword LDUH

### [Mnemonic]

LDUH Rdest,@Rsrc

LDUH Rdest,@(disp16,Rsrc)

### [Function]

### Load

- ① Rdest = \*( unsigned short \*) Rsrc;

- Rdest = \*( unsigned short \*) ( Rsrc + ( signed short ) disp16 );

### [Description]

- ① LDUH zero-extends the halfword data from the memory at the address specified by Rsrc and loads it into Rdest.

- ② LDUH zero-extends the halfword data in memory at the address specified by Rsrc combined with the 16-bit displacement, and loads it into Rdest.

The displacement value is sign-extended to 32 bits before the address calculation. The condition bit (C) is unchanged.

### [EIT occurrence]

Address exception (AE)

### [Encoding]

| 0010                      | dest | 1011 | src | : | LDUH | Rde | st,@I | Rsrc |

|---------------------------|------|------|-----|---|------|-----|-------|------|

| 1010                      | dest | 1011 | src |   | dis  | p16 |       |      |

| I DUH Boat @(dian16 Bara) |      |      |     |   |      |     |       |      |

LDUH Rdest,@(disp16,Rsrc)

3.2 Instruction description

load/store instruction Load locked

### [Mnemonic]

LOCK Rdest,@Rsrc

### [Function]

Load locked LOCK = 1, Rdest = \*( int \*) Rsrc;

### [Description]

The contents of the word at the memory location specified by Rsrc are loaded into Rdest. The condition bit (C) is unchanged. This instruction sets the LOCK bit in addition to simple loading. When the LOCK bit is 1, external bus master access is not accepted. The LOCK bit is cleared by executing the **UNLOCK** instruction. The LOCK bit is internal to the CPU and cannot be accessed directly except by using the **LOCK** or **UNLOCK** instructions.

### [EIT occurrence]

Address exception (AE)

### [Encoding]

0010 dest 1101 src

LOCK Rdest,@Rsrc

### 3.2 Instruction description

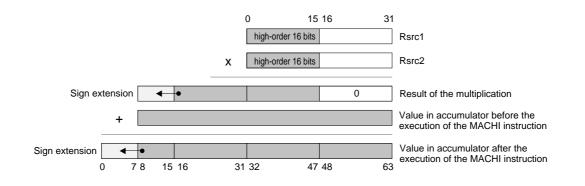

DSP function instruction Multiply-accumulate high-order halfword

[Mnemonic]

MACHI Rsrc1,Rsrc2

### [Function]

Multiply and add accumulator += (( signed) (Rsrc1 & 0xffff0000) \* (signed short) (Rsrc2 >> 16));

### [Description]

MACHI multiplies the high-order 16 bits of Rsrc1 and the high-order 16 bits of Rsrc2, then adds the result to the low-order 56 bits in the accumulator.

The LSB of the multiplication result is aligned with bit 47 in the accumulator, and the portion corresponding to bits 8 through 15 of the accumulator is sign-extended before addition. The result of the addition is stored in the accumulator. The high-order 16 bits of Rsrc1 and Rsrc2 are treated as signed values.

The condition bit (C) is unchanged.

#### [EIT occurrence]

None

|  | 0011 | src1 | 0100 | src2 | MACHI | Rsrc1,Rsrc2 |

|--|------|------|------|------|-------|-------------|

|--|------|------|------|------|-------|-------------|

3.2 Instruction description

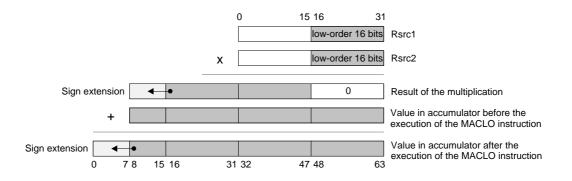

## MACLO

DSP function instruction Multiply-accumulate low-order halfword

MACLO

[Mnemonic]

MACLO Rsrc1,Rsrc2

### [Function]

Multiply and add accumulator += ( (signed) (Rsrc1 << 16) \* (signed short) Rsrc2 );

### [Description]

MACLO multiplies the low-order 16 bits of Rsrc1 and the low-order 16 bits of Rsrc2, then adds the result to the low order 56 bits in the accumulator.

The LSB of the multiplication result is aligned with bit 47 in the accumulator, and the portion corresponding to bits 8 through 15 of the accumulator is sign-extended before addition. The result of the addition is stored in the accumulator. The low-order 16 bits of Rsrc1 and Rsrc2 are treated as signed values.

The condition bit (C) is unchanged.

### [EIT occurrence]

None

3.2 Instruction description

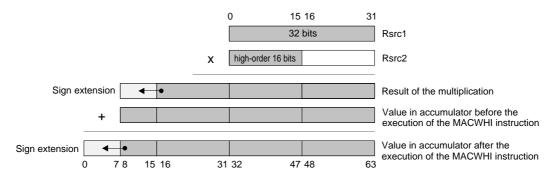

DSP function instruction Multiply-accumulate word **MACWHI** and high-order halfword

[Mnemonic]

MACWHI Rsrc1,Rsrc2

### [Function]

Multiply and add accumulator += ( ( signed ) Rsrc1 \* ( signed short ) ( Rsrc2 >> 16 ) );

### [Description]

MACWHI multiplies the 32 bits of Rsrc1 and the high-order 16 bits of Rsrc2, then adds the result to the low-order 56 bits in the accumulator.

The LSB of the multiplication result is aligned with the LSB of the accumulator, and the portion corresponding to bits 8 through 15 of the accumulator is sign extended before addition. The result of addition is stored in the accumulator. The 32 bits of Rsrc1 and the high-order 16 bits of Rsrc2 are treated as signed values.

The condition bit (C) is unchanged.

### [EIT occurrence]

None

### [Encoding]

MACWHI Rsrc1,Rsrc2

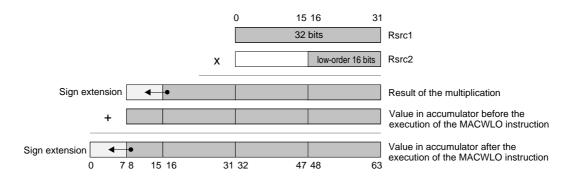

3.2 Instruction description

DSP function instruction Multiply-accumulate word and low-order halfword

[Mnemonic]

MACWLO Rsrc1, Rsrc2

### [Function]

Multiply and add accumulator += ( (signed) Rsrc1 \* (signed short) Rsrc2 );

### [Description]

MACWLO multiplies the 32 bits of Rsrc1 and the low-order 16 bits of Rsrc2, then adds the result to the low-order 56 bits in the accumulator.

The LSB of the multiplication result is aligned with the LSB of the accumulator, and the portion corresponding to bits 8 through 15 of the accumulator is sign-extended before the addition. The result of the addition is stored in the accumulator. The 32 bits Rsrc1 and the low-order 16 bits of Rsrc2 are treated as signed values.

The condition bit (C) is unchanged.

#### [EIT occurrence]

None

### [Encoding]

MACWLO Rsrc1,Rsrc2

### 3.2 Instruction description

## MUL

multiply and divide instruction Multiply MUL

### [Mnemonic]

MUL Rdest,Rsrc

### [Function]

Multiply

{ signed64bit tmp; tmp = ( signed64bit ) Rdest \* ( signed64bit ) Rsrc; Rdest = ( int ) tmp;}

### [Description]

MUL multiplies Rdest by Rsrc and puts the result in Rdest. The operands are treated as signed values. The condition bit (C) is unchanged. The contents of the accumulator are destroyed by this instruction.

### [EIT occurrence]

None

### [Encoding]

0001 dest 0110 src

MUL Rdest,Rsrc

3.2 Instruction description

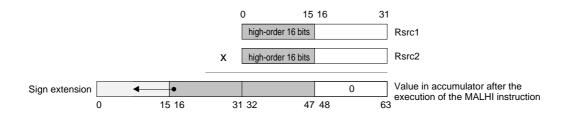

DSP function instruction Multiply high-order halfwords

#### [Mnemonic]

MULHI Rsrc1,Rsrc2

#### [Function]

Multiply

accumulator = (( signed) (Rsrc1 & 0xffff000 ) \* (signed short) (Rsrc2 >> 16));

#### [Description]

MULHI multiplies the high-order 16 bits of Rsrc1 and the high-order 16 bits of Rsrc2, and stores the result in the accumulator.

However, the LSB of the multiplication result is aligned with bit 47 in the accumulator, and the portion corresponding to bits 0 through 15 of the accumulator is sign-extended. Bits 48 through 63 of the accumulator are cleared to 0. The high-order 16 bits of Rsrc1 and Rsrc2 are treated as signed values.

The condition bit (C) is unchanged.

#### [EIT occurrence]

None

#### [Encoding]

0011 src1 0000 src2

MULHI

Rsrc1,Rsrc2

3.2 Instruction description

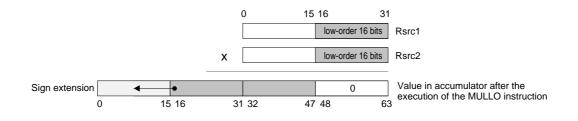

# MULLO

DSP function instruction Multiply low-order halfwords

# MULLO

#### [Mnemonic]

MULLO Rsrc1,Rsrc2

#### [Function]

Multiply

```

accumulator = ( ( signed ) ( Rsrc1 << 16 ) * ( signed short ) Rsrc2 );

```

#### [Description]

MULLO multiplies the low-order 16 bits of Rsrc1 and the low-order 16 bits of Rsrc2, and stores the result in the accumulator.

The LSB of the multiplication result is aligned with bit 47 in the accumulator, and the portion corresponding to bits 0 through 15 of the accumulator is sign extended. Bits 48 through 63 of the accumulator are cleared to 0. The low-order 16 bits of Rsrc1 and Rsrc2 are treated as signed values.

The condition bit (C) is unchanged.

#### [EIT occurrence]

None

#### [Encoding]

0011 src1 0001 src2

MULLO

Rsrc1,Rsrc2

3.2 Instruction description

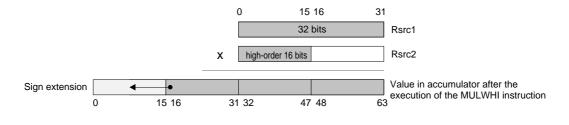

MULWHI

DSP function instruction Multiply word and high-order halfword

[Mnemonic]

MULWHI Rsrc1,Rsrc2

#### [Function]

Multiply

accumulator = ( ( signed ) Rsrc1 \* ( signed short ) ( Rsrc2 >> 16 ) );

#### [Description]

MULWHI multiplies the 32 bits of Rsrc1 and the high-order 16 bits of Rsrc2, and stores the result in the accumulator.

The LSB of the multiplication result is aligned with the LSB of the accumulator, and the portion corresponding to bits 0 through 15 of the accumulator is sign-extended. The 32 bits of Rsrc1 and high-order 16 bits of Rsrc2 are treated as signed values.

The condition bit (C) is unchanged.

#### [EIT occurrence]

None

#### [Encoding]

0011 src1 0010 src2

MULWHI Rsrc1,Rsrc2

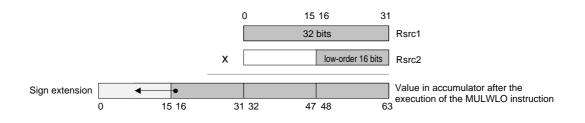

3.2 Instruction description

DSP fucntion instruction Multiply word and low-order halfword MULWLO

[Mnemonic]

MULWLO Rsrc1, Rsrc2

#### [Function]

Multiply

```

accumulator = ( ( signed ) Rsrc1 * ( signed short ) Rsrc2 );

```

#### [Description]

MULWLO multiplies the 32 bits of Rsrc1 and the low-order 16 bits of Rsrc2, and stores the result in the accumulator.

The LSB of the multiplication result is aligned with the LSB of the accumulator, and the portion corresponding to bits 0 through 15 of the accumulator is sign extended. The 32 bits of Rsrc1 and low-order 16 bits of Rsrc2 are treated as signed values. The condition bit (C) is unchanged

The condition bit (C) is unchanged.

#### [EIT occurrence]

None

#### [Encoding]

0011 src1 0011 src2

c2 MULWLO

Rsrc1,Rsrc2

3.2 Instruction description

transfer instruction Move register

#### [Mnemonic]

MV Rdest,Rsrc

#### [Function]

Transfer Rdest = Rsrc;

#### [Description]

MV moves Rsrc to Rdest. The condition bit (C) is unchanged.

#### [EIT occurrence]

None

#### [Encoding]

0001 dest 1000 src

MV Rdest,Rsrc

### 3.2 Instruction description

DSP function instruction Move from accumulator high-order word

# **MVFACHI**

#### [Mnemonic]

MVFACHI Rdest

#### [Function]

Transfer from accumulator to register Rdest = ( int ) ( accumulator >> 32 ) ;

#### [Description]

MVFACHI moves the high-order 32 bits of the accumulator to Rdest. The condition bit (C) is unchanged.

#### [EIT occurrence]

None

#### [Encoding]

0101 dest 1111 0000

MVFACHI Rdest

3.2 Instruction description

low-order word

#### [Mnemonic]

MVFACLO Rdest

#### [Function]

Transfer from accumulator to register Rdest = ( int ) accumulator ;

#### [Description]

MVFACLO moves the low-order 32 bits of the accumulator to Rdest. The condition bit (C) is unchanged.

#### [EIT occurrence]

None

#### [Encoding]

0101 dest 1111 0001

MVFACLO Rdest

### 3.2 Instruction description

**MVFACMI**

DSP function instruction Move from accumulator middle-order word

## **MVFACMI**

#### [Mnemonic]

MVFACMI Rdest

#### [Function]

Transfer from accumulator to register Rdest = ( int ) ( accumulator >> 16 ) ;

#### [Description]

MVFACMI moves bits16 through 47 of the accumulator to Rdest. The condition bit (C) is unchanged.

#### [EIT occurrence]

None

#### [Encoding]

0101 dest 1111 0010

MVFACMI Rdest

3.2 Instruction description

transfer instruction Move from control register

#### [Mnemonic]

MVFC Rdest, CRsrc

#### [Function]

Transfer from control register to register Rdest = CRsrc ;

#### [Description]

MVFC moves CRsrc to Rdest. The condition bit (C) is unchanged.

#### [EIT occurrence]

None

#### [Encoding]

0001 dest 1001 src

MVFC Rdest,CRsrc

### 3.2 Instruction description

DSP function instruction Move to accumulator high-order word

# **MVTACHI**

#### [Mnemonic]

MVTACHI Rsrc

#### [Function]

Transfer from register to accumulator accumulator [ 0 : 31 ] = Rsrc ;

#### [Description]

$\mathsf{MVTACHI}$  moves Rsrc to the high-order 32 bits of the accumulator. The condition bit (C) is unchanged.

#### [EIT occurrence]

None

#### [Encoding]

0101 src 0111 0000

MVTACHI Rsrc

3.2 Instruction description

low-order word

#### [Mnemonic]

MVTACLO Rsrc

#### [Function]

Transfer from register to accumulator accumulator [32:63] = Rsrc;

#### [Description]

MVTACLO moves Rsrc to the low-order 32 bits of the accumulator. The condition bit (C) is unchanged.

#### [EIT occurrence]

None

#### [Encoding]

0101 0111 0001 src

MVTACLO Rsrc

### 3.2 Instruction description

*transfer instruction* Move to control register

# MVTC

#### [Mnemonic]

MVTC Rsrc, CRdest

#### [Function]

Transfer from register to control register CRdest = Rsrc ;

#### [Description]

MVTC moves Rsrc to CRdest. If PSW(CR0) is specified as CRdest, the condition bit (C) is changed; otherwise it is unchanged.

#### [EIT occurrence]

None

#### [Encoding]

0001 dest 1010 src

MVTC Rsrc,CRdest

3.2 Instruction description

# NEG

arithmetic operation instruction Negate

#### [Mnemonic]

NEG Rdest,Rsrc

#### [Function]

Negate

Rdest = 0 - Rsrc;

#### [Description]

NEG negates (changes the sign of) Rsrc treated as a signed 32-bit value, and puts the result in Rdest.

The condition bit (C) is unchanged.

#### [EIT occurrence]

None

#### [Encoding]

0000 dest 0011 src

NEG Rdest,Rsrc

### 3.2 Instruction description

# NOP

branch instruction No operation

# NOP

#### [Mnemonic]

NOP

### [Function]

No operation /\* \*/

#### [Description]

NOP performs no operation. The subsequent instruction then processed. The condition bit (C) is unchanged.

#### [EIT occurrence]

None

#### [Encoding]

0111 0000 0000 0000

NOP

3.2 Instruction description

# NOT

logic operation instruction Logical NOT

#### [Mnemonic]

NOT Rdest,Rsrc

#### [Function]

Logical NOT Rdest = ~ Rsrc ;

#### [Description]

NOT inverts each of the bits of Rsrc and puts the result in Rdest. The condition bit (C) is unchanged.

#### [EIT occurrence]

None

#### [Encoding]

0000 dest 1011 src

NOT Rdest,Rsrc

### 3.2 Instruction description

## OR

logic operation instruction OR OR

#### [Mnemonic]

OR Rdest,Rsrc

#### [Function]

Logical OR Rdest = Rdest | Rsrc ;

#### [Description]

OR computes the logical OR of the corresponding bits of Rdest and Rsrc, and puts the result in Rdest.

The condition bit (C) is unchanged.

#### [EIT occurrence]

None

#### [Encoding]

0000 dest 1110 src

Rdest,Rsrc

OR

3.2 Instruction description

# OR3

logic operation instruction OR 3-operand

#### [Mnemonic]

OR3 Rdest,Rsrc,#imm16

#### [Function]

Logical OR Rdest = Rsrc | (unsigned short) imm16;

#### [Description]

OR3 computes the logical OR of the corresponding bits of Rsrc and the 16-bit immediate value, which is zero-extended to 32 bits, and puts the result in Rdest. The condition bit (C) is unchanged.

#### [EIT occurrence]

None

#### [Encoding]

| 1000 | dest | 1110 | src | imm16 |

|------|------|------|-----|-------|

|      |      |      |     |       |

OR3 Rdest,Rsrc,#imm16

### 3.2 Instruction description

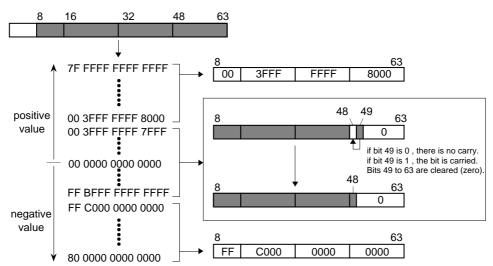

DSP function instruction Round accumulator RAC

#### [Mnemonic]

RAC

#### [Function]

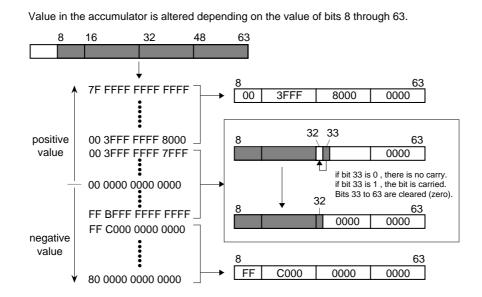

{ signed64bit tmp; if( 0x0000 3fff ffff 8000 =< accumulator ) tmp = 0x0000 3fff ffff 8000; else if( accumulator =< 0xffff c000 0000 0000 ) tmp = 0xffff c000 0000 0000; else { tmp = accumulator + 0x0000 0000 0000 4000; tmp = tmp & 0xffff ffff 8000;} accumulator = tmp << 1;}</pre>

#### [Description]

RAC rounds the contents in the accumulator to word size and stores the result in the accumulator. The condition bit (C) is unchanged.

#### [EIT occurrence]

None

#### [Encoding]

3.2 Instruction description

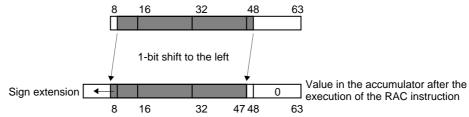

#### [Supplement]

This instruction is executed in two steps as shown below:

#### <step 1>

The value in the accumulator is altered depending on the value of bits 8 through 63.

<step 2>

3.2 Instruction description

RACH

DSP function instruction Round accumulator halfword

# RACH

#### [Mnemonic]

RACH

#### [Function]

{ signed64bit tmp; if( 0x0000 3fff 8000 0000 =< accumulator ) tmp = 0x0000 3fff 8000 0000; else if( accumulator =< 0xffff c000 0000 0000 ) tmp = 0xffff c000 0000 0000; else { tmp = accumulator + 0x0000 0000 4000 0000; tmp = tmp & 0xffff ffff 8000 0000;} accumulator = tmp << 1;}</pre>

#### [Description]

RACH rounds the contents in the accumulator to halfword size and stores the result in the accumulator.

The condition bit (C) is unchanged.

#### [EIT occurrence]

None

#### [Encoding]

0101 0000 1000 0000

RACH

3.2 Instruction description

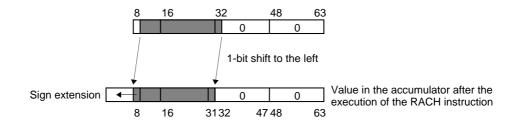

#### [Supplement]

This instruction is executed in two steps, as shown below.

<step 1>

<step 2>

### 3.2 Instruction description

## REM

multiply and divide instruction Remainder

#### [Mnemonic]

REM Rdest,Rsrc

#### [Function]