# Regarding the change of names mentioned in the document, such as Hitachi Electric and Hitachi XX, to Renesas Technology Corp.

The semiconductor operations of Mitsubishi Electric and Hitachi were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Hitachi, Hitachi, Ltd., Hitachi Semiconductors, and other Hitachi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Renesas Technology Home Page: http://www.renesas.com

Renesas Technology Corp. Customer Support Dept. April 1, 2003

#### **Cautions**

Keep safety first in your circuit designs!

1. Renesas Technology Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- 1. These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corporation product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corporation or a third party.

- 2. Renesas Technology Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor for the latest product information before purchasing a product listed herein.

- The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

- Please also pay attention to information published by Renesas Technology Corporation by various means, including the Renesas Technology Corporation Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corporation is necessary to reprint or reproduce in whole or in part these materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

- Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

- 8. Please contact Renesas Technology Corporation for further details on these materials or the products contained therein.

# H8/300L Series Programming Manual

#### **Cautions**

- 1. Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party's rights, including intellectual property rights, in connection with use of the information contained in this document.

- 2. Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- 7. Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

# **Preface**

The H8/300L Series of single-chip microcomputers is built around the high-speed H8/300L CPU, with an architecture featuring eight 16-bit (or sixteen 8-bit) general registers and a concise, optimized instruction set.

This manual gives detailed descriptions of the H8/300L instructions. The descriptions apply to all chips in the H8/300L Series. Assembly-language programmers should also read the separate *H8/300 Series Cross Assembler User's Manual*.

For hardware details, refer to the hardware manual of the specific chip.

# **Contents**

| Sec | tion 1. C   | PU                                               | . 1  |

|-----|-------------|--------------------------------------------------|------|

| 1.1 | Overview    |                                                  | . 1  |

|     | 1.1.1 Fe    | atures                                           | . 1  |

|     | 1.1.2 Da    | ta Structure                                     | . 2  |

|     | 1.1.3 Ad    | dress Space                                      | . 4  |

|     | 1.1.4 Re    | gister Configuration                             | . 5  |

| 1.2 | Registers   |                                                  | . 6  |

|     | 1.2.1 Ge    | neral Registers                                  | . 6  |

|     | 1.2.2 Co    | ntrol Registers                                  | . 6  |

|     | 1.2.3 Ini   | tial Register Values                             | . 7  |

| 1.3 | Instruction | ns                                               | . 8  |

|     | 1.3.1 Ty    | pes of Instructions                              | . 8  |

|     | 1.3.2 Ins   | truction Functions                               | . 9  |

|     | 1.3.3 Ba    | sic Instruction Formats                          | . 20 |

|     | 1.3.4 Ad    | dressing Modes and Effective Address Calculation | . 26 |

|     |             |                                                  |      |

| Sec | tion 2. In  | struction Set                                    | . 31 |

| 2.1 | Explanation | on Format                                        | . 31 |

| 2.2 | Instruction | ns                                               | . 36 |

|     | 2.2.1 (1)   | ADD (add binary) (byte)                          | . 36 |

|     | 2.2.1 (2)   | ADD (add binary) (word)                          | . 37 |

|     | 2.2.2       | ADDS (add with sign extension)                   | . 38 |

|     | 2.2.3       | ADDX (add with extend carry)                     | . 39 |

|     | 2.2.4       | AND (AND logical)                                | . 40 |

|     | 2.2.5       | ANDC (AND control register)                      | . 41 |

|     | 2.2.6       | BAND (bit AND)                                   | . 42 |

|     | 2.2.7       | Bcc (branch conditionally)                       | . 43 |

|     | 2.2.8       | BCLR (bit clear)                                 | . 46 |

|     | 2.2.9       | BIAND (bit invert AND)                           | . 48 |

|     | 2.2.10      | BILD (bit invert load)                           | . 49 |

|     | 2.2.11      | BIOR (bit invert inclusive OR)                   | . 50 |

|     | 2.2.12      | BIST (bit invert store)                          | . 51 |

|     | 2.2.13      | BIXOR (bit invert exclusive OR)                  | . 52 |

|     | 2.2.14      | BLD (bit load)                                   | . 53 |

|     | 2.2.15      | BNOT (bit NOT)                                   | . 54 |

| 2.2.16     | BOR (bit inclusive OR)                 | . 56 |

|------------|----------------------------------------|------|

| 2.2.17     | BSET (bit set)                         | . 57 |

| 2.2.18     | BSR (branch to subroutine)             | . 59 |

| 2.2.19     | BST (bit store)                        | . 60 |

| 2.2.20     | BTST (bit test)                        | . 61 |

| 2.2.21     | BXOR (bit exclusive OR)                | . 63 |

| 2.2.22 (1) | CMP (compare) (byte)                   | . 64 |

| 2.2.22 (2) | CMP (compare) (word)                   | . 65 |

| 2.2.23     | DAA (decimal adjust add)               | . 66 |

| 2.2.24     | DAS (decimal adjust subtract)          | . 68 |

| 2.2.25     | DEC (decrement)                        | . 70 |

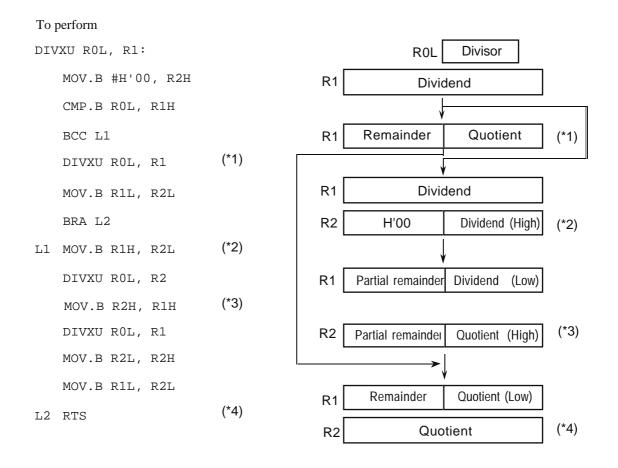

| 2.2.26     | DIVXU (divide extend as unsigned)      | . 71 |

| 2.2.27     | EEPMOV (move data to EEPROM)           | . 73 |

| 2.2.28     | INC (increment)                        | . 74 |

| 2.2.29     | JMP (jump)                             | . 75 |

| 2.2.30     | JSR (jump to subroutine)               | . 76 |

| 2.2.31     | LDC (load to control register)         | . 77 |

| 2.2.32 (1) | MOV (move data) (byte)                 | . 78 |

| 2.2.32 (2) | MOV (move data) (word)                 | . 79 |

| 2.2.32 (3) | MOV (move data) (byte)                 | . 80 |

| 2.2.32 (4) | MOV (move data) (word)                 | . 81 |

| 2.2.32 (5) | MOV (move data) (byte)                 | . 82 |

| 2.2.32 (6) | MOV (move data) (word)                 | . 83 |

| 2.2.33     | MULXU (multiply extend as unsigned)    | . 84 |

| 2.2.34     | NEG (negate)                           | . 85 |

| 2.2.35     | NOP (no operation)                     | . 86 |

| 2.2.36     | NOT (NOT = logical complement)         | . 87 |

| 2.2.37     | OR (inclusive OR logical)              | . 88 |

| 2.2.38     | ORC (inclusive OR control register)    | . 89 |

| 2.2.39     | POP (pop data)                         | . 90 |

| 2.2.40     | PUSH (push data)                       | . 91 |

| 2.2.41     | ROTL (rotate left)                     | . 92 |

| 2.2.42     | ROTR (rotate right)                    | . 93 |

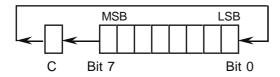

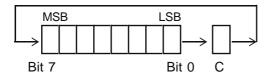

| 2.2.43     | ROTXL (rotate with extend carry left)  | . 94 |

| 2.2.44     | ROTXR (rotate with extend carry right) | . 95 |

| 2.2.45     | RTE (return from exception)            | . 96 |

| 2.2.46     | RTS (return from subroutine)           | . 97 |

|                                 | 2.2.47                                                                        | SHAL (shift arithmetic left)                                                                                                                                                      | 98                |

|---------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|                                 | 2.2.48                                                                        | SHAR (shift arithmetic right)                                                                                                                                                     | 99                |

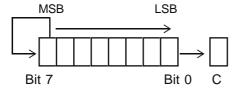

|                                 | 2.2.49                                                                        | SHLL (shift logical left)                                                                                                                                                         | 100               |

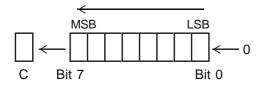

|                                 | 2.2.50                                                                        | SHLR (shift logical right)                                                                                                                                                        | 101               |

|                                 | 2.2.51                                                                        | SLEEP (sleep)                                                                                                                                                                     | 102               |

|                                 | 2.2.52                                                                        | STC (store from control register)                                                                                                                                                 | 103               |

|                                 | 2.2.53 (1)                                                                    | SUB (subtract binary) (byte)                                                                                                                                                      | 104               |

|                                 | 2.2.53 (2)                                                                    | SUB (subtract binary) (word)                                                                                                                                                      | 105               |

|                                 | 2.2.54                                                                        | SUBS (subtract with sign extension)                                                                                                                                               | 106               |

|                                 | 2.2.55                                                                        | SUBX (subtract with extend carry)                                                                                                                                                 | 107               |

|                                 | 2.2.56                                                                        | XOR (exclusive OR logical)                                                                                                                                                        | 108               |

|                                 | 2.2.57                                                                        | XORC (exclusive OR control register)                                                                                                                                              | 109               |

| 2.3                             | Operation                                                                     | Code Map                                                                                                                                                                          | 110               |

| 2.4                             | List of Ins                                                                   | tructions                                                                                                                                                                         | 112               |

|                                 |                                                                               |                                                                                                                                                                                   |                   |

| 2.5                             | Number of                                                                     | f Execution States                                                                                                                                                                | 119               |

|                                 |                                                                               | f Execution States PU Operation States                                                                                                                                            |                   |

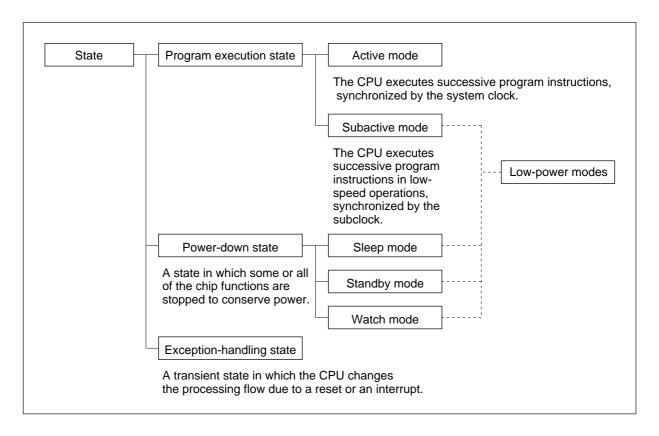

| 2.5<br>Sec<br>3.1               | etion 3. Cl                                                                   |                                                                                                                                                                                   | 127               |

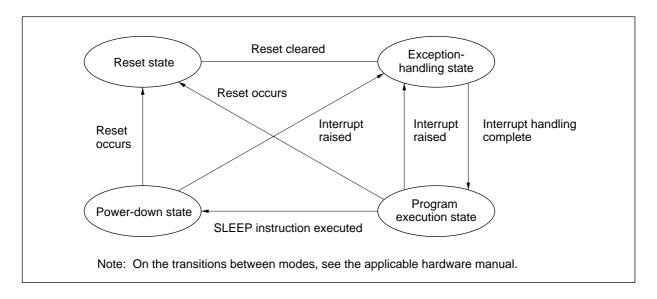

| Sec                             | ction 3. Cl<br>Program E                                                      | PU Operation States                                                                                                                                                               | 127               |

| Sec                             | ction 3. Cl<br>Program E                                                      | PU Operation States                                                                                                                                                               | 127<br>128<br>128 |

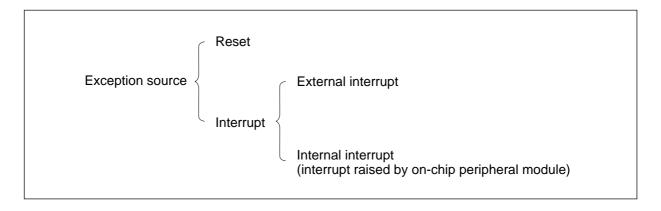

| Sec                             | etion 3. Cl<br>Program E<br>Exception                                         | PU Operation States  Execution State  Handling States                                                                                                                             | 127<br>128<br>128 |

| Sec                             | Program E<br>Exception<br>3.2.1                                               | PU Operation States  Execution State  Handling States  Types and Priorities of Exception Handling                                                                                 | 127128128128      |

| Sec 3.1 3.2                     | Program E Exception 3.2.1 3.2.2 3.2.3                                         | PU Operation States  Execution State  Handling States  Types and Priorities of Exception Handling  Exception Sources and Vector Table                                             |                   |

| Sec<br>3.1<br>3.2               | Program E<br>Exception<br>3.2.1<br>3.2.2<br>3.2.3<br>Reset State              | PU Operation States  Execution State  Handling States  Types and Priorities of Exception Handling  Exception Sources and Vector Table  Outline of Exception Handling Operation    |                   |

| Sec<br>3.1<br>3.2<br>3.3<br>3.4 | Program E<br>Exception<br>3.2.1<br>3.2.2<br>3.2.3<br>Reset State<br>Power-Dov | PU Operation States  Execution State  Handling States  Types and Priorities of Exception Handling  Exception Sources and Vector Table  Outline of Exception Handling Operation    |                   |

| Sec 3.1 3.2 3.3 3.4             | Program E Exception 3.2.1 3.2.2 3.2.3 Reset State Power-Dovertion 4. Ba       | PU Operation States  Execution State  Handling States.  Types and Priorities of Exception Handling.  Exception Sources and Vector Table.  Outline of Exception Handling Operation |                   |

# Section 1. CPU

#### 1.1 Overview

The H8/300L CPU at the heart of the H8/300L Series features 16 general registers of 8 bits each (or 8 registers of 16-bits each), and a concise, optimized instruction set geared to high-speed operation.

#### 1.1.1 Features

The H8/300L CPU has the following features.

General register configuration

16 8-bit registers (can be used as 8 16-bit registers)

#### 55 basic instructions

- Multiply and divide instructions

- Powerful bit manipulation instructions

# 8 addressing modes

- Register direct (Rn)

- Register indirect (@Rn)

- Register indirect with displacement (@(d:16, Rn))

- Register indirect with post-increment/pre-decrement (@Rn+/@-Rn)

- Absolute address (@aa:8/@aa:16)

- Immediate (#xx:8/#xx:16)

- Program-counter relative (@(d:8, PC))

- Memory indirect (@@aa:8)

64-kbyte address space

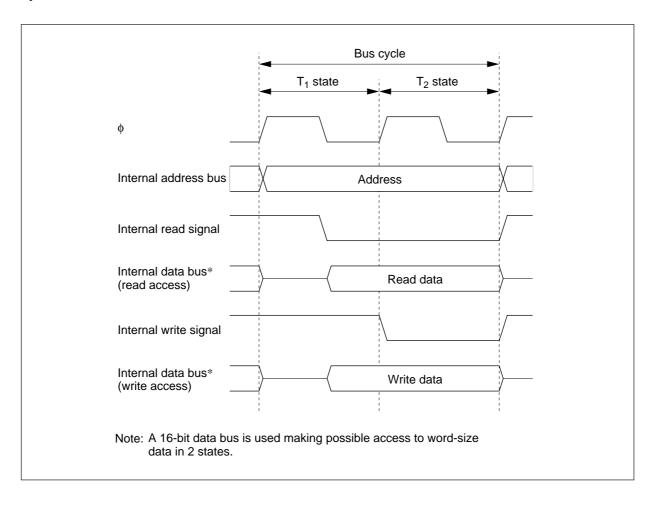

# High-speed operation

- All frequently used instructions are executed in 2 to 4 states

- High-speed operating frequency: 5 MHz

Add/subtract between 8/16-bit registers: 0.4 µs

$8 \times 8$ -bit multiply:  $2.8 \mu s$

$16 \div 8$ -bit divide: 2.8 µs

# Low-power operation

• Transition to power-down state using SLEEP instruction

#### 1.1.2 Data Structure

The H8/300L CPU can process 1-bit data, 4-bit (packed BCD) data, 8-bit (byte) data, and 16-bit (word) data.

- Bit manipulation instructions operate on 1-bit data specified as bit n (n = 0, 1, 2, ..., 7) in a byte operand.

- All operational instructions except ADDS and SUBS can operate on byte data.

- The MOV.W, ADD.W, SUB.W, CMP.W, ADDS, SUBS, MULXU (8 bits  $\times$  8 bits), and DIVXU (16 bits  $\div$  8 bits) instructions operate on word data.

- The DAA and DAS instruction perform decimal arithmetic adjustments on byte data in packed BCD form. Each 4-bit of the byte is treated as a decimal digit.

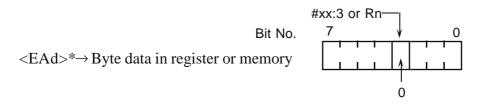

**Data Structure in General Registers:** Data of all the sizes above can be stored in general registers as shown in figure 1-1.

| Data type                                                                                                                        | Register No. | Data format                       |  |  |

|----------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------------------------|--|--|

| 1-Bit data                                                                                                                       | RnH          | 7 0<br>7 6 5 4 3 2 1 0 Don't-care |  |  |

| 1-Bit data                                                                                                                       | RnL          | 7 0<br>Don't-care 7 6 5 4 3 2 1 0 |  |  |

| Byte data                                                                                                                        | RnH          | 7 0                               |  |  |

| Byte data                                                                                                                        | RnL          | Don't-care                        |  |  |

| Word data                                                                                                                        | Rn           | 15 0                              |  |  |

| 4-Bit BCD data                                                                                                                   | RnH          | 7 43 0 Upper Lower Don't-care     |  |  |

| 4-Bit BCD data                                                                                                                   | RnL          | 7 43 0 Don't-care Upper Lower     |  |  |

| RnH: Upper 8 bits of General Register RnL: Lower 8 bits of General Register MSB: Most Significant Bit LSB: Least Significant Bit |              |                                   |  |  |

Figure 1-1. Register Data Structure

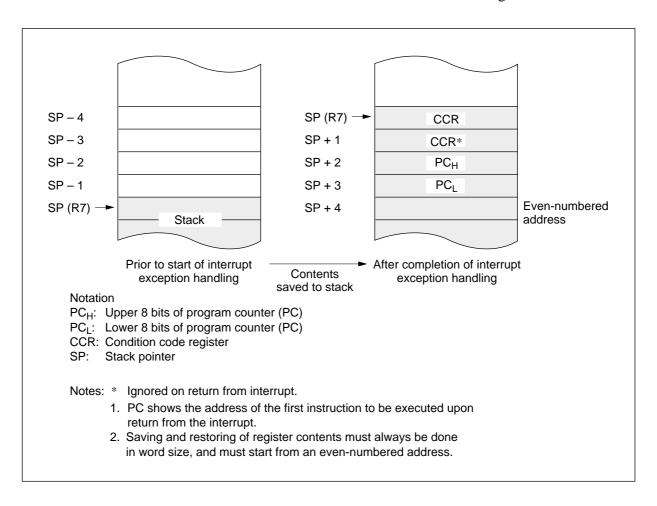

**Data Structure in Memory:** Figure 1-2 shows the structure of data in memory. The H8/300L CPU is able to access word data in memory (MOV.W instruction), but only if the word data starts from an even-numbered address. If an odd address is designated, no address error occurs, but the access is performed starting from the previous even address, with the least significant bit of the address regarded as 0.\* The same applies to instruction codes.

\* Note that the LSIs in the H8/300L Series also contain on-chip peripheral modules for which access in word size is not possible. Details are given in the applicable hardware manual.

| Data type                | Address                     | Data format                                                                                                                                                                                                                                                                                                                                  |

|--------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          |                             | 7 0                                                                                                                                                                                                                                                                                                                                          |

| 1-Bit data               | Address n                   | 76543210                                                                                                                                                                                                                                                                                                                                     |

| Byte data                | Address n                   | M L S S B B B B                                                                                                                                                                                                                                                                                                                              |

| Word data                | Even address<br>Odd address | S Upper 8 bits Lower 8 bits S                                                                                                                                                                                                                                                                                                                |

| Byte data (CCR) on stack | Even address<br>Odd address | S CCR S B CCR* S B B B B CCR* S B B B B CCR* S B B B B B CCR* S B B B B B B B B B B B B B B B B B B |

| Word data on stack       | Even address<br>Odd address | S Upper 8 bits Lower 8 bits S                                                                                                                                                                                                                                                                                                                |

|                          |                             |                                                                                                                                                                                                                                                                                                                                              |

CCR: Condition code register.

Note: Word data must begin at an even address.

\*: Ignored when returned.

Figure 1-2. Memory Data Formats

The stack is always accessed a word at a time. When the CCR is pushed on the stack, two identical copies of the CCR are pushed to make a complete word. When they are returned, the lower byte is ignored.

#### 1.1.3 Address Space

The H8/300L CPU supports a 64-Kbyte address space (program code + data). The memory map differs depending on the particular chip in the H8/300L Series and its operating mode. See the applicable hardware manual for details.

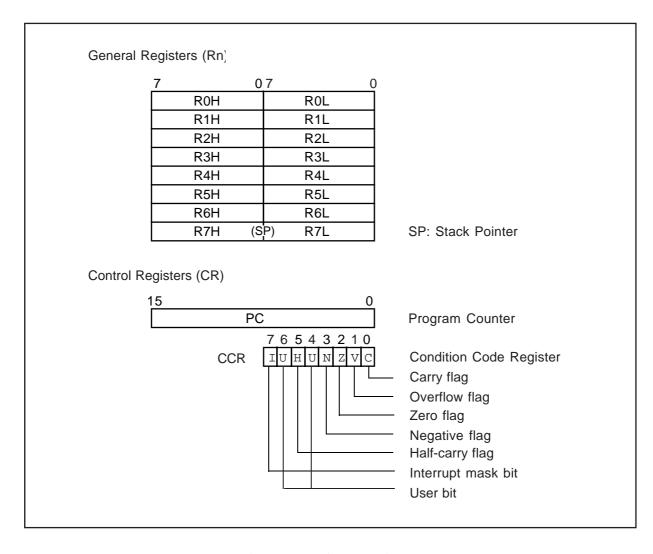

# 1.1.4 Register Configuration

Figure 1-3 shows the register configuration of the H8/300L CPU. There are 16 8-bit general registers (R0H, R0L, ..., R7H, R7L), which can also be accessed as eight 16-bit registers (R0 to R7). There are two control registers: the 16-bit program counter (PC) and the 8-bit condition code register (CCR).

Figure 1-3. CPU Registers

# 1.2 Registers

#### 1.2.1 General Registers

All the general registers can be used as both data registers and address registers. When used as address registers, the general registers are accessed as 16-bit registers (R0 to R7). When used as data registers, they can be accessed as 16-bit registers (R0 to R7), or the high (R0H to R7H) and low (R0L to R7L) bytes can be accessed separately as 8-bit registers. The register length is determined by the instruction.

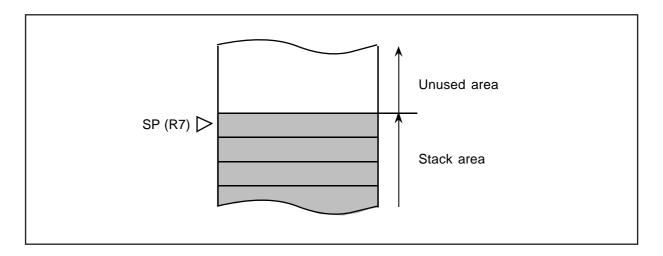

R7 also functions as the stack pointer, used implicitly by hardware in processing interrupts and subroutine calls. In assembly language, the letters SP can be coded as a synonym for R7. As indicated in figure 1-4, R7 (SP) points to the top of the stack.

Figure 1-4. Stack Pointer

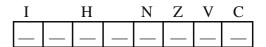

### 1.2.2 Control Registers

The CPU has a 16-bit program counter (PC) and an 8-bit condition code register (CCR).

- (1) **Program Counter (PC):** This 16-bit register indicates the address of the next instruction the CPU will execute. Instructions are fetched by 16-bit (word) access, so the least significant bit of the PC is ignored (always regarded as 0).

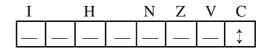

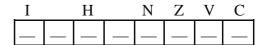

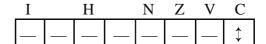

- (2) Condition Code Register (CCR): This 8-bit register indicates the internal status of the CPU with an interrupt mask (I) bit and five flag bits: half-carry (H), negative (N), zero (Z), overflow (V), and carry (C) flags. The two unused bits are available to the user. The bit configuration of the condition code register is shown below.

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|---|

|               | Ι   | U   | Н   | U   | N   | Z   | V   | С   | ] |

| Initial value | 1   | *   | *   | *   | *   | *   | *   | *   | _ |

| Read/Write    | R/W |   |

<sup>\*</sup> Not fixed

**Bit 7—Interrupt Mask Bit (I):** When this bit is set to 1, all interrupts except NMI are masked. This bit is set to 1 automatically at the start of interrupt handling.

**Bits 6 and 4—User Bits (U):** These bits can be written and read by software for its own purposes using LDC, STC, ANDC, ORC, and XORC instructions.

**Bit 5—Half-Carry (H):** This bit is used by add, subtract, and compare instructions to indicate a borrow or carry out of bit 3 or bit 11. It is referenced by the decimal adjust instructions.

**Bit 3—Negative** (N): This bit indicates the value of the most significant bit (sign bit) of the result of an instruction.

**Bit 2—Zero (Z):** This bit is set to 1 to indicate a zero result and cleared to 0 to indicate a nonzero result.

**Bit 1—Overflow** (V): This bit is set to 1 when an arithmetic overflow occurs, and cleared to 0 at other times.

**Bit 0—Carry (C):** This bit is used by:

- Add, subtract, and compare instructions, to indicate a carry or borrow at the most significant bit

- Shift and rotate instructions, to store the value shifted out of the most or least significant bit

- Bit manipulation instructions, as a bit accumulator

Note that some instructions involve no flag changes. The flag operations with each instruction are indicated in the individual instruction descriptions that follow in section 2, Instruction Set. CCR is used by LDC, STC, ANDC, ORC, and XORC instructions. The N, Z, V, and C flags are used by the conditional branch instruction (Bcc).

#### 1.2.3 Initial Register Values

When the CPU is reset, the program counter (PC) is loaded from the vector table and the interrupt mask bit (I) in CCR is set to 1. The other CCR bits and the general registers are not initialized.

The initial value of the stack pointer (R7) is not fixed. To prevent program crashes the stack pointer should be initialized by software, by the first instruction executed after a reset.

# 1.3 Instructions

#### Features:

- The H8/300L CPU has a concise set of 55 instructions.

- A general-register architecture is adopted.

- All instructions are 2 or 4 bytes long.

- Fast multiply/divide instructions and extensive bit manipulation instructions are supported.

- Eight addressing modes are supported.

# **1.3.1** Types of Instructions

Table 1-1 classifies the H8/300L instructions by type. Section 2, Instruction Set, gives detailed descriptions.

**Table 1-1. Instruction Classification**

| Function             | Instructions                                | Types |

|----------------------|---------------------------------------------|-------|

| Data transfer        | MOV, POP*, PUSH*                            | 1     |

| Arithmetic operation | SADD, SUB, ADDX, SUBX, INC, DEC, ADDS, SUBS | , 14  |

|                      | DAA, DAS, MULXU, DIVXU, CMP, NEG            |       |

| Logic operations     | AND, OR, XOR, NOT                           | 4     |

| Shift                | SHAL, SHAR, SHLL, SHLR, ROTL, ROTR, ROTXL,  | 8     |

|                      | ROTXR                                       |       |

| Bit manipulation     | BSET, BCLR, BNOT, BTST, BAND, BIAND, BOR    | 14    |

|                      | BIOR, BXOR, BIXOR, BLD, BILD, BST, BIST     |       |

| Branch               | Bcc**, JMP, BSR, JSR, RTS                   | 5     |

| System control       | RTE, SLEEP, LDC, STC, ANDC, ORC, XORC, NOP  | 8     |

| Block data transfer  | EEPMOV                                      | 1     |

|                      | Total                                       | 55    |

<sup>\*</sup> POP Rn is equivalent to MOV.W @SP+, Rn. PUSH Rn is equivalent to MOV.W Rn, @-SP.

<sup>\*\*</sup> Bcc is a conditional branch instruction in which cc represents a condition.

# **1.3.2 Instruction Functions**

Tables 1-2 to 1-9 give brief descriptions of the instructions in each functional group. The following notation is used.

| Notati        | Notation                                   |  |  |  |  |

|---------------|--------------------------------------------|--|--|--|--|

| Rd            | General register (destination)             |  |  |  |  |

| Rs            | General register (source)                  |  |  |  |  |

| Rn            | General register                           |  |  |  |  |

| (EAd)         | Destination operand                        |  |  |  |  |

| (EAs)         | Source operand                             |  |  |  |  |

| CCR           | Condition code register                    |  |  |  |  |

| N             | N (negative) bit of CCR                    |  |  |  |  |

| Z             | Z (zero) bit of CCR                        |  |  |  |  |

| $\frac{Z}{V}$ | V (overflow) bit of CCR                    |  |  |  |  |

| С             | C (carry) bit of CCR                       |  |  |  |  |

| PC            | Program counter                            |  |  |  |  |

| SP            | Stack pointer (R7)                         |  |  |  |  |

| #Imm          | Immediate data                             |  |  |  |  |

| op            | Operation field                            |  |  |  |  |

| disp          | Displacement                               |  |  |  |  |

| +             | Addition                                   |  |  |  |  |

| _             | Subtraction                                |  |  |  |  |

| ×             | Multiplication                             |  |  |  |  |

| ×<br>÷        | Division                                   |  |  |  |  |

| ^             | AND logical                                |  |  |  |  |

| <u></u>       | OR logical                                 |  |  |  |  |

| $\oplus$      | Exclusive OR logical                       |  |  |  |  |

| $\rightarrow$ | Move                                       |  |  |  |  |

| $\overline{}$ | Not                                        |  |  |  |  |

| :3, :8, :     | :3, :8, :16 3-bit, 8-bit, or 16-bit length |  |  |  |  |

**Table 1-2. Data Transfer Instructions**

| Instruction | Size* | Function                                                            |

|-------------|-------|---------------------------------------------------------------------|

| MOV         | B/W   | $(EAs) \rightarrow Rd, Rs \rightarrow (EAd)$                        |

|             |       | Moves data between two general registers or between a general       |

|             |       | register and memory, or moves immediate data to a general register. |

|             |       | The Rn, @Rn, @(d:16, Rn), @aa:16, #xx:8 or #xx:16, @-Rn, and        |

|             |       | @Rn+ addressing modes are available for byte or word data. The      |

|             |       | @aa:8 addressing mode is available for byte data only.              |

|             |       | The @-R7 and @R7+ modes require word operands. Do not               |

|             |       | specify byte size for these two modes.                              |

| POP         | W     | $@SP+ \longrightarrow Rn$                                           |

|             |       | Pops a 16-bit general register from the stack.                      |

|             |       | Equivalent to MOV.W @SP+, Rn.                                       |

| PUSH        | W     | $Rn \rightarrow @-SP$                                               |

|             |       | Pushes a 16-bit general register onto the stack.                    |

|             |       | Equivalent to MOV.W Rn, @-SP.                                       |

B: Byte W: Word

**Table 1-3. Arithmetic Instructions**

| Size* | Function                                                                  |

|-------|---------------------------------------------------------------------------|

| B/W   | $Rd \pm Rs \rightarrow Rd, Rd + \#Imm \rightarrow Rd$                     |

|       | Performs addition or subtraction on data in two general registers,        |

|       | or addition on immediate data and data in a general register.             |

|       | Immediate data cannot be subtracted from data in a general register.      |

|       | Word data can be added or subtracted only when both words are in          |

|       | general registers.                                                        |

| В     | $Rd \pm Rs \pm C \rightarrow Rd, Rd \pm \#Imm \pm C \rightarrow Rd$       |

|       | Performs addition or subtraction with carry or borrow on byte data        |

|       | in two general registers, or addition or subtraction on immediate data    |

|       | and data in a general register.                                           |

| В     | $Rd \pm 1 \rightarrow Rd$                                                 |

|       | Increments or decrements a general register.                              |

| W     | $Rd \pm 1 \rightarrow Rd, Rd \pm 2 \rightarrow Rd$                        |

|       | Adds or subtracts immediate data to or from data in a general             |

|       | register. The immediate data must be 1 or 2.                              |

| В     | Rd decimal adjust $\rightarrow$ Rd                                        |

|       | Decimal-adjusts (adjusts to packed BCD) an addition or subtraction        |

|       | result in a general register by referring to the condition code register. |

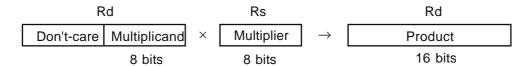

| В     | $Rd \times Rs \rightarrow Rd$                                             |

|       | Performs 8-bit $\times$ 8-bit unsigned multiplication on data in two      |

|       | general registers, providing a 16-bit result.                             |

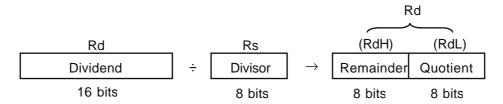

| В     | $Rd \div Rs \longrightarrow Rd$                                           |

|       | Performs 16-bit ÷ 8-bit unsigned division on data in two general          |

|       | registers, providing an 8-bit quotient and 8-bit remainder.               |

| B/W   | Rd-Rs, $Rd-#Imm$                                                          |

|       | Compares data in a general register with data in another general          |

|       | register or with immediate data. Word data can be compared only           |

|       | between two general registers.                                            |

| В     | $0-Rd \rightarrow Rd$                                                     |

|       | Obtains the two's complement (arithmetic complement) of data in a         |

|       | general register.                                                         |

|       | B/W B B B B                                                               |

B: Byte W: Word

**Table 1-4. Logic Operation Instructions**

| Instruction | Size* | Function                                                                           |

|-------------|-------|------------------------------------------------------------------------------------|

| AND         | В     | $Rd \ _{\wedge} Rs \ _{\rightarrow} Rd,  Rd \ _{\wedge} \#Imm \ _{\rightarrow} Rd$ |

|             |       | Performs a logical AND operation on a general register and                         |

|             |       | another general register or immediate data.                                        |

| OR          | В     | Rd $_{\vee}$ Rs $_{\rightarrow}$ Rd, Rd $_{\vee}$ #Imm $_{\rightarrow}$ Rd         |

|             |       | Performs a logical OR operation on a general register and another                  |

|             |       | general register or immediate data.                                                |

| XOR         | В     | $Rd \oplus Rs \rightarrow Rd$ , $Rd \oplus \#Imm \rightarrow Rd$                   |

|             |       | Performs a logical exclusive OR operation on a general register                    |

|             |       | and another general register or immediate data.                                    |

| NOT         | В     | $\neg \operatorname{Rd} \longrightarrow \operatorname{Rd}$                         |

|             |       | Obtains the one's complement (logical complement) of general                       |

|             |       | register contents.                                                                 |

B: Byte

**Table 1-5. Shift Instructions**

| Instruction | Size* | Function                                                             |

|-------------|-------|----------------------------------------------------------------------|

| SHAL        | В     | $Rd 	ext{ shift } \rightarrow Rd$                                    |

| SHAR        |       | Performs an arithmetic shift operation on general register contents. |

| SHLL        | В     | $Rd 	ext{ shift } \rightarrow Rd$                                    |

| SHLR        |       | Performs a logical shift operation on general register contents.     |

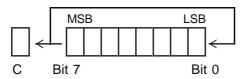

| ROTL        | В     | Rd rotate $\rightarrow$ Rd                                           |

| ROTR        |       | Rotates general register contents.                                   |

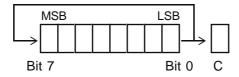

| ROTXL       | В     | Rd rotate through carry $\rightarrow$ Rd                             |

| ROTXR       |       | Rotates general register contents through the C (carry) bit.         |

\* Size: Operand size

B: Byte

**Table 1-6. Bit Manipulation Instructions**

| Instruction | Size* | Function                                                                                                                                      |

|-------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|

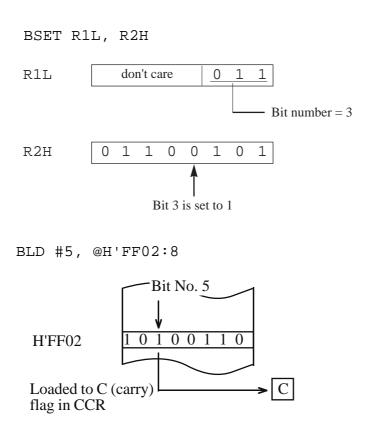

| BSET        | В     | $1 \rightarrow (< bit-No. > of < EAd >)$                                                                                                      |

|             |       | Sets a specified bit in a general register or memory to 1. The bit is                                                                         |

|             |       | specified by a bit number, given in 3-bit immediate data or the lower                                                                         |

|             |       | three bits of a general register.                                                                                                             |

| BCLR        | В     | $0 \rightarrow ( of )$                                                                                                                        |

|             |       | Clears a specified bit in a general register or memory to 0. The bit                                                                          |

|             |       | is specified by a bit number, given in 3-bit immediate data or the lower                                                                      |

|             |       | three bits of a general register.                                                                                                             |

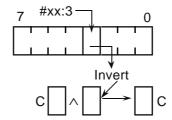

| BNOT        | В     | $\neg(\langle bit\text{-No.}\rangle \text{ of }\langle EAd\rangle) \rightarrow (\langle bit\text{-No.}\rangle \text{ of }\langle EAd\rangle)$ |

|             |       | Inverts a specified bit in a general register or memory. The bit is                                                                           |

|             |       | specified by a bit number, given in 3-bit immediate data or the lower                                                                         |

|             |       | three bits of a general register.                                                                                                             |

| BTST        | В     | $\neg (< bit-No. > of < EAd >) \rightarrow Z$                                                                                                 |

|             |       | Tests a specified bit in a general register or memory and sets or                                                                             |

|             |       | clears the Z flag accordingly. The bit is specified by a bit number,                                                                          |

|             |       | given in 3-bit immediate data or the lower three bits of a general                                                                            |

|             |       | register.                                                                                                                                     |

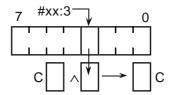

| BAND        | В     | $C \land (< bit-No. > of < EAd >) \rightarrow C$                                                                                              |

|             |       | ANDs the C flag with a specified bit in a general register or                                                                                 |

|             |       | memory.                                                                                                                                       |

| BIAND       | В     | $C \cap (\langle \text{bit-No.} \rangle \text{ of } \langle \text{EAd} \rangle)] \rightarrow C$                                               |

|             |       | ANDs the C flag with the inverse of a specified bit in a general                                                                              |

|             |       | register or memory.                                                                                                                           |

|             |       | The bit number is specified by 3-bit immediate data.                                                                                          |

| BOR         | В     | $C_{\lor}$ ( <bit-no.> of <ead>) <math>\rightarrow</math> <math>C</math></ead></bit-no.>                                                      |

|             |       | ORs the C flag with a specified bit in a general register or memory.                                                                          |

| BIOR        | В     | $C \setminus [\neg (< bit-No. > of < EAd >)] \rightarrow C$                                                                                   |

|             |       | ORs the C flag with the inverse of a specified bit in a general                                                                               |

|             |       | register or memory.                                                                                                                           |

|             |       | The bit number is specified by 3-bit immediate data.                                                                                          |

**Table 1-6. Bit Manipulation Instructions (Cont.)**

| Instruction | Size* | Function                                                                                         |

|-------------|-------|--------------------------------------------------------------------------------------------------|

| BXOR        | В     | $C \oplus (\langle bit\text{-No.}\rangle \text{ of }\langle EAd \rangle) \rightarrow C$          |

|             |       | Exclusive-ORs the C flag with a specified bit in a general register                              |

|             |       | or memory.                                                                                       |

| BIXOR       | В     | $C \oplus [\neg (\langle bit\text{-No.} \rangle \text{ of } \langle EAd \rangle)] \rightarrow C$ |

|             |       | Exclusive-ORs the C flag with the inverse of a specified bit in a                                |

|             |       | general register or memory.                                                                      |

|             |       | The bit number is specified by 3-bit immediate data.                                             |

| BLD         | В     | $(<$ bit-No. $>$ of $<$ EAd $>) \rightarrow C$                                                   |

|             |       | Copies a specified bit in a general register or memory to the C flag.                            |

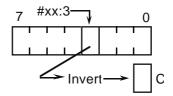

| BILD        | В     | $\neg (< bit-No. > of < EAd >) \rightarrow C$                                                    |

|             |       | Copies the inverse of a specified bit in a general register or                                   |

|             |       | memory to the C flag.                                                                            |

|             |       | The bit number is specified by 3-bit immediate data.                                             |

| BST         | В     | $C \rightarrow ( of < EAd>)$                                                                     |

|             |       | Copies the C flag to a specified bit in a general register or memory.                            |

| BIST        | В     | $\neg C \rightarrow (< bit-No. > of < EAd >)$                                                    |

|             |       | Copies the inverse of the C flag to a specified bit in a general                                 |

|             |       | register or memory.                                                                              |

|             |       | The bit number is specified by 3-bit immediate data.                                             |

B: Byte

**Table 1-7. Branching Instructions**

| Instruction | Size | Function          |                                                                   |                              |  |  |  |  |  |  |

|-------------|------|-------------------|-------------------------------------------------------------------|------------------------------|--|--|--|--|--|--|

| Bcc         | _    | Branches if condi | Branches if condition cc is true. The branching conditions are as |                              |  |  |  |  |  |  |

|             |      | follows.          |                                                                   |                              |  |  |  |  |  |  |

|             |      |                   |                                                                   |                              |  |  |  |  |  |  |

|             |      | Mnemonic          | Description                                                       | Condition                    |  |  |  |  |  |  |

|             |      | BRA (BT)          | Always (True)                                                     | Always                       |  |  |  |  |  |  |

|             |      | BRN (BF)          | Never (False)                                                     | Never                        |  |  |  |  |  |  |

|             |      | BHI               | High                                                              | $C \vee Z = 0$               |  |  |  |  |  |  |

|             |      | BLS               | Low or Same                                                       | $C_{\vee}Z=1$                |  |  |  |  |  |  |

|             |      | BCC (BHS)         | Carry Clear                                                       | C = 0                        |  |  |  |  |  |  |

|             |      |                   | (High or Same)                                                    |                              |  |  |  |  |  |  |

|             |      | BCS (BLO)         | Carry Set (Low)                                                   | C = 1                        |  |  |  |  |  |  |

|             |      | BNE               | Not Equal                                                         | Z = 0                        |  |  |  |  |  |  |

|             |      | BEQ               | Equal                                                             | Z = 1                        |  |  |  |  |  |  |

|             |      | BVC               | Overflow Clear                                                    | V = 0                        |  |  |  |  |  |  |

|             |      | BVS               | Overflow Set                                                      | V = 1                        |  |  |  |  |  |  |

|             |      | BPL               | Plus                                                              | N = 0                        |  |  |  |  |  |  |

|             |      | BMI               | Minus                                                             | N = 1                        |  |  |  |  |  |  |

|             |      | BGE               | Greater or Equal                                                  | $N \oplus V = 0$             |  |  |  |  |  |  |

|             |      | BLT               | Less Than                                                         | $N \oplus V = 1$             |  |  |  |  |  |  |

|             |      | BGT               | Greater Than                                                      | $Z_{\vee}(N_{\bigoplus}V)=0$ |  |  |  |  |  |  |

|             |      | BLE               | Less or Equal                                                     | $Z_{\vee}(N_{\bigoplus}V)=1$ |  |  |  |  |  |  |

|             |      |                   |                                                                   |                              |  |  |  |  |  |  |

| JMP         |      |                   | itionally to a specified ad                                       |                              |  |  |  |  |  |  |

| BSR         | _    |                   | proutine at a specified dis                                       | placement from the current   |  |  |  |  |  |  |

|             |      | address.          |                                                                   |                              |  |  |  |  |  |  |

| JSR         | _    |                   | proutine at a specified add                                       | dress.                       |  |  |  |  |  |  |

| RTS         |      | Returns from a su | ibroutine.                                                        |                              |  |  |  |  |  |  |

**Table 1-8. System Control Instructions**

| Instruction | Size* | Function                                                            |  |  |  |  |

|-------------|-------|---------------------------------------------------------------------|--|--|--|--|

| RTE         | _     | Returns from an exception handling routine.                         |  |  |  |  |

| SLEEP       | _     | Causes a transition to power-down state.                            |  |  |  |  |

| LDC         | В     | $Rs \rightarrow CCR$ , #Imm $\rightarrow CCR$                       |  |  |  |  |

|             |       | Moves immediate data or general register contents to the condition  |  |  |  |  |

|             |       | code register.                                                      |  |  |  |  |

| STC         | В     | CCR  Rd                                                             |  |  |  |  |

|             |       | Copies the condition code register to a specified general register. |  |  |  |  |

| ANDC        | В     | $CCR \wedge \#Imm \rightarrow CCR$                                  |  |  |  |  |

|             |       | Logically ANDs the condition code register with immediate data.     |  |  |  |  |

| ORC         | В     | $CCR \downarrow \#Imm \rightarrow CCR$                              |  |  |  |  |

|             |       | Logically ORs the condition code register with immediate data.      |  |  |  |  |

| XORC        | В     | $CCR \oplus \#Imm \rightarrow CCR$                                  |  |  |  |  |

|             |       | Logically exclusive-ORs the condition code register with immediate  |  |  |  |  |

|             |       | data.                                                               |  |  |  |  |

| NOP         |       | $PC + 2 \rightarrow PC$                                             |  |  |  |  |

|             |       | Only increments the program counter.                                |  |  |  |  |

B: Byte

**Table 1-9. Block Data Transfer Instruction**

| Instruction | Size | Function                                                                  |

|-------------|------|---------------------------------------------------------------------------|

| EEPMOV      | _    | if $R4L \neq 0$ then                                                      |

|             |      | repeat $@R5+ \rightarrow @R6+$                                            |

|             |      | $R4L-1 \xrightarrow{r} R4L$                                               |

|             |      | until $R4L = 0$                                                           |

|             |      | else next;                                                                |

|             |      | Moves a data block according to parameters set in general registers       |

|             |      | R4L, R5, and R6.                                                          |

|             |      | R4L: size of block (bytes)                                                |

|             |      | R5: starting source address                                               |

|             |      | R6: starting destination address                                          |

|             |      | Execution of the next instruction starts as soon as the block transfer is |

|             |      | completed.                                                                |

|             |      | This instruction is for writing to the large-capacity EEPROM provided     |

|             |      | on chip with some models in the H8/300L Series. For details see the       |

|             |      | applicable hardware manual.                                               |

**Notes on Bit Manipulation Instructions:** BSET, BCLR, BNOT, BST, and BIST are read-modify-write instructions. They read a byte of data, modify one bit in the byte, then write the byte back. Care is required when these instructions are applied to registers with write-only bits and to the I/O port registers.

| Sequence |        | Operation                                                  |  |  |  |  |

|----------|--------|------------------------------------------------------------|--|--|--|--|

| 1        | Read   | Read one data byte at the specified address                |  |  |  |  |

| 2        | Modify | Modify one bit in the data byte                            |  |  |  |  |

| 3        | Write  | Write the modified data byte back to the specified address |  |  |  |  |

**Example 1:** BCLR is executed to clear bit 0 in port control register 4 (PCR4) under the following conditions.

P47: Input pin, Low

P46: Input pin, High

P45 – P40: Output pins, Low

The intended purpose of this BCLR instruction is to switch P40 from output to input.

# **Before Execution of BCLR Instruction**

|              | P47   | P46   | P45    | P44    | P43    | P42    | P41    | P40    |

|--------------|-------|-------|--------|--------|--------|--------|--------|--------|

| Input/output | Input | Input | Output | Output | Output | Output | Output | Output |

| Pin state    | Low   | High  | Low    | Low    | Low    | Low    | Low    | Low    |

| PCR4         | 0     | 0     | 1      | 1      | 1      | 1      | 1      | 1      |

| PDR4         | 1     | 0     | 0      | 0      | 0      | 0      | 0      | 0      |

#### **Execution of BCLR Instruction**

BCLR #0 @PCR4 ; clear bit 0 in PCR4

### **After Execution of BCLR Instruction**

|              | P47    | P46    | P45    | P44    | P43    | P42    | P41    | P40   |

|--------------|--------|--------|--------|--------|--------|--------|--------|-------|

| Input/output | Output | Input |

| Pin state    | Low    | High   | Low    | Low    | Low    | Low    | Low    | High  |

| PCR4         | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 0     |

| PDR4         | 1      | 0      | 0      | 0      | 0      | 0      | 0      | 0     |

**Explanation:** To execute the BCLR instruction, the CPU begins by reading PCR4. Since PCR4 is a write-only register, it is read as H'FF, even though its true value is H'3F.

Next the CPU clears bit 0 of the read data, changing the value to H'FE.

Finally, the CPU writes this value (H'FE) back to PCR4 to complete the BCLR instruction.

As a result, bit 0 in PCR4 is cleared to 0, making P4<sup>0</sup> an input pin. In addition, bits 7 and 6 in PCR4 are set to 1, making P4<sup>7</sup> and P4<sup>6</sup> output pins.

**Example 2:** BSET is executed to set bit 0 in the port 4 port data register (PDR4) under the following conditions.

P47: Input pin, Low

P46: Input pin, High

P45 – P40: Output pins, Low

The intended purpose of this BSET instruction is to switch the output level at P40 from Low to High.

## **Before Execution of BSET Instruction**

|              | P47   | P46   | P45    | P44    | P43    | P42    | P41    | P40    |

|--------------|-------|-------|--------|--------|--------|--------|--------|--------|

| Input/output | Input | Input | Output | Output | Output | Output | Output | Output |

| Pin state    | Low   | High  | Low    | Low    | Low    | Low    | Low    | Low    |

| PCR4         | 0     | 0     | 1      | 1      | 1      | 1      | 1      | 1      |

| PDR4         | 1     | 0     | 0      | 0      | 0      | 0      | 0      | 0      |

#### **Execution of BSET Instruction**

BSET #0 @PDR4 ; set bit 0 in port 4 port data register

#### **After Execution of BSET Instruction**

|              | P47   | P46   | P45    | P44    | P43    | P42    | P41    | P40    |

|--------------|-------|-------|--------|--------|--------|--------|--------|--------|

| Input/output | Input | Input | Output | Output | Output | Output | Output | Output |

| Pin state    | Low   | High  | Low    | Low    | Low    | Low    | Low    | High   |

| PCR4         | 0     | 0     | 1      | 1      | 1      | 1      | 1      | 1      |

| PDR4         | 0     | 1     | 0      | 0      | 0      | 0      | 0      | 1      |

**Explanation:** To execute the BSET instruction, the CPU begins by reading port 4. Since P4<sup>7</sup> and P4<sup>6</sup> are input pins, the CPU reads the level of these pins directly, not the value in the port data register. It reads P4<sup>7</sup> as Low (0) and P4<sup>6</sup> as High (1).

Since P4<sup>5</sup> to P4<sup>0</sup> are output pins, for these pins the CPU reads the value in PDR4. The CPU therefore reads the value of port 4 as H'40, although the actual value in PDR4 is H'80.

Next the CPU sets bit 0 of the read data to 1, changing the value to H'41.

Finally, the CPU writes this value (H'41) back to PDR4 to complete the BSET instruction.

As a result, bit 0 in PDR4 is set to 0, switching pin P40 to High output. However, bits 7 and 6 in PDR4 change their values.

#### 1.3.3 Basic Instruction Formats

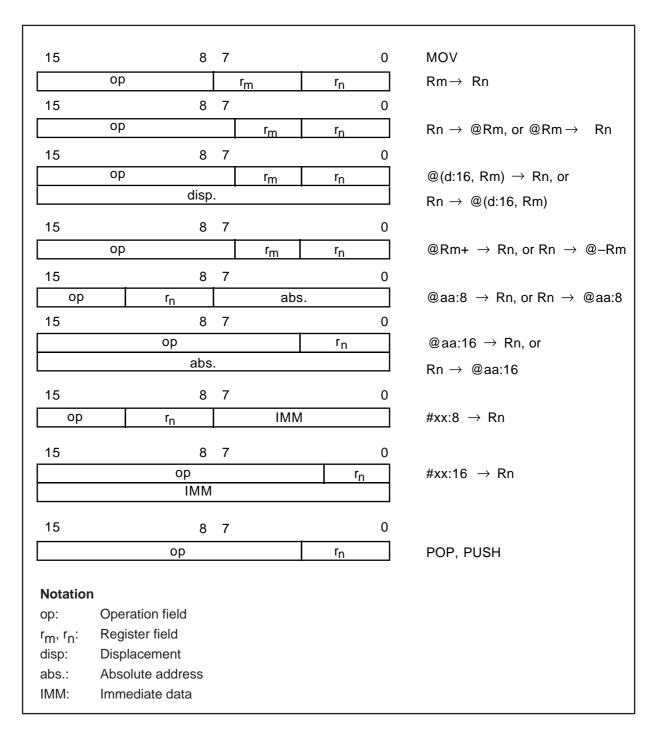

# (1) Format of Data Transfer Instructions

Figure 1-5 shows the format used for data transfer instructions.

Figure 1-5. Instruction Format of Data Transfer Instructions

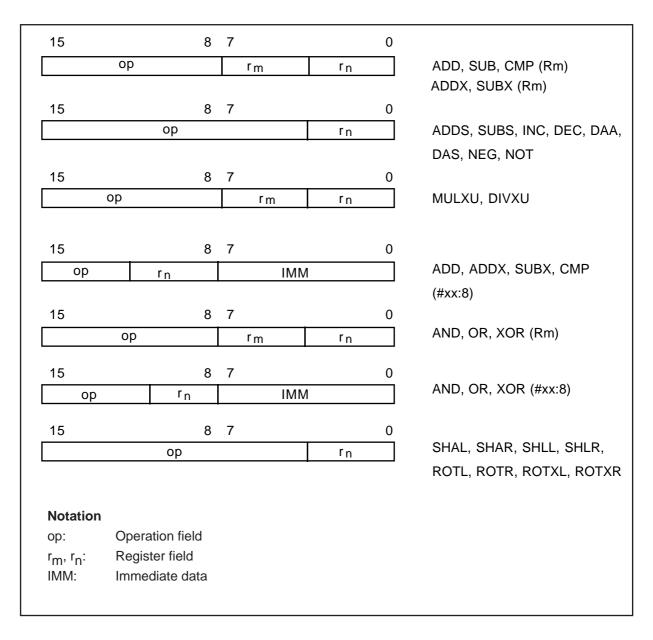

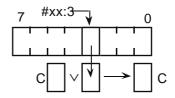

# (2) Format of Arithmetic, Logic Operation, and Shift Instructions

Figure 1-6 shows the format used for arithmetic, logic operation, and shift instructions.

Figure 1-6. Instruction Format of Arithmetic, Logic, and Shift Instructions

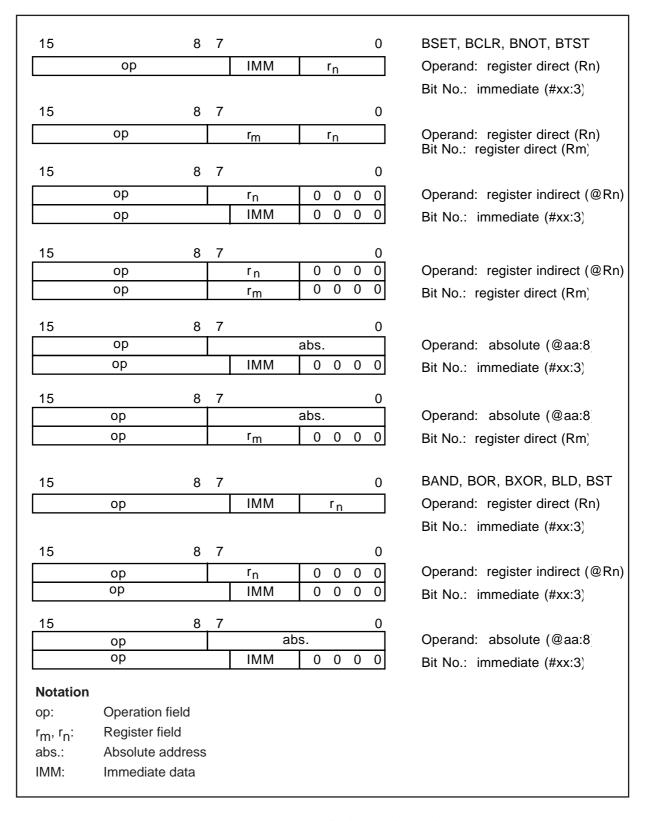

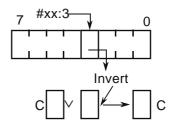

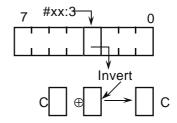

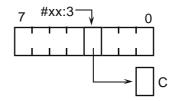

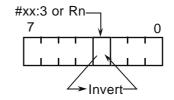

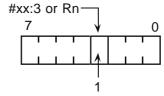

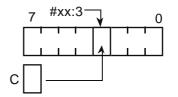

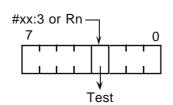

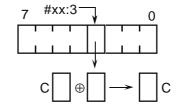

# (3) Format of Bit Manipulation Instructions

Figure 1-7 shows the format used for bit manipulation instructions.

Figure 1-7. Instruction Format of Bit Manipulation Instructions

Figure 1-7. Instruction Format of Bit Manipulation Instructions (Cont.)

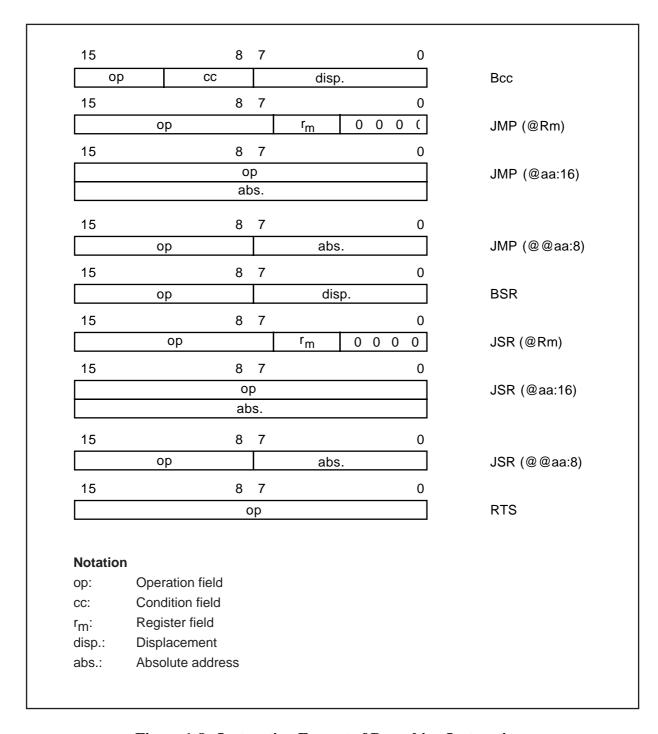

# (4) Format of Branching Instructions

Figure 1-8 shows the format used for branching instructions.

Figure 1-8. Instruction Format of Branching Instructions

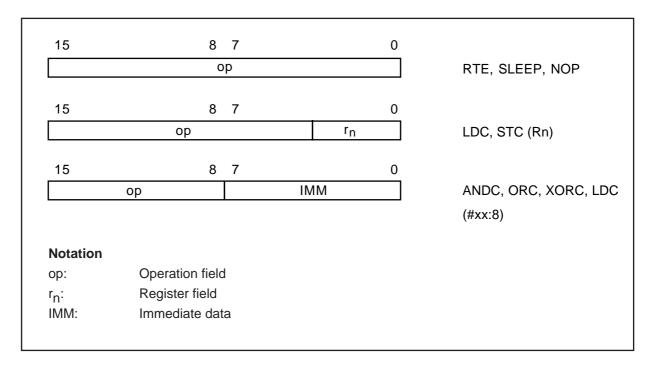

# (5) Format of System Control Instructions

Figure 1-9 shows the format used for system control instructions.

Figure 1-9. Instruction Format of System Control Instructions

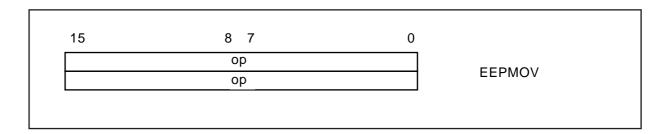

# (6) Format of Block Data Transfer Instruction

Figure 1-10 shows the format used for the block data transfer instruction.

Figure 1-10. Instruction Format of Block Data Transfer Instruction

# 1.3.4 Addressing Modes and Effective Address Calculation

Table 1-10 lists the eight addressing modes and their assembly-language notation. Each instruction can use a specific subset of these addressing modes.

Arithmetic, logic, and shift instructions use register direct addressing (1). The ADD.B, ADDX, SUBX, CMP.B, AND, OR, and XOR instructions can also use immediate addressing (6).

The MOV instruction uses all the addressing modes except program-counter relative (7) and memory indirect (8).

Bit manipulation instructions use register direct (1), register indirect (2), or absolute (5) addressing to identify a byte operand and 3-bit immediate addressing to identify a bit within the byte. The BSET, BCLR, BNOT, and BTST instructions can also use register direct addressing (1) to identify the bit.

Table 1-10. Addressing Modes

| No. | Mode                                       | Notation             |

|-----|--------------------------------------------|----------------------|

| (1) | Register direct                            | Rn                   |

| (2) | Register indirect                          | @Rn                  |

| (3) | Register indirect with 16-bit displacement | @(d:16, Rn)          |

| (4) | Register indirect with post-increment      | @Rn+                 |

|     | Register indirect with pre-decrement       | @-Rn                 |

| (5) | Absolute address (8 or 16 bits)            | @aa:8, @aa:16        |

| (6) | Immediate (3-, 8-, or 16-bit data)         | #xx:3, #xx:8, #xx:16 |

| (7) | PC-relative (8-bit displacement)           | @(d:8, PC)           |

| (8) | Memory indirect                            | @@aa:8               |

- (1) **Register Direct—Rn:** The register field of the instruction specifies an 8- or 16-bit general register containing the operand. In most cases the general register is accessed as an 8-bit register. Only the MOV.W, ADD.W, SUB.W, CMP.W, ADDS, SUBS, MULXU (8 bits  $\times$  8 bits), and DIVXU (16 bits  $\div$  8 bits) instructions have 16-bit operands.

- (2) **Register indirect**—@Rn: The register field of the instruction specifies a 16-bit general register containing the address of the operand.

(3) Register Indirect with Displacement—@(d:16, Rn): This mode, which is used only in MOV instructions, is similar to register indirect but the instruction has a second word (bytes 3 and 4) which is added to the contents of the specified general register to obtain the operand address. For the MOV.W instruction, the resulting address must be even.

# (4) Register Indirect with Post-Increment or Pre-Decrement—@Rn+ or @-Rn:

- Register indirect with post-increment—@Rn+

The @Rn+ mode is used with MOV instructions that load registers from memory.

It is similar to the register indirect mode, but the 16-bit general register specified in the register field of the instruction is incremented after the operand is accessed. The size of the increment is 1 or 2 depending on the size of the operand: 1 for a byte operand; 2 for a word operand. For a word operand, the original contents of the 16-bit general register must be even.

- Register indirect with pre-decrement—@—Rn

The @—Rn mode is used with MOV instructions that store register contents to memory.

It is similar to the register indirect mode, but the 16-bit general register specified in the register field of the instruction is decremented before the operand is accessed. The size of the decrement is 1 or 2 depending on the size of the operand: 1 for a byte operand; 2 for a word operand. For a word operand, the original contents of the 16-bit general register must be even.

- (5) Absolute Address—@aa:8 or @aa:16: The instruction specifies the absolute address of the operand in memory. The @aa:8 mode uses an 8-bit absolute address of the form H'FFxx. The upper 8 bits are assumed to be 1, so the possible address range is H'FF00 to H'FFFF (65280 to 65535). The MOV.B, MOV.W, JMP, and JSR instructions can use 16-bit absolute addresses.

- (6) **Immediate**—#xx:8 or #xx:16: The instruction contains an 8-bit operand in its second byte, or a 16-bit operand in its third and fourth bytes. Only MOV.W instructions can contain 16-bit immediate values.

The ADDS and SUBS instructions implicitly contain the value 1 or 2 as immediate data. Some bit manipulation instructions contain 3-bit immediate data (#xx:3) in the second or fourth byte of the instruction, specifying a bit number.

- (7) **PC-Relative**—@(**d:8, PC**): This mode is used to generate branch addresses in the Bcc and BSR instructions. An 8-bit value in byte 2 of the instruction code is added as a sign-extended value to the program counter contents. The result must be an even number. The possible branching range is -126 to +128 bytes (-63 to +64 words) from the current address.

- (8) Memory Indirect—@@aa:8: This mode can be used by the JMP and JSR instructions. The second byte of the instruction code specifies an 8-bit absolute address from H'0000 to H'00FF (0 to 255). Note that the initial part of the area from H'0000 to H'00FF contains the exception vector table. See the applicable hardware manual for details. The word located at this address contains the branch address.

If an odd address is specified as a branch destination or as the operand address of a MOV.W instruction, the least significant bit is regarded as 0, causing word access to be performed at the address preceding the specified address. See the memory data structure description in section 1.1.2, Data Structure.

#### **Effective Address Calculation**

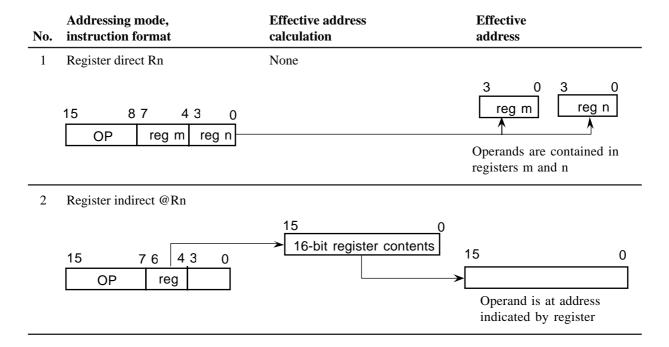

Table 1-11 explains how the effective address is calculated in each addressing mode.

**Table 1-11. Effective Address Calculation (1)**

**Table 1-11. Effective Address Calculation (2)**

Addressing mode, Effective address **Effective** instruction format calculation address No. Register indirect with displacement 3 @(d:16, Rn) 15 0 16-bit register contents 15 0 4 3 7 6 15 16-bit displacement Operand address is sum reg OP of register contents and disp displacement Register indirect with pre-decrement @-Rn 15 16-bit register contents 15 0 15 7 6 4 3 OP reg 1 or 2' Register is decremented before operand access Register indirect with post-increment @Rn+15 0 15 16-bit register contents 15 7 6 4 3 0 Register is incremented reg OP after operand access 1 or 2 \* 1 for a byte operand, 2 for a word operand 5 Absolute address None @aa:8 15 8 7 0 H'FF 15 8 7 0 OP abs Operand address is in range from H'FF00 to H'FFFF Absolute address @aa:16 0 15 0 15 OP abs Any address

**Table 1-11. Effective Address Calculation (3)**

| No. | Addressing mode, instruction format | Effective address calculation | Effective address                |

|-----|-------------------------------------|-------------------------------|----------------------------------|

| 6   | Immediate #xx:8.                    | None                          |                                  |

|     | 15 8 7 IMM                          | 0                             | Operand is 1-byte immediate data |

|     | Immediate #xx:16                    | None                          |                                  |

|     | 15                                  | 0                             |                                  |

|     | OP                                  |                               | Operand is 2-byte                |

|     | IMM                                 |                               | immediate data                   |

| 7   | PC-relative @(d:8, PC)              | 15 PC contents                | 0 15 0                           |

|     | 15 8 7 OP disp                      | Sign extension disp           | Destination address              |

| 8   | Memory indirect @@aa:8              |                               |                                  |

|     | 15 8 7 OP abs                       | 15 8 7 W                      | 0                                |

15

0

15

Destination address

0

16-bit memory contents

reg, regm, regn: General register op: Operation field disp: Displacement abs: Absolute address IMM: Immediate data

# **Section 2. Instruction Set**

# 2.1 Explanation Format

Section 2 gives full descriptions of all the H8/300L Series instructions, presenting them in alphabetic order. Each instruction is explained in a table like the following:

## ADD (add binary) (byte)

**ADD**

#### **Operation**

$Rd + (EAs) \rightarrow Rd$

### **Assembly-Language Format**

ADD.B <EAs>, Rd

#### **Operand Size**

Byte

### **Condition Code**

| I |   | Н         |   | N        | Z         | V        | C         |

|---|---|-----------|---|----------|-----------|----------|-----------|

| _ | _ | <b>\$</b> | _ | <b>‡</b> | <b>\$</b> | <b>‡</b> | <b>\$</b> |

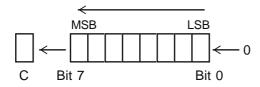

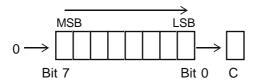

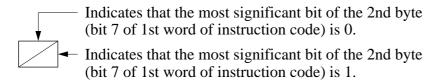

- I: Previous value remains unchanged.