# Regarding the change of names mentioned in the document, such as Mitsubishi Electric and Mitsubishi XX, to Renesas Technology Corp.

The semiconductor operations of Hitachi and Mitsubishi Electric were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Mitsubishi Electric, Mitsubishi Electric Corporation, Mitsubishi Semiconductors, and other Mitsubishi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Note : Mitsubishi Electric will continue the business operations of high frequency & optical devices and power devices.

Renesas Technology Corp. Customer Support Dept. April 1, 2003

## MITSUBISHI 16-BIT SINGLE-CHIP MICROCOMPUTER 7700 Family / 7900 Series

Software Manual

Mitsubishi Electric Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of non-flammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Mitsubishi semiconductor product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Mitsubishi Electric Corporation or a third party.

- Mitsubishi Electric Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts or circuit application examples contained in these materials.

- All information contained in these materials, including product data, diagrams and charts, represent information on products at the time of publication of these materials, and are subject to change by Mitsubishi Electric Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor for the latest product information before purchasing a product listed herein.

- Mitsubishi Electric Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- The prior written approval of Mitsubishi Electric Corporation is necessary to reprint or reproduce in whole or in part these materials.

- If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination. Any diversion or reexport contrary to the export control laws and regulations of JAPAN and/or the country of destination is prohibited.

- Please contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor for further details on these materials or the products contained therein.

### **REVISION DESCRIPTION LIST**

### 7900 Series Software Manual

| Rev.<br>No. | Revision Description | Rev.<br>date |

|-------------|----------------------|--------------|

|             |                      |              |

| 1.0         | First Edition        | 980731       |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

# Preface

This manual describes the software of the Mitsubishi CMOS 16-bit microcomputers, the 7900 Series. After reading this manual, the users will be able to understand the instruction set and the features about software of the 7900 Series, so that they can utilize their capabilities fully.

# **Table of contents**

### CHAPTER 1. DESCRIPTION

### CHAPTER 2. CENTRAL PROCESSING UNIT (CPU)

| 2.1 Central processing unit                      |      |

|--------------------------------------------------|------|

| 2.1.1 Accumulator (Acc)                          | 2-3  |

| 2.1.2 Index register X (X)                       |      |

| 2.1.3 Index register Y (Y)                       |      |

| 2.1.4 Stack pointer (S)                          |      |

| 2.1.5 Program counter (PC)                       |      |

| 2.1.6 Program bank register (PG)                 |      |

| 2.1.7 Data bank register (DT)                    |      |

| 2.1.8 Direct page register 0 to 3 (DPR0 to DPR3) |      |

| 2.1.9 Processor status register (PS)             |      |

| 2.2 Access space                                 |      |

| 2.3 Addressing modes                             |      |

| 2.3.1 Overview                                   | 2-11 |

| 2.3.2 Explanation of addressing modes            | 2-11 |

### CHAPTER 3. HOW TO USE 7900 SERIES INSTRUCTIONS

| 3.1 Memory access                                      |     |

|--------------------------------------------------------|-----|

| 3.1.1 Direct addressing                                |     |

| 3.1.2 Absolute addressing and Absolute long addressing |     |

| 3.1.3 Indirect addressing and Indirect long addressing |     |

| 3.2 Direct page registers (DPR0-DPR3)                  |     |

| 3.3 8- and 16-bit data processing                      | 3-5 |

| 3.4 Index registers X and Y                            | 3-6 |

| 3.5 Branch instructions                                |     |

### CHAPTER 4. INSTRUCTIONS

| 4.1 Instruction set                               |       |

|---------------------------------------------------|-------|

| 4.2 Description of each instruction               | 4-9   |

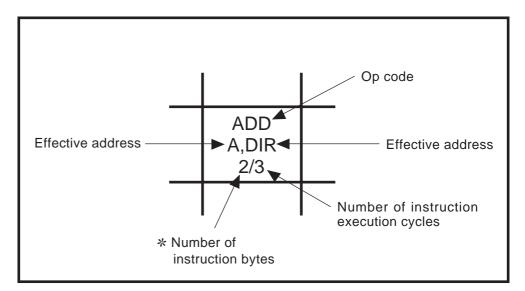

| 4.3 Notes on software development                 | 4-230 |

| 4.3.1 Instruction execution cycles                |       |

| 4.3.2 Status of flags m and x                     |       |

| 4.3.3 Tips for data area location                 |       |

| 4.3.4 Performing arithmetic operations in decimal |       |

#### APPENDIX

| Appendix 1. 7900 Series machine instructions5-2     | 2 |

|-----------------------------------------------------|---|

| Appendix 2. Hexadecimal instruction code tables5-44 | ŀ |

The 7900 Series is upper compatible with the conventional 7700 Family.

The following outlines the features of the 7900 Series:

- Source-level-compatible with the conventional 7700 Family. (e.g., 7700 and 7751 Series).

- Whereas the 7700 and 7751 Series respectively support 103 and 109 instructions, the 7900 Series has its instruction set expanded to 203 instructions. The following instructions have been added:

- (i) 32-bit operation instructions

- (ii) 8-bit-data-dedicated instructions

- (iii) Memory-to-memory data transfer instructions

- (iv) Zero-clear instructions for register and memory

- (v) Add/Subtract without-carry instructions

- (vi) Add/Subtract instructions for stack pointer

- (vii) OR, AND, and EOR instructions for memory

- (viii) Compare instructions for memory

- (ix) Signed conditional branch instructions

- (x) Compare & Conditional branch instructions

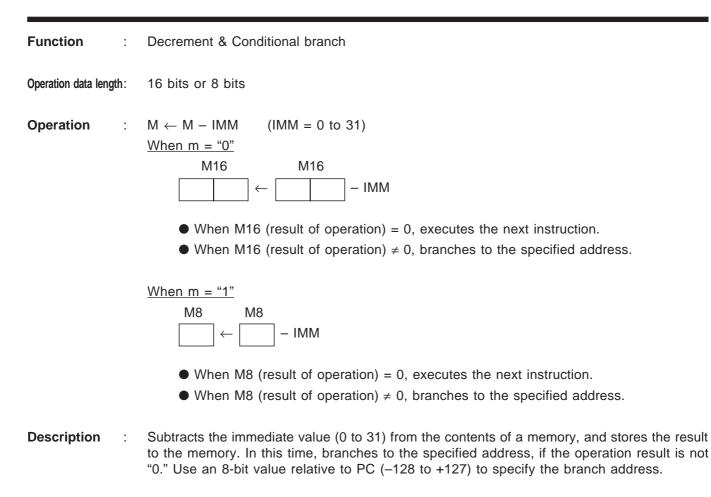

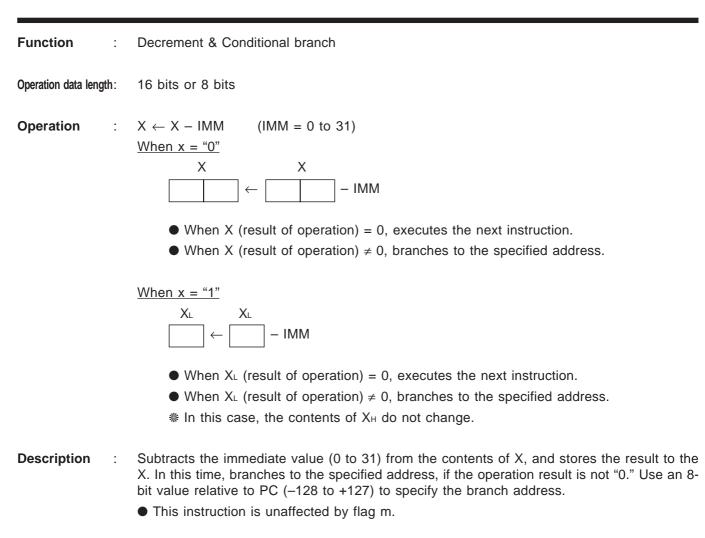

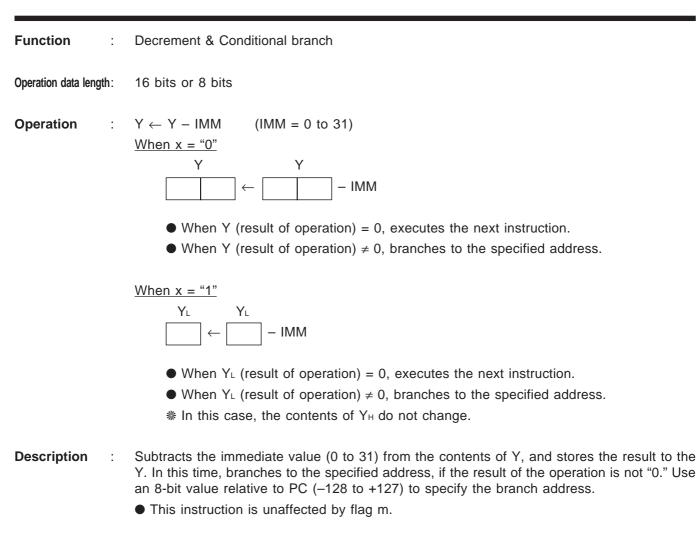

- (xi) Decrement & Conditional branch instructions

- (xii) PC relative subroutine call instructions

Thanks to its expanded instruction set, the 7900 Series allows program sizes to be reduced by 20 to 30% on the average from the conventional 7700 Family.

- 16 Mbytes of memory space. Various addressing modes for accessing this memory space are available.

- A 64-Kbyte space from 000000<sub>16</sub> to 00FFFF<sub>16</sub> can be accessed at high speed by an instruction which has a small number of bytes. The 7900 Series has 4 direct page registers that can be used for this purpose.

- Reduced instruction execution cycles than the conventional 7700 Family.

# CHAPTER 2 CENTRAL PROCESSING UNIT (CPU)

- 2.1 Central processing unit (CPU)

- 2.2 Memory space

- 2.3 Addressing modes

### 2.1 Central processing unit (CPU)

### 2.1 Central processing unit

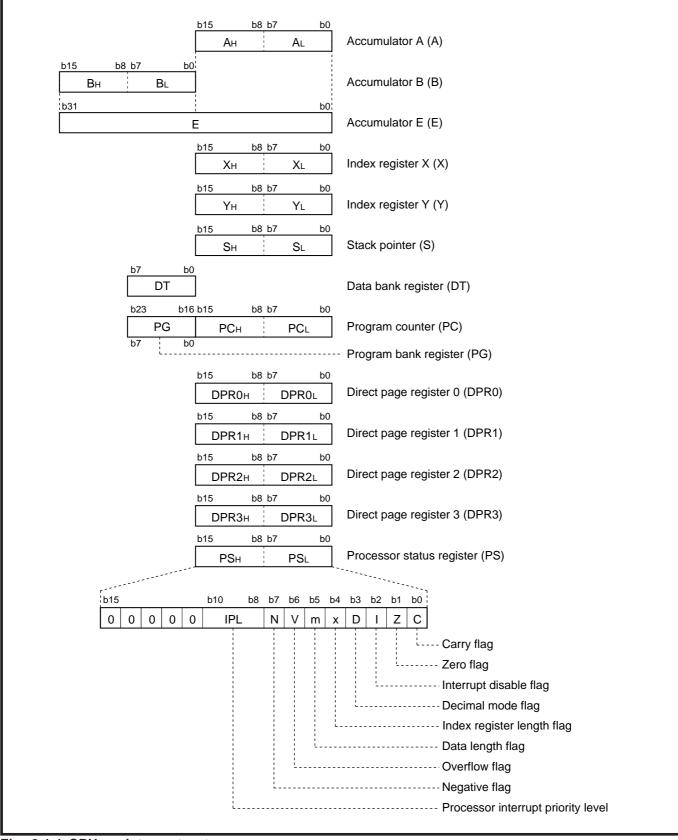

The CPU (Central Processing Unit) has 13 registers as shown in Figure 2.1.1.

Fig. 2.1.1 CPU registers structure

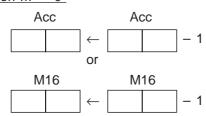

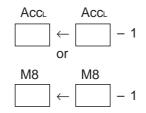

#### 2.1.1 Accumulator (Acc)

Accumulators A and B are available. Also, accumulators A and B can be connected in series for use as a 32-bit accumulator (accumulator E).

#### (1) Accumulator A (A)

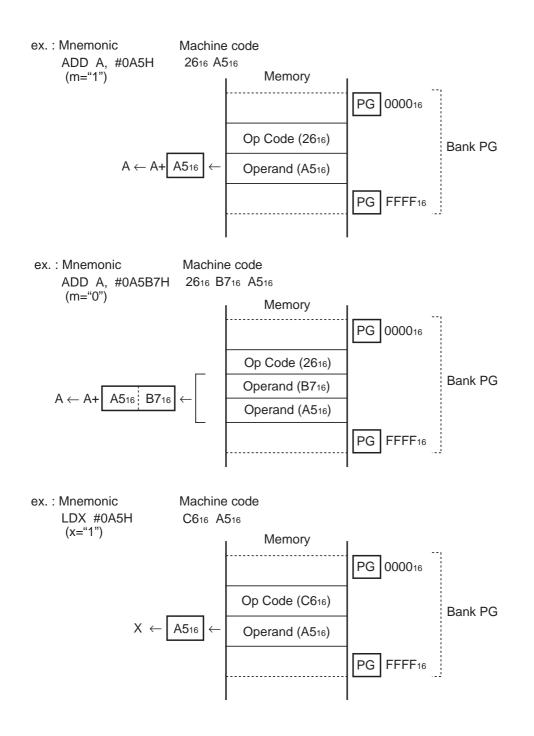

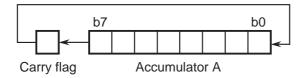

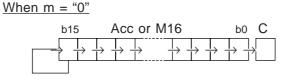

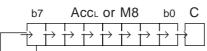

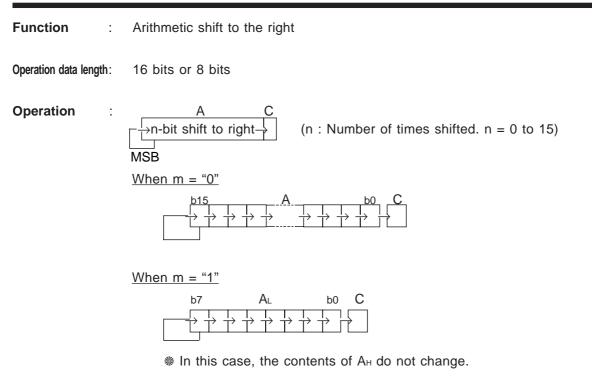

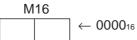

Accumulator A is the main register of the microcomputer. The transaction of data such as calculation, data transfer, and input/output are performed mainly through accumulator A. It consists of 16 bits, and the low-order 8 bits can also be used separately. The data length flag (m) determines whether the register is used as a 16-bit register or as an 8-bit register. Flag m is a part of the processor status register which is described later. When an 8-bit register is selected, only the low-order 8 bits of accumulator A are used and the contents of the high-order 8 bits is unchanged.

#### (2) Accumulator B (B)

Accumulator B is a 16-bit register with the same function as accumulator A. Accumulator B can be used instead of accumulator A. The use of accumulator B, however except for some instructions, requires more instruction bytes and execution cycles than that of accumulator A. Accumulator B is also controlled by the data length flag (m) just as in accumulator A.

#### (3) Accumulator E (E)

This 32-bit accumulator consists of accumulator A for low-order 16 bits and accumulator B for highorder 16 bits. This accumulator is used for instructions that handle 32-bit data. It is not controlled by flag m.

#### 2.1.2 Index register X (X)

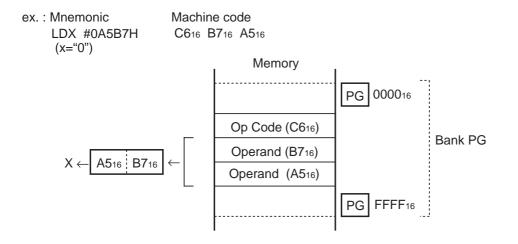

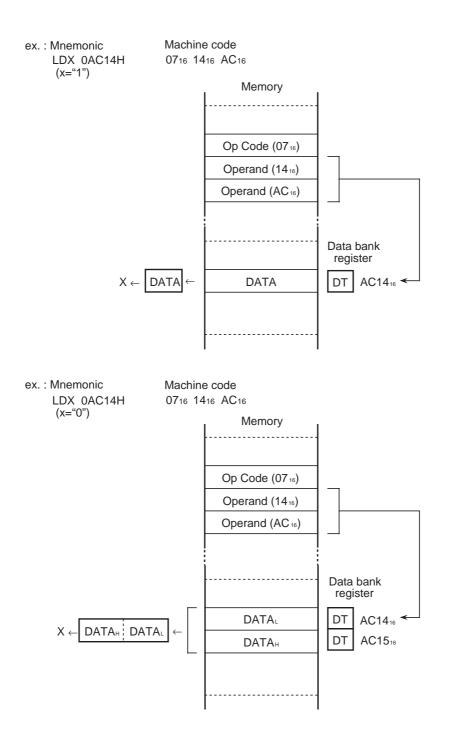

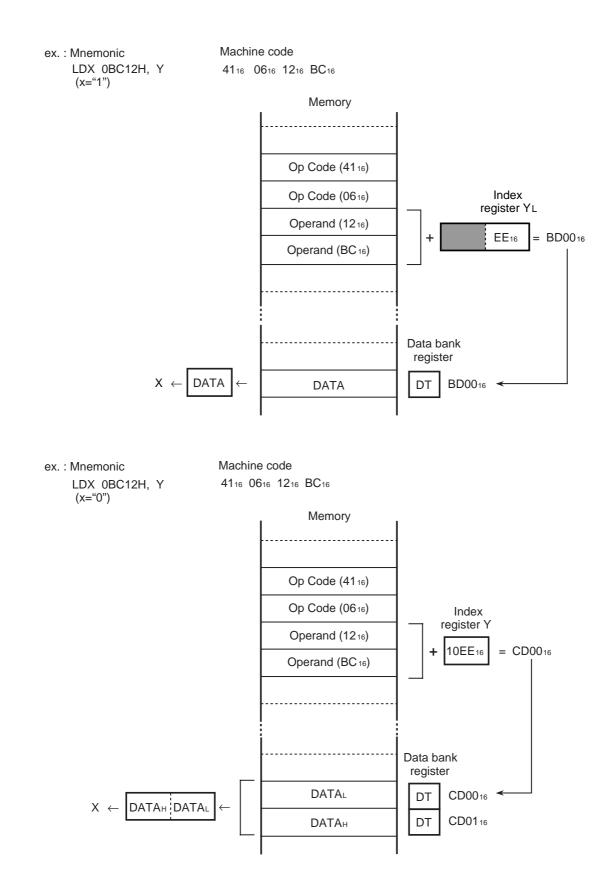

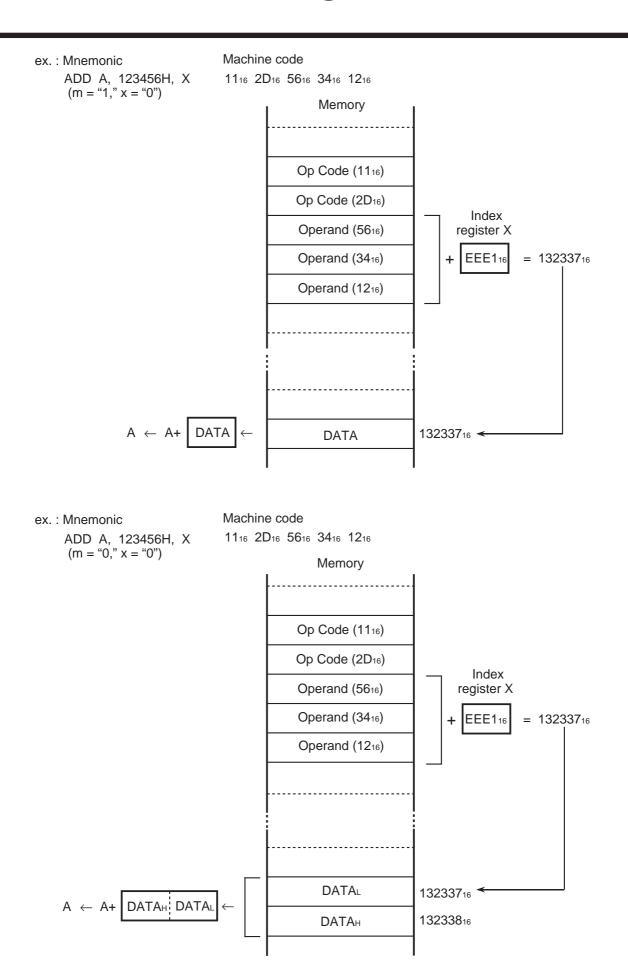

Index register X consists of 16 bits and the low-order 8 bits can also be used separately. The index register length flag (x) determines whether the register is used as a 16-bit register or as an 8-bit register. Flag x is a part of the processor status register which is described later. When an 8-bit register is selected, only the low-order 8 bits of index register X are used and the contents of the high-order 8 bits is unchanged. In an addressing mode in which index register X is used as an index register, the address obtained by adding the contents of this register to the operand's contents is accessed.

In the MVP, MVN or RMPA instruction, index register X is used, also.

#### 2.1.3 Index register Y (Y)

Index register Y is a 16-bit register with the same function as index register X. Just as in index register X, the index register length flag (x) determines whether this register is used as a 16-bit register or as an 8-bit register.

### 2.1 Central processing unit (CPU)

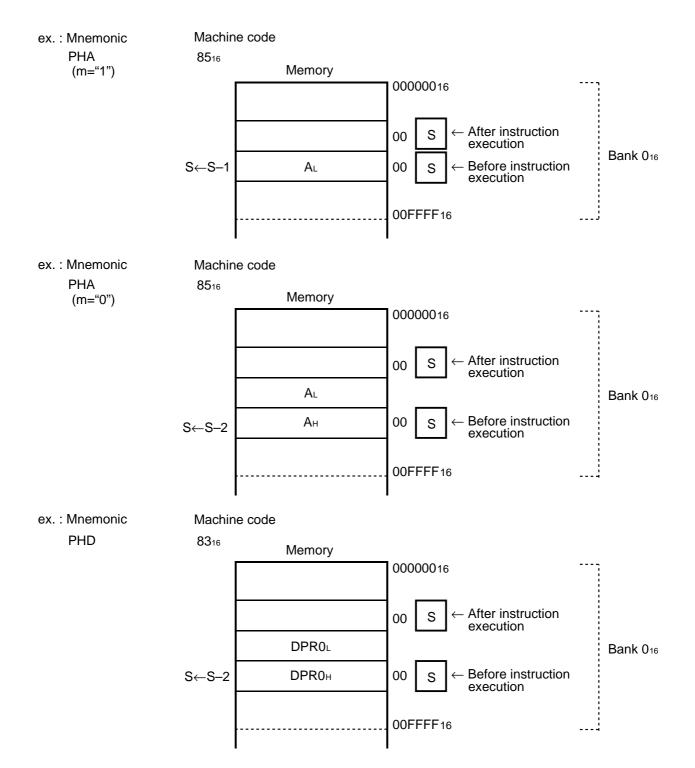

#### 2.1.4 Stack pointer (S)

The stack pointer (S) is a 16-bit register. It is used for a subroutine call or an interrupt. It is also used when addressing modes using the stack are executed. The contents of S indicate an address (stack area) for storing registers during subroutine calls and interrupts. Bank 016 is specified for the stack area. (Refer to "2.2 Memory space."

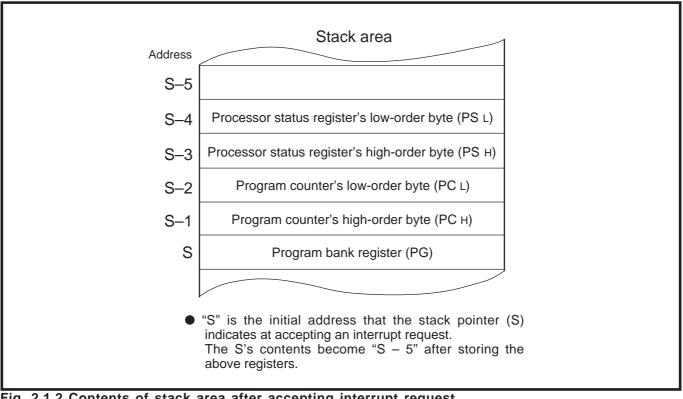

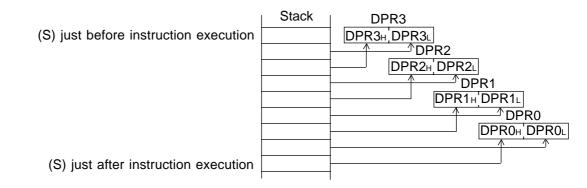

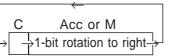

When an interrupt request is accepted, the microcomputer stores the contents of the program bank register (PG) at the address indicated by the contents of S and decrements the contents of S by 1. Then the contents of the program counter (PC) and the processor status register (PS) are stored. The contents of S after accepting an interrupt request is equal to the contents of S decremented by 5 before accepting of the interrupt request. (Refer to **Figure 2.1.2.**)

When completing the process in the interrupt routine and returning to the original routine, the contents of registers stored in the stack area are restored into the original registers in the reverse sequence ( $PS \rightarrow PC \rightarrow PG$ ) by executing the **RTI** instruction. The contents of S is returned to the state before accepting an interrupt request.

The same operation is performed during a subroutine call, however, the contents of PS is not automatically stored. (The contents of PG may not be stored. This depends on the addressing mode.)

During interrupts or subroutine calls, the other registers are not automatically stored. Therefore, if the contents of these registers need to be held on, be sure to store them by software.

Additionally, the S's contents become "0FFF<sub>16</sub>" at reset. The stack area changes when subroutines are nested or when multiple interrupt requests are accepted. Therefore, make sure of the subroutine's nesting depth not to destroy the necessary data.

Fig. 2.1.2 Contents of stack area after accepting interrupt request

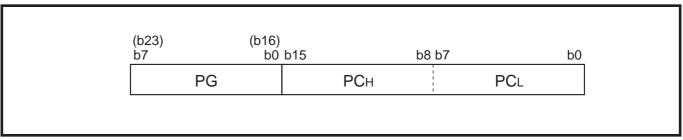

#### 2.1.5 Program counter (PC)

The program counter is a 16-bit counter that indicates the low-order 16 bits of the address (24 bits) at which an instruction to be executed next (in other words, an instruction to be read out from an instruction queue buffer next) is stored. The contents of the high-order program counter (PCH) become "FF16," and the low-order program counter (PCL) becomes "FE16" at reset. The contents of the program counter becomes the contents of the reset's vector address (addresses FFFE16, FFFF16) just after reset. Figure 2.1.3 shows the program counter and the program bank register.

Fig. 2.1.3 Program counter and program bank register

#### 2.1.6 Program bank register (PG)

The memory space is divided into units of 64 Kbytes. This unit is called "bank." (Refer to "2.2 Memory space.")

The program bank register is an 8-bit register that indicates the high-order 8 bits of the address (24 bits) at which an instruction to be executed next (in other words, an instruction to be read out from an instruction queue buffer next) is stored. These 8 bits indicate a bank.

When a carry occurs after adding the contents of the program counter or adding the offset value to the contents of the program counter in the branch instruction and others, the contents of the program bank register is automatically incremented by 1. When a borrow occurs after subtracting the contents of the program counter, the contents of the program bank register is automatically decremented by 1. Therefore, there is no need to consider bank boundaries during programming, usually.

This register is cleared to "0016" at reset.

### 2.1 Central processing unit (CPU)

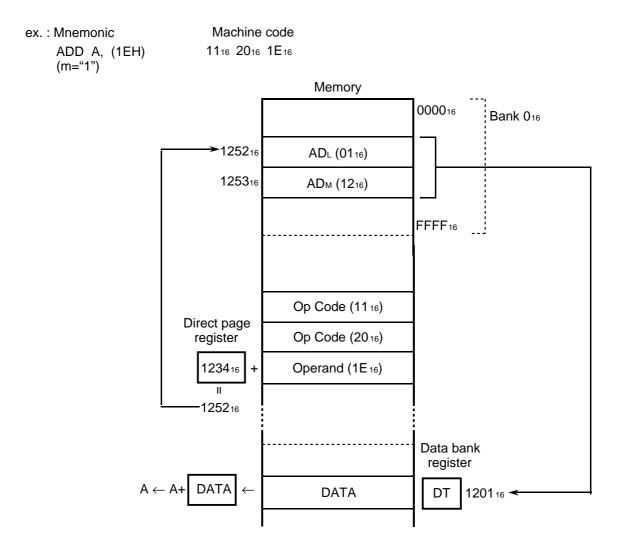

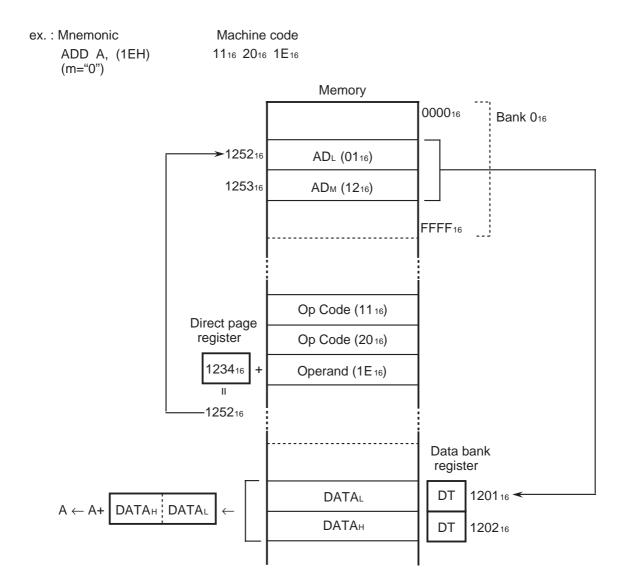

#### 2.1.7 Data bank register (DT)

The data bank register is an 8-bit register. In the following addressing modes using the data bank register, the contents of this register is used as the high-order 8 bits (bank) of a 24-bit address to be accessed.

Use the LDT instruction when setting a value to this register. This register is cleared to "0016" at reset.

•Addressing modes using data bank register

- •Direct indirect

- •Direct indexed X indirect

- •Direct indirect indexed Y

- •Absolute

- •Absolute indexed X

- Absolute indexed Y

- Absolute bit relative

- •Stack pointer relative indirect indexed Y

- •Multiplied accumulation

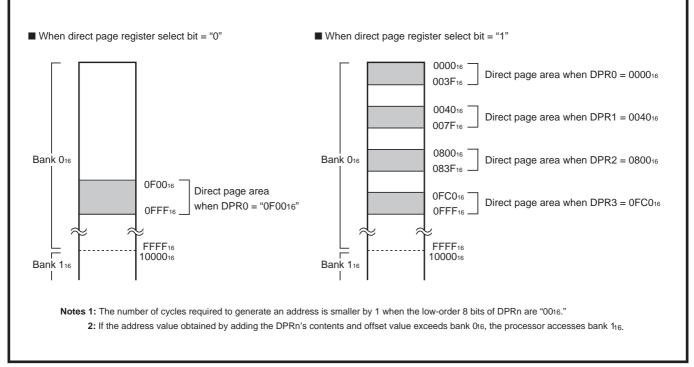

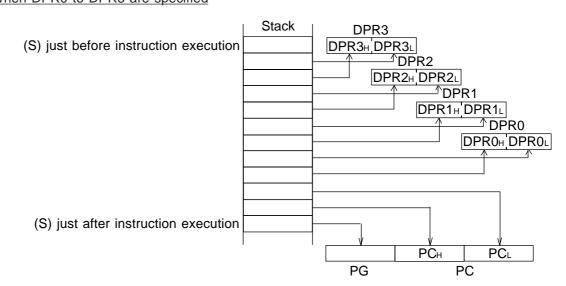

#### 2.1.8 Direct page register 0 to 3 (DPR0 to DPR3)

The direct page register is a 16-bit register. The direct page registers (hereafter called the "DPRn") have been enhanced from the conventional 7700 Family.

These registers are used to access the 64-Kbyte space in bank 0 efficiently.

The direct page register select bit of processor mode register 1 determines whether to use DPR0 only or DPR0 through DPR3. The function of this bit is described below.

#### Table 2.1.1 Direct page register selection

|                                                 | Direct page register select bit          |              |

|-------------------------------------------------|------------------------------------------|--------------|

|                                                 | 0                                        | 1            |

| DPRn that can be used                           | DPR0                                     | DPR0 to DPR3 |

| Block size accessible from DPRn as base address | 256 bytes                                | 64 bytes     |

| Remarks                                         | Compatible with conventional 7700 Family | _            |

Note : Once the direct page register select bit is set, do not change its value.

### 2.1 Central processing unit

#### Fig. 2.1.4 Direct page area selection example

When the contents of low-order 8 bits of the direct page register is "0016," the number of cycles required to generate an address is smaller by 1 than the number when its contents are not "0016." Accordingly, the access efficiency can be enhanced in this case. This register is cleared to "000016" at reset.

- •Addressing modes using direct page register

- Direct

- •Direct indexed X

- •Direct indexed Y

- •Direct indirect

- •Direct indexed X indirect

- •Direct indirect indexed Y

- •Direct indirect long

- •Direct indirect long indexed Y

- •Direct bit relative

### 2.1 Central processing unit (CPU)

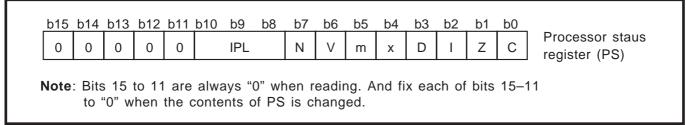

#### 2.1.9 Processor status register (PS)

The processor status register is an 11-bit register.

Figure 2.1.5 shows the structure of the processor status register.

#### Fig. 2.1.5 Processor status register structure

#### (1) Bit 0: Carry flag (C)

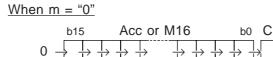

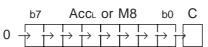

It retains a carry or a borrow generated in the arithmetic and logic unit (ALU) during an arithmetic operation. This flag is also affected by shift and rotate instructions.

Use the **SEC** or **SEP** instruction to set this flag to "1", and use the **CLC** or **CLP** instruction to clear it to "0".

The contents of this flag is undefined at reset.

#### (2) Bit 1: Zero flag (Z)

It is set to "1" when the result of an arithmetic operation or data transfer is "0," and cleared to "0" when otherwise. <u>This flag is invalid in the decimal mode addition.</u>

Use the **SEP** instruction to set this flag to "1," and use the **CLP** instruction to clear it to "0." The contents of this flag is undefined at reset.

#### (3) Bit 2: Interrupt disable flag (I)

It disables all maskable interrupts. Interrupts are disabled when this flag is "1." When an interrupt request is accepted, this flag is automatically set to "1" to avoid multiple interrupts. Use the **SEI** or **SEP** instruction to set this flag to "1," and use the **CLI** or **CLP** instruction to clear it to "0." This flag is set to "1" at reset.

#### (4) Bit 3: Decimal mode flag (D)

It determines whether addition and subtraction are performed in binary or decimal. Binary arithmetic is performed when this flag is "0." When it is "1," decimal arithmetic is performed with each 8-bit treated as 2-digit decimal (at m = 1) or each 16-bit treated as 4-digit decimal (at m = 0). Decimal adjust is automatically performed. Decimal operation is possible only with the **ADC**, **ADCB**, **SBC** and **SBCB** instructions. Use the **SEP** instruction to set this flag to "1," and use the **CLP** instruction to clear it to "0." This flag is cleared to "0" at reset.

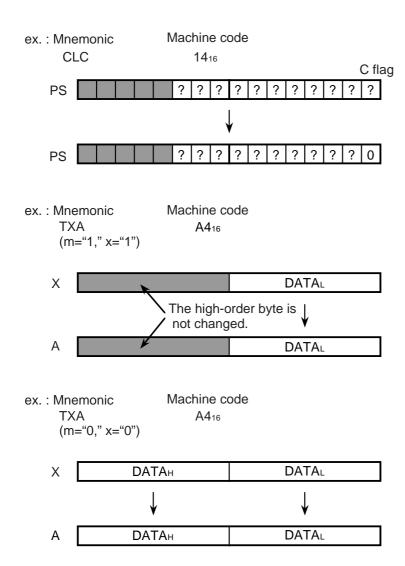

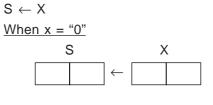

#### (5) Bit 4: Index register length flag (x)

It determines whether each of index register X and index register Y is used as a 16-bit register or an 8-bit register. That register is used as a 16-bit register when this flag is "0," and as an 8-bit register when it is "1" **(Note)**. Use the **SEP** instruction to set this flag to "1," and use the **CLP** instruction to clear it to "0." This flag is cleared to "0" at reset.

**Note:** When transferring data between registers which are different in bit length, the data is transferred with the length of the destination register, but except for the **TXA**, **TYA**, **TXB**, **TYB**, and **TXS** instructions.

2.1 Central processing unit

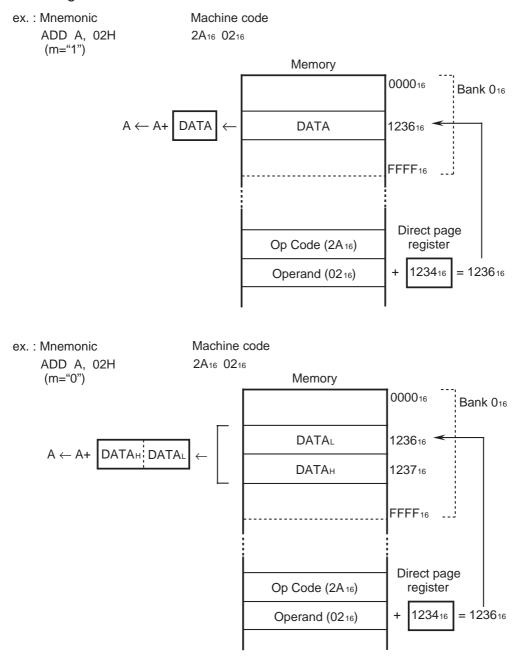

#### (6) Bit 5: Data length flag (m)

It determines whether to use data as a 16-bit unit or as an 8-bit unit. A data is treated as a 16-bit unit when this flag is "0," and as an 8-bit unit when it is "1" (Note).

Use the **SEM** or **SEP** instruction to set this flag to "1," and use the **CLM** or **CLP** instruction to clear it to "0." This flag is cleared to "0" at reset.

**Note:** When transferring data between registers which are different in bit length, the data is transferred with the length of the destination register, but except for the **TXA**, **TYA**, **TXB**, **TYB**, and **TXS** instructions.

#### (7) Bit 6: Overflow flag (V)

It is used when adding or subtracting with a word regarded as signed binary. The overflow flag is set to "1" when the result of addition or subtraction exceeds the range between -2147483648 and +2147483647 (when 32-bit length operation), the range between -32768 and +32767 (when 16-bit length operation), or the range between -128 and +127 (when 8-bit length operation).

The overflow flag is also set to "1" when the result of division exceeds the length of the register which will store the result, in the **DIV** or **DIVS** instruction. This flag is invalid in the decimal mode. Use the **SEP** instruction to set this flag to "1," and use the **CLV** or **CLP** instruction to clear it to "0." The contents of this flag is undefined at reset.

#### (8) Bit 7: Negative flag (N)

It is set to "1" when the result of arithmetic operation or data transfer is negative. (The most significant bit of the result is "1.") It is cleared to "0" in all other cases. This flag is invalid in the decimal mode. Use the **SEP** instruction to set this flag to "1," and use the **CLP** instruction to clear it to "0." The contents of this flag is undefined at reset.

#### (9) Bits 10 to 8: Processor interrupt priority level (IPL)

These 3 bits can determine the processor interrupt priority level to one of levels 0 to 7. The interrupt is enabled when <u>the interrupt priority level</u> of a required interrupt, which is set in each interrupt control register, is higher than IPL. When an interrupt request is accepted, IPL is stored in the stack area, and IPL is replaced by the interrupt priority level of the accepted interrupt request.

There are no instruction to directly set or clear the bits of IPL. IPL can be changed by storing the new IPL into the stack area and updating the processor status register with the **PUL** or **PLP** instruction. The contents of IPL is cleared to "0002" at reset.

2.2 Access space

### 2.2 Access space

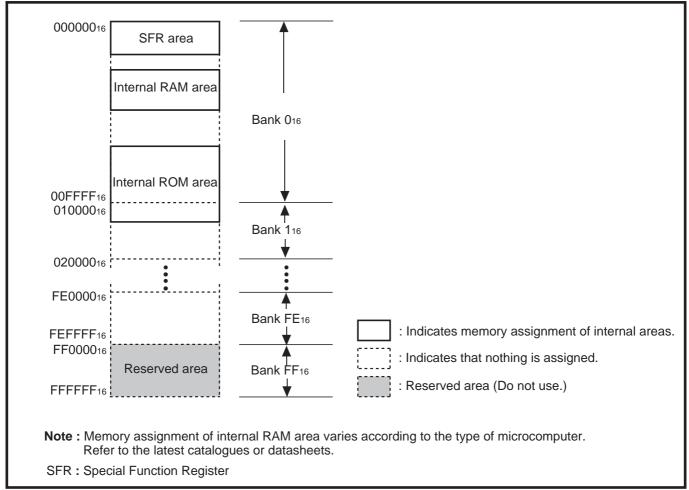

The memory space of the 7900 Series is a 16-Mbyte space from addresses 0<sub>16</sub> to FFFFF<sub>16</sub>. (Refer to the **Figure 2.2.1**.) However, addresses FF0000<sub>16</sub> to FFFFF<sub>16</sub> cannot be used because this area is reserved. A 24-bit address is generated by combination of the program counter (PC), which is 16 bits of structure, and the program bank register (PG), which is 8 bits of structure. The memory space of the 7900 Series is divided into units of 64 Kbytes. This unit is called "bank." The PG indicates the bank number.

The memory and I/O devices are assigned in the same access space. Accordingly, it is possible to perform transfer and arithmetic operations using the same instructions without discrimination of the memory from I/O devices.

Fig. 2.2.1 7900 Series's access space

## 2.3 Addressing modes

#### 2.3.1 Overview

To execute an instruction, when the data required for the operation is retrieved from a memory or the result of the operation is stored to it, it is necessary to specify the address of the memory location in advance. Address specification is also necessary when the control is to jump to a certain memory address during program execution. Addressing means the method of specifying the memory address.

The memory access of the 7900 Series microcomputers is reinforced with 27 different addressing modes.

#### 2.3.2 Explanation of addressing modes

Each addressing mode is explained on the corresponding page indicated below:

| Immediate addressing mode (IMM)2-13<br>Accumulator addressing mode (A)2-15 |

|----------------------------------------------------------------------------|

| Accumulator addressing mode (A)2-15                                        |

|                                                                            |

| Direct addressing mode (DIR)2-16                                           |

| Direct indexed X addressing mode (DIR,X)2-19                               |

| Direct indexed Y addressing mode (DIR,Y)2-22                               |

| Direct indirect addressing mode ((DIR))2-23                                |

| Direct indexed X indirect addressing mode ((DIR,X))2-25                    |

| Direct indirect indexed Y addressing mode ((DIR,Y))2-28                    |

| Direct indirect long addressing mode (L (DIR))2-31                         |

| Direct indirect long indexed Y addressing mode (L (DIR),Y)2-33             |

| Absolute addressing mode (ABS)2-36                                         |

| Absolute indexed X addressing mode (ABS,X) 2-39                            |

| Absolute indexed Y addressing mode (ABS,Y) 2-42                            |

| Absolute long addressing mode (ABL)2-45                                    |

| Absolute long indexed X addressing mode (ABL,X) 2-47                       |

| Absolute indirect addressing mode ((ABS))2-49                              |

| Absolute indirect long addressing mode (L (ABS))                           |

| Absolute indexed X indirect addressing mode ((ABS,X))2-51                  |

| Stack addressing mode (STK)2-52                                            |

| Relative addressing mode (REL)2-55                                         |

| Direct bit relative addressing mode (DIR,b,R)2-56                          |

| Absolute bit relative addressing mode (ABS,b,R)2-58                        |

| Stack pointer relative addressing mode (SR)2-60                            |

| Stack pointer relative indirect indexed Y addressing mode ((SR),Y) 2-61    |

| Block transfer addressing mode (BLK)2-64                                   |

| Multiplied accumulation addressing mode (Multiplied accumulation) 2-66     |

**Note:** Unless otherwise noted, in each explanation diagram for the addressing mode of which name includes "direct," "Direct page register" means DPR0 only.

# Implied

Mode : Implied addressing mode

Function : These instructions do not have an operand in the mnemonic.

# Immediate

Mode : Immediate addressing mode

Function : These instructions operate with a register and a immediate value.

# Accumulator

Mode : Accumulator addressing mode

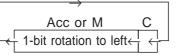

Function : These instructions manipulate the contents of an accumulator.

- ex. : Mnemonic

- ROL A (m="1")

Machine code 1316

ex. : Mnemonic ROL A (m="0") Machine code 13<sub>16</sub>

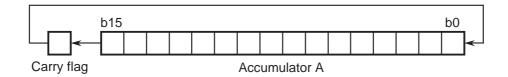

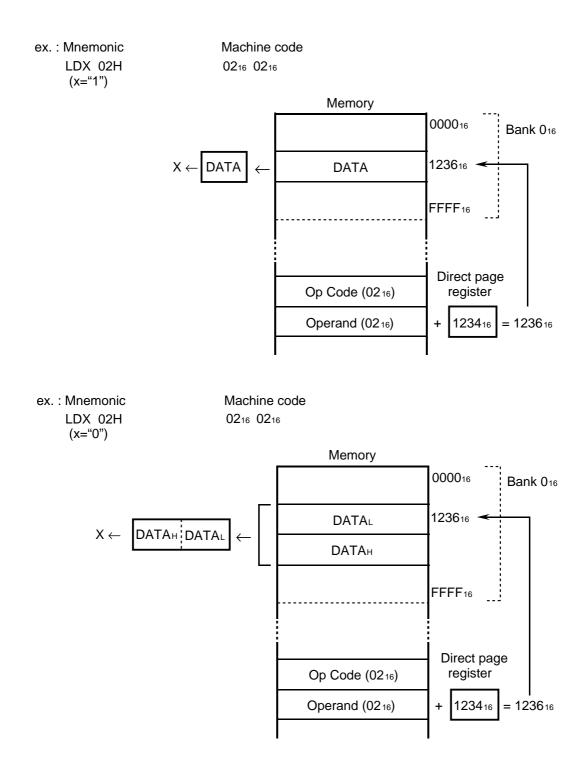

#### Mode : Direct addressing mode

**Function** : The memory contents in bank 0 specified by the result of adding the instruction's operand and the contents of the direct page register are an actual data. However, if the value derived by adding the instruction's operand and the direct page register's content's exceeds the bank 0<sub>16</sub> range, memory in bank 1 is specified.

The direct page register select bit of processor mode register 1 allows the user to choose one of the following options :

- Use direct page register 0 (DPR0) only. In this case, specify the offset from DPR0 in length of 8 bits.

- Use direct page registers 0 through 3 (DPR0 through 3). In this case, use the high-order 2 bits of the operand (8 bits) to specify the direct page register and the low-order 6 bits to specify the offset.

#### < Diect addressing mode>

# Direct

### <Extension direct addressing mode>

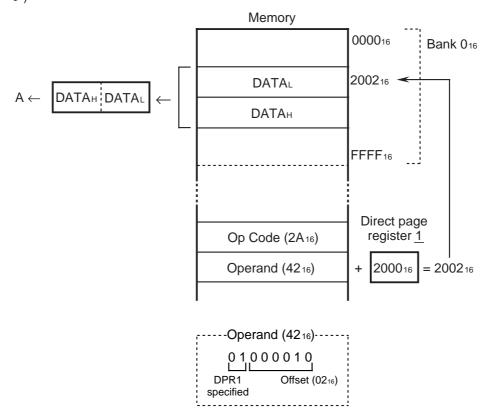

ex. : Mnemonic ADD A, 42H (x="0") Machine code 2A<sub>16</sub> 42<sub>16</sub>

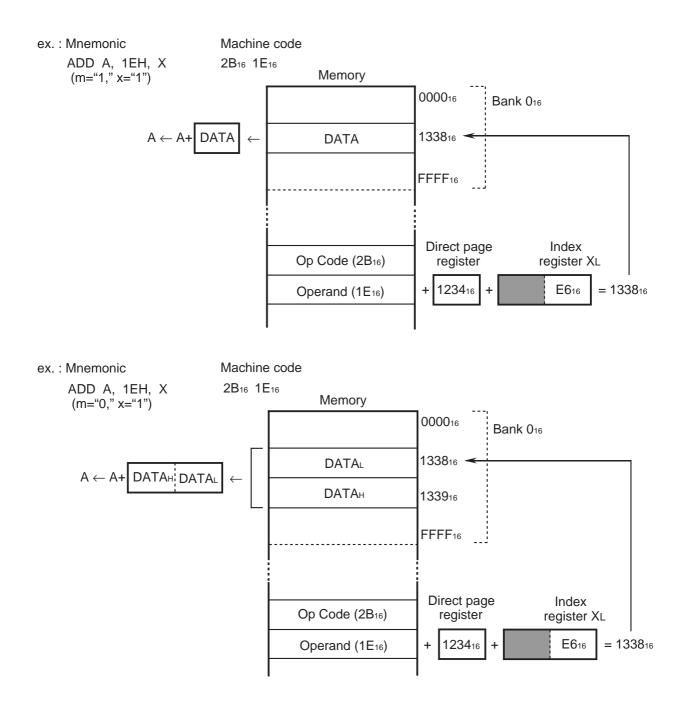

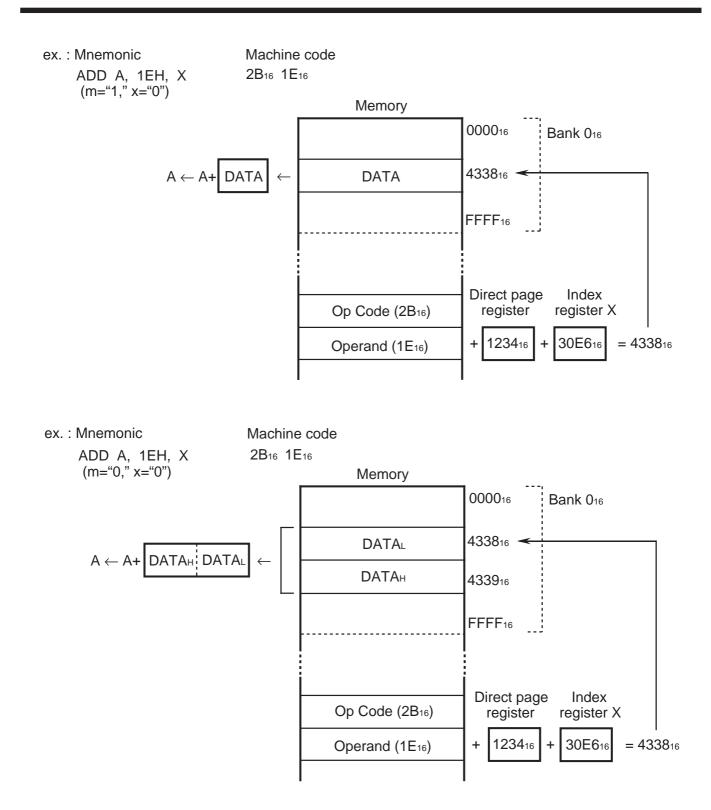

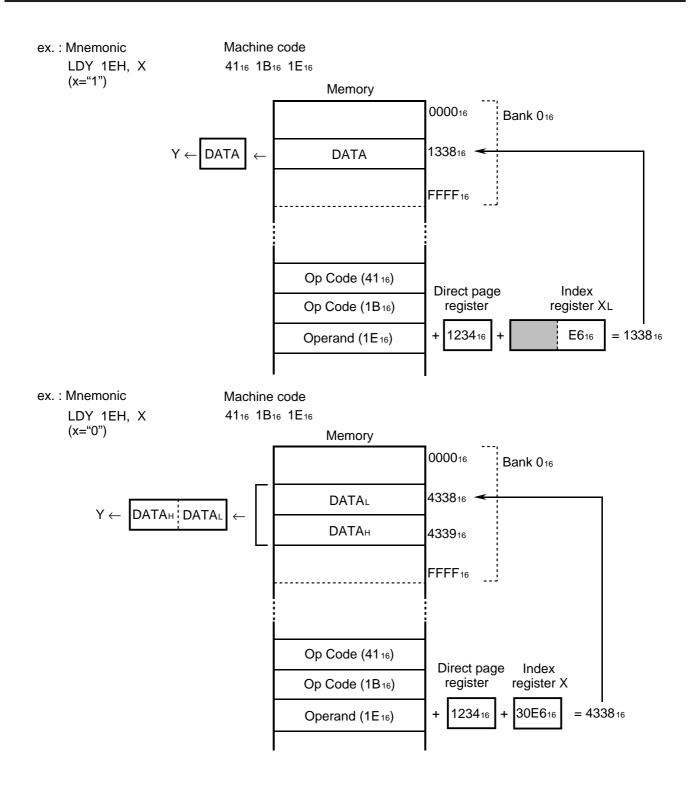

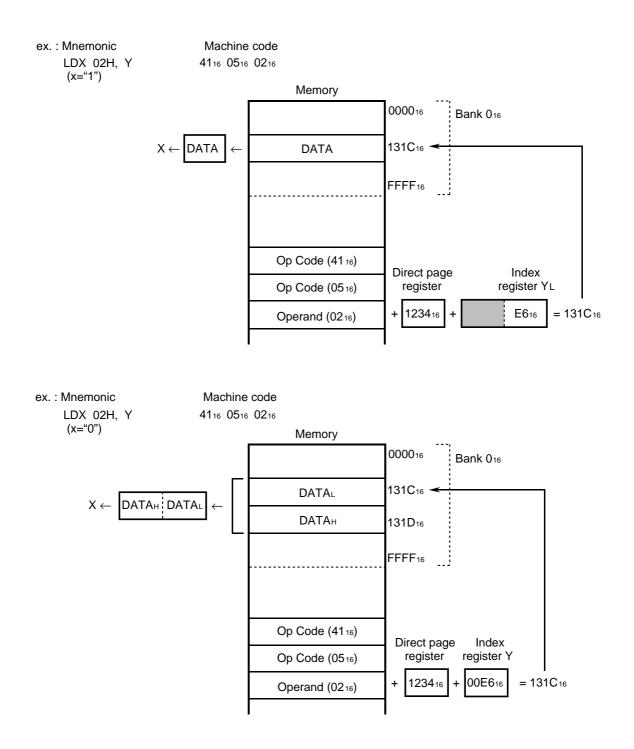

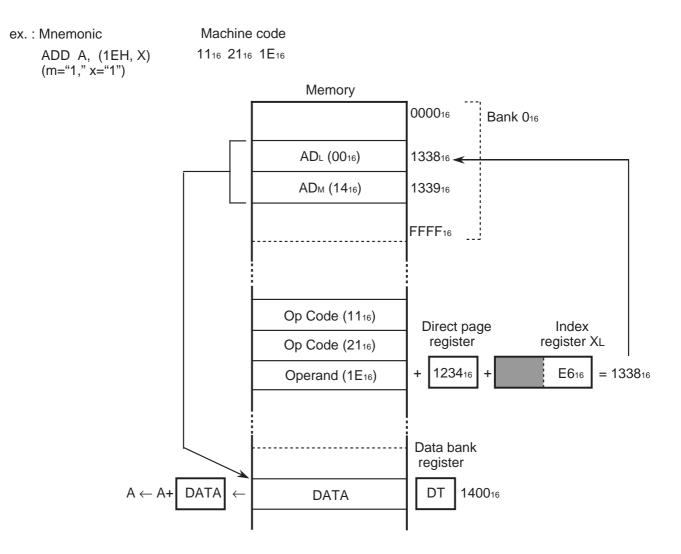

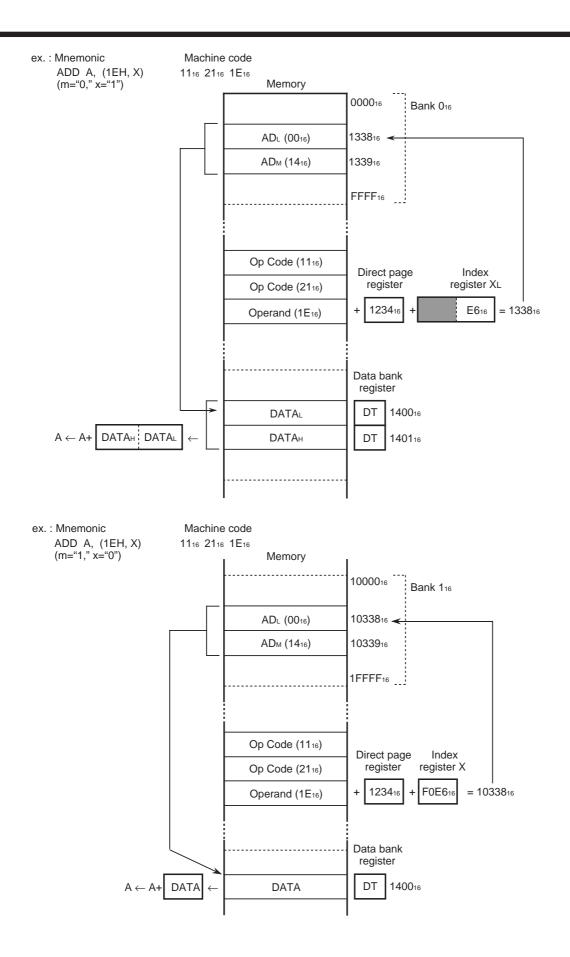

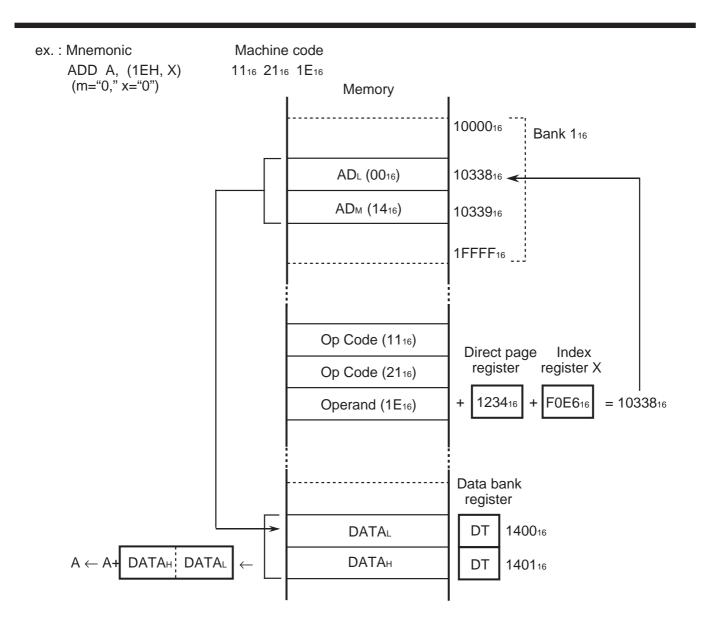

#### Mode : Direct indexed X addressing mode

**Function** : The contents of a memory in bank 016 are an actual data. This memory location is specified by the result of adding the instruction's operand, the direct page register's contents and the index register X's contents. When, however, the result of adding the instruction's operand, the direct page register's contents and the index register X's contents exceeds the bank 016 or bank 116 range, the memory location in bank 116 or bank 216 is specified.

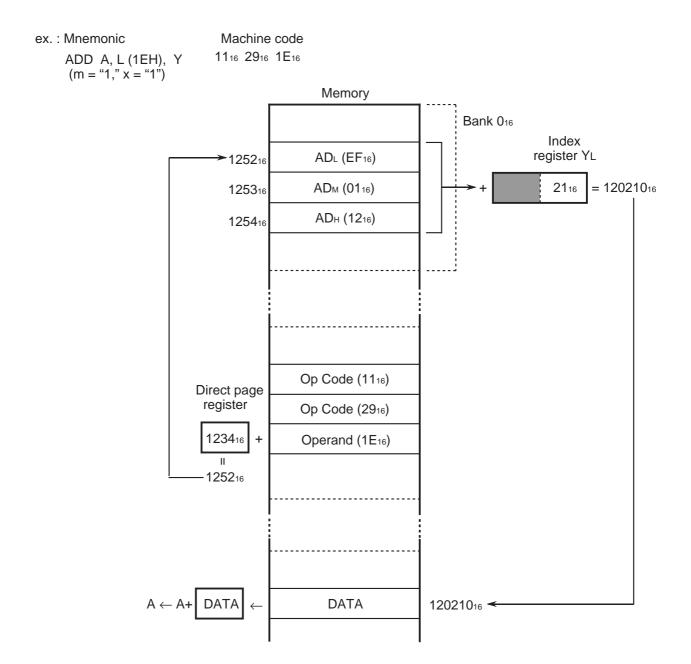

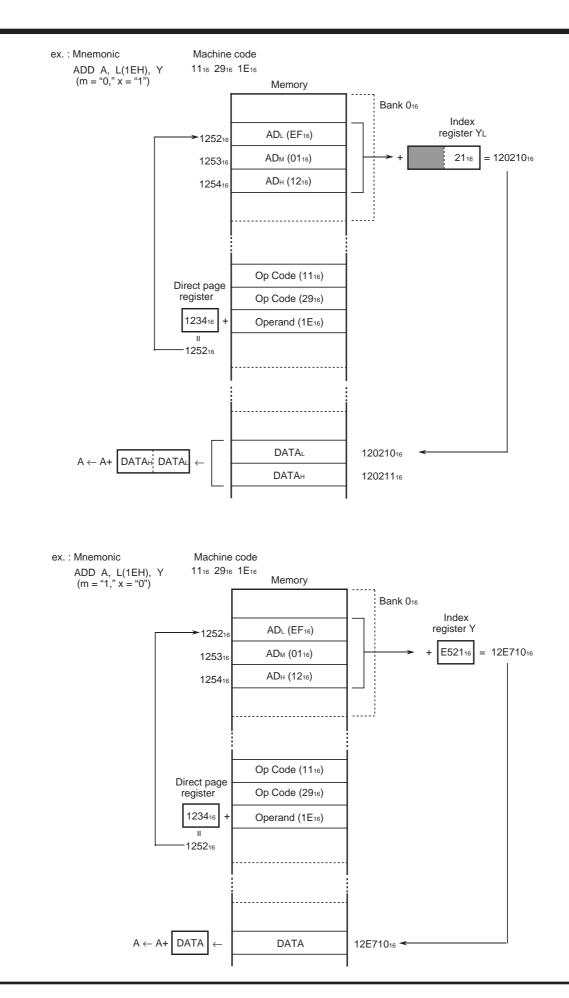

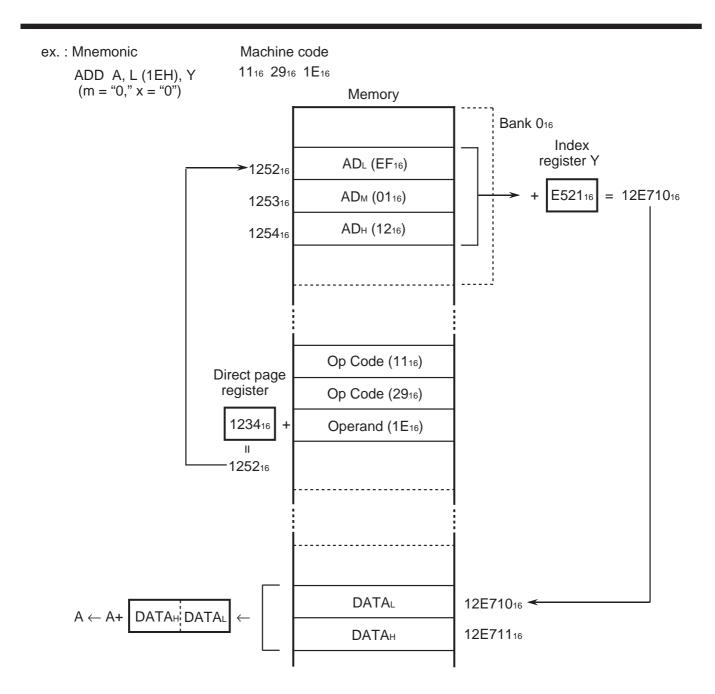

#### Mode : Direct indexed Y addressing mode

**Function** : The contents of a memory in bank 016 are an actual data. This memory location is specified by the result of adding the instruction's operand, the direct page register's contents and the index register Y's contents. When, however, the result of adding the instruction's operand, the direct page register's contents and the index register Y's contents exceeds the bank 016 or bank 116 range, the memory location in bank 116 or bank 216 is specified.

#### Mode : Direct indirect addressing mode

**Function :** Specifies a sequence of 2-byte memory in bank 016 by the result of adding the instruction's operand to the direct page register's contents. The contents of the memory location specified by these 2 bytes in bank DT (DT is the data bank register's contents) are an actual data. When, however, the result of adding the instruction's operand to the direct page register's contents exceeds the bank 016 range, the memory location in bank 116 is specified.

# **Direct Indexed X Indirect**

- Mode : Direct indexed X indirect addressing mode

- **Function** : Specifies a sequence of 2-byte memory in bank 016 by the result of adding the instruction's operand, the direct page register's contents and the index register X's contents. The contents of the memory location specified by these bytes in bank DT (DT is the data bank register's contents) are an actual data. When, however, the result of adding the instruction's operand, the direct page register's contents and the index register X's contents exceeds the bank 016 or bank 116 range, the memory location in bank 116 or bank 216 is specified.

# **Direct Indexed X Indirect**

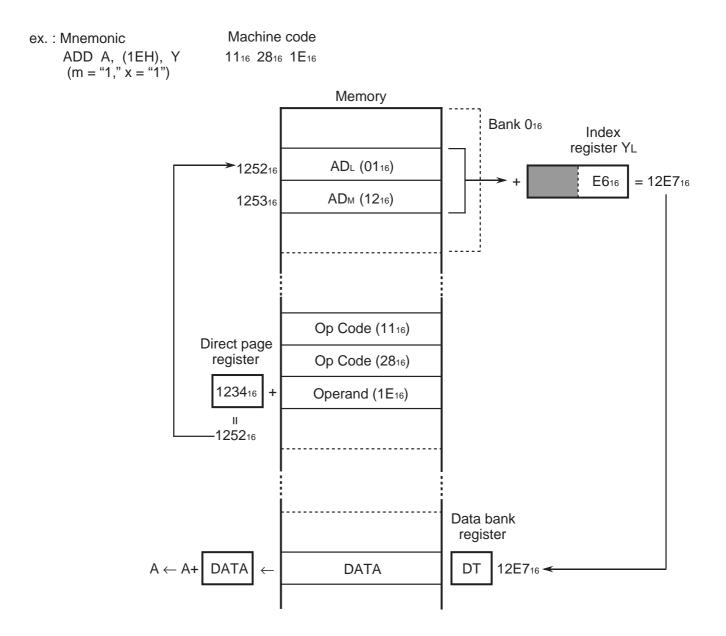

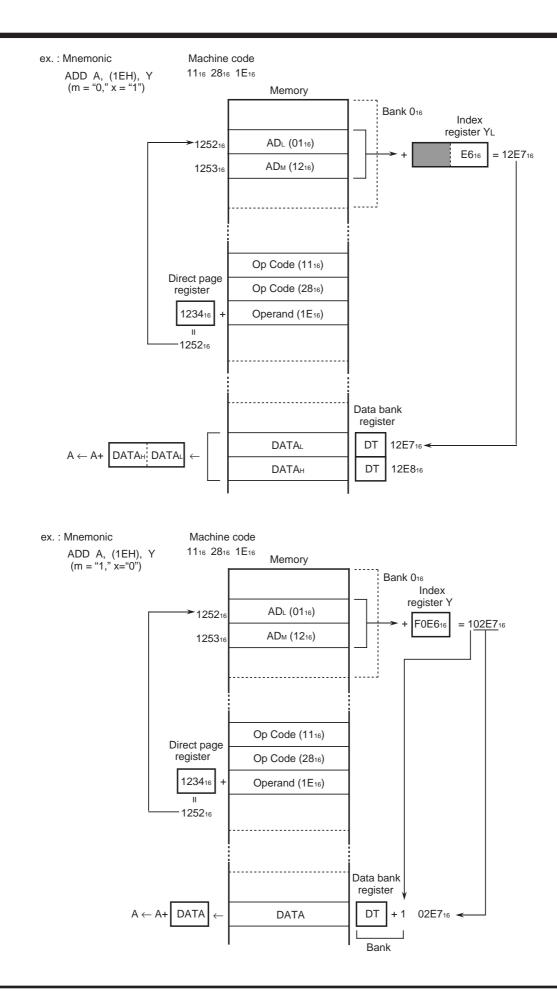

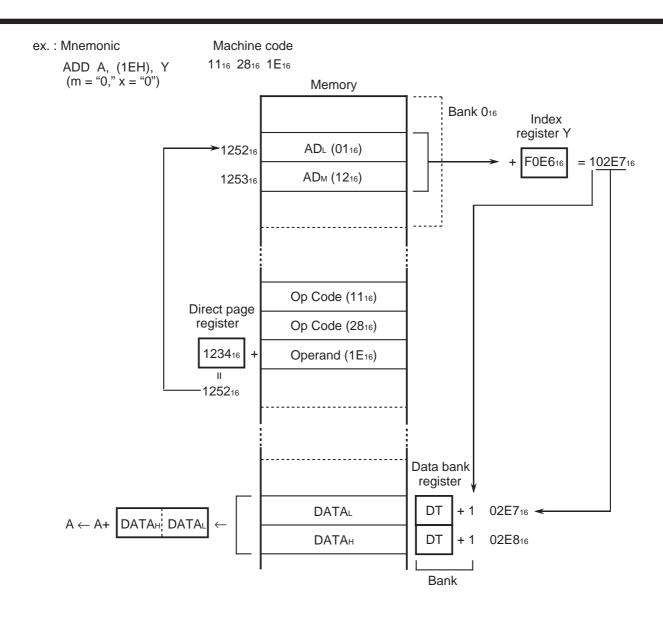

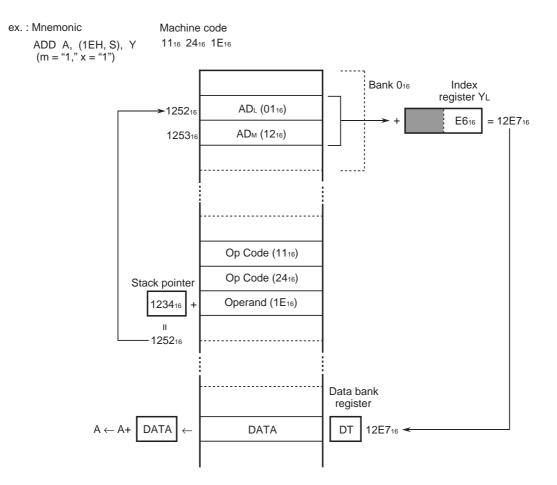

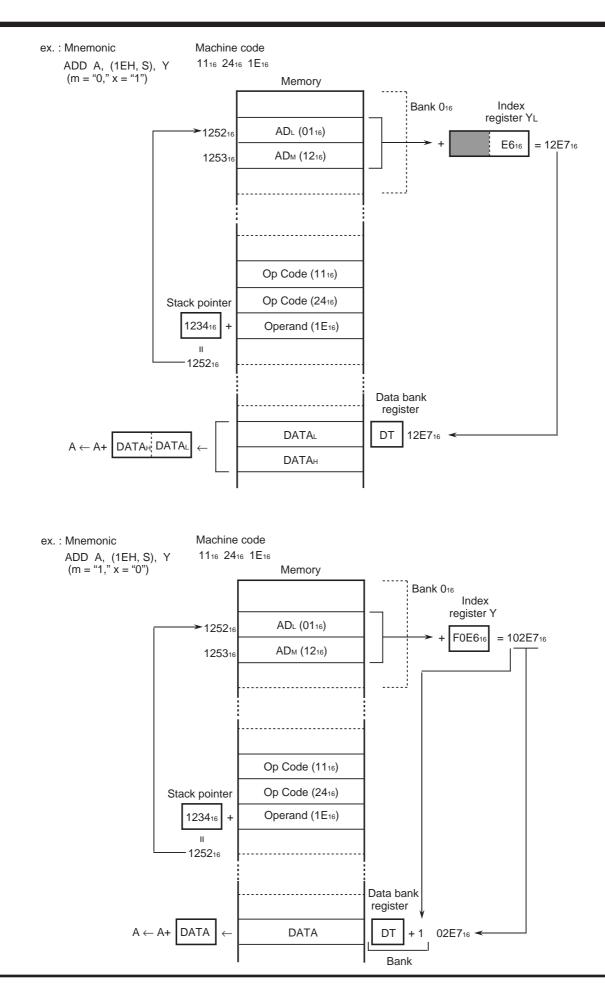

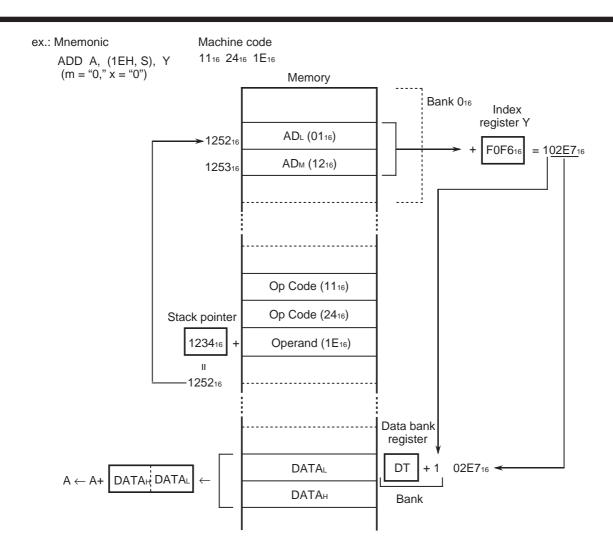

- Mode : Direct indirect indexed Y addressing mode

- **Function** : Specifies a sequence of 2-byte memory in bank 016 by the result of adding the instruction's operand to the direct page register's contents. The following is an actual data: the contents of the memory location specified by the result of adding the contents of these 2 bytes to the index register Y's contents and the contents of the data bank register. When, however, the result of adding the instruction's operand to the direct page register's contents exceeds the bank 016 range, the memory location in bank 116 is specified. Additionally, if the addition of the memory's contents and the index register Y's contents generates a carry, the value which is 1 larger than the contents of the data bank register indicates the bank.

## **Direct Indirect Indexed Y**

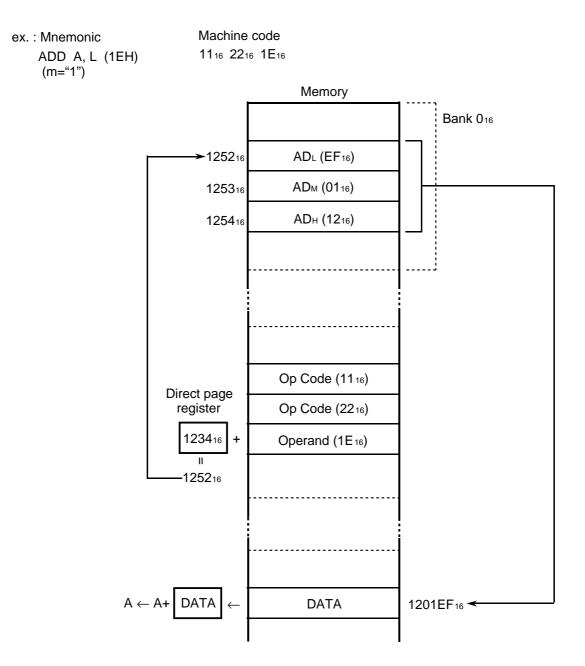

- Mode : Direct indirect long addressing mode

- **Function :** Specifies a sequence of 3-byte memory in bank 016 by the result of adding the instruction's operand to the direct page register's contents. The contents at the address specified by the contents of these 3 bytes are an actual data. When, however, the result of adding the instruction's operand to the direct page register's contents exceeds the bank 016 range, the memory location in bank 116 is specified. A sequence of 3-byte memory can cross over the bank boundary.

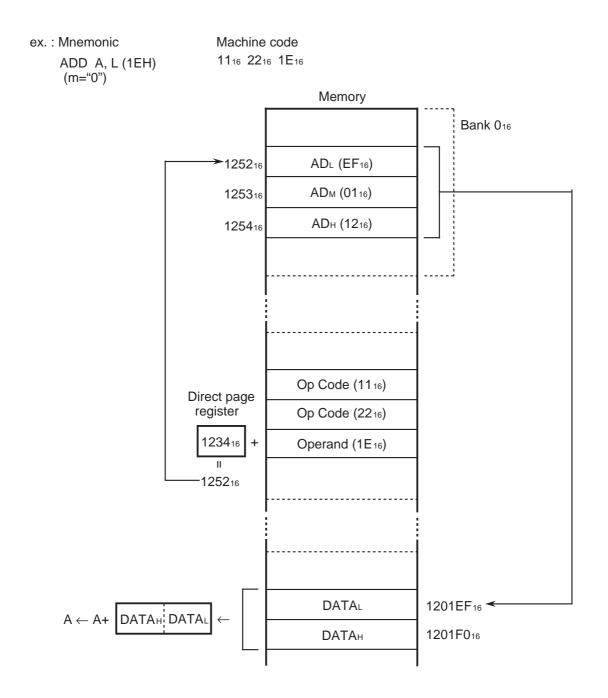

## **Direct Indirect Long Indexed Y**

- Mode : Direct indirect long indexed Y addressing mode

- **Function** : Specifies a sequence of 3-byte memory in bank 016 by the result of adding the instruction's operand to the direct page register's contents. The contents at the address specified by the result of adding the contents of these 3 bytes to the index register Y's contents are an actual data. When, however, the result of adding the instruction's operand to the direct page register's contents exceeds the bank 016 range, the memory location in bank 116 is specified. A sequence of 3-byte memory can cross over the bank boundary.

# **Direct Indirect Long Indexed Y**

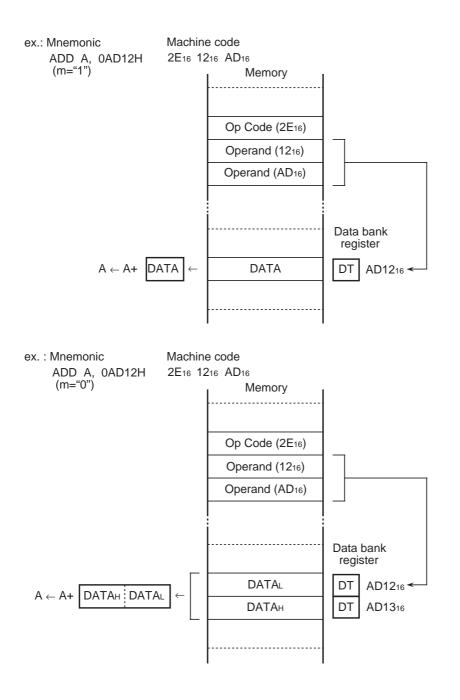

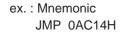

#### Mode : Absolute addressing mode

**Function** : The following is an actual data: the contents of the memory location specified by the instruction's operands and the contents of the data bank register. Note that, in the cases of the JMP and JSR instructions, the instruction's operands are transferred to the program counter.

## Absolute

Machine code

9C16 1416 AC16

- **Note :** Note the branch destination bank in the case where a JMP or a JSR instruction is located near a bank boundary.

- ⇒Refer to the description of a JMP/JMPL instruction (Page 4-111). Refer to the description of a JSR/JSRL instruction (Page 4-112).

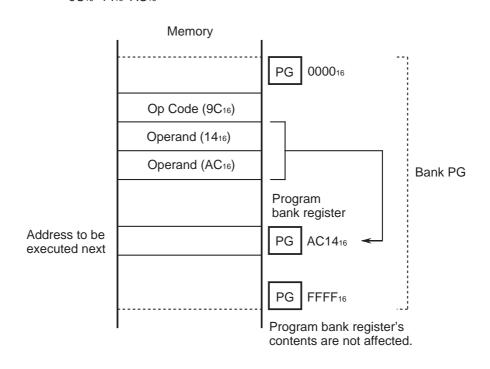

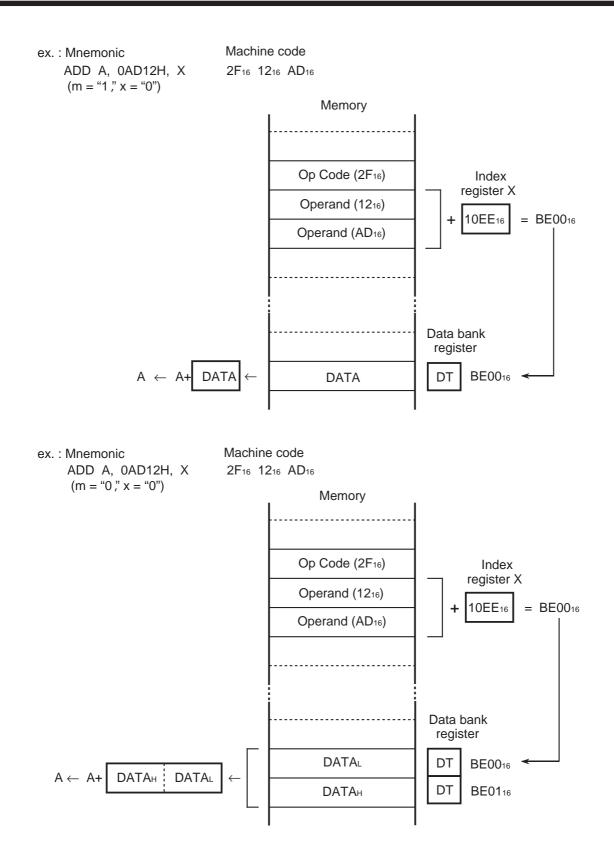

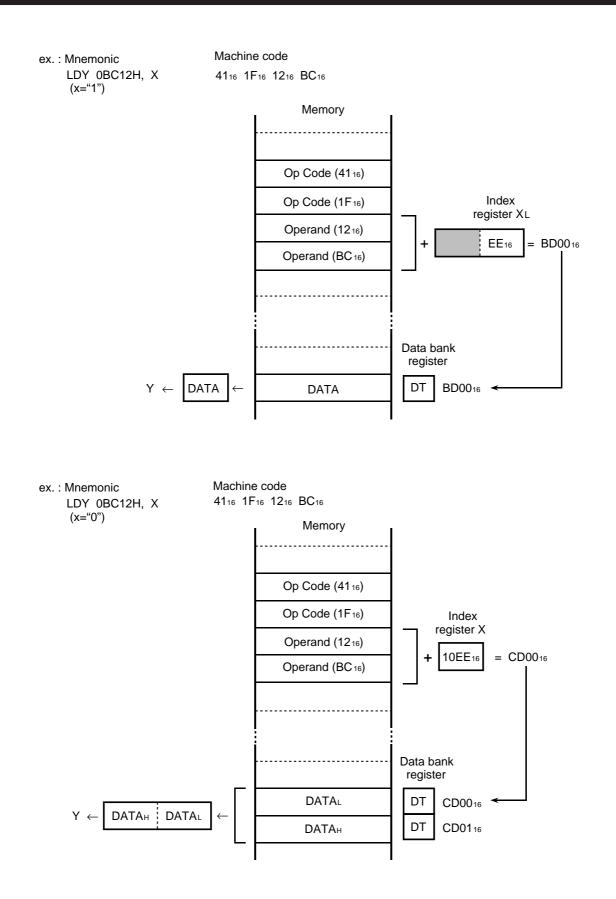

Mode : Absolute indexed X addressing mode

**Function** : The following is an actual data: the contents of the memory location specified by the result of adding a 16-bit length numerical value expressed with the instruction's operands to the index register X's contents, and the contents of the data bank register. If, however, the addition of the numerical value expressed with the instruction's operands and the index register X's contents generates a carry, the value which is 1 larger than the contents of the data bank register indicates the bank.

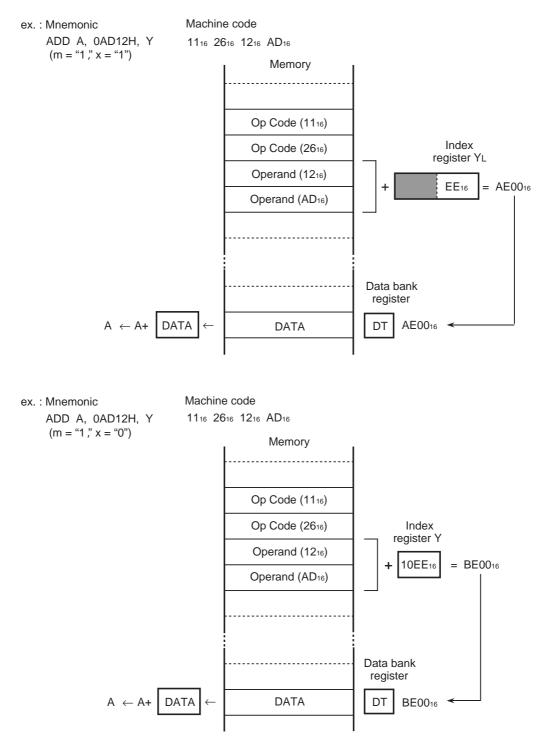

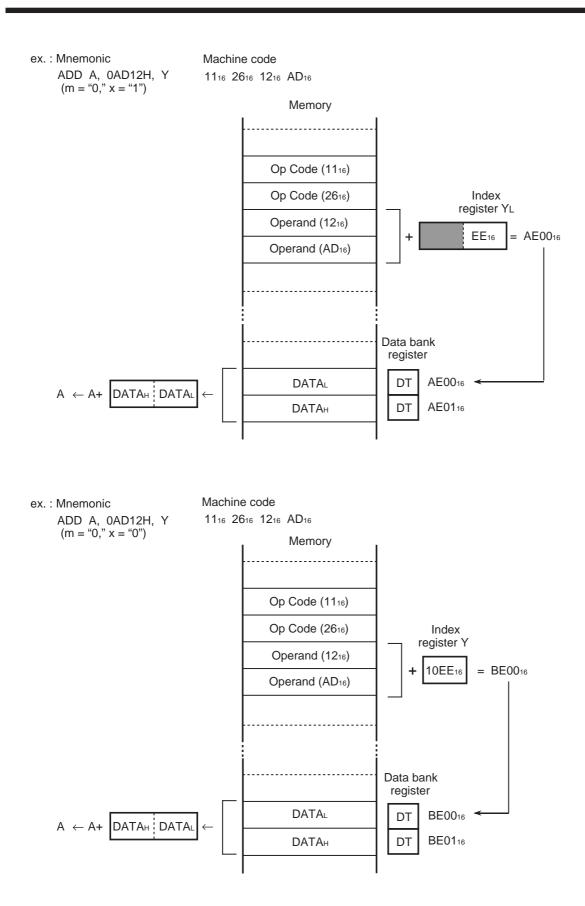

- Mode : Absolute indexed Y addressing mode

- **Function** : The following is an actual data: the contents of the memory location specified by the result of adding a 16-bit length numerical value expressed with the instruction's operands to the index register Y's contents, and the contents of the data bank register. If, however, the addition of the numerical value expressed with the instruction's operands to the index register Y's contents generates a carry, the value which is 1 larger than the contents of the data bank register indicates the bank.

## **Absolute Long**

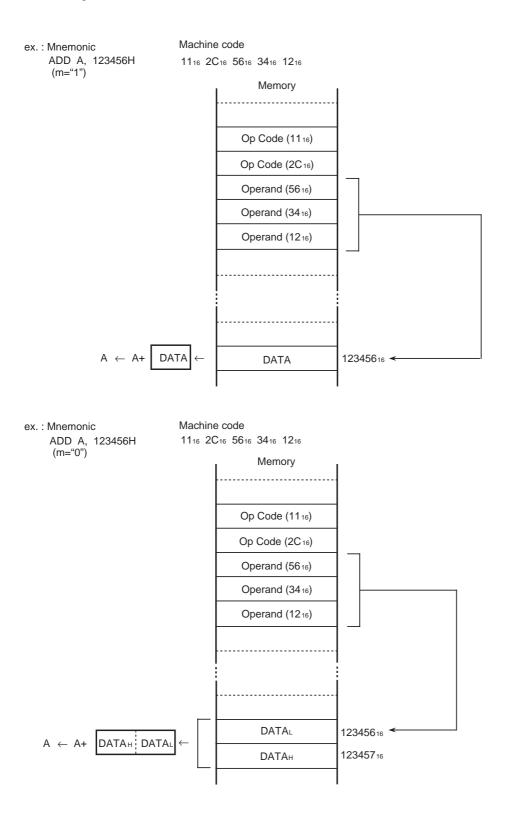

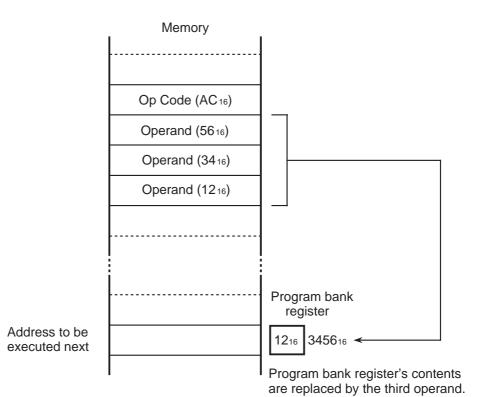

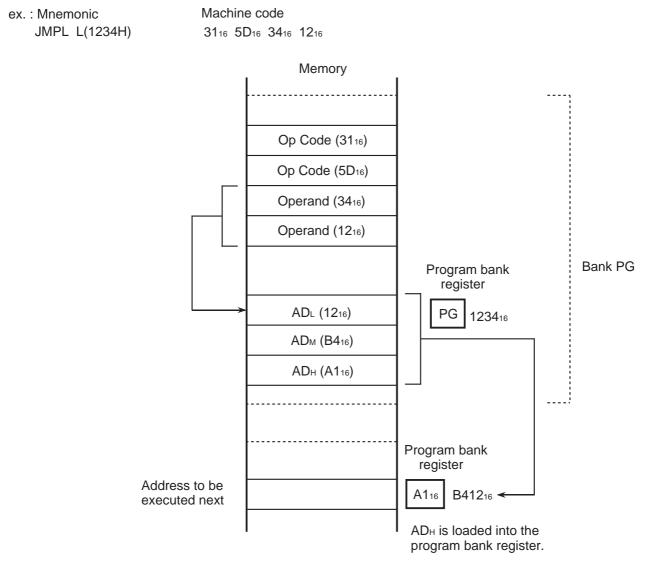

#### Mode : Absolute long addressing mode

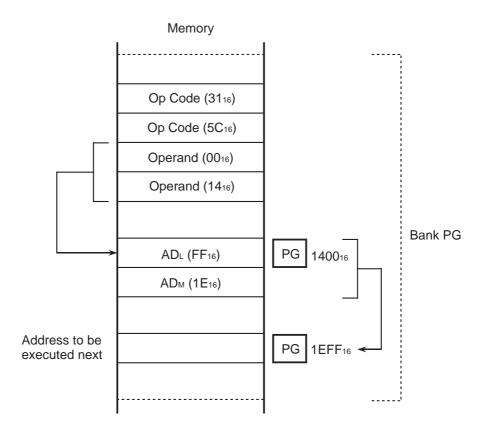

**Function** : The contents of the memory location specified by the instruction's operands are an actual data. Note that, in the cases of the JMPL and JSRL instructions, the instruction's second and third bytes are transferred to the program counter and the fourth byte is transferred to the program bank register.

ex. : Mnemonic JMPL 123456H Machine code AC16 5616 3416 1216

### **Absolute Long Indexed X**

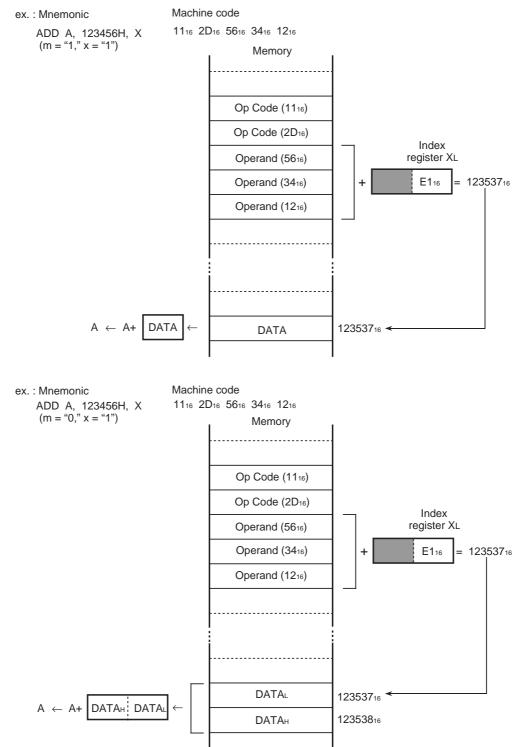

- Mode : Absolute long indexed X addressing mode

- **Function** : The following is an actual data: the contents of the memory location specified by the result of adding a numerical value expressed with the instruction's operands to the index register X's contents.

- Mode : Absolute indirect addressing mode

- **Function** : A sequence of 2-byte memory is specified by the instruction's third and fourth bytes in the same program bank. The contents of this 2-byte memory specify the branch destination address within the same program bank.

This addressing mode is used by a JMP instruction.

ex. : Mnemonic Machine code JMP (1400H) 31<sub>16</sub> 5C<sub>16</sub> 00<sub>16</sub> 14<sub>16</sub>

Note : Note the reference/branch destination bank when an instruction or a reference destination is located near a bank boundary.

⇒ Refer to the description of a JMP/JMPL instruction (Page 4-111).

### **Absolute Indirect Long**

- Mode : Absolute indirect long addressing mode

- **Function** : A sequence of 3-byte memory is specified by the instruction's third and fourth bytes in the same program bank. The contents of this 3-byte memory specify the branch destination address. This addressing mode is used by a JMPL instruction.

Note : Note the reference destination bank when an instruction is located near a bank boundary.

⇒Refer to the description of a JMP/JMPL instruction (Page 4-111).

## **Absolute Indexed X Indirect**

- Mode : Absolute indexed X indirect addressing mode

- **Function** : A sequence of 2-byte memory is specified by the result of adding a numerical value expressed with the instruction's second and third bytes to the index register X's contents; the memory bank is specified by program bank register PG at this time. The contents of this 2-byte memory specify the branch destination address.

This addressing mode is used by a JMP and a JSR instructions.

- ex.: Mnemonic Machine code JMP (1234H, X) BC16 3416 1216 (x = "1")Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . , Index Op Code (BC16) register X∟ Operand (3416) 1216 = 124616 Operand (1216) Bank PG 124616 ADL (1216) 124716 ADM (BC16) Program bank register Address to be BC1216 PG executed next .....

- **Note :** Note the reference/branch destination bank in the case of a JMP or a JSR instruction when the instruction or the branch destination address is located near a bank boundary.

- ➢ Refer to the description of a JMP/JMPL instruction (Page 4-111).

- Refer to the description of a JSR/JSRL instruction (Page 4-112).

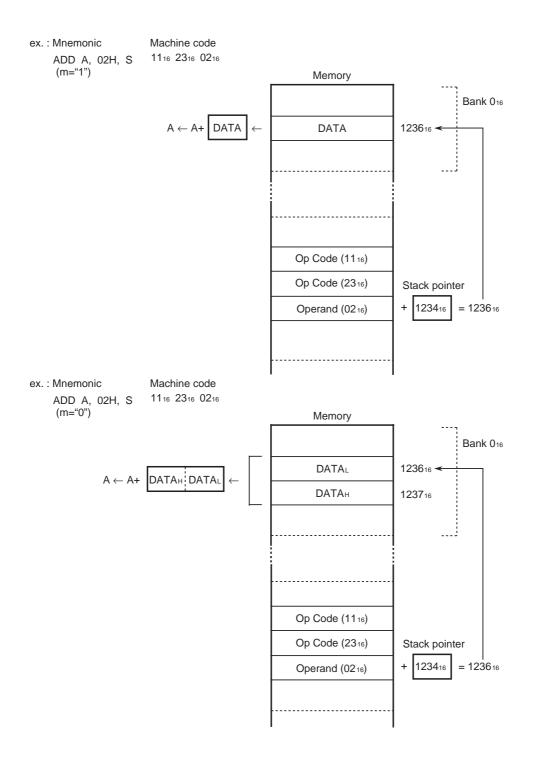

Mode : Stack addressing mode

**Function** : The contents of a register or others are stored to or restored from the memory of which location is specified by the stack pointer; this memory is called "stack area." The stack area is set in bank 016.

## Stack

ex. : Mnemonic PER #1234H Machine code

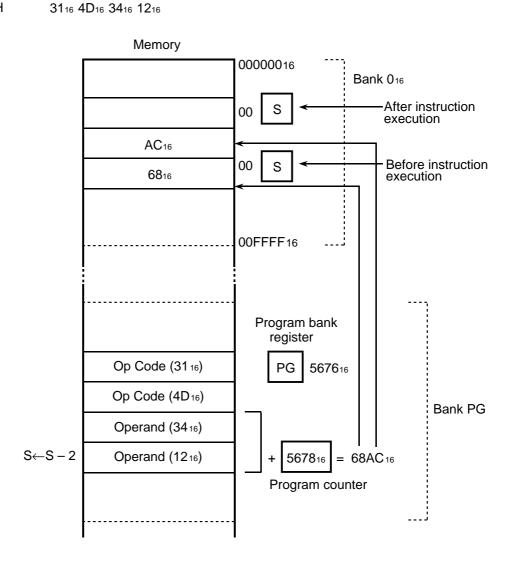

#### Mode : Relative addressing mode

**Function** : Branches to the address specified by the result of adding the program counter's contents to the instruction's second byte. In the case of a long branch with the BRA instruction, the instruction's second and third bytes are added to the program counter's contents as a 15-bit signed numerical value. In the case of the BSR instruction, the instruction's 3 bits of the first byte and the second byte are added to the program counter's contents as a 11-dit signed numerical value. If the addition generates a carry or a borrow, 1 is added to or subtracted from the program bank register.

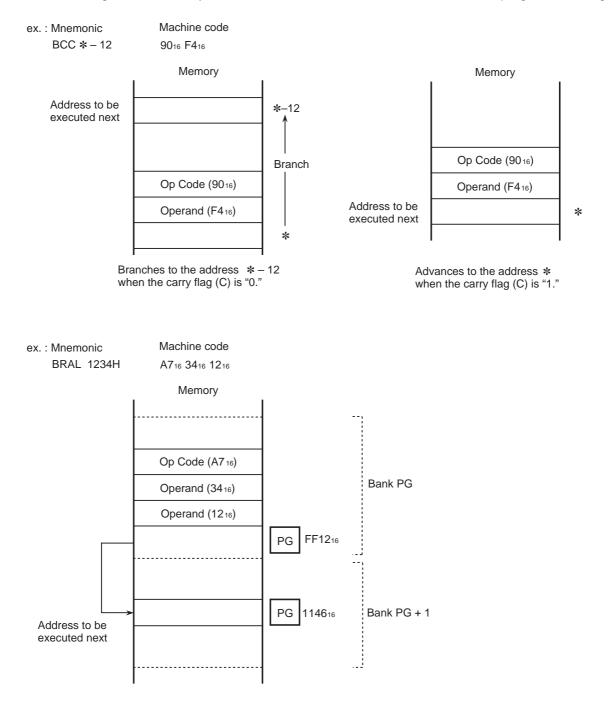

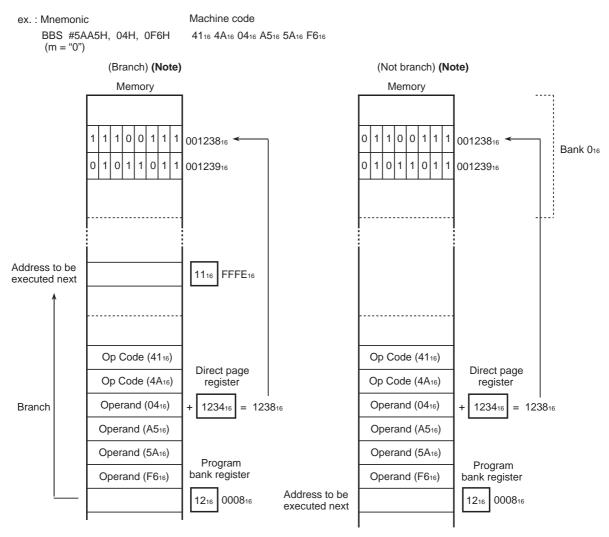

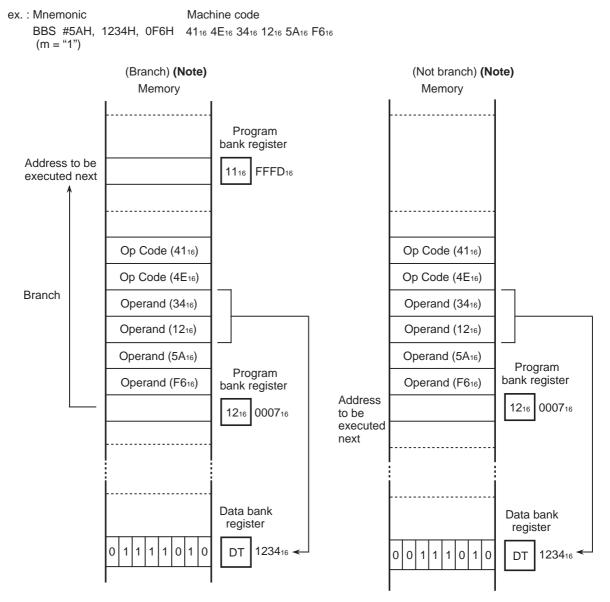

#### Mode : Direct bit relative addressing mode

Function : • BBC and BBS instructions

Specifies the memory location in bank 016 by the result of adding the instruction's third byte to the direct page register's contents; specifies the multiple bits' position in that memory by the bit pattern of the instruction's fourth and fifth bytes (when the m flag is "1," the fourth byte only). Then, when the specified bits all satisfy the branching conditions, branches to the address specified by the result of adding the instruction's sixth byte (or when the m flag is "1," the fifth byte) as a signed numerical value to the program counter's contents. When, however, the result of adding the instruction's second byte to the direct page register's contents exceeds the bank 016 range, the memory location in bank 116 is specified.

• BBCB and BBSB instructions

Specifies the memory location in bank 016 by the result of adding the instruction's second byte to the direct page register's contents; specifies the multiple bits' position in that memory by the bit pattern of the instruction's third byte. Then, when the specified bits all satisfy the branching conditions, branches to the address specified by the result of adding the instruction's fourth byte as a signed numerical value to the program counter's contents. When, however, the result of adding the instruction's second byte to the direct page register's contents exceeds the bank 016 range, the memory location in bank 116 is specified.

Note: Whether to branch or not depends on the branching conditions.

### **Direct Bit Relative**

Note: Whether to branch or not depends on the branching conditions.

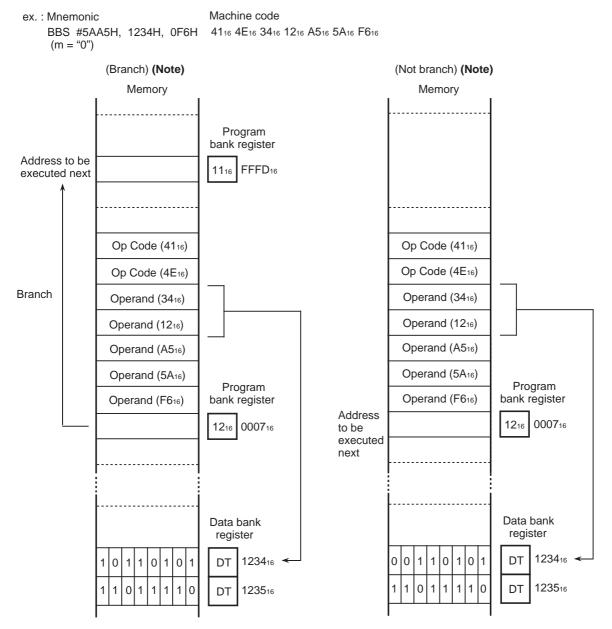

- Mode : Absolute bit relative addressing mode

- Function : BBC and BBS instructions

Specifies the memory location by the instruction's third and fourth bytes and the contents of the data bank register; specifies the multiple bits' position in that memory by the bit pattern of the instruction's fifth and sixth bytes (when the m flag is "1," the fifth byte only). Then, when the specified bits all satisfy the branching conditions, branches to the address specified by the result of adding the instruction's seventh byte (or when the m flag is "1," the sixth byte) as a signed numerical value to the program counter's contents.

• BBCB and BBSB instructions

Specifies the memory location by the instruction's second and third bytes and the contents of the data bank register; specifies the multiple bits' position in that memory by the bit pattern of the instruction's fourth byte. Then, when the specified bits all satisfy the branching conditions, branches to the address specified by the result of adding the instruction's fifth byte as a signed numerical value to the program counter's contents.

Note: Whether to branch or not depends on the branching conditions.

### **Absolute Bit Relative**

Note: Whether to branch or not depends on the branching conditions.

- Mode : Stack pointer relative addressing mode

- **Function** : The contents of the memory location in bank 016 are an actual data. This memory is specified by the result of adding the instruction's operand to the stack pointer's contents. When, however, the result of adding the instruction's operand to the stack pointer's contents exceeds the bank 016 range, the memory location in bank 116 is specified.

## **Stack Pointer Relative Indirect Indexed Y**

#### Mode : Stack pointer relative indirect indexed Y addressing mode

**Function** : Specifies a sequence of 2-byte memory by the result of adding the instruction's operand to the stack pointer's contents. The contents of the memory location specified by the above addition are added to the index register Y's contents. The result of second addition and the contents of data bank register DT indicate the memory location which contents an actual data. If, however, the result of adding the contents of that sequence of 2-byte memory to the index register Y's contents generates a carry, the value which is 1 larger than the contents of the data bank register DT indicates the bank.

### **Stack Pointer Relative Indirect Indexed Y**

## **Stack Pointer Relative Indirect Indexed Y**

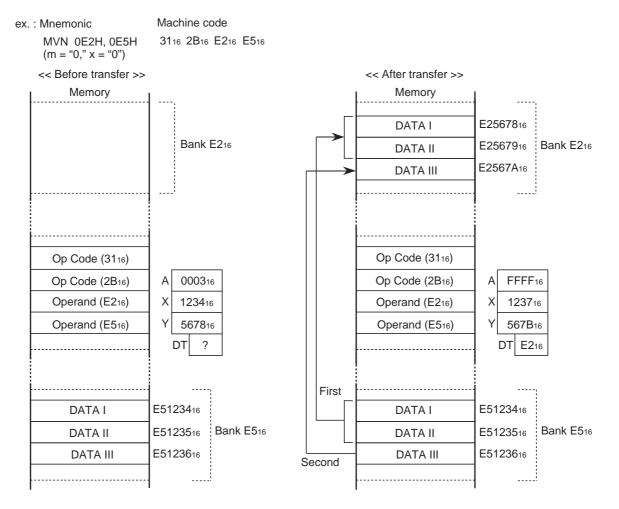

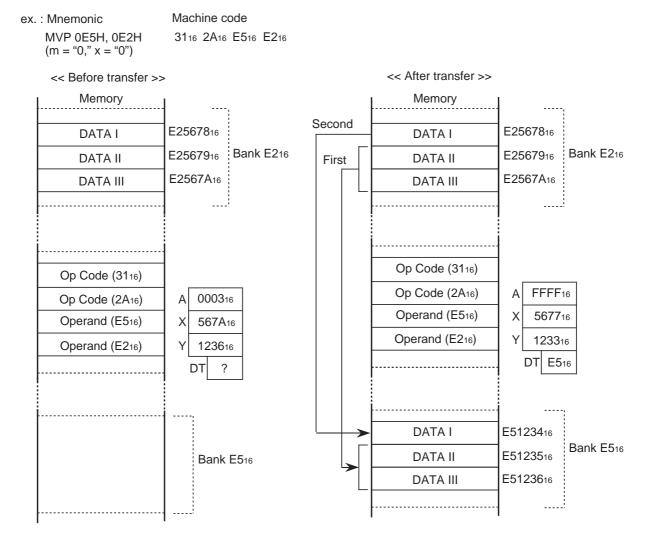

#### Mode : Block transfer addressing mode

- **Function** : Specifies the transfer destination data bank by the instruction's third byte, and specifies the transfer destination address within the data bank by the index register Y's contents. Specifies the transfer source data bank by the instruction's fourth byte, and specifies the address of transfer data within the data bank by the index register X's contents. The accumulator A's contents are the number of bytes to be transferred. At termination of transfer, the data bank register's contents specify the transfer destination data bank.

- MVN instruction The MVN instruction is used for transfer toward lower addresses. In this case, the contents of index registers X and Y are incremented each time data is transferred.

- MVP instruction

The MVP instruction is used for transfer toward higher addresses. In this case, the contents of index registers X and Y are decremented each time data is transferred. The transfer data can cross over the bank boundary.

**Note :** For block transfer instructions, the number of bytes to be transferred and the range can be specified as transfer source/destination addresses change with the state of the m and x flags. However, the transfer unit is unaffected. The transfer unit is "word" (16 bits). However, only 1 byte is transferred when transferring the last byte at odd-byte transfer.

## **Multiplied accumulation**

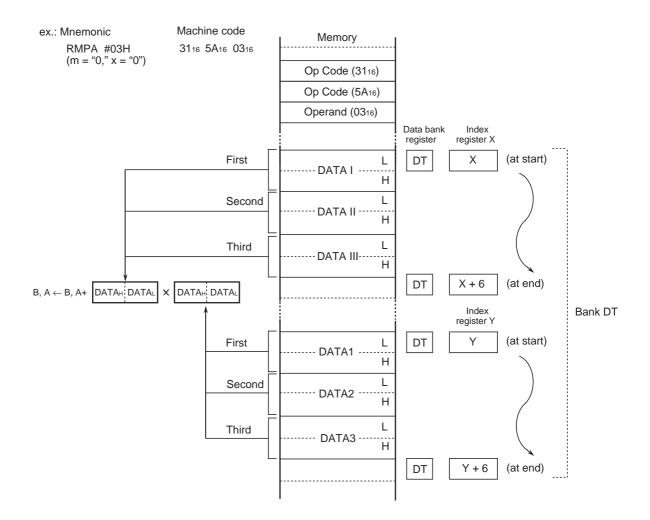

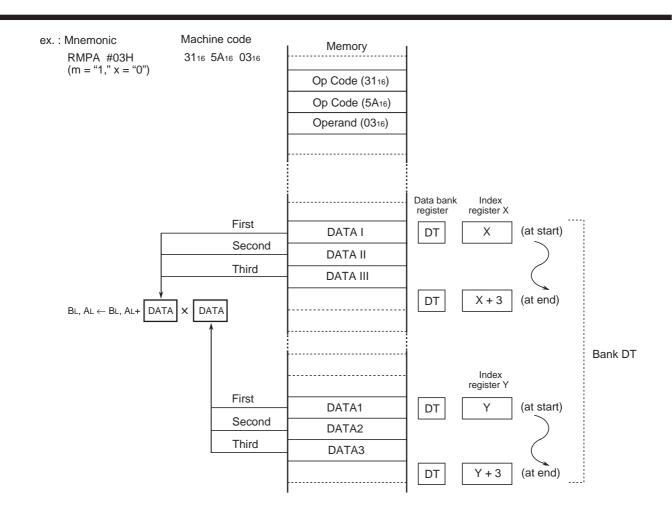

#### Mode : Multiplied accumulation addressing mode

**Function** : The following is a multiplicand and a multiplier: the contents of the memory location specified by the contents of index registers X and Y, and the data bank register's contents. The instruction's third byte is the repeat number of arithmetic operation. The contents of index registers X and Y are incremented each time the addition of the contents of accumulators B and A to the multiplication result finishes. Accordingly, the contents of index registers X and Y specify the next address where the multiplicand and the multiplier are read at last.

Allocate a multiplicand and a multiplier within the same bank and do not cross them over the bank boundary.

Set index register length flag x to "0" before executing this instruction.

This addressing mode is used by an RMPA instruction.

## **Multiplied accumulation**

# CHAPTER 3 HOW TO USE 7900 SERIES INSTRUCTIONS

- 3.1 Memory access

- 3.2 Direct page registers (DPR0-DPR3)

- 3.3 8- and 16-bit data processing

- 3.4 Index registers X and Y

- 3.5 Branch instructions

## HOW TO USE 7900 SERIES INSTRUCTIONS

### 3.1 Memory access

### 3.1 Memory access

Memory access modes are typically classified into the following 3 categories:

- Direct addressing

- Absolute addressing and Absolute long addressing

- Indirect addressing and Indirect long addressing

Their features are described below.

#### 3.1.1 Direct addressing

- Each instruction has a length of 2 or 3 bytes.

- Reduced number of consumed instruction execution cycles.

- A block (within bank 0: addresses 00000016-00FFF16) of which base address is specified by DPRn is addressable.

- (i) Direct page register select bit is "0": Block size = 256 bytes

- (ii) Direct page register select bit is "1":

Block size = 64 bytes

When a sum of DPRn's contents and an offset value exceeds the bank boundary, however, access over the boundary is enabled.

### 3.1.2 Absolute addressing and Absolute long addressing

### (1) Absolute addressing

- Each instruction has a length of 3 or 4 bytes.

- A 64-Kbyte space (a bank within addresses 000000<sub>16</sub>-FFFFF<sub>16</sub>) is addressable, where the high-order 8 bits of 24-bit address are specified by DT. For the JMP and JSR instructions, however, these high-order 8 bits are specified by PG.

#### (2) Absolute long addressing

- Each instruction has a length of 4 or 5 bytes.

- Addresses 00000016-FFFFF16 are addressable. All of 24 bits of the address are directly specified.

#### 3.1.3 Indirect addressing and Indirect long addressing

#### (1) Direct indirect addressing

- Each instruction has a length of 2 or 3 bytes.

- 16-bit pointer data is placed in the space specified by DPRn, and the specified memory is accessed.

- A 64-KB space (a bank within addresses 00000016-FFFFFF16) is addressable, where the highorder 8 bits of 24-bit address are specified by DT.

#### (2) Direct indirect long addressing

- Each instruction has a length of 2 or 3 bytes.

- 24-bit pointer data is placed in the space specified by DPRn, and the specified memory is accessed.

- An address within the 16-Mbyte space (addresses 00000016-FFFFFF16) is addressable.

#### (3) Absolute indirect addressing

- This addressing mode can be used only for the indirect branch and indirect subroutine call instructions.

- Each instruction has a length of 3 or 4 bytes.

- 16-bit pointer data is placed in the space specified by PG, and the specified memory is accessed.

- A 64-KB space (a bank within addresses 00000016-FFFFFF16) is addressable, where the highorder 8 bits of 24-bit address are specified by PG.

#### (4) Absolute indirect long addressing

- This addressing mode can be used only for the indirect branch instruction.

- Each instruction has a length of 3 or 4 bytes.

- 24-bit pointer data is placed in the space specified by PG, and the specified memory is accessed.

- Any address of the 16-Mbyte space (addresses 00000016-FFFFF16) is addressable.

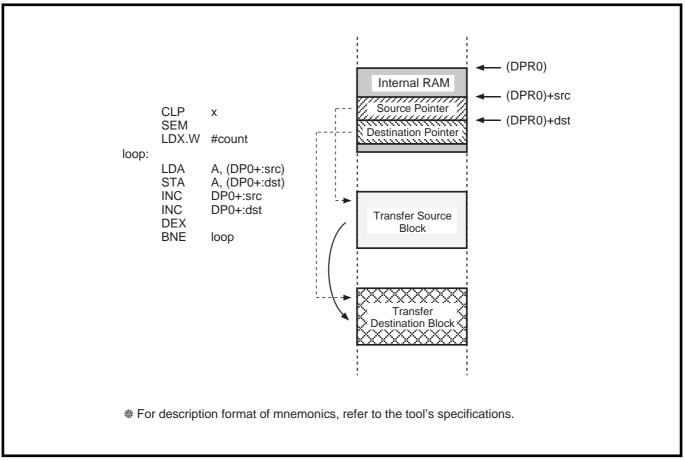

Figure 3.1.1 shows a usage example of indirect addressing mode.

Here, the data of the pointers pointing to memory areas are processed in the program, and the results are referenced as effective addresses.

Fig. 3.1.1 Usage example of indirect addressing mode: block transfer

The 7900 Series also provides many other useful addressing modes. For details, refer to section "2.3 Addressing modes."

3.2 Direct page registers (DPR0–DPR3)

## 3.2 Direct page registers (DPR0-DPR3)

The 7900 Series provides more enhanced direct addressing modes than those of the conventional 7700 Family. These powerful addressing modes greatly improve programming efficiency, especially in a range of addresses  $000000_{16}-00FFFF_{16}$ .

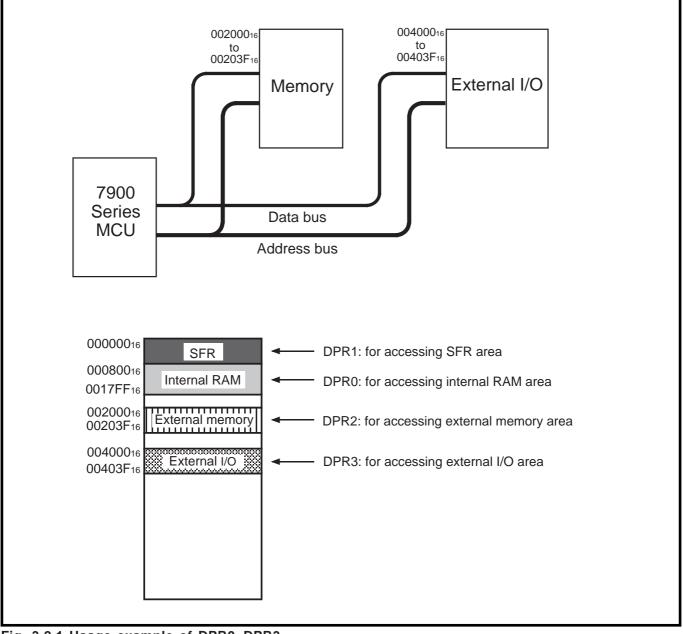

In the 7900 Series, just after a reset, only DPR0 can be used. When the direct page register select bit of the processor mode register 1 is set to "1," however, direct page registers DPR0–DPR3 can be used. Figure 3.2.1 shows an usage example of DPR0–DPR3.

In the conventional 7700 Family, since only one direct page register can be used, it is required to frequently change the contents of the direct page register for efficient memory access using direct page addressing mode. On the contrary, the 7900 Series does not need such a procedure as in the conventional 7700 Family because it can assign a direct page register to each base address of each block.

Fig. 3.2.1 Usage example of DPR0–DPR3

### 3.3 8- and 16-bit data processing

In the conventional 7700 Family, the same machine code is assigned to an 8- and its corresponding 16-bit instruction in order to reduce program size, so that it is necessary to specify whether 8- or 16-bit data is processed, by using flags m and x. The 7900 Series incorporates new instructions with the conventional instructions. These new instructions enable 8-bit operation independent of flags m and x. By using these new instructions, 8-bit data can be processed while flags are set for 16-bit data length, preventing an overhead generated by setting flags. Figure 3.3.1 shows an 8-bit operation example.

### Fig. 3.3.1 8-bit operation example

When executing the instructions that require the data length setting by flags m and x, the number of bytes or execution cycles is affected by this setting. For details, refer to section "4.2 Description of each instruction" or "Appendix 1. 7900 Series machine instructions."

## HOW TO USE 7900 SERIES INSTRUCTIONS

### 3.4 Index registers X and Y

### 3.4 Index registers X and Y

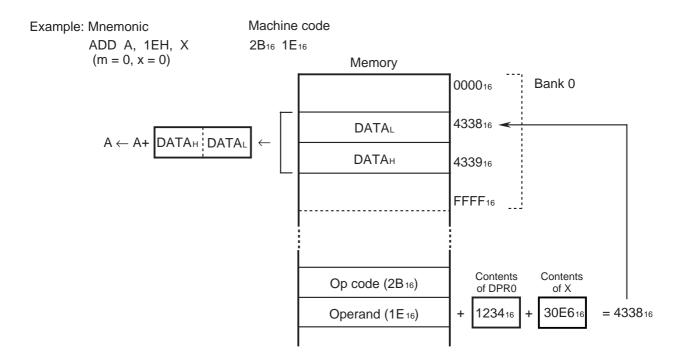

The contents of index register X or Y facilitate to specify an effective address. For example, the direct indexed X addressing mode is described below. Refer to section "**2.3 Addressing modes**" for details.

#### <Example> Direct indexed X addressing mode

A sum of the instruction's operand, the contents of a direct page register, and the contents of index register X indicates a memory location in bank 0. The contents in this memory location are data to be processed. However, when the above sum exceeds the boundary of bank 0 or bank 1, a memory location in bank 1 or bank 2 is specified, respectively.

3.5 Branch instructions

## 3.5 Branch instructions

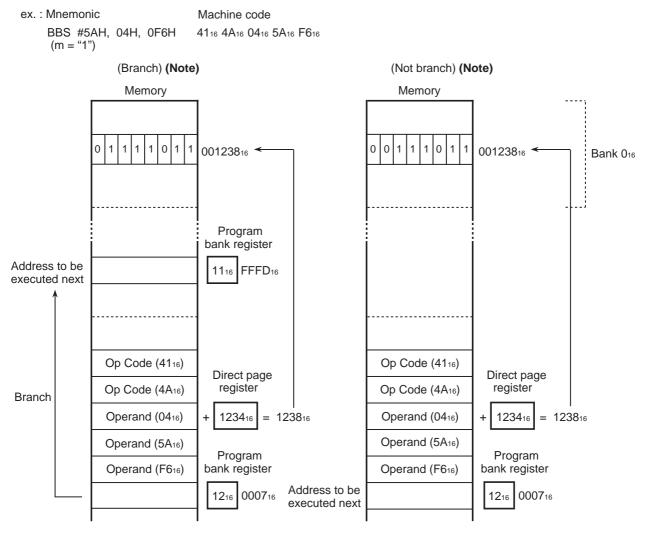

The branch instructions are classified into the following 6 categories:

- (1) Relative branch

- (2) Absolute branches (absolute and absolute long)

- (3) Indirect branches (absolute indirect and absolute indirect long)

- (4) Relative subroutine call

- (5) Absolute subroutine calls (absolute and absolute long)

- (6) Indirect subroutine call (absolute Indexed X indirect)

Relative branch and relative subroutine call instructions have the following features:

- Each instruction has a length of 2 or 3 bytes.

- Program area can be reallocated dynamically during program execution.

- Addresses to which the program can branch are limited within a specified range. Refer to section "4.2 Description of each instruction" for details.

#### Examples:

| Exampleoi             |                                                                            |

|-----------------------|----------------------------------------------------------------------------|

| (i) BRA instruction   | Within a range of -128 to +127 referenced to PC just after instruction     |

|                       | execution                                                                  |

| (ii) BRAL instruction | Within a range of -32768 to +32767 referenced to PC just after instruction |

|                       | execution                                                                  |

| (iii) BSR instruction | Within a range of -1024 to +1023 referenced to PC just after instruction   |

|                       | execution                                                                  |

|                       |                                                                            |

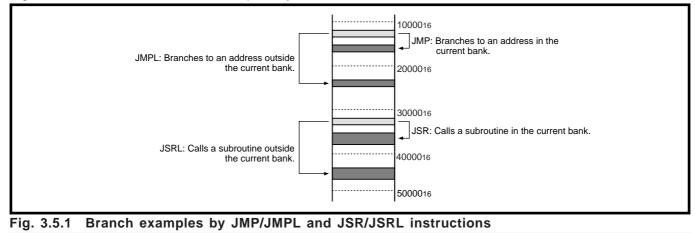

On the other hand, absolute branch, absolute subroutine call, indirect branch and indirect subroutine call instructions have the following features:

• Any address within the 16-Mbyte space can be directly specified as a branch destination address (absolute long).

• Any address limited within the 64-Kbyte space (a bank), containing PC being used, also can be specified as a branch destination address. In this case, byte length of an instruction and the number of instruction execution cycles can be reduced. Refer to section **"4.2 Description of each instruction"** for details.

#### Examples:

| (i) JMP instruction     | Branches to a 64-Kbyte space specified by PG in which the last byte of an instruction is located.                                                                     |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (ii) JMPL instruction … | Branches to a specified address within the 16-Mbyte space.                                                                                                            |

| (iii) JSR instruction … | Branches to a 64-Kbyte space specified by PG in which the last byte of an instruction is located. Returns from the branch destination address by the RTS instruction. |

| (iv) JSRL instruction   | Branches to a specified address within the 16-Mbyte space. Returns from the branch destination address by the RTL instruction.                                        |

Figure 3.5.1 shows the branch examples by JMP/JMPL and JSR/JSRL instructions.

# CHAPTER 4 INSTRUCTIONS

4.1 Instruction set

4.2 Description of each instruction

4.3 Notes for software development

## 4.1 Instruction set

## 4.1 Instruction set

The 7900 Series CPU uses the instruction set with 203 instructions.

Instructions marked by \* are the new instructions that have been added to the 7751 Series instruction set. The remarks column shows that a conventional 7700 Family's instruction is included in the corresponding new instruction.

| Category         | Instruction | Description                                                    | Remarks                   |

|------------------|-------------|----------------------------------------------------------------|---------------------------|

| Load             | LDA         | Acc ←M                                                         |                           |

|                  | * LDAB      | Acc ←M8 (Extended with "0"s.)                                  |                           |

|                  | * LDAD      | E ←M32                                                         |                           |

|                  | * LDD n     | DPRn←IMM16 (n = 0 to 3. Multiple operations can be specified.) |                           |

|                  | LDT         | DT ←IMM8                                                       |                           |

|                  | LDX         | $X \leftarrow M$                                               |                           |

|                  | * LDXB      | X $\leftarrow$ IMM8 (Extended with "0"s.)                      |                           |

|                  | LDY         | Y ←M                                                           |                           |

|                  | * LDYB      | Y ←IMM8 (Extended with "0"s.)                                  |                           |

| Store            | STA         | M ←Acc                                                         |                           |

|                  | * STAB      | M8 ←Acc∟                                                       |                           |

|                  | * STAD      | M32 ←E                                                         |                           |

|                  | STX         | M ←X                                                           |                           |

|                  | STY         | M ←Y                                                           |                           |

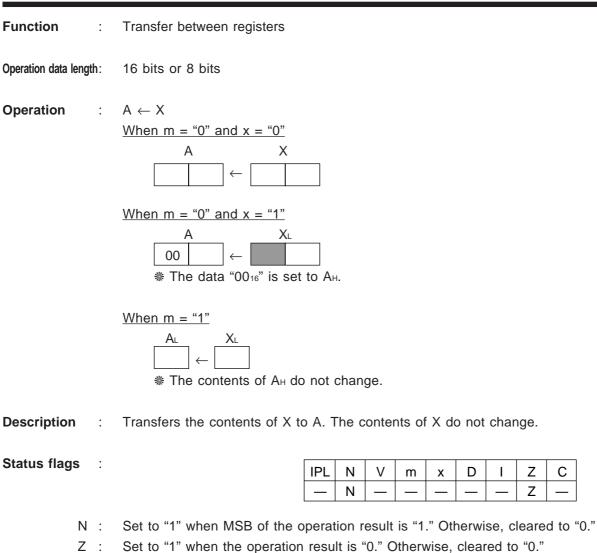

| Transfer between | * TAD n     | $DPRn \leftarrow A (n = 0 \text{ to } 3)$                      | including TAD instruction |

| registers        | TAS         | S ←A                                                           |                           |

|                  | TAX         | $X \leftarrow A$                                               |                           |

|                  | TAY         | Y ←A                                                           |                           |

|                  | * TBD n     | $DPRn \leftarrow B (n = 0 \text{ to } 3)$                      | including TBD instruction |

|                  | TBS         | S ←B                                                           |                           |

|                  | ТВХ         | X ←B                                                           |                           |

|                  | TBY         | Y ←B                                                           |                           |

|                  | * TDA n     | A $\leftarrow$ DPRn (n = 0 to 3)                               | including TDA instruction |

|                  | * TDB n     | B $\leftarrow$ DPRn (n = 0 to 3)                               | including TDB instruction |

|                  | * TDS       | S ←DPR0                                                        |                           |

|                  | TSA         | A ←S                                                           |                           |

|                  | TSB         | B ←S                                                           |                           |

|                  | * TSD       | DPR0←S                                                         |                           |

|                  | TSX         | X ←S                                                           |                           |

|                  | ТХА         | A ←X                                                           |                           |

|                  | ТХВ         | B ←X                                                           |                           |

|                  | TXS         | S ←X                                                           |                           |

|                  | TXY         | Y ←X                                                           |                           |

|                  | TYA         | A ←Y                                                           |                           |

|                  | TYB         | B ←Y                                                           |                           |

|                  | TYX         | $X \leftarrow Y$                                               |                           |

|                  | XAB         | A                                                              |                           |

| Category         | Instruction | Description                                                                       | Remarks                   |

|------------------|-------------|-----------------------------------------------------------------------------------|---------------------------|

| Transfer between | * MOVM      | $M \rightarrow M$                                                                 | including LDM instruction |

| memories         | * MOVMB     | M8 ←M8                                                                            |                           |

|                  | * MOVR      | $M(dest n) \leftarrow M(source n)$ (Multiple operations can                       |                           |

|                  |             | be specified.) $(n = 0 \text{ to } 15)$                                           |                           |

|                  | * MOVRB     | M8(dest n) ←M8(source n) (Multiple operations can                                 |                           |

|                  |             | be specified.) $(n = 0 \text{ to } 15)$                                           |                           |

| Block transfer   | MVN         | M (n to $n + i - 1$ ) $\leftarrow$ M (m to $m + i - 1$ ) (i:transfer byte number) |                           |

|                  | MVP         | M (n - i + 1 to n) $\leftarrow$ M (m - i + 1 to m) (i:transfer byte number)       |                           |

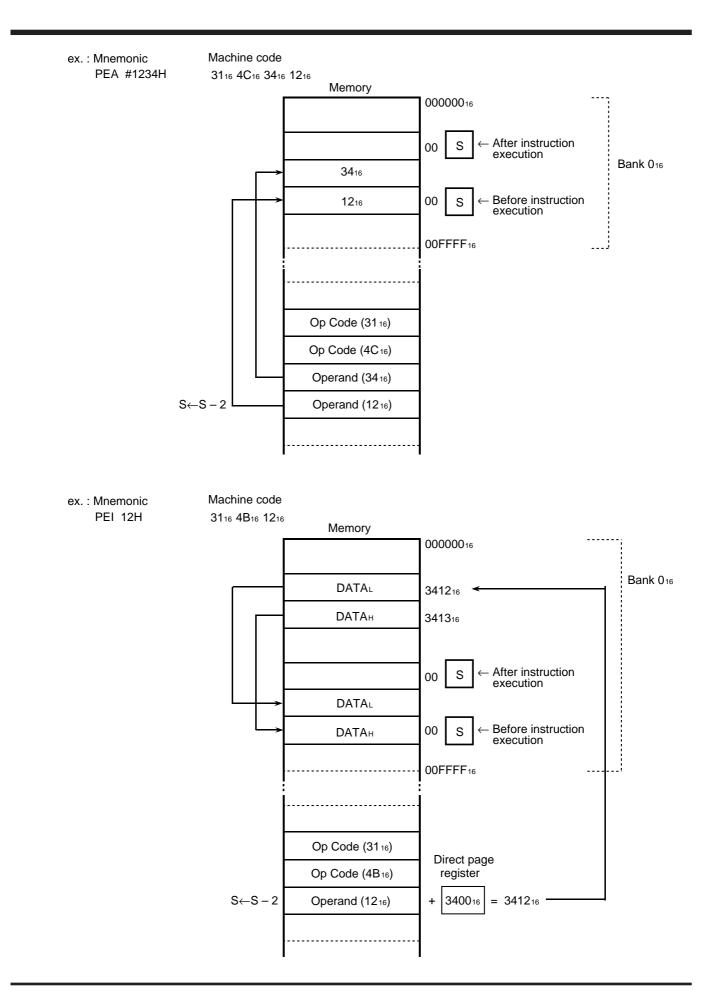

| Stack operation  | PEA         | Stack ←IMM16                                                                      |                           |

|                  | PEI         | Stack $\leftarrow$ M16 (DPRn + dd) (n = 0 to 3)                                   |                           |

|                  | PER         | Stack←PC + IMM16                                                                  |                           |

|                  | PHA         | Stack ← A                                                                         |                           |

|                  | PHB         | Stack ← B                                                                         |                           |

|                  | PHD         | Stack ← DPR0                                                                      |                           |

|                  | * PHD n     | Stack ← DPRn (n = 0 to 3. Multiple operations can be specified.)                  |                           |

|                  | PHG         | Stack ← PG                                                                        |                           |

|                  | PHP         | Stack←PS                                                                          |                           |

|                  | PHT         | Stack ← DT                                                                        |                           |

|                  | PHX         | Stack←X                                                                           |                           |

|                  | PHY         | Stack←Y                                                                           |                           |

|                  | PLA         | A ←Stack                                                                          |                           |

|                  | PLB         | B ←Stack                                                                          |                           |

|                  | PLD         | DPR0←Stack                                                                        |                           |

|                  | * PLD n     | DPRn←Stack (n = 0 to 3. Multiple operations can be specified.)                    |                           |

|                  | PLP         | PS ←Stack                                                                         |                           |

|                  | PLT         | DT ←Stack                                                                         |                           |

|                  | PLX         | X ←Stack                                                                          |                           |

|                  | PLY         | Y ←Stack                                                                          |                           |

|                  | PSH         | Stack $\leftarrow$ Any specified register among A, B, X, Y,                       |                           |

|                  |             | DPR0, DT, PG, and PS. (Multiple operations                                        |                           |

|                  |             | can be specified)                                                                 |                           |

|                  |             | M (S to $S-i+1$ ) $\leftarrow A, B, X, Y, DPR0, DT, PG, PS$                       |                           |

|                  |             | $S \leftarrow S - i$                                                              |                           |

|                  |             | (i : Number of bytes corresponding to the registers                               |                           |

|                  |             | saved to the stack.)                                                              |                           |

|                  | PUL         | Any specified register among A, B, X, Y, DPR0,                                    |                           |

|                  |             | DT, and PS. ←Stack (Multiple operations can be specified)                         |                           |

|                  |             | A, B, X, Y, DPR0, DT, PS $\leftarrow$ M (S + 1 to S + i)                          |                           |

|                  |             | $S \leftarrow S+i$                                                                |                           |

|                  |             | (i : Number of bytes corresponding to the registers                               |                           |

|                  |             | restored from the stack.)                                                         |                           |

|                  |             |                                                                                   |                           |

| Category               | Instruction | Description                                                            | Remarks |

|------------------------|-------------|------------------------------------------------------------------------|---------|

| Stack operation & Load | * PHLD n    | stack $\leftarrow$ DPRn, DPRn $\leftarrow$ IMM16 (n = 0 to 3. Multiple |         |

|                        |             | operations can be specified)                                           |         |

| Clearance              | * CLR       | Acc ←0                                                                 |         |

|                        | * CLRB      | Acc∟ ←0                                                                |         |

|                        | * CLRM      | M ←0                                                                   |         |

|                        | * CLRMB     | M8 ←0                                                                  |         |

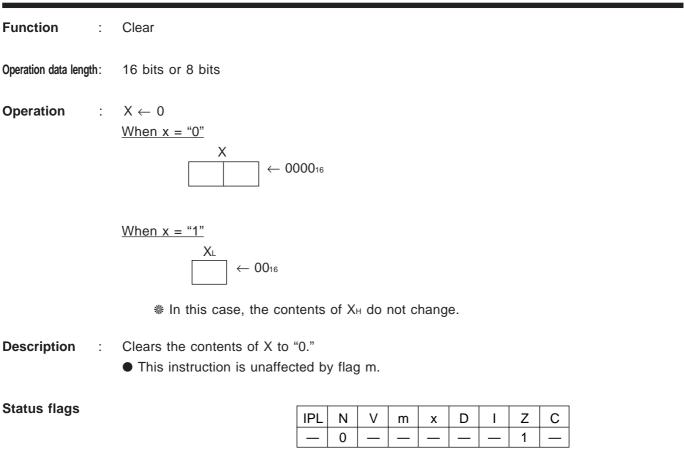

|                        | * CLRX      | $X \leftarrow 0$                                                       |         |

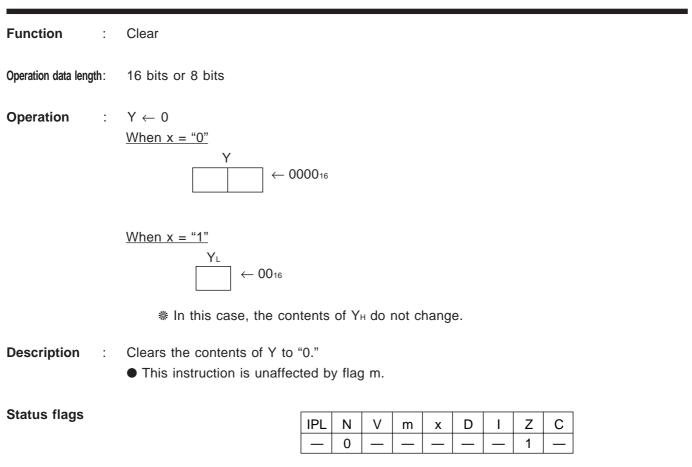

|                        | * CLRY      | Y ←0                                                                   |         |

| Addition               | ADC         | Acc $\leftarrow$ Acc + M + C                                           |         |

|                        | * ADCB      | Acc∟ ←Acc∟ + IMM8 + C                                                  |         |

|                        | * ADCD      | $E \leftarrow E + M32 + C$                                             |         |

|                        | * ADD       | Acc $\leftarrow$ Acc + M                                               |         |

|                        | * ADDB      | Acc∟ ←Acc⊾ + IMM8                                                      |         |

|                        | * ADDD      | $E \leftarrow E + M32$                                                 |         |

|                        | * ADDM      | $M \leftarrow M + IMM$                                                 |         |

|                        | * ADDMB     | M8 $\leftarrow$ M8 + IMM8                                              |         |

|                        | * ADDMD     | M32 ←M32 + IMM32                                                       |         |

|                        | * ADDS      | S ←S + IMM8                                                            |         |

|                        | * ADDX      | $X \leftarrow X + IMM (IMM = 0 \text{ to } 31)$                        |         |

|                        | * ADDY      | $Y \leftarrow Y + IMM (IMM = 0 \text{ to } 31)$                        |         |

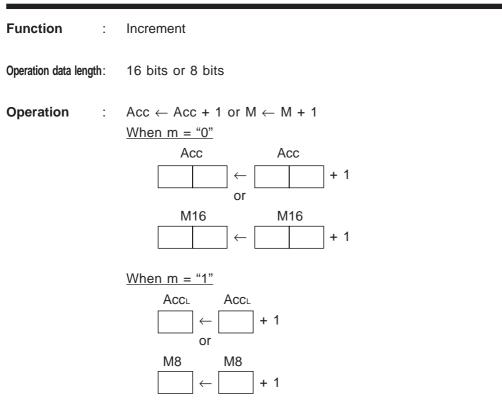

| Increment              | INC         | Acc $\leftarrow$ Acc + 1 or M $\leftarrow$ M + 1                       |         |

|                        | INX         | $X \leftarrow X + 1$                                                   |         |

|                        | INY         | $Y \leftarrow Y + 1$                                                   |         |

| Subtraction            | SBC         | Acc $\leftarrow$ Acc - M - $\overline{C}$                              |         |

|                        | * SBCB      | $Acc \leftarrow Acc \leftarrow - IMM8 - \overline{C}$                  |         |

|                        | * SBCD      | $E \leftarrow E - M32 - \overline{C}$                                  |         |

|                        | * SUB       | Acc ←Acc - M                                                           |         |

|                        | * SUBB      | Acc∟ ←Acc∟ − IMM8                                                      |         |

|                        | * SUBD      | $E \leftarrow E - M32$                                                 |         |

|                        | * SUBM      | $M \leftarrow M - IMM$                                                 |         |

|                        | * SUBMB     | M8 $\leftarrow$ M8 - IMM8                                              |         |

|                        | * SUBMD     | M32 ←M32 - IMM32                                                       |         |

|                        | * SUBS      | S ←S – IMM8                                                            |         |

|                        | * SUBX      | $X \leftarrow X - IMM (IMM = 0 \text{ to } 31)$                        |         |

|                        | * SUBY      | Y $\leftarrow$ Y - IMM (IMM = 0 to 31)                                 |         |

| Decrement              | DEC         | Acc $\leftarrow$ Acc - 1 or M $\leftarrow$ M - 1                       |         |

|                        | DEX         | $X \leftarrow X - 1$                                                   |         |

|                        | DEY         | $Y \leftarrow Y - 1$                                                   |         |

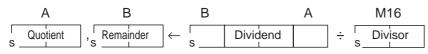

| Multiplication         | MPY         | (B, A) $\leftarrow$ A (Multiplicand) X M (Multiplier), Unsigned        |         |

| -                      | MPYS        | $(B, A) \leftarrow A$ (Multiplicand) X M (Multiplier), Signed          |         |

| Division               | DIV         | A (Quoitent), B (remainder) $\leftarrow$ (B, A) $\div$ M, Unsigned     |         |

|                        | DIVS        | A (Quoitent), B (remainder) $\leftarrow$ (B, A) $\div$ M, Signed       |         |

| Multiplied             | RMPA        | $(B, A) \leftarrow (B, A) + M (DT:X) \times M (DT:Y)$                  |         |

| accumulation           |             | (repeating 0 to 255 times)                                             |         |

|                        |             |                                                                        |         |

| Category               | Instruction | Description                                                       | Remarks       |

|------------------------|-------------|-------------------------------------------------------------------|---------------|

| Logical OR             | ORA         | Acc ←Acc∨M                                                        |               |

|                        | * ORAB      | Acc∟ ←Acc∟∨IMM8                                                   |               |

|                        | * ORAM      | $M \leftarrow M \lor IMM$                                         | Including SEB |

|                        |             |                                                                   | instruction   |

|                        | * ORAMB     | M8 $\leftarrow$ M8 $\vee$ IMM8                                    |               |

|                        | * ORAMD     | M32 ←M32∨IMM32                                                    |               |

| Logical AND            | AND         | Acc ←Acc∧M                                                        |               |

|                        | * ANDB      | Acc∟ ←Acc∟∧IMM8                                                   |               |

|                        | * ANDM      | $M \leftarrow M \land MM$                                         | Including CLB |

|                        |             |                                                                   | instruction   |

|                        | * ANDMB     | M8 $\leftarrow$ M8 $^{MM8}$                                       |               |

|                        | * ANDMD     | M32 ←M32∧IMM32                                                    |               |

| Logical exclusive OR   | EOR         | Acc ←Acc∀M                                                        |               |

|                        | * EORB      | Acc∟ ←Acc∟∀IMM8                                                   |               |

|                        | * EORM      | $M \leftarrow M \forall IMM$                                      |               |

|                        | * EORMB     | $M8 \leftarrow M8 \forall IMM8$                                   |               |

|                        | * EORMD     | M32 ←M32∀IMM32                                                    |               |

| Comparison             | CMP         | Acc – M                                                           |               |