## INTEGRATED CIRCUITS

Product specification Supersedes data of 1999 Apr 20

1999 Nov 04

Philips Semiconductors

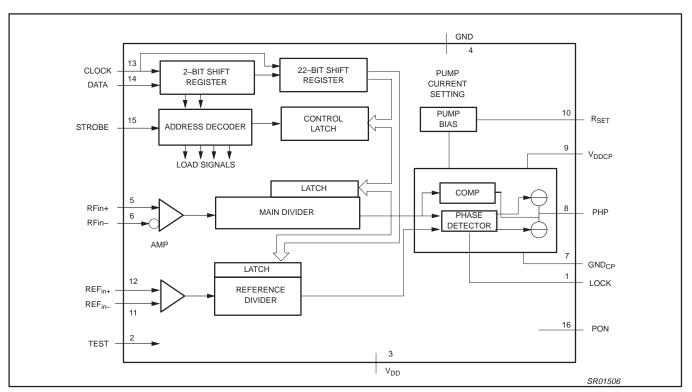

#### **GENERAL DESCRIPTION**

The SA7016 BICMOS device integrates programmable dividers, charge pumps and a phase comparator to implement a phase-locked loop. The device is designed to operate from 3 NiCd cells, in pocket phones, with low current and nominal 3 V supplies.

The synthesizer operates at VCO input frequencies up to 1.3 GHz. The synthesizer has fully programmable main and reference dividers. All divider ratios are supplied via a 3-wire serial programming bus.

Separate power and ground pins are provided to the analog and digital circuits. The ground leads should be externally short-circuited to prevent large currents flowing across the die and thus causing damage. V<sub>DDCP</sub> must be greater than or equal to V<sub>DD</sub>.

The charge pump current (gain) is set by an external resistance at the RSET pin. Only passive loop filters could be used; the charge pump operates within a wide voltage compliance range to provide a wider tuning range.

### **FEATURES**

- Low phase noise

- Low power

- Fully programmable main divider

- Internal fractional spurious compensation

- Hardware and software power down

- Split supply for V<sub>DD</sub> and V<sub>DDCP</sub>

### QUICK REFERENCE DATA

| SYMBOL                             | PARAMETER                               | CONDITIONS            | MIN. | TYP. | MAX. | UNIT |

|------------------------------------|-----------------------------------------|-----------------------|------|------|------|------|

| V <sub>DD</sub>                    | Supply voltage                          |                       | 2.7  | -    | 5.5  | V    |

| V <sub>DDCP</sub>                  | Analog supply voltage                   | $V_{DDCP} \ge V_{DD}$ | 2.7  | -    | 5.5  | V    |

| I <sub>DDCP</sub> +I <sub>DD</sub> | Total supply current                    |                       | -    | 6.2  | 7.3  | mA   |

| I <sub>DDCP</sub> +I <sub>DD</sub> | Total supply current in power-down mode |                       | -    | 1    | -    | μA   |

| f <sub>VCO</sub>                   | Input frequency                         |                       | 350  | -    | 1300 | MHz  |

| f <sub>REF</sub>                   | Crystal reference input frequency       |                       | 5    | -    | 40   | MHz  |

| f <sub>PC</sub>                    | Maximum phase comparator frequency      |                       | -    |      | 4    | MHz  |

| T <sub>amb</sub>                   | Operating ambient temperature           |                       | -40  | -    | +85  | °C   |

**APPLICATIONS**

Cellular phones

• 350-1300 MHz wireless equipment

• Portable battery-powered radio equipment.

### ORDERING INFORMATION

| TYPE NUMBER | PACKAGE |                                                                        |          |

|-------------|---------|------------------------------------------------------------------------|----------|

|             | NAME    | DESCRIPTION                                                            | VERSION  |

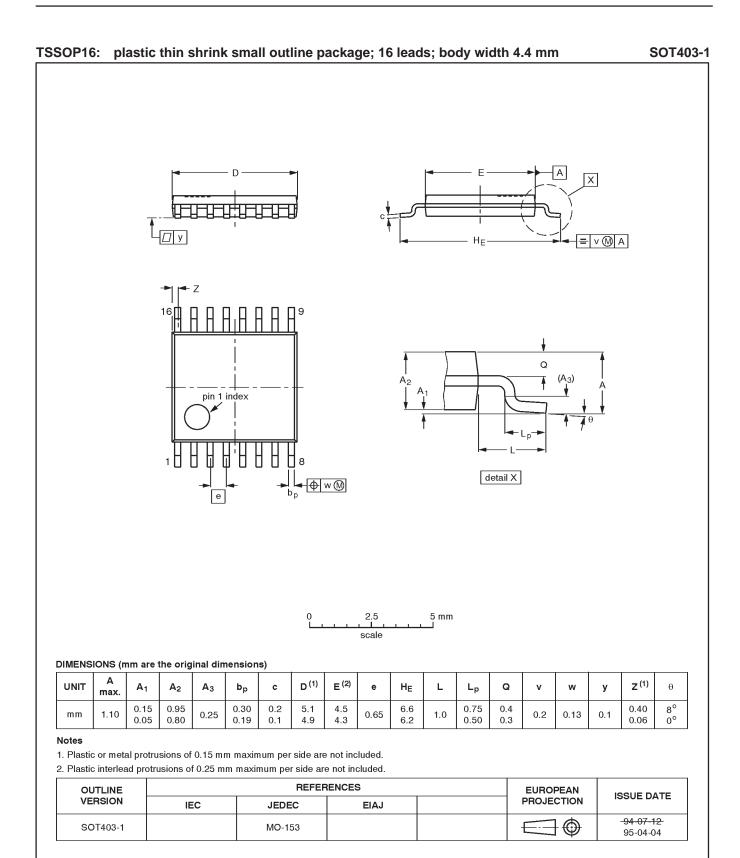

| SA7016DH    | TSSOP16 | Plastic thin shrink small outline package; 16 leads; body width 4.4 mm | SOT403-1 |

2

#### 16 PON LOCK 1 TEST 2 15 STROBE V<sub>DD</sub> 3 14 DATA 13 CLOCK GND 4 RFin+ 5 12 REFin+ 11 REFin-RFin- 6 GND<sub>CP</sub> 7 10 R<sub>SET</sub> 9 V<sub>DDCP</sub> PHP 8 SR01505

Figure 1. Pin Configuration

SA7016

## 1.3GHz low voltage fractional-N synthesizer

Figure 2. Block Diagram

### PINNING

| SYMBOL            | PIN | DESCRIPTION                                                           |

|-------------------|-----|-----------------------------------------------------------------------|

| LOCK              | 1   | Lock detect output                                                    |

| TEST              | 2   | Test (should be either grounded or connected to V <sub>DD)</sub>      |

| V <sub>DD</sub>   | 3   | Digital supply                                                        |

| GND               | 4   | Digital ground                                                        |

| RFin+             | 5   | RF input to main divider                                              |

| RFin-             | 6   | RF input to main divider                                              |

| GND <sub>CP</sub> | 7   | Charge pump ground                                                    |

| PHP               | 8   | Main normal chargepump                                                |

| V <sub>DDCP</sub> | 9   | Charge pump supply voltage                                            |

| R <sub>SET</sub>  | 10  | External resistor from this pin to ground sets the chargepump current |

| REFin-            | 11  | Reference input                                                       |

| REFin+            | 12  | Reference input                                                       |

| CLOCK             | 13  | Programming bus clock input                                           |

| DATA              | 14  | Programming bus data input                                            |

| STROBE            | 15  | Programming bus enable input                                          |

| PON               | 16  | Power down control                                                    |

## 1999 Nov 04

SA7016

### LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134).

| SYMBOL                     | PARAMETER                                                                                  | MIN. | MAX.                    | UNIT |

|----------------------------|--------------------------------------------------------------------------------------------|------|-------------------------|------|

| V <sub>DD</sub>            | Digital supply voltage                                                                     | -0.3 | +5.5                    | V    |

| V <sub>DDCP</sub>          | Analog supply voltage                                                                      | -0.3 | +5.5                    | V    |

| $\Delta V_{DDCP} - V_{DD}$ | Difference in voltage between $V_{DDCP and} V_{DD} (V_{DDCP} \ge V_{DD})$                  | -0.3 | +2.8                    | V    |

| V <sub>n</sub>             | Voltage at pins 1, 2, 5, 6, 11 to 16                                                       | -0.3 | V <sub>DD</sub> + 0.3   | V    |

| V <sub>1</sub>             | Voltage at pin 8, 9                                                                        | -0.3 | V <sub>DDCP</sub> + 0.3 | V    |

| $\Delta V_{GND}$           | Difference in voltage between $GND_CP$ and $GND$ (these pins should be connected together) | -0.3 | +0.3                    | V    |

| T <sub>stg</sub>           | Storage temperature                                                                        | -55  | +125                    | °C   |

| T <sub>amb</sub>           | Operating ambient temperature                                                              | -40  | +85                     | °C   |

| Тj                         | Maximum junction temperature                                                               |      | 150                     | °C   |

### Handling

Inputs and outputs are protected against electrostatic discharge in normal handling. However, to be totally safe, it is desirable to take normal precautions appropriate to handling MOS devices.

### THERMAL CHARACTERISTICS

| SYMBOL              | PARAMETER                                               | VALUE | UNIT |

|---------------------|---------------------------------------------------------|-------|------|

| R <sub>th j–a</sub> | Thermal resistance from junction to ambient in free air | 120   | K/W  |

### Product specification

## 1.3GHz low voltage fractional-N synthesizer

## SA7016

### **CHARACTERISTICS**

$V_{DDCP} = V_{DD} = +3.0V$ ,  $T_{amb} = +25^{\circ}C$ ; unless otherwise specified.

| SYMBOL                 | PARAMETER                                                    | CONDITIONS                                                                                                       | MIN. | TYP. | MAX.                   | UNIT             |

|------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------|------|------------------------|------------------|

| Supply; pir            | ns 3, 9                                                      | •                                                                                                                |      |      | •                      |                  |

| V <sub>DD</sub>        | Digital supply voltage                                       |                                                                                                                  | 2.7  | -    | 5.5                    | V                |

| V <sub>DDCP</sub>      | Analog supply voltage                                        | $V_{DDCP} = V_{DD}$                                                                                              | 2.7  | -    | 5.5                    | V                |

| I <sub>DDTotal</sub>   | Synthesizer operational total supply current                 | V <sub>DD</sub> = +3.0V                                                                                          | -    | 6.2  | 7.3                    | mA               |

| I <sub>Standby</sub>   | Total supply current in power-down mode                      | logic levels 0 or VDD                                                                                            | -    | 1    | TBD                    | μA               |

| RFin main              | divider input; pins 5, 6                                     | -                                                                                                                |      |      |                        | -                |

| f <sub>VCO</sub>       | VCO input frequency                                          |                                                                                                                  | 350  | -    | 1300                   | MHz              |

| V <sub>RFin(rms)</sub> | AC-coupled input signal level                                | $R_{in}$ (external) = $R_s = 50\Omega$ ;<br>single-ended drive;<br>max. limit is indicative<br>@ 500 to 1300 MHz | -18  | -    | 0                      | dBm              |

| Z <sub>IRFin</sub>     | Input impedance (real part)                                  | f <sub>VCO</sub> = 1.2 GHz                                                                                       | -    | 625  | -                      | Ω                |

| C <sub>IRFin</sub>     | Typical pin input capacitance                                | f <sub>VCO</sub> = 1.2 GHz                                                                                       | -    | 1.0  | -                      | pF               |

| N <sub>main</sub>      | Main divider ratio                                           |                                                                                                                  | 512  | -    | 65535                  |                  |

| f <sub>PCmax</sub>     | Maximum loop comparison frequency                            | indicative, not tested                                                                                           | -    | -    | 4                      | MHz              |

| Reference              | divider input; pins 11, 12                                   |                                                                                                                  |      |      |                        |                  |

| f <sub>REFin</sub>     | Input frequency range from TCXO                              |                                                                                                                  | 5    | -    | 40                     | MHz              |

| VRFin                  | AC-coupled input signal level                                | single-ended drive;<br>max. limit is indicative                                                                  | 360  | -    | 1300                   | mV <sub>PP</sub> |

| Z <sub>REFin</sub>     | Input impedance (real part)                                  | f <sub>REF</sub> = 20 MHz                                                                                        | -    | 10   | -                      | kΩ               |

| C <sub>REFin</sub>     | Typical pin input capacitance                                | f <sub>REF</sub> = 20 MHz                                                                                        | -    | 1.0  | -                      | pF               |

| R <sub>REF</sub>       | Reference division ratio                                     |                                                                                                                  | 4    | -    | 1023                   |                  |

| Charge pu              | mp current setting resistor input; pin 10                    |                                                                                                                  |      |      |                        |                  |

| R <sub>SET</sub>       | External resistor from pin to ground                         |                                                                                                                  | 6    | 7.5  | 15                     | kΩ               |

| V <sub>SET</sub>       | Regulated voltage at pin                                     | R <sub>SET</sub> =7.5 kΩ                                                                                         | -    | 1.25 | -                      | V                |

| Charge pu              | mp outputs (including fractional compensation                | n pump); pin 8; R <sub>SET</sub> =7.5kΩ, FC                                                                      | 2=80 |      |                        |                  |

| I <sub>CP</sub>        | Charge pump current ratio to I <sub>SET</sub> <sup>1</sup>   | Current gain I <sub>PH</sub> /I <sub>SET</sub>                                                                   | -15  |      | +15                    | %                |

| IMATCH                 | Sink-to-source current matching                              | V <sub>PH</sub> =1/2 V <sub>DDCP</sub> .                                                                         | -10  |      | +10                    | %                |

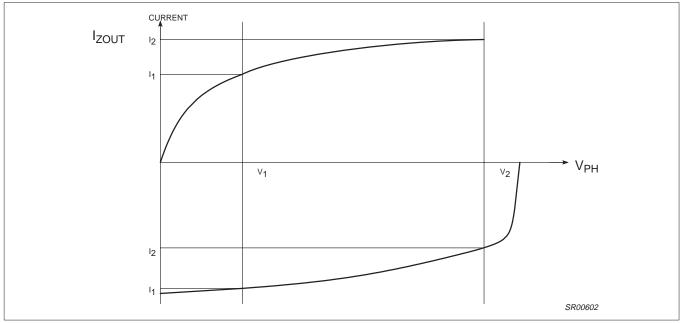

| I <sub>ZOUT</sub>      | Output current variation versus V <sub>PH</sub> <sup>2</sup> | V <sub>PH</sub> in compliance range                                                                              | -10  |      | +10                    | %                |

| I <sub>LPH</sub>       | Charge pump off leakage current                              | V <sub>PH</sub> =1/2 V <sub>CC</sub>                                                                             | -10  |      | +10                    | nA               |

| V <sub>PH</sub>        | Charge pump voltage compliance                               |                                                                                                                  | 0.7  | -    | V <sub>DDCP</sub> -0.8 | V                |

#### Philips Semiconductors

## 1.3GHz low voltage fractional-N synthesizer

## SA7016

| SYMBOL            | PARAMETER                                                                                | CONDITIONS                                                                                         | MIN.                 | TYP. | MAX.                 | UNIT   |

|-------------------|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|----------------------|------|----------------------|--------|

| Phase noi         | se (R <sub>SET</sub> = 7.5 kΩ, CP=00)                                                    |                                                                                                    | •                    |      | •                    |        |

|                   | Synthesizer's contribution to close-in phase noise of 900 MHz RF signal at 1 kHz offset. | GSM<br>f <sub>REF</sub> = 13MHz, TCXO,                                                             | -                    | -90  | -                    | dBc/Hz |

| 0                 |                                                                                          | f <sub>COMP</sub> = 1MHz<br>indicative, not tested                                                 |                      |      |                      |        |

| L <sub>(f)</sub>  | Synthesizer's contribution to close-in phase noise of 800 MHz RF signal at 1 kHz offset. | TDMA<br>f <sub>REF</sub> = 19.44MHz, TCXO,<br>f <sub>COMP</sub> = 240kHz<br>indicative, not tested | -                    | -85  | _                    | dBc/Hz |

| Interface l       | ogic input signal levels; pins 13, 14, 15, 16                                            |                                                                                                    |                      |      |                      |        |

| V <sub>IH</sub>   | HIGH level input voltage                                                                 |                                                                                                    | 0.7*V <sub>DD</sub>  | -    | V <sub>DD</sub> +0.3 | V      |

| V <sub>IL</sub>   | LOW level input voltage                                                                  |                                                                                                    | -0.3                 | -    | 0.3*V <sub>DD</sub>  | V      |

| I <sub>LEAK</sub> | Input leakage current                                                                    | logic 1 or logic 0                                                                                 | -0.5                 | -    | +0.5                 | μΑ     |

| Lock dete         | ct output signal (in push/pull mode); pin 1                                              |                                                                                                    |                      |      |                      |        |

| V <sub>OL</sub>   | LOW level output voltage                                                                 | I <sub>sink</sub> =2mA                                                                             | -                    | -    | 0.4                  | V      |

| V <sub>OH</sub>   | HIGH level output voltage                                                                | I <sub>source</sub> =-2mA                                                                          | V <sub>DD</sub> -0.4 | -    | -                    | V      |

NOTES:

1.  $I_{SET} = \frac{V_{SET}}{R_{SET}}$  bias current for charge pumps.

2. The relative output current variation is defined as:

$$\frac{\Delta I_{OUT}}{I_{OUT}} = 2 \cdot \frac{(I_2 - I_1)}{I(I_2 + I_1)I}; \text{ with } V_1 = 0.7V, V_2 = V_{DDCP} - 0.8V \text{ (See Figure 3.)}$$

Figure 3. Relative Output Current Variation

### FUNCTIONAL DESCRIPTION

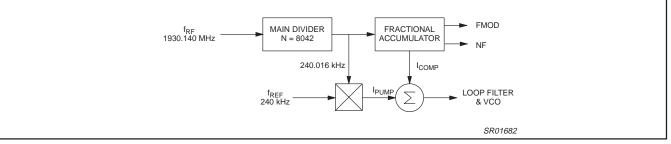

#### Main Fractional-N divider

The RFin inputs drive a pre-amplifier to provide the clock to the first divider stage. For single ended operation, the signal should be fed to one of the inputs while the other one is AC grounded. The pre-amplifier has a high input impedance, dominated by pin and pad capacitance. The circuit operates with signal levels from –18 dBm to 0 dBm, and at frequencies as high as 1.3 GHz. The divider consists of a fully programmable bipolar prescaler followed by a CMOS counter. Total divide ratios range from 512 to 65536.

At the completion of a main divider cycle, a main divider output pulse is generated which will drive the main phase comparator. Also, the fractional accumulator is incremented by the value of NF. The accumulator works with modulo Q set by FMOD. When the accumulator overflows, the overall division ratio N will be increased by 1 to N + 1, the average division ratio over Q main divider cycles (either 5 or 8) will be

Nfrac = N +

$$\frac{NF}{Q}$$

The output of the main divider will be modulated with a fractional phase ripple. The phase ripple is proportional to the contents of the

fractional accumulator and is nulled by the fractional compensation charge pump.

The reloading of a new main divider ratio is synchronized to the state of the main divider to avoid introducing a phase disturbance.

#### **Reference divider**

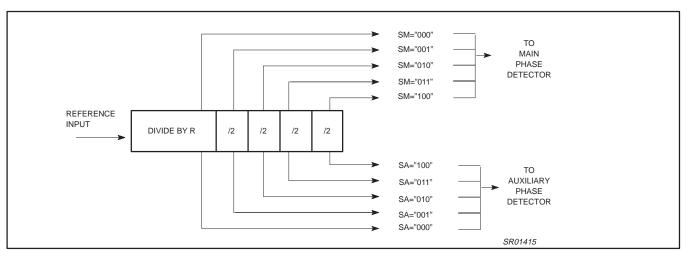

The reference divider consists of a divider with programmable values between 4 and 1023 followed by a three bit binary counter. The 3 bit SM (SA) register (see Figure 4) determines which of the 5 output pulses are selected as the main (auxiliary) phase detector input.

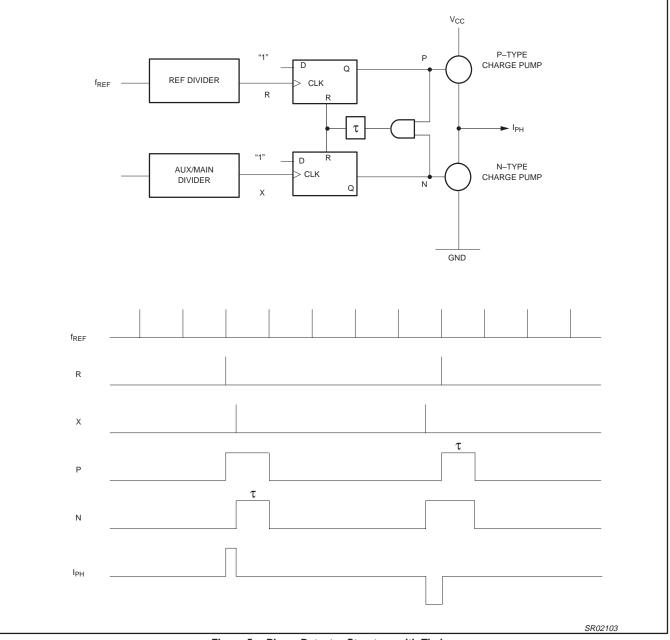

#### Phase detector (see Figure 5)

The reference and main (aux) divider outputs are connected to a phase/frequency detector that controls the charge pump. The pump current is set by an external resistor in conjunction with control bits CP0 and CP1 in the C-word (see Charge Pump table). The dead zone (caused by finite time taken to switch the current sources on or off) is cancelled by forcing the pumps ON for a minimum time at every cycle (backlash time) providing improved linearity.

Figure 4. Reference Divider

SA7016

## 1.3GHz low voltage fractional-N synthesizer

Figure 5. Phase Detector Structure with Timing

#### Product specification

SA7016

## 1.3GHz low voltage fractional-N synthesizer

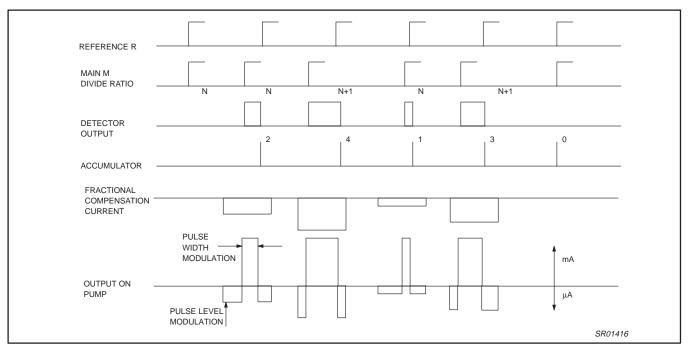

### Main Output Charge Pumps and Fractional Compensation Currents (see Figure 6)

The main charge pumps on pins PHP and PHI are driven by the main phase detector and the charge pump current values are determined by the current at pin  $R_{SET}$  in conjunction with bits CP0, CP1 in the B-word (see table of charge pump ratios). The fractional compensation is derived from the current at  $R_{SET}$ , the contents of the fractional accumulator FRD and by the program value of the FDAC. The timing for the fractional compensation is derived from the main divider. The main charge pumps will enter speed up mode after the A-word is set and strobe goes High. When strobe goes Low, charge pump will exit speed up mode.

#### **Principle of Fractional Compensation**

The fractional compensation is designed into the circuit as a means of reducing or eliminating fractional spurs that are caused by the fractional phase ripple of the main divider. If  $I_{COMP}$  is the compensation current and  $I_{PUMP}$  is the pump current, then for each charge pump:

fractional compensation, the area of the fractional compensation current pulse must be equal to the area of the fractional charge pump ripple. The width of the fractional compensation pulse is fixed to 128 VCO cycles, the amplitude is proportional to the fractional accumulator value and is adjusted by FDAC values (bits FC7–0 in the B-word). The fractional compensation current is derived from the main charge pump in that it follows all the current scaling through external resistor setting,  $R_{SET}$ , programming or speed-up operation. For a given charge pump,

The compensation is done by sourcing a small current,  $I_{COMP}$ , see

Figure 7, that is proportional to the fractional error phase. For proper

I<sub>COMP</sub> = ( I<sub>PUMP</sub> / 128 ) \* ( FDAC / 5\*128) \* FRD

FRD is the fractional accumulator value.

The target values for FDAC are: 128 for FMOD = 1 (modulo 5) and 80 for FMOD = 0 (modulo 8).

Figure 7. Current Injection Concept

9

## IPUMP TOTAL = IPUMP + ICOMP.

## SA7016

#### Charge pump currents

| CP0 | I <sub>PHP</sub>   | I <sub>PHP-SU</sub> |

|-----|--------------------|---------------------|

| 0   | 3xI <sub>SET</sub> | 15xl <sub>SET</sub> |

| 1   | 1xl <sub>SET</sub> | 5xl <sub>SET</sub>  |

#### NOTES:

1.  $I_{SET}=V_{SET}/R_{SET}$  bias current for charge pumps.

I<sub>PHP-SU</sub> is the total current at pin PHP during speed up condition.

#### Lock Detect

The output LOCK maintains a logic '1' when the auxiliary phase detector ANDed with the main phase detector indicates a lock condition. The lock condition for the main and auxiliary synthesizers is defined as a phase difference of less than  $\pm 1$  period of the frequency at the input REFin+, –. One counter can fulfill the lock condition when the other counter is powered down. Out of lock (logic '0') is indicated when both counters are powered down.

#### Power-down mode

The power-down signal can be either hardware (PON) or software (PD). The PON signal is exclusively ORed with the PD bits in B-word. If PON = 0, then the part is powered up when PD = 1. PON can be used to invert the polarity of the software bit PD. When the synthesizer is reactivated after power-down, the main and reference dividers are synchronized to avoid possibility of random phase errors on power-up.

## SA7016

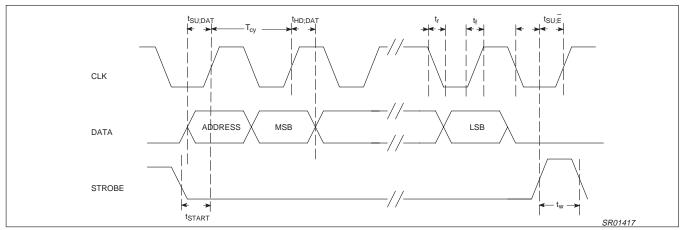

#### Serial programming bus

The serial input is a 3-wire input (CLOCK, STROBE, DATA) to program all counter divide ratios, fractional compensation DAC, selection and enable bits. The programming data is structured into 24 bit words; each word includes 2 or 3 address bits. Figure 8 shows the timing diagram of the serial input. When the STROBE goes active HIGH, the clock is disabled and the data in the shift register remains unchanged. Depending on the address bits, the data is latched into different working registers or temporary registers. In order to fully program the synthesizer, 3 words must be sent: C, B, and A. Table 1 shows the format and the contents of each word. The D word is normally used for testing purposes. When sending the B-word, data bits FC7–0 for the fractional compensation DAC are not loaded immediately. Instead they are stored in temporary registers. Only when the A-word is loaded, these temporary registers are loaded together with the main divider ratio.

## Serial bus timing characteristics. See Figure 8.

$V_{DD} = V_{DDCP} = +3.0V$ ;  $T_{amb} = +25^{\circ}C$  unless otherwise specified.

| SYMBOL              | PARAMETER                             | MIN.                | TYP. | MAX. | UNIT |

|---------------------|---------------------------------------|---------------------|------|------|------|

| Serial programm     | ing clock; CLK                        |                     |      |      |      |

| t <sub>r</sub>      | Input rise time                       | -                   | 10   | 40   | ns   |

| t <sub>f</sub>      | Input fall time                       | -                   | 10   | 40   | ns   |

| T <sub>cy</sub>     | Clock period                          | 100                 | -    | -    | ns   |

| Enable programm     | ning; STROBE                          |                     |      |      |      |

| t <sub>START</sub>  | Delay to rising clock edge            | 40                  | -    | -    | ns   |

| t <sub>W</sub>      | Minimum inactive pulse width          | 1/f <sub>COMP</sub> | -    | -    | ns   |

| t <sub>SU;E</sub>   | Enable set-up time to next clock edge | 20                  | -    | -    | ns   |

| Register serial in  | put data; DATA                        |                     |      |      |      |

| t <sub>SU;DAT</sub> | Input data to clock set-up time       | 20                  | -    | -    | ns   |

| t <sub>HD;DAT</sub> | Input data to clock hold time         | 20                  | -    | -    | ns   |

#### Application information

Figure 8. Serial Bus Timing Diagram

SA7016

### Data format

## Table 1. Format of programmed data

| LAST IN |     | MSB |     | SERIAL PROGRA | MMING FORMAT |    | FIRST IN LSB |

|---------|-----|-----|-----|---------------|--------------|----|--------------|

| p23     | p22 | p21 | p20 | /             | /            | р1 | p0           |

## Table 2. A word, length 24 bits

| LAST   | IN                        |         |       |     |       | MSB                                                                |                                                       |       |       |       |        |       |    |   |   |    |     |     |   |   | FIR | ST IN |   |

|--------|---------------------------|---------|-------|-----|-------|--------------------------------------------------------------------|-------------------------------------------------------|-------|-------|-------|--------|-------|----|---|---|----|-----|-----|---|---|-----|-------|---|

| Addre  | Address fmod Fractional-N |         |       |     | -N    | Main Divider ratio                                                 |                                                       |       |       |       |        |       |    |   |   |    |     |     |   |   | Sp  | oare  |   |

| 0      | 0                         | FM      | NF2   | NF1 | NF0   | N15                                                                | N15 N14 N13 N12 N11 N10 N9 N8 N7 N6 N5 N4 N3 N2 N1 N0 |       |       |       |        |       |    |   |   | N0 | SP1 | SP2 |   |   |     |       |   |

| Defa   | Default: 0 0 1 0          |         |       |     |       |                                                                    | 0                                                     | 1     | 0     | 0     | 0      | 1     | 0  | 0 | 0 | 1  | 1   | 0   | 0 | 0 | 0   | 0     | 0 |

| A wor  | d sele                    | ct      |       |     | Fixed | Fixed to 00.                                                       |                                                       |       |       |       |        |       |    |   |   |    |     |     |   |   |     |       |   |

| Fracti | onal N                    | lodulus | selec | t   | FM 0  | FM 0 = modulo 8, 1 = modulo 5.                                     |                                                       |       |       |       |        |       |    |   |   |    |     |     |   |   |     |       |   |

| Fracti | onal-N                    | Increm  | nent  |     | NF2   | 0 Fractio                                                          | onal N                                                | Incre | ement | value | es 000 | to 11 | 1. |   |   |    |     |     |   |   |     |       |   |

| N-Div  | ider                      |         |       |     | N0N   | N0N15, Main divider values 512 to 65535 allowed for divider ratio. |                                                       |       |       |       |        |       |    |   |   |    |     |     |   |   |     |       |   |

## Table 3. B word, length 24 bits

| Add           | ress   |        |        | F                                                                           | REFE | RENC                                                                                           | E DI                                                                                                                                                                                                      | /IDER  | 2     |            |         | LOCK                           | PD       | СР    | FF     | RACT | IONA | L COI | MPEN | SATIO | ON DA | AC | SPARE |

|---------------|--------|--------|--------|-----------------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|------------|---------|--------------------------------|----------|-------|--------|------|------|-------|------|-------|-------|----|-------|

| 0             | 1      | R9     | R8     | R7                                                                          | R6   | R5                                                                                             | R5         R4         R3         R2         R1         R0         LO         MAIN         CP0         FC7         FC6         FC5         FC4         FC3         FC2         FC1         FC0         SP2 |        |       |            |         |                                |          |       |        |      |      | SP3   |      |       |       |    |       |

| Defa          | ault:  | 0      | 0      | 0                                                                           | 1    | 0                                                                                              | 1                                                                                                                                                                                                         | 0      | 0     | 0          | 1       | 0                              | 0        | 0     | 0      | 1    | 0    | 1     | 0    | 0     | 0     | 0  | 0     |

| B wo          | rd sel | ect    | -      |                                                                             | Fixe | d to 0                                                                                         | 1                                                                                                                                                                                                         |        |       |            |         |                                |          |       |        |      |      |       |      | -     |       | -  |       |

| R-Di          | vider  |        |        |                                                                             | R0I  | R9, Reference divider values 4 to 1023 allowed for divider ration.                             |                                                                                                                                                                                                           |        |       |            |         |                                |          |       |        |      |      |       |      |       |       |    |       |

| Char<br>Ratio | ge pu  | mp cı  | urrent |                                                                             | CP0  | P0: Charge pump current ratio, see table of charge pump currents.                              |                                                                                                                                                                                                           |        |       |            |         |                                |          |       |        |      |      |       |      |       |       |    |       |

| Lock          | detec  | t outp | out    |                                                                             | 1 N  | /lain lo                                                                                       | ock de                                                                                                                                                                                                    | tect s | ignal | ,<br>prese | nt at t | he LOC<br>he LOC<br>le, the lo | K pin (c | pen d | rain). |      |      |       |      |       |       |    |       |

| Powe          | er dow | /n     |        |                                                                             | Main | Main = 1: power to main divider, reference divider, main charge pumps, Main = 0 to power down. |                                                                                                                                                                                                           |        |       |            |         |                                |          |       |        |      |      |       |      |       |       |    |       |

| Frac          | tional | Comp   | ensat  | tion FC70 Fractional Compensation charge pump current DAC, values 0 to 255. |      |                                                                                                |                                                                                                                                                                                                           |        |       |            |         |                                |          |       |        |      |      |       |      |       |       |    |       |

## Table 4. D word, length 24 bits

| Address |       |      |   | SYNTHESIZER TEST<br>BITS |   |   |   |                                                                                               |      | SYNTHESIZER TEST BITS |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|---------|-------|------|---|--------------------------|---|---|---|-----------------------------------------------------------------------------------------------|------|-----------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1       | 1     | Т    | 0 | -                        | - | - | - | -                                                                                             | Tspu | -                     | - | - | - | - | - | - | - | - | - | - | - | - | - | - |

|         | Defau | ult: |   | 0                        | 0 | 0 | 0 | 0                                                                                             | 0    | 0                     | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Tsp     |       |      |   |                          |   |   |   | in charge pumps in speed-up mode all the time.<br>bits must be set to 0 for normal operation. |      |                       |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

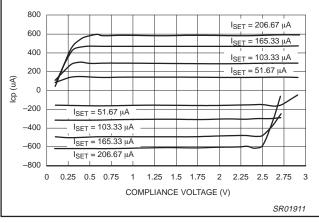

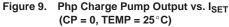

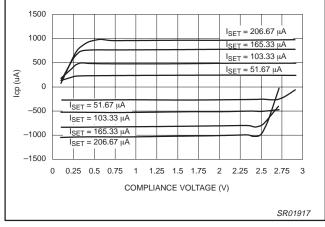

Figure 11. Php Charge Pump Output vs.  $I_{SET}$ (CP = 1; TEMP = 25°C)

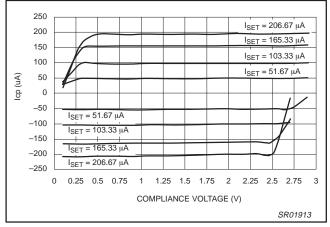

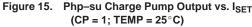

Figure 13. Php-su Charge Pump Output vs. I<sub>SET</sub> (CP = 0; TEMP = 25°C)

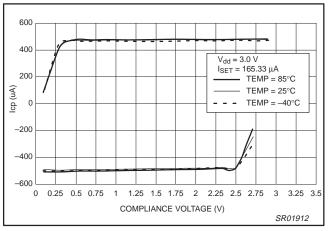

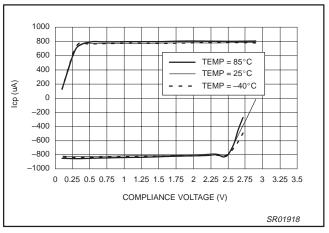

Figure 10. Php Charge Pump Output vs. Temperature (CP = 0; V<sub>DD</sub> = 3.0 V; I<sub>SET</sub> = 165.33  $\mu$ A)

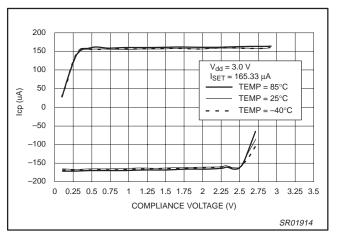

Figure 12. Php Charge Pump Output vs. Temperature (CP = 1;  $V_{DD}$  = 3.0 V;  $I_{SET}$  = 165.33  $\mu$ A)

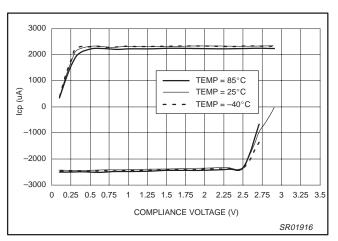

Figure 14. Php–su Charge Pump Output vs. Temperature (CP = 0;  $V_{DD}$  = 3.0 V;  $I_{SET}$  = 165.33  $\mu$ A)

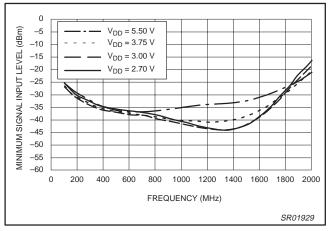

Figure 17. Main Divider Input Sensitivity vs. Frequency and Supply Voltage (TEMP =  $25^{\circ}$ C)

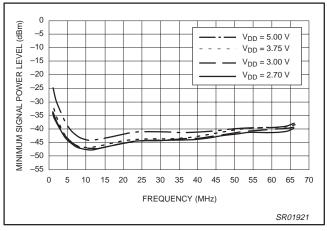

Figure 19. Reference Divider Input Sensitivity vs. Frequency and Supply Voltage (TEMP = 25°C)

Figure 16. Php–su Charge Pump Output vs. Temperature (CP = 1;  $V_{DD}$  = 3.0 V;  $I_{SET}$  = 165.33  $\mu$ A)

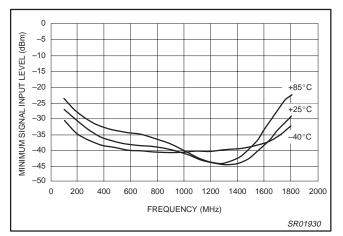

Figure 18. Main Divider Input Sensitivity vs. Frequency and Temperature ( $V_{DD} = 3.00 \text{ V}$ )

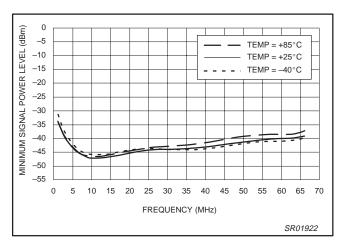

Figure 20. Reference Divider Input Sensitivity vs. Frequency and Temperature (V<sub>DD</sub> = 3.00 V)

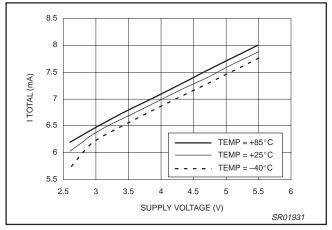

Figure 21. Current Supply Over  $V_{DD}$

## synthesizer

Product specification

# 1.3GHz low voltage fractional-N frequency synthesizer

### Data sheet status

| Data sheet<br>status      | Product<br>status | Definition [1]                                                                                                                                                                                                                                                  |

|---------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective specification   | Development       | This data sheet contains the design target or goal specifications for product development.<br>Specification may change in any manner without notice.                                                                                                            |

| Preliminary specification | Qualification     | This data sheet contains preliminary data, and supplementary data will be published at a later date.<br>Philips Semiconductors reserves the right to make chages at any time without notice in order to<br>improve design and supply the best possible product. |

| Product specification     | Production        | This data sheet contains final specifications. Philips Semiconductors reserves the right to make changes at any time without notice in order to improve design and supply the best possible product.                                                            |

[1] Please consult the most recently issued datasheet before initiating or completing a design.

### Definitions

**Short-form specification** — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

**Application information** — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### Disclaimers

Life support — These products are not designed for use in life support appliances, devices or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

**Right to make changes** — Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

Philips Semiconductors 811 East Arques Avenue P.O. Box 3409 Sunnyvale, California 94088–3409 Telephone 800-234-7381 © Copyright Philips Electronics North America Corporation 1999 All rights reserved. Printed in U.S.A.

Date of release: 11-99

Document order number:

9397 750 06565

Let's make things better.

SUNSTAR 商斯达实业集团是集研发、生产、工程、销售、代理经销、技术咨询、信息服务等为一体的高科技企业,是专业高科技电子产品生产厂家,是具有10多年历史的专业电子元器件供应商,是中国最早和最大的仓储式连锁规模经营大型综合电子零部件代理分销商之一,是一家专业代理和分銷世界各大品牌IC芯片和電子元器件的连锁经营综合性国际公司,专业经营进口、国产名厂名牌电子元件,型号、种类齐全。在香港、北京、深圳、上海、西安、成都等全国主要电子市场设有直属分公司和产品展示展销窗口门市部专卖店及代理分销商,已在全国范围内建成强大统一的供货和代理分销网络。我们专业代理经销、开发生产电子元器件、集成电路、传感器、微波光电元器件、工控机/DOC/DOM电子盘、专用电路、单片机开发、MCU/DSP/ARM/FPGA软件硬件、二极管、三极管、模块等,是您可靠的一站式现货配套供应商、方案提供商、部件功能模块开发配套商。商斯达实业公司拥有庞大的资料库,有数位毕业于著名高校——有中国电子工业摇篮之称的西安电子科技大学(西军电)并长期从事国防尖端科技研究的高级工程师为您精挑细选、量身订做各种高科技电子元器件,并解决各种技术问题。

微波光电部专业代理经销高频、微波、光纤、光电元器件、组件、部件、模块、整机;电磁兼容元器件、材料、设备;微波 CAD、EDA 软件、开发测试仿真工具;微波、光纤仪器仪表。 欢迎国外高科技微波、光纤厂商将优秀产品介绍到中国、共同开拓市场。长期大量现货专业批发 高频、微波、卫星、光纤、电视、CATV 器件: 晶振、VCO、连接器、PIN 开关、变容二极管、开 关二极管、低噪晶体管、功率电阻及电容、放大器、功率管、MIIC、混频器、耦合器、功分器、 振荡器、合成器、衰减器、滤波器、隔离器、环行器、移相器、调制解调器;光电子元器件和组 件:红外发射管、红外接收管、光电开关、光敏管、发光二极管和发光二极管组件、半导体激光 二极管和激光器组件、光电探测器和光接收组件、光发射接收模块、光纤激光器和光放大器、光 调制器、光开关、DWDM 用光发射和接收器件、用户接入系统光光收发器件与模块、光纤连接器、 光纤跳线/尾纤、光衰减器、光纤适 配器、光隔离器、光耦合器、光环行器、光复用器/转换器; 无线收发芯片和模组、蓝牙芯片和模组。

更多产品请看本公司产品专用销售网站:

商斯达中国传感器科技信息网: http://www.sensor-ic.com/

商斯达工控安防网: http://www.pc-ps.net/

商斯达电子元器件网: http://www.sunstare.com/

商斯达微波光电产品网:HTTP://www.rfoe.net/

商斯达消费电子产品网://www.icasic.com/

商斯达实业科技产品网://www.sunstars.cn/ 微波元器件销售热线:

地址: 深圳市福田区福华路福庆街鸿图大厦 1602 室

电话: 0755-82884100 83397033 83396822 83398585

传真: 0755-83376182 (0) 13823648918 MSN: SUNS8888@hotmail.com

邮编: 518033 E-mail:szss20@163.com QQ: 195847376

深圳赛格展销部: 深圳华强北路赛格电子市场 2583 号 电话: 0755-83665529 25059422 技术支持: 0755-83394033 13501568376

欢迎索取免费详细资料、设计指南和光盘;产品凡多,未能尽录,欢迎来电查询。

北京分公司:北京海淀区知春路 132 号中发电子大厦 3097 号

TEL: 010-81159046 82615020 13501189838 FAX: 010-62543996 上海分公司: 上海市北京东路 668 号上海賽格电子市场 D125 号

TEL: 021-28311762 56703037 13701955389 FAX: 021-56703037

西安分公司: 西安高新开发区 20 所(中国电子科技集团导航技术研究所) 西安劳动南路 88 号电子商城二楼 D23 号

TEL: 029-81022619 13072977981 FAX:029-88789382