#### TRANSMITTING TRANSISTOR DESIGN 1

#### 1.1 Die technology and design

A transmitting transistor has to deliver high power at high frequency (>1 MHz). This means that a large transistor die with a fine structure is required. Bipolar and MOS

### Transmitting transistor design

transistors are suitable, see panel, and Philips Semiconductors' portfolio includes both types. Their relative merits are summarized later in this section. First, however, let's look at the basic aspects of design that contribute to the reliability and high-performance of a modern RF transmitting transistor.

### TRANSISTOR FABRICATION

As is well-known, most transistors are fabricated from silicon wafers (5" dia. or larger, and about 0.25 mm thick) in a multi-stage batch process that involves precise, localized doping of an epitaxial layer grown on the silicon substrate to form the different transistor regions. The main process steps for fabricating bipolar transistors are shown here as a reminder. MOS transistors are fabricated using similar techniques. Though semiconductor manufacturers have many processes available to meet different commercial and technical specifications, they all are based on the principles outlined below.

#### Silicon wafer 1.

- Oxidize to form oxide layer 2.

- Apply photosensitive layer 3.

- 4. Expose through high-resolution mask

- Develop photosensitive layer 5.

- Etch base window through oxide layer 6.

- Remove remaining photosensitive layer 7. Diffuse or ion-implant the base

- 8. Oxidize base window 9.

- 10. Expose emitter window

- 11.

- Etch emitter window through oxide layer 12. Remove remaining photosensitive layer

- 13. Diffuse or ion-implant the emitter

- 14.

- Create metallization window Metallize base and emitter regions 15.

- Polish and metallize bottom (collector). 16.

### Transmitting transistor design

### 1.1.1 Bipolar transistor dies

#### 1.1.1.1 THE COLLECTOR (SUBSTRATE MATERIAL)

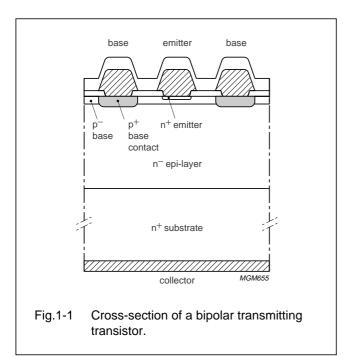

All of Philips' present bipolar types are NPN silicon planar epitaxial transistors, see Figs 1-1 and 1-2. The basic epitaxial material consists of a highly doped n-substrate (100 to 200  $\mu$ m thick) with a rather high ohmic n-layer (epi-layer) deposited on top. The resistivity of this layer determines the collector-base breakdown voltage of the device (V<sub>(BR)CBO</sub>). Most Philips transistors intended for operation at a supply voltage of 28 V have a *guaranteed* breakdown voltage of 65 V (and a typical value of about 80 V). The required resistivity of the epi-layer for this breakdown voltage is 1.6 to 2.0  $\Omega$ cm, the exact value having a very small tolerance.

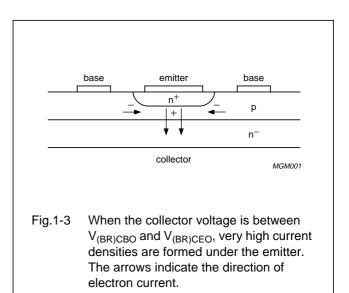

A second important design parameter is the epi-layer thickness, which must be thicker than the collector depletion layer thickness at breakdown to prevent reverse second breakdown when the base current is negative. This occurs when the collector voltage is higher than the collector-emitter breakdown voltage with open base,  $V_{(BR)CEO}$ . Normally, this voltage is about half the collector-base breakdown voltage mentioned earlier. When the collector voltage is between these two collector breakdown voltages ( $V_{(BR)CEO}$  and  $V_{(BR)CEO}$ ), the situation is as shown in Fig.1-3.

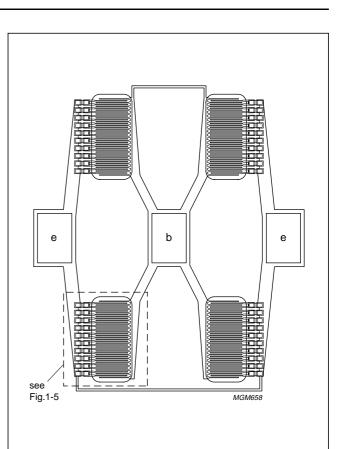

Fig.1-2 Layout of a typical bipolar transmitting transistor die.

As Fig.1-3 shows, the collector current is concentrated in the middle of the emitter which can lead to very high current densities. The base is negative along the edge of the emitter and positive beneath it. If this situation continues for a long time, it will eventually destroy the transistor. This effect can be reduced by making the epi-layer somewhat thicker than strictly necessary, the chosen thickness being a compromise between the transistor's RF performance and its ability to withstand certain forms of output mismatching.

### 1.1.1.2 THE EMITTER AND BASE

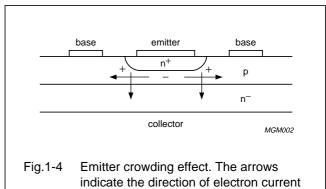

The emitter of an RF power transistor must be dimensioned such that the transistor can deliver the required output power with all performance-degrading effects such as capacitances minimized. To achieve this, both the emitter area and periphery are important parameters, because of 'emitter-crowding', see Fig.1-4.

The base (electron) current makes the base positive along the edge of the emitter but negative in the middle. This means that collector current only flows at the edge of the emitter, so the potential output power is mainly determined by the emitter periphery. Under normal operating conditions, only 1 to 2  $\mu$ m of the edge of the emitter is active; the rest of the emitter merely introduces parasitic capacitance. A practical choice for emitter width is 2 to 4  $\mu$ m.

For a 2 to 4  $\mu$ m wide emitter, a good design rule of thumb is that every watt of output power requires about 2 mm of emitter periphery. A narrower emitter can improve some characteristics, but requires more emitter periphery per watt.

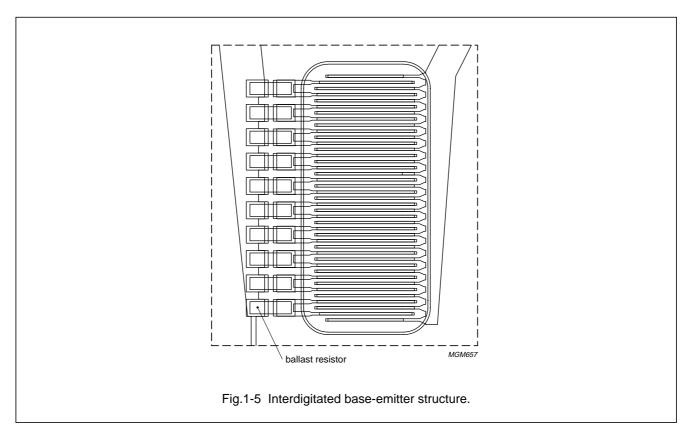

Of course, it is not very practical to make one extremely long, narrow emitter, so transistor designers use an interdigitated structure as shown in Fig.1-5. In this structure, the emitter is split into several parallel parts ('fingers') with the base contacts in between. The finger pitch is mainly determined by the maximum frequency of operation - the higher the frequency, the smaller the pitch.

The emitter fingers are normally connected at one end by metallization. As a result, there is a voltage drop along

### Transmitting transistor design

each finger. This must not exceed 25 to 30 mV at maximum collector current otherwise part of the finger will be cut off near the other end.

Splitting the emitter into many sections is thus required for practical reasons and for good operation. This is also true to some extent for the base, but for different reasons. In fact, if the required output power is low, say 2 to 3 W, a single base area is acceptable. At higher powers, it is necessary to split the base area into several parts as this:

- Reduces the thermal resistance of the die

- Increases the base periphery, improving the distribution of dissipation at breakdown since collector breakdown occurs first along the edges of the base areas

- Allows more base and emitter bonding pads to be included, which reduces the emitter lead inductance, increasing the power gain. In addition, splitting the base area reduces the current through each bonding wire.

The preferred distance between successive base areas is approximately twice the die thickness, say about 300  $\mu$ m, to obtain a low thermal resistance. A disadvantage of splitting the base is higher parasitic capacitances.

Fig.1-4 Emitter crowding effect. The arrows indicate the direction of electron current in normal operation. Note, to prevent confusion, the base current has also been drawn as an electron current.

### Transmitting transistor design

### 1.1.1.3 EMITTER BALLAST RESISTORS

For electrical ruggedness, a built-in emitter ballast resistor is virtually a necessity. This is certainly the case when class-A or class-AB operation can be expected. In class-A for instance, without such an emitter resistor, the collector current can become restricted to a small area in the middle of the die where the temperature is highest. This causes a large increase in the thermal resistance which can destroy the transistor at a much-reduced DC power.

To prevent this effect, each emitter finger or group of two fingers, is provided with an emitter resistor. Good current distribution is obtained if the total emitter resistance is such that the voltage drop across it is approximately 200 to 300 mV at the normal DC collector current.

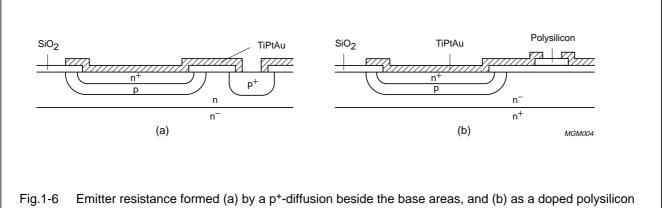

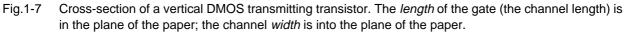

Emitter resistors can be made as a p<sup>+</sup>-diffusion beside the base areas (Fig.1-6a) or as a doped polysilicon layer on top of the oxide (Fig.1-6b), the latter producing less parasitic capacitance.

The temperature coefficient (t.c.) of a diffused emitter resistance is positive, and at practical operating temperatures (~125 °C), the resistance increases by approximately 0.1%/K. The t.c. of a polysilicon resistor is much smaller.

#### 1.1.1.4 DIFFUSION AND IMPLANTATION PROCESSES

The first transmitting transistors were made using diffusion processes. Nowadays, ion implantation followed by temperature treatment is the preferred manufacturing process as it provides superior reproducibility and sharper (i.e. better defined) doping transitions. The specific implantation process used depends primarily on the maximum frequency of operation required. For the highest frequency transistors, extremely shallow implantations are used, giving a thin base and a high  $f_T$ . The resulting  $h_{FE}$ , usually about 50, is ample for RF operation.

### Transmitting transistor design

### 1.1.2 Vertical DMOS transistor dies

#### 1.1.2.1 THE DRAIN (SUBSTRATE MATERIAL)

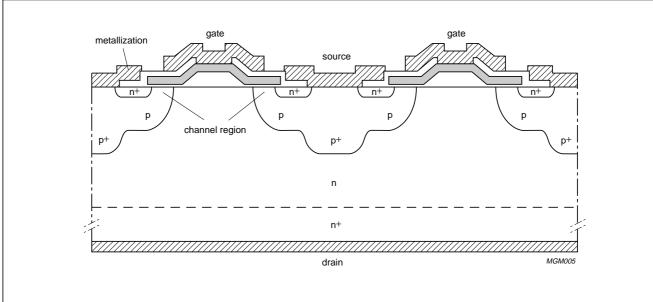

Philips' RF power MOS transistors are all silicon n-channel enhancement types, (see Fig.1-7). The considerations for and dimensioning of the epitaxial material are principally the same as those for bipolar transistors (Section 1.1.1.1).

layer on top of the oxide.

### 1.1.2.2 THE SOURCE AND GATE

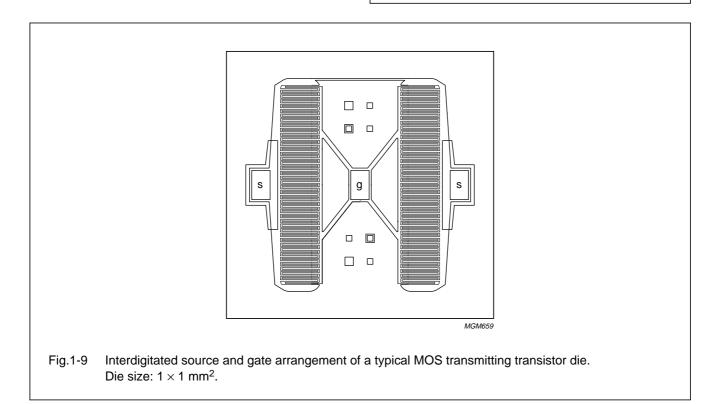

The configuration of source and gate in most MOS transmitting transistors is similar to the interdigitated emitter and base of a bipolar transistor, see Fig.1-9.

The RF output power that such a device can deliver depends of course on the maximum drain current ( $I_{DSX}$ ) which, in turn, is directly proportional to the width of the gate (approximately equal to the 'channel width'). To facilitate comparison with bipolar transistors, the source periphery (virtually the same as the total channel width) is used. Dimensioning is then very similar to that of a bipolar transistor, namely 2 to 3 mm of source periphery per watt of output power.

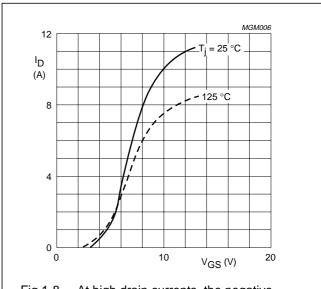

An equivalent to the emitter ballast resistors of a bipolar transistor is not required. This is because the temperature coefficient of the drain current as a function of the gate voltage is negative at high drain currents, providing automatic protection against thermal runaway, see Fig.1-8.

Fig.1-8 At high drain currents, the negative temperature coefficient of the drain current vs. gate voltage protects against thermal runaway.

### Transmitting transistor design

### 1.1.2.3 THE CHANNEL REGION

As for bipolar devices, the process used to manufacture a MOS transistor is dependent on the intended maximum operating frequency. A key parameter is the length of the channel,  $I_{ch}$ , (gate) because it determines the cut-off frequency,  $f_T$ :

$$f_{T} = \frac{G_{fs}}{2\pi C_{is}} = \frac{V_{sat}}{4\pi I_{ch}}$$

where:

G<sub>fs</sub> is the forward transconductance

Cis is the input capacitance

$V_{sat}$  is the saturation velocity (for silicon: 10<sup>7</sup> cm/s)

| Table 1-1 | VDMOS and | bipolar | devices | compared |

|-----------|-----------|---------|---------|----------|

|           |           |         |         |          |

## Transmitting transistor design

#### and

$\mathsf{I}_{ch}$  is the channel (gate) length.

#### 1.1.2.4 COMPARISON OF VDMOS AND BIPOLAR TRANSISTORS

Both Philips' bipolar and MOS types can provide excellent performance. At high frequencies (~1 GHz and above), bipolar transistors usually provide the best all-round performance. At lower frequencies, VDMOS devices can outperform bipolar types, e.g. on power gain, and will likely capture an increasing part of the present bipolar market as performance continues to improve.

| ADVANTAGES OF VDMOS                                                                                                                                                                                                                                      | DISADVANTAGES OF VDMOS                                                                                                                             |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| <b>Simpler biasing circuit.</b> This is primarily due to a MOS transistor's high input impedance, and the low and negative temperature coefficient at high drain currents.                                                                               | The gate is sensitive to electrostatic charges so ESD protection measures must be taken.                                                           |  |  |

| <b>Lower noise.</b> This is especially important in duplex equipment and where many transceivers are operating near to each other and at similar frequencies. In one test, an improvement of 7 dB was measured at 75 MHz in similar wideband amplifiers. | <b>Higher output power 'slump'</b> (reduction of output power at high temperature). Note, this is primarily caused by decreasing transconductance. |  |  |

| <b>Higher power gain (up to</b> ~ <b>5 dB higher)</b> than<br>comparable bipolar types at lower frequencies. This is<br>mainly due to the high transconductance and low<br>feedback capacitance.                                                         |                                                                                                                                                    |  |  |

| <b>Simple control of the output power.</b> The output power can be controlled down to almost zero simply by reducing the DC gate-source voltage.                                                                                                         |                                                                                                                                                    |  |  |

| <b>Superior thermal stability</b> owing to the negative temperature coefficient of the drain current at high levels, this is also why the current distribution over the whole active area of a VDMOS device is so good.                                  |                                                                                                                                                    |  |  |

| <b>Superior load mismatch tolerance</b> - Another benefit of the superior thermal stability of a VDMOSFET.                                                                                                                                               |                                                                                                                                                    |  |  |

| Lower high-order (7th and higher) intermodulation products due to the 'smoother' characteristics of MOS devices.                                                                                                                                         |                                                                                                                                                    |  |  |

### 1.1.3 Lateral DMOS (LDMOS) transistor dies

LDMOS technology is a relatively recent development. Unlike VDMOS which can be used up to about 1 GHz, LDMOS, like bipolar, is suitable for use at higher frequencies owing to its lower feedback capacitance and source inductance than VDMOS. However, depending on the particular performance and cost requirements, VDMOS, LDMOS or bipolar can provide the best solution.

### 1.1.3.1 THE SOURCE (SUBSTRATE MATERIAL)

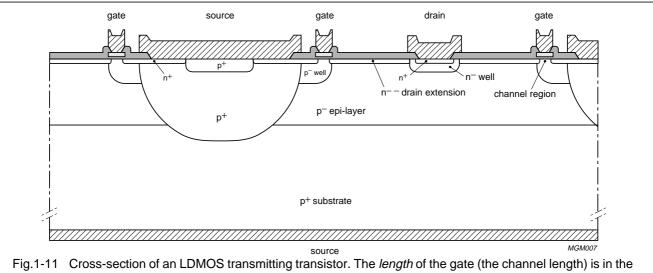

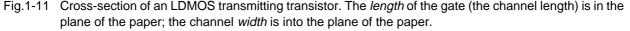

Philips LDMOS transistors are all silicon n-channel enhancement types, (see Fig.1-11). The substrate is highly doped p-material, whereas the epitaxial layer is lightly doped p<sup>-</sup>material.

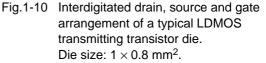

### 1.1.3.2 THE DRAIN AND GATE

The configuration of drain and gate is fairly similar to the interdigitated emitter and base of a bipolar transistor, see Fig.1-10. Note however that *all regions, (gate, source and drain) are metallized on top of the die.* The gate and drain are connected to bonding pads, and the source is grounded to the substrate by means of a via-diffusion through the epi-layer. The benefit of this design is that a *single* metal interconnect can be used. Note, the top source metallization is solely for interconnecting the p<sup>+</sup> and n<sup>+</sup> regions; the transistor's source electrode is connected to the bottom (substrate) metallization.

As for a VDMOS device, the RF output power that an LDMOS device can deliver depends on the maximum drain current ( $I_{DSX}$ ) which is directly proportional to the width of the gate (approximately equal to the 'channel

### Transmitting transistor design

width'). And, an equivalent to the emitter ballast resistors of a bipolar transistor is again not required, see Section 1.1.2.2.

### 1.1.3.3 THE CHANNEL REGION

As with VDMOS, a key parameter of an LDMOS transistor is the length of the channel,  $l_{ch}$  (gate) because it determines the cut-off frequency,  $f_T$  (defined as for VDMOS in Section 1.1.2.3).

#### 1.1.3.4 COMPARISON OF LDMOS AND BIPOLAR TRANSISTORS

Both Philips' LDMOS and bipolar transistors can provide excellent performance in a variety of applications. Nevertheless, there are some differences. For example, the lateral structure of an LDMOS transistor means it has a very low feedback capacitance compared with a bipolar transistor. And as power gain is directly related to the feedback capacitance and source (or emitter) inductance, this means an LDMOS transistor has higher power gain. Furthermore, an LDMOS transistor has superior intermodulation distortion performance over a large dynamic range.

#### Table 1-2 LDMOS and bipolar devices compared

| ADVANTAGES OF LDMOS                                                                                                                                                                                                                                                                            | DISADVANTAGES OF LDMOS                                                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Simpler biasing circuit.</b> This is primarily due to a MOS transistor's high input impedance, and the low and negative temperature coefficient at high drain currents.                                                                                                                     | The gate is sensitive to electrostatic charges, so ESD protection measures must be taken.                                                                |

| <ul> <li>Higher power gain than comparable bipolar types. This is due to the low source inductance and low feedback capacitance.</li> <li>Simple control of the output power. The output power can be controlled down to almost zero simply by reducing the DC gate-source voltage.</li> </ul> | <b>Higher output power 'slump'</b> (reduction of output power<br>at high temperature). Note, this is primarily caused by<br>decreasing transconductance. |

| <b>Superior thermal stability</b> owing to the negative temperature coefficient of the drain current at high levels. This is also why the current distribution over the whole active area of an LDMOS device is so good.                                                                       |                                                                                                                                                          |

| Superior load mismatch tolerance - another benefit of<br>the superior thermal stability of an LDMOSFET.<br>Lower high-order (7th and higher) intermodulation<br>products due to the 'smoother' characteristics of MOS<br>devices.                                                              |                                                                                                                                                          |

### 1.2 Transistor equivalent circuit

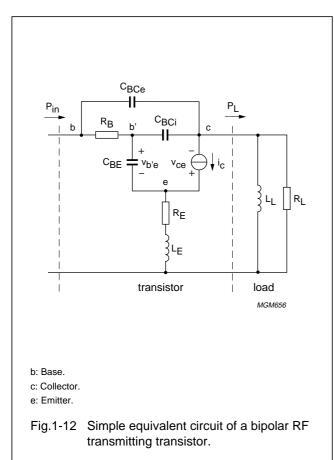

At this point, it is useful to introduce a basic equivalent circuit of a bipolar RF transmitting transistor, and a few simple expressions that indicate the behaviour of power gain, input and load impedance under different conditions. This will assist the understanding of the following section on internal matching.

Figure 1-12 shows a simple equivalent circuit of an RF transistor with load circuit. Note, the emitter inductance,  $L_E$ , affects transistor performance significantly as we shall see presently.

### 1.2.1 Main elements

The collector-to-base feedback capacitance consists of two parts (see Fig.1-1, transistor cross-section):

- An intrinsic part C<sub>BCi</sub>: the capacitance of the reverse biased collector-to-base junction in the regions below the emitter

- An extrinsic part C<sub>BCe</sub>: the capacitance of the same junction beyond the emitter. C<sub>BCe</sub> also includes parasitic capacitances introduced by the base metallization.

The sum of these capacitances,  $C_{BCt}\!,$  is published in data sheets as  $C_{re}\!\!:$

$$C_{re} = C_{BCi} + C_{BCe}$$

$R_B$  represents the series resistance of the base layer, and  $R_E$  is the emitter ballast resistance.  $C_{BE}$  represents the total forward biased base-emitter capacitance which is mainly determined by the diffusion capacitance, and which varies directly with the emitter current. This capacitance is normally shunted by a resistor, omitted here, since at high frequency operation, virtually all current flows into  $C_{BE}$ .

The collector is terminated by a load resistance  $R_L$  shunted by an inductance  $L_L$  which resonates with the total collector-to-base capacitance. Approximate expressions for these circuit elements are:

$$L_{L} = \frac{1}{\omega^{2}C_{BC}}$$

and  $R_{L} = \frac{V_{C}^{2}}{2P_{L}}$

### Transmitting transistor design

At high frequencies, the collector current,  $i_c$ , is proportional to the base-emitter current,  $i_{be}$ , and lags the latter by 90°:

$$i_{c} \approx i_{b'e} \left(\frac{\omega_{T}}{j\omega}\right)$$

Clearly, the high frequency common-emitter current gain,  $h_{fe}$ , is approximately  $\omega_T/\omega$ .

To simplify the following approximations, it has been assumed that:

- For maximum power, the collector circuit is in resonance, i.e. v<sub>ce</sub> and i<sub>c</sub> are in antiphase

- The base potential is very small compared to the collector voltage

- All collector parasitics are part of the load circuit.

## Transmitting transistor design

#### 1.2.2 Input impedance

With these assumptions, the input impedance,  $Z_{\text{in}},$  can be approximated by:

$$\begin{split} & Z_{in} = \left\lfloor \frac{1}{1 + \omega_T C_{BCt} R_L} \right\rfloor \times \\ & \left[ \left( 1 + \omega_T C_{BCi} R_L \right) R_B + \omega_T L_E + R_E + j \omega L_E \right. \\ & \left. + \frac{1}{j \omega} \left( \frac{1}{C_{BE}} + R_E \omega_T \right) \right] \end{split}$$

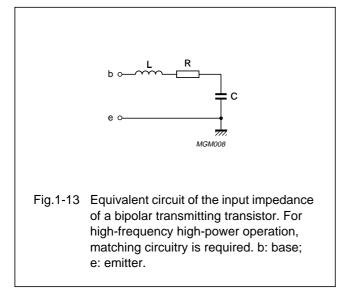

Note that emitter inductance effectively increases the total input resistance by  $\omega_T L_E$ . The emitter ballast resistance  $R_E$  appears as a series capacitance  $1/R_E\omega_T$ , decreasing the total input capacitance. Based on this expression, the total input impedance can be represented by a series RLC equivalent circuit, see Section 1.3.1.

### 1.2.3 Power gain

The power gain, Gp, can be approximated by:

$$G_{p} = \frac{P_{L}}{P_{in}} = \left(\frac{\omega_{T}}{\omega}\right)^{2} \left(\frac{1}{1 + \omega_{T}C_{BCt}R_{L}}\right) \times \left(\frac{R_{L}}{(1 + \omega_{T}C_{BCi}R_{L})R_{B} + R_{E} + \omega_{T}L_{E}}\right)$$

Note that emitter inductance  $L_E$  reduces power gain and is a key performance-determining factor in high-frequency transistors. It depends on bonding wire and package inductances. Other important parameters affecting power gain are  $R_E$  and these are determined by the active parts of the die design.

### 1.2.4 Large-signal expressions

The expressions given for  $Z_{in}$  and  $G_p$  relate to class-A amplifiers operating in the linear (i.e. small-signal) region. For large-signal operation, several elements become non-linear. The expressions can however still be used for a first-order approximation by substituting *average* values for the voltage and current dependent elements. In addition for class-B and class-C operation, the conduction angle, which affects the average value of  $\omega_T$ , should be taken into account.

### 1.3 Internal matching

Impedance matching is required to optimize the performance of a transmitting transistor in the application for which it was designed. Internal matching raises impedances and improves wideband capability. To assist designers, many of Philips' transmitting transistors already incorporate internal matching circuitry, simplifying or reducing the external matching required.

### 1.3.1 Input matching

Figure 1-13 shows the equivalent circuit of the input impedance of a bipolar transmitting transistor without matching circuitry.

At high frequencies, the capacitor has very low reactance and can be neglected in most cases. In a high-power transistor, the resistor becomes very small, typically <1  $\Omega$ , as such a device can be considered as many small 'transistors' in parallel The inductor, which is normally 1 to 2 nH, has a rather high reactance in the UHF region, so the input Q becomes high, making wideband matching difficult if not impossible, while circuit losses increase significantly. To compensate for these effects, an additional capacitor is often fabricated 'inside' the

### Transmitting transistor design

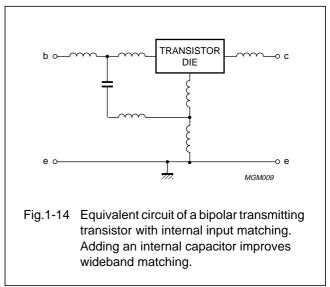

transistor such that the transistor equivalent circuit is as shown in Fig.1-14.

This capacitor, together with the base and emitter inductances, forms a first matching section that raises the input impedance to a more acceptable level. The resonant frequency of the section is set to be somewhat above the maximum operating frequency for which the transistor is intended.

An additional advantage of this configuration is that it increases the power gain slightly at the high end of the frequency band, not only because of reduced circuit losses, but mainly because the capacitor is, in effect, connected to a tap on the emitter lead inductance, overcoming a major cause of reduced power gain at high frequencies (emitter lead inductance).

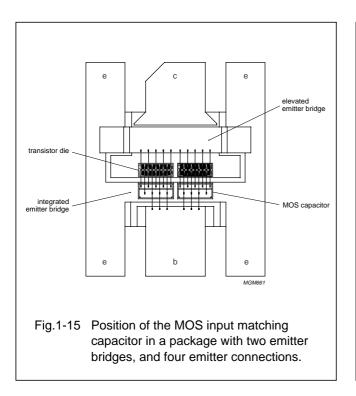

A MOS capacitor is used, and it can only be used in transistor packages with two emitter 'bridges': one, the normal elevated bridge; the other, an integrated bridge on the beryllia disc to which the capacitor is soldered. The maximum performance improvement is obtained with packages having *four* emitter connections (see Fig.1-15). Better still of course are packages with internal emitter grounding.

### 1.3.2 Output matching

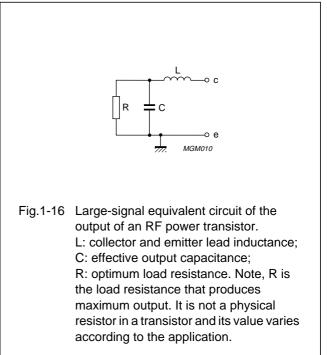

At the output of a transistor, the situation is somewhat different, see Fig.1-16.

In wideband matching circuits, it is desirable to tune out (with inductive shunt) the capacitor C somewhere in the frequency band for which the transistor is intended. In practice, the best results are obtained when the resonant frequency is in the lower part of the band.

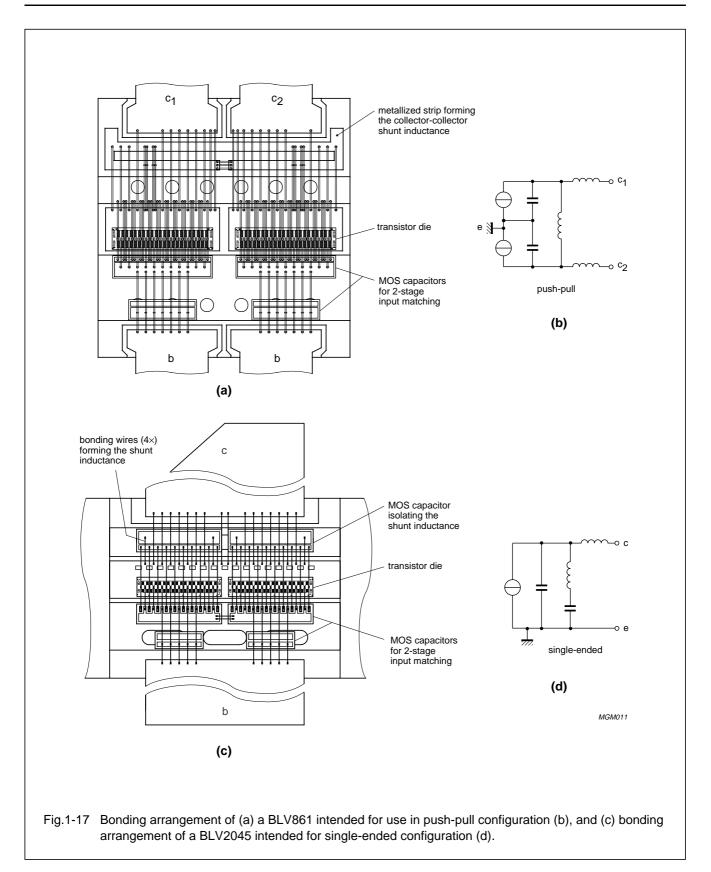

If an *external* shunt inductor were used for this purpose, the result would be a very low inductive tap, making further matching extremely difficult, especially at high powers and frequencies. A better solution would be to tune out the collector capacitance *inside the transistor package*. This is

done in practice in balanced (push-pull) transistors by adding a metallized strip onto the beryllia or aluminium nitride disc. In single-ended devices, it is done by connecting one side (the other is grounded) of a MOS capacitor that provides isolation to the collector via bonding wires that form the required shunt inductance, see Fig.1-17.

A disadvantage of this approach in both cases is that such a transistor is unsuitable for use in frequency bands lower than the one for which it is intended. This limitation is outweighed however by the higher load impedance and lower Q-factor, resulting in lower losses in the matching circuit and improved wideband performance.

## Transmitting transistor design

Transmitting transistor design

SUNSTAR 商斯达实业集团是集研发、生产、工程、销售、代理经销、技术咨询、信息服务等为一体的高科技企业,是专业高科技电子产品生产厂家,是具有10多年历史的专业电子元器件供应商,是中国最早和最大的仓储式连锁规模经营大型综合电子零部件代理分销商之一,是一家专业代理和分銷世界各大品牌IC芯片和電子元器件的连锁经营综合性国际公司,专业经营进口、国产名厂名牌电子元件,型号、种类齐全。在香港、北京、深圳、上海、西安、成都等全国主要电子市场设有直属分公司和产品展示展销窗口门市部专卖店及代理分销商,已在全国范围内建成强大统一的供货和代理分销网络。我们专业代理经销、开发生产电子元器件、集成电路、传感器、微波光电元器件、工控机/DOC/DOM电子盘、专用电路、单片机开发、MCU/DSP/ARM/FPGA软件硬件、二极管、三极管、模块等,是您可靠的一站式现货配套供应商、方案提供商、部件功能模块开发配套商。商斯达实业公司拥有庞大的资料库,有数位毕业于著名高校——有中国电子工业摇篮之称的西安电子科技大学(西军电)并长期从事国防尖端科技研究的高级工程师为您精挑细选、量身订做各种高科技电子元器件,并解决各种技术问题。

微波光电部专业代理经销高频、微波、光纤、光电元器件、组件、部件、模块、整机;电磁兼容元器件、材料、设备;微波 CAD、EDA 软件、开发测试仿真工具;微波、光纤仪器仪表。 欢迎国外高科技微波、光纤厂商将优秀产品介绍到中国、共同开拓市场。长期大量现货专业批发 高频、微波、卫星、光纤、电视、CATV 器件: 晶振、VCO、连接器、PIN 开关、变容二极管、开 关二极管、低噪晶体管、功率电阻及电容、放大器、功率管、MIIC、混频器、耦合器、功分器、 振荡器、合成器、衰减器、滤波器、隔离器、环行器、移相器、调制解调器;光电子元器件和组 件:红外发射管、红外接收管、光电开关、光敏管、发光二极管和发光二极管组件、半导体激光 二极管和激光器组件、光电探测器和光接收组件、光发射接收模块、光纤激光器和光放大器、光 调制器、光开关、DWDM 用光发射和接收器件、用户接入系统光光收发器件与模块、光纤连接器、 光纤跳线/尾纤、光衰减器、光纤适 配器、光隔离器、光耦合器、光环行器、光复用器/转换器; 无线收发芯片和模组、蓝牙芯片和模组。

更多产品请看本公司产品专用销售网站:

商斯达中国传感器科技信息网: http://www.sensor-ic.com/

商斯达工控安防网: http://www.pc-ps.net/

商斯达电子元器件网: http://www.sunstare.com/

商斯达微波光电产品网:HTTP://www.rfoe.net/

商斯达消费电子产品网://www.icasic.com/

商斯达实业科技产品网://www.sunstars.cn/ 微波元器件销售热线:

地址: 深圳市福田区福华路福庆街鸿图大厦 1602 室

电话: 0755-82884100 83397033 83396822 83398585

传真: 0755-83376182 (0) 13823648918 MSN: SUNS8888@hotmail.com

邮编: 518033 E-mail:szss20@163.com QQ: 195847376

深圳赛格展销部: 深圳华强北路赛格电子市场 2583 号 电话: 0755-83665529 25059422 技术支持: 0755-83394033 13501568376

欢迎索取免费详细资料、设计指南和光盘;产品凡多,未能尽录,欢迎来电查询。

北京分公司:北京海淀区知春路 132 号中发电子大厦 3097 号

TEL: 010-81159046 82615020 13501189838 FAX: 010-62543996 上海分公司: 上海市北京东路 668 号上海賽格电子市场 D125 号

TEL: 021-28311762 56703037 13701955389 FAX: 021-56703037

西安分公司: 西安高新开发区 20 所(中国电子科技集团导航技术研究所) 西安劳动南路 88 号电子商城二楼 D23 号

TEL: 029-81022619 13072977981 FAX:029-88789382